Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                  |

| Core Processor             | HC08                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | -                                                                    |

| Peripherals                | LVD, POR, PWM                                                        |

| Number of I/O              | 13                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 4x10b                                                            |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | 16-SOIC                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908qy8cdwe |

# MC68HC908QB8 MC68HC908QB4 MC68HC908QY8

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005–2010. All rights reserved.

MC68HC908QB8 Data Sheet, Rev. 3

# Chapter 11 Oscillator Module (OSC)

| 11.1 Introduction                             | . 93 |

|-----------------------------------------------|------|

| 11.2 Features                                 | . 93 |

| 11.3 Functional Description                   | . 93 |

| 11.3.1 Internal Signal Definitions            |      |

| 11.3.1.1 Oscillator Enable Signal (SIMOSCEN)  |      |

| 11.3.1.2 XTAL Oscillator Clock (XTALCLK)      |      |

| 11.3.1.3 RC Oscillator Clock (RCCLK)          | . 95 |

| 11.3.1.4 Internal Oscillator Clock (INTCLK)   | . 95 |

| 11.3.1.5 Bus Clock Times 4 (BUSCLKX4)         | . 95 |

| 11.3.1.6 Bus Clock Times 2 (BUSCLKX2)         | . 95 |

| 11.3.2 Internal Oscillator                    | . 95 |

| 11.3.2.1 Internal Oscillator Trimming         | . 96 |

| 11.3.2.2 Internal to External Clock Switching |      |

| 11.3.2.3 External to Internal Clock Switching |      |

| 11.3.3 External Oscillator                    |      |

| 11.3.4 XTAL Oscillator                        |      |

| 11.3.5 RC Oscillator                          | . 98 |

| 11.4 Interrupts                               | . 98 |

| 11.5 Low-Power Modes                          | . 98 |

| 11.5.1 Wait Mode                              | . 98 |

| 11.5.2 Stop Mode                              | . 98 |

| 11.6 OSC During Break Interrupts              | . 99 |

| 11.7 I/O Signals                              |      |

| 11.7.1 Oscillator Input Pin (OSC1)            |      |

| 11.7.2 Oscillator Output Pin (OSC2)           |      |

| 11.8 Registers                                |      |

| 11.8.1 Oscillator Status and Control Register |      |

| 11.8.2 Oscillator Trim Register (OSCTRIM)     |      |

| Those Committee Thin Hogistor (Coc Hinn)      |      |

| Chapter 12                                    |      |

| Input/Output Ports (PORTS)                    |      |

| 12.1 Introduction                             | 102  |

|                                               |      |

|                                               | 103  |

| 12.2.1 Port A Data Register                   |      |

| 12.2.2 Data Direction Register A              |      |

| 12.2.3 Port A Input Pullup Enable Register    |      |

| 12.2.4 Port A Summary Table                   |      |

| 12.3 Port B                                   |      |

| $oldsymbol{\circ}$                            |      |

| 12.3.2 Data Direction Register B              |      |

| 12.3.3 Port B Input Pullup Enable Register    |      |

| 12.3.4 Port B Summary Table                   | 108  |

|                                               |      |

# Chapter 13

MC68HC908QB8 Data Sheet, Rev. 3

# **Chapter 1 General Description**

# 1.1 Introduction

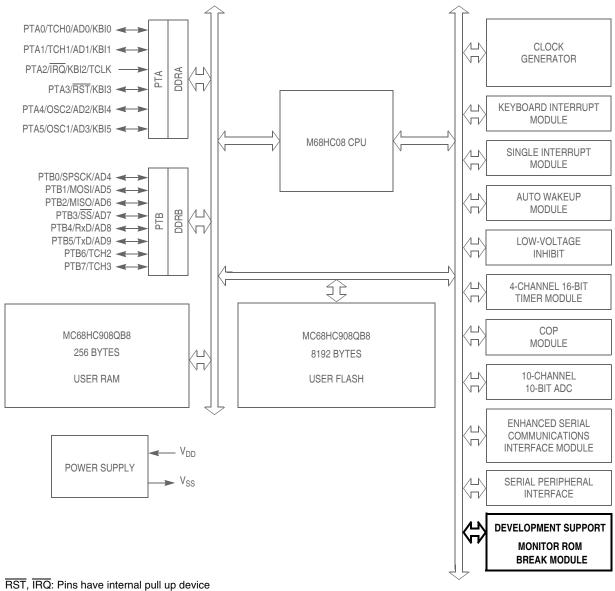

The MC68HC908QB8 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

Pin FLASH/RAM 16-Bit Timer **ADC ESCI** SPI **Device** Channels **Memory Size** Count MC68HC908QB8 8K/256 bytes 10 channel, 10 bit Yes Yes 16 pins 4 4 10 channel, 10 bit Yes MC68HC908QB4 4K/128 bytes Yes 16 pins MC68HC908QY8 4 channel, 10 bit 2 8K/256 bytes No No 16 pins

**Table 1-1. Summary of Device Variations**

# 1.2 Features

#### Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

- Trimmable internal oscillator

- Software selectable 1 MHz, 2 MHz, or 3.2 MHz internal bus operation

- 8-bit trim capability

- ± 25% untrimmed

- Trimmable to approximately 0.4%<sup>(1)</sup>

- Software selectable crystal oscillator range, 32–100 kHz, 1–8 MHz, and 8–32 MHz

- Software configurable input clock from either internal or external source

- Auto wakeup from STOP capability using dedicated internal 32-kHz RC or bus clock source

- On-chip in-application programmable FLASH memory

- Internal program/erase voltage generation

- Monitor ROM containing user callable program/erase routines

- FLASH security<sup>(2)</sup>

<sup>1.</sup> See 18.11 Oscillator Characteristics for internal oscillator specifications

No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

| Addr.                                          | Register Name                                       |                 | Bit 7     | 6          | 5      | 4           | 3              | 2        | 1      | Bit 0  |

|------------------------------------------------|-----------------------------------------------------|-----------------|-----------|------------|--------|-------------|----------------|----------|--------|--------|

|                                                | TIM Counter Register Low                            | Read:           | Bit 7     | Bit 6      | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0  |

| \$0022                                         | (TCNTL)                                             | Write:          |           |            |        |             |                |          |        |        |

|                                                | See page 185.                                       | Reset:          | 0         | 0          | 0      | 0           | 0              | 0        | 0      | 0      |

| \$0023                                         | TIM Counter Modulo<br>Register High (TMODH)         | Read:<br>Write: | Bit 15    | Bit 14     | Bit 13 | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8  |

|                                                | See page 185.                                       | Reset:          | 1         | 1          | 1      | 1           | 1              | 1        | 1      |        |

| \$0024                                         | TIM Counter Modulo<br>Register Low (TMODL)          | Read:<br>Write: | Bit 7     | Bit 6      | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0  |

|                                                | See page 185.                                       | Reset:          | 1         | 1          | 1      | 1           | 1              | 1        | 1      | 1      |

| \$0025                                         | TIM Channel 0 Status and Control Register (TSC0)    | Read:<br>Write: | CH0F<br>0 | CH0IE      | MS0B   | MS0A        | ELS0B          | ELS0A    | TOV0   | CH0MAX |

|                                                | See page 186.                                       | Reset:          | 0         | 0          | 0      | 0           | 0              | 0        | 0      | 0      |

| \$0026                                         | TIM Channel 0<br>Register High (TCH0H)              | Read:<br>Write: | Bit 15    | Bit 14     | Bit 13 | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8  |

|                                                | See page 189.                                       | Reset:          |           |            |        | Indetermina | te after reset |          |        |        |

| \$0027                                         | TIM Channel 0<br>Register Low (TCH0L)               | Read:<br>Write: | Bit 7     | Bit 6      | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0  |

|                                                | See page 189.                                       | Reset:          |           |            | l-     | Indetermina | te after reset |          | l .    |        |

| \$0028                                         | TIM Channel 1 Status and Control Register (TSC1)    | Read:<br>Write: | CH1F<br>0 | CH1IE      | 0      | MS1A        | ELS1B          | ELS1A    | TOV1   | CH1MAX |

|                                                | See page 186.                                       | Reset:          | 0         | 0          | 0      | 0           | 0              | 0        | 0      | 0      |

| \$0029                                         | TIM Channel 1<br>Register High (TCH1H)              | Read:<br>Write: | Bit 15    | Bit 14     | Bit 13 | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8  |

| See page 189. Reset: Indeterminate after reset |                                                     |                 |           |            |        |             |                | l .      |        |        |

| \$002A                                         | TIM Channel 1<br>Register Low (TCH1L)               | Read:<br>Write: | Bit 7     | Bit 6      | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0  |

| ,                                              | See page 189.                                       | Reset:          |           |            |        | Indetermina | te after reset |          | I      |        |

| \$002B                                         |                                                     |                 |           |            |        |             |                |          |        |        |

| ↓<br>************************************      | Reserved                                            |                 |           |            |        |             |                |          |        |        |

| \$002F                                         |                                                     |                 |           |            |        |             |                |          |        |        |

| \$0030                                         | TIM Channel 2 Status and<br>Control Register (TSC2) | Read:<br>Write: | CH2F<br>0 | CH2IE      | 0      | MS2A        | ELS2B          | ELS2A    | TOV2   | CH2MAX |

| ψυσσο                                          | See page 186.                                       | Reset:          | 0         | 0          | 0      | 0           | 0              | 0        | 0      | 0      |

| \$0031                                         | TIM Channel 2<br>Register High (TCH2H)              | Read:<br>Write: | Bit 15    | Bit 14     | Bit 13 | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8  |

| φυυσ ι                                         | See page 189.                                       | Reset:          |           |            |        | Indetermina | te after reset |          |        |        |

|                                                | TIM Channel 2                                       | Read:           |           |            |        |             |                |          |        |        |

| \$0032                                         | Register Low (TCH2L) See page 189.                  | Write:          | Bit 7     | Bit 6      | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0  |

|                                                | TIM Channel 3 Status and                            | Reset:<br>Read: |           |            |        |             |                |          |        |        |

| \$0033                                         | Control Register (TSC3)                             | Write:          | CH3F<br>0 | CH3IE      | 0      | MS3A        | ELS3B          | ELS3A    | TOV3   | CH3MAX |

|                                                | See page 186.                                       | Reset:          | 0         | 0          | 0      | 0           | 0              | 0        | 0      | 0      |

| \$0034                                         | TIM Channel 3<br>Register High (TCH3H)              | Read:<br>Write: | Bit 15    | Bit 14     | Bit 13 | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8  |

|                                                | See page 189.                                       | Reset:          |           | I          | I      | Indetermina | te after reset |          | I      |        |

| \$0035                                         | TIM Channel 3<br>Register Low (TCH3L)               | Read:<br>Write: | Bit 7     | Bit 6      | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0  |

|                                                | See page 189.                                       | Reset:          |           | т          |        |             | te after reset |          |        |        |

|                                                |                                                     |                 |           | = Unimplem | ented  | R           | = Reserved     | U = Unaf | fected |        |

Figure 2-2. Control, Status, and Data Registers (Sheet 3 of 5)

MC68HC908QB8 Data Sheet, Rev. 3

# **AWUIE** — Auto Wakeup Interrupt Enable Bit

This read/write bit enables the auto wakeup interrupt input to latch interrupt requests. Reset clears AWUIE.

- 1 = Auto wakeup enabled as interrupt input

- 0 = Auto wakeup not enabled as interrupt input

#### NOTE

KBIE5–KBIE0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 9.8.2 Keyboard Interrupt Enable Register (KBIER).

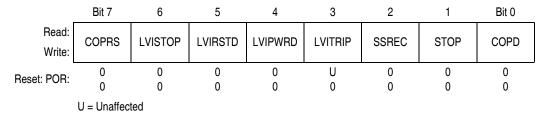

# 4.6.4 Configuration Register 2

The configuration register 2 (CONFIG2), is used to allow the bus clock source to run in STOP. In this case, the clock, BUSCLKX2 will be used to drive the AWU request generator.

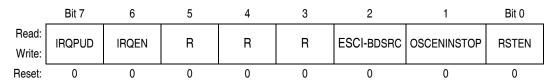

Figure 4-5. Configuration Register 2 (CONFIG2)

# OSCENINSTOP — Oscillator Enable in Stop Mode Bit

OSCENINSTOP, when set, will allow the bus clock source (BUSCLKX2) to generate clocks for the AWU in stop mode. See 11.8.1 Oscillator Status and Control Register for information on enabling the external clock sources.

- 1 = Oscillator enabled to operate during stop mode

- 0 = Oscillator disabled during stop mode

#### NOTE

IRQPUD, IRQEN, ESCIBDSRC, and RSTEN bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see Chapter 5 Configuration Register (CONFIG).

# 4.6.5 Configuration Register 1

The configuration register 1 (CONFIG1), is used to select the period for the AWU. The timeout will be based on the COPRS bit along with the clock source for the AWU.

Figure 4-6. Configuration Register 1 (CONFIG1)

# Table 7-1. Instruction Set Summary (Sheet 6 of 6)

| Source                                                       | Operation                             | Description                                                                                                                                                                                                                                                                                                                                                                  | Effect on CCR |   |         |          | - |   | Address<br>Mode                       | Opcode                             | Operand        | es     |

|--------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---|---------|----------|---|---|---------------------------------------|------------------------------------|----------------|--------|

| Form                                                         | operation.                            | =                                                                                                                                                                                                                                                                                                                                                                            |               |   | / H I N |          | Z | С | Add                                   | Opc                                | Ope            | Cycles |

| SWI                                                          | Software Interrupt                    | $\begin{array}{c} PC \leftarrow (PC) + 1;  Push  (PCL) \\ SP \leftarrow (SP) - 1;  Push  (PCH) \\ SP \leftarrow (SP) - 1;  Push  (X) \\ SP \leftarrow (SP) - 1;  Push  (A) \\ SP \leftarrow (SP) - 1;  Push  (CCR) \\ SP \leftarrow (SP) - 1;  I \leftarrow 1 \\ PCH \leftarrow Interrupt  Vector  High  Byte \\ PCL \leftarrow Interrupt  Vector  Low  Byte \\ \end{array}$ | _             | _ | 1       | _        | _ | _ | INH                                   | 83                                 |                | 9      |

| TAP                                                          | Transfer A to CCR                     | CCR ← (A)                                                                                                                                                                                                                                                                                                                                                                    | 1             | 1 | ‡       | ‡        | 1 | 1 | INH                                   | 84                                 |                | 2      |

| TAX                                                          | Transfer A to X                       | X ← (A)                                                                                                                                                                                                                                                                                                                                                                      | -             | - | _       | -        | - | - | INH                                   | 97                                 |                | 1      |

| TPA                                                          | Transfer CCR to A                     | $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                         | -             | - | _       | -        | - | - | INH                                   | 85                                 |                | 1      |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP | Test for Negative or Zero             | (A) – \$00 or (X) – \$00 or (M) – \$00                                                                                                                                                                                                                                                                                                                                       | 0             | _ | _       | <b>‡</b> | 1 | ı | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D | dd<br>ff<br>ff | 311324 |

| TSX                                                          | Transfer SP to H:X                    | H:X ← (SP) + 1                                                                                                                                                                                                                                                                                                                                                               | -             | - | -       | -        | - | - | INH                                   | 95                                 |                | 2      |

| TXA                                                          | Transfer X to A                       | A ← (X)                                                                                                                                                                                                                                                                                                                                                                      | -             | - | _       | -        | - | - | INH                                   | 9F                                 |                | 1      |

| TXS                                                          | Transfer H:X to SP                    | (SP) ← (H:X) – 1                                                                                                                                                                                                                                                                                                                                                             | -             | - | _       | _        | _ | - | INH                                   | 94                                 |                | 2      |

| WAIT                                                         | Enable Interrupts; Wait for Interrupt | I bit ← 0; Inhibit CPU clocking until interrupted                                                                                                                                                                                                                                                                                                                            | -             | - | 0       | -        | - | _ | INH                                   | 8F                                 |                | 1      |

| Α     | Accumulator                                                         | n               | Any bit                                     |

|-------|---------------------------------------------------------------------|-----------------|---------------------------------------------|

| С     | Carry/borrow bit                                                    | opr             | Operand (one or two bytes)                  |

| CCR   | Condition code register                                             | PC              | Program counter                             |

| dd    | Direct address of operand                                           | PCH             | Program counter high byte                   |

| dd rr | Direct address of operand and relative offset of branch instruction | PCL             | Program counter low byte                    |

| DD    | Direct to direct addressing mode                                    | REL             | Relative addressing mode                    |

| DIR   | Direct addressing mode                                              | rel             | Relative program counter offset byte        |

| DIX+  | Direct to indexed with post increment addressing mode               | rr              | Relative program counter offset byte        |

| ee ff | High and low bytes of offset in indexed, 16-bit offset addressing   | SP1             | Stack pointer, 8-bit offset addressing mode |

| EXT   | Extended addressing mode                                            |                 | Stack pointer 16-bit offset addressing mode |

| ff    | Offset byte in indexed, 8-bit offset addressing                     | SP              | Stack pointer                               |

| H     | Half-carry bit                                                      | U               | Undefined                                   |

| H     | Index register high byte                                            | V               | Overflow bit                                |

| hh II | High and low bytes of operand address in extended addressing        | Χ               | Index register low byte                     |

|       | Interrupt mask                                                      | Z               | Zero bit                                    |

| ii    | Immediate operand byte                                              | &               | Logical AND                                 |

| IMD   | Immediate source to direct destination addressing mode              |                 | Logical OR                                  |

| IMM   | Immediate addressing mode                                           | $\oplus$        | Logical EXCLUSIVE OR                        |

| INH   | Inherent addressing mode                                            | ()              | Contents of                                 |

| IX    | Indexed, no offset addressing mode                                  | <del>-</del> () | Negation (two's complement)                 |

| IX+   | Indexed, no offset, post increment addressing mode                  | #`              | Immediate value                             |

| IX+D  | Indexed with post increment to direct addressing mode               | **              | Sign extend                                 |

| IX1   | Indexed, 8-bit offset addressing mode                               | $\leftarrow$    | Loaded with                                 |

| IX1+  | Indexed, 8-bit offset, post increment addressing mode               | ?               | If                                          |

| IX2   | Indexed, 16-bit offset addressing mode                              | :               | Concatenated with                           |

| M     | Memory location                                                     | <b>‡</b>        | Set or cleared                              |

| N     | Negative bit                                                        | _               | Not affected                                |

|       |                                                                     |                 |                                             |

# 7.8 Opcode Map

See Table 7-2.

External Interrupt (IRQ)

# 11.3.1 Internal Signal Definitions

The following signals and clocks are used in the functional description and figures of the OSC module.

# 11.3.1.1 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and disables the XTAL oscillator circuit, the RC oscillator, or the internal oscillator in stop mode. OSCENINSTOP in the configuration register can be used to override this signal.

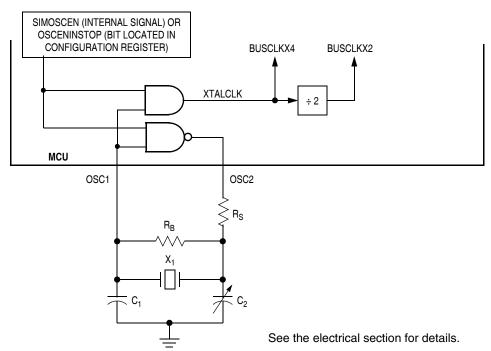

## 11.3.1.2 XTAL Oscillator Clock (XTALCLK)

XTALCLK is the XTAL oscillator output signal. It runs at the full speed of the crystal (f<sub>XCLK</sub>) and comes directly from the crystal oscillator circuit. Figure 11-2 shows only the logical relation of XTALCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of XTALCLK is unknown and may depend on the crystal and other external factors. The frequency of XTALCLK can be unstable at start up.

#### 11.3.1.3 RC Oscillator Clock (RCCLK)

RCCLK is the RC oscillator output signal. Its frequency is directly proportional to the time constant of the external R ( $R_{EXT}$ ) and internal C. Figure 11-3 shows only the logical relation of RCCLK to OSC1 and may not represent the actual circuitry.

#### 11.3.1.4 Internal Oscillator Clock (INTCLK)

INTCLK is the internal oscillator output signal. INTCLK is software selectable to be nominally 12.8 MHz, 8.0 MHz, or 4.0 MHz. INTCLK can be digitally adjusted using the oscillator trimming feature of the OSCTRIM register (see 11.3.2.1 Internal Oscillator Trimming).

#### 11.3.1.5 Bus Clock Times 4 (BUSCLKX4)

BUSCLKX4 is the same frequency as the input clock (XTALCLK, RCCLK, or INTCLK). This signal is driven to the SIM module and is used during recovery from reset and stop and is the clock source for the COP module.

# 11.3.1.6 Bus Clock Times 2 (BUSCLKX2)

The frequency of this signal is equal to half of the BUSCLKX4. This signal is driven to the SIM for generation of the bus clocks used by the CPU and other modules on the MCU. BUSCLKX2 will be divided by two in the SIM. The internal bus frequency is one fourth of the XTALCLK, RCCLK, or INTCLK frequency.

#### 11.3.2 Internal Oscillator

The internal oscillator circuit is designed for use with no external components to provide a clock source with a tolerance of less than  $\pm 25\%$  untrimmed. An 8-bit register (OSCTRIM) allows the digital adjustment to a tolerance of ACC<sub>INT</sub>. See the oscillator characteristics in the Electrical section of this data sheet.

The internal oscillator is capable of generating clocks of 12.8 MHz, 8.0 MHz, or 4.0 MHz (INTCLK) resulting in a bus frequency (INTCLK divided by 4) of 3.2 MHz, 2.0 MHz, or 1.0 MHz respectively. The bus clock is software selectable and defaults to the 1.0-MHz bus out of reset. Users can increase the bus frequency based on the voltage range of their application.

Freescale Semiconductor 95

MC68HC908QB8 Data Sheet, Rev. 3

## 11.3.4 XTAL Oscillator

The XTAL oscillator circuit is designed for use with an external crystal or ceramic resonator to provide an accurate clock source. In this configuration, the OSC2 pin is dedicated to the external crystal circuit. The OSC2EN bit has no effect when this clock mode is selected.

In its typical configuration, the XTAL oscillator is connected in a Pierce oscillator configuration, as shown in Figure 11-2. This figure shows only the logical representation of the internal components and may not represent actual circuitry.

The oscillator configuration uses five components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>B</sub>

- Series resistor, R<sub>s</sub> (optional)

#### NOTE

The series resistor ( $R_s$ ) is included in the diagram to follow strict Pierce oscillator guidelines and may not be required for all ranges of operation, especially with high frequency crystals. Refer to the oscillator characteristics table in the Electricals section for more information.

Figure 11-2. XTAL Oscillator External Connections

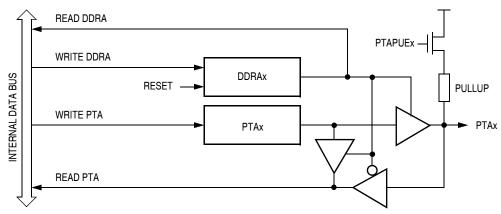

Figure 12-3. Port A I/O Circuit NOTE

Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading PTA reads the PTAx data latch. When DDRAx is a 0, reading PTA reads the logic level on the PTAx pin. The data latch can always be written, regardless of the state of its data direction bit.

# 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each of the port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

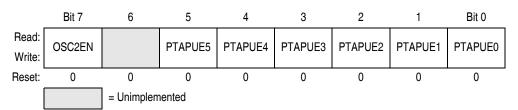

Figure 12-4. Port A Input Pullup Enable Register (PTAPUE)

#### OSC2EN — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

- 1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

- 0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

# PTAPUE[5:0] — Port A Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port A pins.

- 1 = Corresponding port A pin configured to have internal pullup if its DDRA bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port A pin regardless of the state of its DDRA bit

#### **Enhanced Serial Communications Interface (ESCI) Module**

# 13.4.1 Transmitter Interrupts

These conditions can generate interrupt requests from the ESCI transmitter:

- ESCI transmitter empty (SCTE) The SCTE bit in SCS1 indicates that the SCDR has transferred

a character to the transmit shift register. SCTE can generate a transmitter interrupt request. Setting

the ESCI transmit interrupt enable bit, SCTIE, in SCC2 enables the SCTE bit to generate

transmitter interrupt requests.

- Transmission complete (TC) The TC bit in SCS1 indicates that the transmit shift register and the SCDR are empty and that no break or idle character has been generated. The transmission complete interrupt enable bit, TCIE, in SCC2 enables the TC bit to generate transmitter interrupt requests.

# 13.4.2 Receiver Interrupts

These sources can generate interrupt requests from the ESCI receiver:

- ESCI receiver full (SCRF) The SCRF bit in SCS1 indicates that the receive shift register has

transferred a character to the SCDR. SCRF can generate a receiver interrupt request. Setting the

ESCI receive interrupt enable bit, SCRIE, in SCC2 enables the SCRF bit to generate receiver

interrupts.

- Idle input (IDLE) The IDLE bit in SCS1 indicates that 10 or 11 consecutive 1s shifted in from the RxD pin. The idle line interrupt enable bit, ILIE, in SCC2 enables the IDLE bit to generate interrupt requests.

# 13.4.3 Error Interrupts

These receiver error flags in SCS1 can generate interrupt requests:

- Receiver overrun (OR) The OR bit indicates that the receive shift register shifted in a new

character before the previous character was read from the SCDR. The previous character remains

in the SCDR, and the new character is lost. The overrun interrupt enable bit, ORIE, in SCC3

enables OR to generate ESCI error interrupt requests.

- Noise flag (NF) The NF bit is set when the ESCI detects noise on incoming data or break characters, including start, data, and stop bits. The noise error interrupt enable bit, NEIE, in SCC3 enables NF to generate ESCI error interrupt requests.

- Framing error (FE) The FE bit in SCS1 is set when a 0 occurs where the receiver expects a stop bit. The framing error interrupt enable bit, FEIE, in SCC3 enables FE to generate ESCI error interrupt requests.

- Parity error (PE) The PE bit in SCS1 is set when the ESCI detects a parity error in incoming data. The parity error interrupt enable bit, PEIE, in SCC3 enables PE to generate ESCI error interrupt requests.

# 13.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 13.5.1 Wait Mode

The ESCI module remains active in wait mode. Any enabled interrupt request from the ESCI module can bring the MCU out of wait mode.

If ESCI module functions are not required during wait mode, reduce power consumption by disabling the module before executing the WAIT instruction.

MC68HC908QB8 Data Sheet, Rev. 3

## SCP1 and SCP0 — ESCI Baud Rate Register Prescaler Bits

These read/write bits select the baud rate register prescaler divisor as shown in Table 13-6.

Table 13-6. ESCI Baud Rate Prescaling

| SCP[1:0] | Baud Rate Register<br>Prescaler Divisor (BPD) |

|----------|-----------------------------------------------|

| 0 0      | 1                                             |

| 0 1      | 3                                             |

| 1 0      | 4                                             |

| 1 1      | 13                                            |

#### SCR2-SCR0 — ESCI Baud Rate Select Bits

These read/write bits select the ESCI baud rate divisor as shown in Table 13-7. Reset clears SCR2–SCR0.

Table 13-7. ESCI Baud Rate Selection

| SCR[2:1:0] | Baud Rate Divisor (BD) |

|------------|------------------------|

| 0 0 0      | 1                      |

| 0 0 1      | 2                      |

| 0 1 0      | 4                      |

| 0 1 1      | 8                      |

| 1 0 0      | 16                     |

| 1 0 1      | 32                     |

| 1 1 0      | 64                     |

| 1 1 1      | 128                    |

# 13.8.8 ESCI Prescaler Register

The ESCI prescaler register (SCPSC) together with the ESCI baud rate register selects the baud rate for both the receiver and the transmitter.

#### **NOTE**

There are two prescalers available to adjust the baud rate — one in the ESCI baud rate register and one in the ESCI prescaler register.

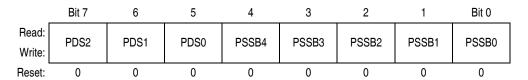

Figure 13-17. ESCI Prescaler Register (SCPSC)

MC68HC908QB8 Data Sheet, Rev. 3

**System Integration Module (SIM)**

#### 14.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

# 14.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 17 Development Support.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

# 14.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

#### 14.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

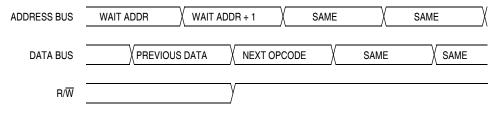

#### 14.7.1 Wait Mode

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 14-14 shows the timing for wait mode entry.

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

#### Figure 14-14. Wait Mode Entry Timing

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred.

MC68HC908QB8 Data Sheet, Rev. 3

#### Serial Peripheral Interface (SPI) Module

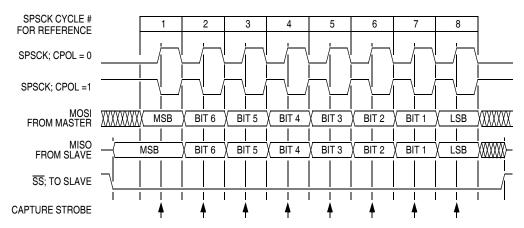

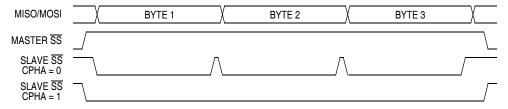

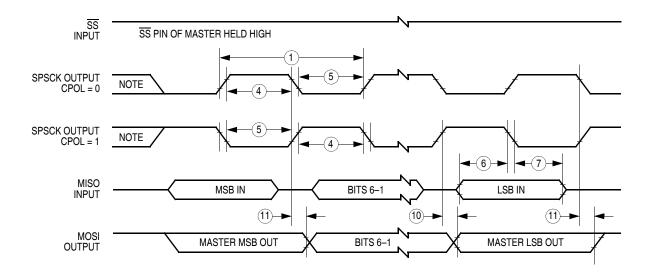

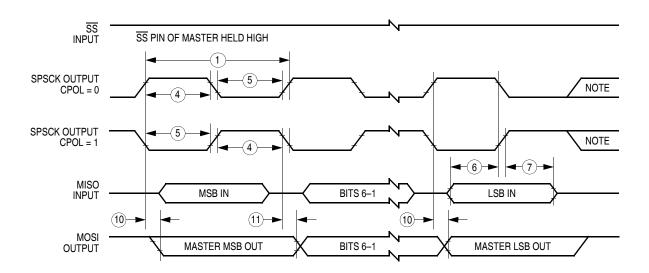

Figure 15-4. Transmission Format (CPHA = 0)

Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram because the serial clock (SPSCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input ( $\overline{SS}$ ) is low, so that only the selected slave drives to the master. The  $\overline{SS}$  pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$  pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI. (See 15.3.6.2 Mode Fault Error.) When CPHA = 0, the first SPSCK edge is the MSB capture strobe. Therefore, the slave must begin driving its data before the first SPSCK edge, and a falling edge on the  $\overline{SS}$  pin is used to start the slave data transmission. The slave's  $\overline{SS}$  pin must be toggled back to high and then low again between each byte transmitted as shown in Figure 15-5.

Figure 15-5. CPHA/SS Timing

#### 15.3.3.3 Transmission Format When CPHA = 1

Figure 15-6 shows an SPI transmission in which CPHA = 1. The figure should not be used as a replacement for data sheet parametric information. Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram because the serial clock (SPSCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input ( $\overline{SS}$ ) is low, so that only the selected slave drives to the master. The  $\overline{SS}$  pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$  pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI. (See 15.3.6.2 Mode Fault Error.) When CPHA = 1, the master begins driving its MOSI pin on the first SPSCK edge. Therefore, the slave uses the first SPSCK edge as a start transmission signal. The  $\overline{SS}$  pin can

MC68HC908QB8 Data Sheet, Rev. 3

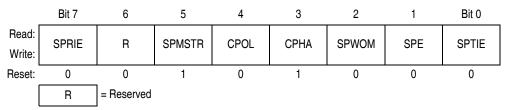

# 15.8.1 SPI Control Register

The SPI control register:

- Enables SPI module interrupt requests

- Configures the SPI module as master or slave

- Selects serial clock polarity and phase

- Configures the SPSCK, MOSI, and MISO pins as open-drain outputs

- Enables the SPI module

Figure 15-13. SPI Control Register (SPCR)

## SPRIE — SPI Receiver Interrupt Enable Bit

This read/write bit enables interrupt requests generated by the SPRF bit. The SPRF bit is set when a byte transfers from the shift register to the receive data register.

- 1 = SPRF interrupt requests enabled

- 0 = SPRF interrupt requests disabled

#### SPMSTR — SPI Master Bit

This read/write bit selects master mode operation or slave mode operation.

- 1 = Master mode

- 0 = Slave mode

#### **CPOL** — Clock Polarity Bit

This read/write bit determines the logic state of the SPSCK pin between transmissions. (See Figure 15-4 and Figure 15-6.) To transmit data between SPI modules, the SPI modules must have identical CPOL values.

#### CPHA — Clock Phase Bit

This read/write bit controls the timing relationship between the serial clock and SPI data. (See Figure 15-4 and Figure 15-6.) To transmit data between SPI modules, the SPI modules must have identical CPHA values. When CPHA = 0, the SS pin of the slave SPI module must be high between bytes. (See Figure 15-12.)

## SPWOM — SPI Wired-OR Mode Bit

This read/write bit configures pins SPSCK, MOSI, and MISO so that these pins become open-drain outputs.

- 1 = Wired-OR SPSCK, MOSI, and MISO pins

- 0 = Normal push-pull SPSCK, MOSI, and MISO pins

# SPE — SPI Enable

This read/write bit enables the SPI module. Clearing SPE causes a partial reset of the SPI. (See 15.3.5 Resetting the SPI.)

- 1 = SPI module enabled

- 0 = SPI module disabled

#### **Development Support**

All port pins have programmable pull up device PTA[0:5]: Higher current sink and source capability

Figure 17-1. Block Diagram Highlighting BRK and MON Blocks

#### **Development Support**

**Table 17-1. Monitor Mode Signal Requirements and Options**

| Mode                           | nde I III               |            |                   | RST<br>(PTA3) |              |              | Reset<br>Vector | Serial<br>Communi-<br>cation |                      | ode<br>ction | СОР                             | Со | mmunication<br>Speed | 1 | Comments |

|--------------------------------|-------------------------|------------|-------------------|---------------|--------------|--------------|-----------------|------------------------------|----------------------|--------------|---------------------------------|----|----------------------|---|----------|

|                                | (FIAZ)                  | (FTAS)     | Vector            | PTA0          | PTA1         | PTA4         |                 | External Clock               | Bus<br>Frequency     | Baud<br>Rate |                                 |    |                      |   |          |

| Normal<br>Monitor              | V <sub>TST</sub>        | $V_{DD}$   | Х                 | 1             | 1            | 0            | Disabled        | 9.8304<br>MHz                | 2.4576<br>MHz        | 9600         | Provide external clock at OSC1. |    |                      |   |          |

| Forced                         | V <sub>DD</sub>         | Х          | \$FFFF<br>(blank) | 1             | Х            | Х            | Disabled        | 9.8304<br>MHz                | 2.4576<br>MHz        | 9600         | Provide external clock at OSC1. |    |                      |   |          |

| Monitor                        | V <sub>SS</sub>         | Х          | \$FFFF<br>(blank) | 1             | Х            | Х            | Disabled        | Х                            | 3.2 MHz<br>(Trimmed) | 9600         | Internal clock is active.       |    |                      |   |          |

| User                           | Х                       | Х          | Not<br>\$FFFF     | Х             | Х            | Х            | Enabled         | Х                            | Х                    | Х            |                                 |    |                      |   |          |

| MON08<br>Function<br>[Pin No.] | V <sub>TST</sub><br>[6] | RST<br>[4] | _                 | COM<br>[8]    | MOD0<br>[12] | MOD1<br>[10] | _               | OSC1<br>[13]                 | _                    | _            |                                 |    |                      |   |          |

- 1. PTA0 must have a pullup resistor to  $V_{DD}$  in monitor mode.

- 2. Communication speed in the table is an example to obtain a baud rate of 9600. Baud rate using external oscillator is bus frequency / 256 and baud rate using internal oscillator is bus frequency / 335.

- 3. External clock is a 9.8304 MHz oscillator on OSC1.

- Lowering V<sub>TST</sub> once monitor mode is entered allows the clock source to be controlled by the OSCSC register.

- 5. X = don't care

- 6. MON08 pin refers to P&E Microcomputer Systems' MON08-Cyclone 2 by 8-pin connector.

| NC       | 1  | 2  | GND  |

|----------|----|----|------|

| NC       | 3  | 4  | RST  |

| NC       | 5  | 6  | IRQ  |

| NC       | 7  | 8  | PTA0 |

| NC       | 9  | 10 | PTA4 |

| NC       | 11 | 12 | PTA1 |

| OSC1     | 13 | 14 | NC   |

| $V_{DD}$ | 15 | 16 | NC   |

#### 17.3.1.1 Normal Monitor Mode

$\overline{RST}$  and OSC1 functions will be active on the PTA3 and PTA5 pins respectively as long as  $V_{TST}$  is applied to the  $\overline{IRQ}$  pin. If the  $\overline{IRQ}$  pin is lowered (no longer  $V_{TST}$ ) then the chip will still be operating in monitor mode, but the pin functions will be determined by the settings in the configuration registers (see Chapter 5 Configuration Register (CONFIG)) when  $V_{TST}$  was lowered. With  $V_{TST}$  lowered, the BIH and BIL instructions will read the  $\overline{IRQ}$  pin state only if IRQEN is set in the CONFIG2 register.

If monitor mode was entered with  $V_{TST}$  on  $\overline{IRQ}$ , then the COP is disabled as long as  $V_{TST}$  is applied to  $\overline{IRQ}$ .

MC68HC908QB8 Data Sheet, Rev. 3

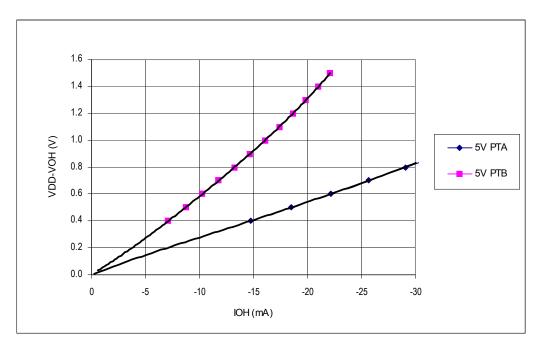

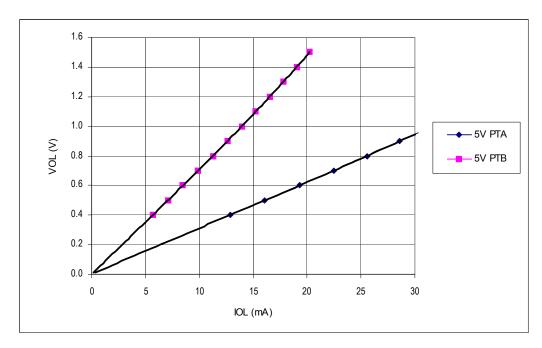

# **18.6 Typical 5-V Output Drive Characteristics**

Figure 18-1. Typical 5-Volt Output High Voltage versus Output High Current (25°C)

Figure 18-2. Typical 5-Volt Output Low Voltage versus Output Low Current (25°C)

#### **Electrical Specifications**

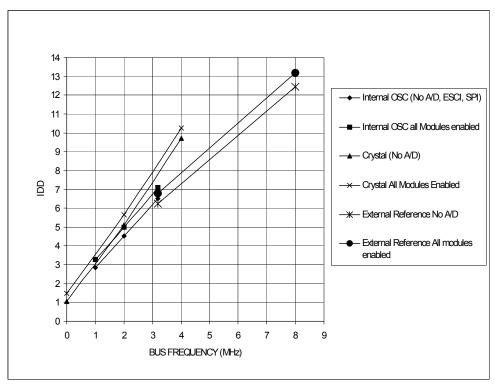

Figure 18-9. Typical 5-Volt Run Current versus Bus Frequency (25•C)

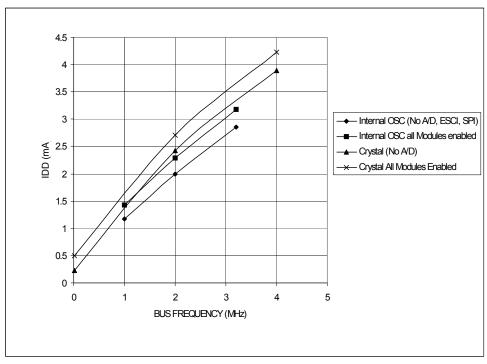

Figure 18-10. Typical 3-Volt Run Current versus Bus Frequency (25•C)

MC68HC908QB8 Data Sheet, Rev. 3

Note: This first clock edge is generated internally, but is not seen at the SPSCK pin.

# a) SPI Master Timing (CPHA = 0)

Note: This last clock edge is generated internally, but is not seen at the SPSCK pin.

# b) SPI Master Timing (CPHA = 1)

Figure 18-11. SPI Master Timing

MC68HC908QB8 Data Sheet, Rev. 3