Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | LVD, POR, PWM                                             |

| Number of I/O              | 13                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | External                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | 16-SOIC                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908qy8vdwe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

This page intentionally blank.

#### **Table of Contents**

# **Enhanced Serial Communications Interface (ESCI) Module**

| 13.1    | Introduction                  | 109 |

|---------|-------------------------------|-----|

| 13.2    | Features                      | 109 |

| 13.3    | Functional Description        | 111 |

| 13.3.1  | Data Format                   |     |

| 13.3.2  | Transmitter                   |     |

| 13.3.2. |                               |     |

| 13.3.2. |                               |     |

| 13.3.2. |                               |     |

| 13.3.2. |                               |     |

| 13.3.2. |                               |     |

| 13.3.3  | Receiver                      |     |

| 13.3.3. |                               |     |

| 13.3.3. |                               |     |

| 13.3.3. | ·                             |     |

| 13.3.3. |                               |     |

| 13.3.3. |                               |     |

| 13.3.3. |                               |     |

| 13.4    | Interrupts                    |     |

| 13.4.1  | Transmitter Interrupts.       |     |

| 13.4.2  | Receiver Interrupts           |     |

| 13.4.3  | Error Interrupts              |     |

| 13.5    | Low-Power Modes               |     |

| 13.5.1  | Wait Mode                     |     |

| 13.5.2  | Stop Mode                     |     |

|         | ·                             |     |

| 13.6    | ESCI During Break Interrupts  |     |

| 13.7    | I/O Signals                   |     |

| 13.7.1  | ESCI Transmit Data (TxD)      |     |

| 13.7.2  | ESCI Receive Data (RxD)       | 121 |

| 13.8    | Registers                     |     |

| 13.8.1  | ESCI Control Register 1       | 122 |

| 13.8.2  | ESCI Control Register 2       | 123 |

| 13.8.3  | ESCI Control Register 3       | 125 |

| 13.8.4  | ESCI Status Register 1        |     |

| 13.8.5  | ESCI Status Register 2        | 129 |

| 13.8.6  | ESCI Data Register            | 129 |

| 13.8.7  | ESCI Baud Rate Register       | 130 |

| 13.8.8  | ESCI Prescaler Register       | 131 |

| 13.9    | ESCI Arbiter                  | 135 |

| 13.9.1  | ESCI Arbiter Control Register |     |

| 13.9.2  | ESCI Arbiter Data Register    |     |

| 13.9.3  | Bit Time Measurement.         |     |

| 13.9.4  | Arbitration Mode              |     |

# Chapter 14 System Integration Module (SIM)

#### MC68HC908QB8 Data Sheet, Rev. 3

| 14.1                 | Introduction                                   | 139 |

|----------------------|------------------------------------------------|-----|

| 14.2                 | RST and IRQ Pins Initialization                | 139 |

| 14.3                 | SIM Bus Clock Control and Generation           | 140 |

| 14.3.1               | Bus Timing                                     |     |

| 14.3.2               | Clock Start-Up from POR                        |     |

| 14.3.3               | Clocks in Stop Mode and Wait Mode              | 141 |

|                      | Reset and System Initialization                | 141 |

| 14.4.1               | External Pin Reset                             |     |

| 14.4.2               | Active Resets from Internal Sources            |     |

| 14.4.2.              |                                                |     |

| 14.4.2.2<br>14.4.2.3 |                                                |     |

| 14.4.2.4             |                                                |     |

| 14.4.2.              |                                                |     |

|                      | SIM Counter                                    |     |

| 14.5.1               | SIM Counter During Power-On Reset              |     |

| 14.5.2               | SIM Counter During Stop Mode Recovery          |     |

| 14.5.3               | SIM Counter and Reset States                   |     |

| 14.6                 | Exception Control                              |     |

| 14.6.1               | Interrupts                                     |     |

| 14.6.1.              | 1 Hardware Interrupts                          | 145 |

| 14.6.1.2             |                                                |     |

| 14.6.2               | Interrupt Status Registers                     |     |

| 14.6.2.              | 15 1 Pro 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |     |

| 14.6.2.2             | 15 1 Pro 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |     |

| 14.6.2.3<br>14.6.3   | Interrupt Status Register 3                    |     |

| 14.6.4               | Break Interrupts                               |     |

| 14.6.5               | Status Flag Protection in Break Mode           |     |

|                      | Low-Power Modes                                |     |

| 14.7.1               | Wait Mode                                      |     |

| 14.7.2               | Stop Mode                                      |     |

| 14.8                 | SIM Registers                                  |     |

|                      | SIM Reset Status Register                      |     |

| 14.8.2               | Break Flag Control Register                    |     |

|                      |                                                |     |

|                      | Chapter 15                                     |     |

|                      | Serial Peripheral Interface (SPI) Module       |     |

| 15.1                 | Introduction                                   | 155 |

| 15.2                 | Features                                       | 155 |

|                      | Functional Description                         |     |

| 15.3.1               | Master Mode                                    |     |

| 15.3.2               | Slave Mode                                     |     |

| 15.3.3               | Transmission Formats                           |     |

| 15.3.3.              |                                                |     |

| 15.3.3.2             | 2 Transmission Format When CPHA = 0            | 159 |

|                      |                                                |     |

MC68HC908QB8 Data Sheet, Rev. 3

#### 2.6.3 FLASH Mass Erase Operation

Use the following procedure to erase the entire FLASH memory to read as a 1:

- 1. Set both the ERASE bit and the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH address<sup>(1)</sup> within the FLASH memory address range.

- Wait for a time, t<sub>NVS</sub>.

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>MErase</sub>.

- 7. Clear the ERASE and MASS bits.

#### NOTE

Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF).

- 8. Wait for a time, t<sub>NVHI</sub>.

- 9. Clear the HVEN bit.

- 10. After time, t<sub>BCV</sub>, the memory can be accessed in read mode again.

#### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order as shown, other unrelated operations may occur between the steps.

#### **CAUTION**

A mass erase will erase the internal oscillator trim value at \$FFC0.

#### 2.6.4 FLASH Program Operation

Programming of the FLASH memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0, or \$XXE0. Use the following step-by-step procedure to program a row of FLASH memory

Figure 2-4 shows a flowchart of the programming algorithm.

#### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte which is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH location within the address range desired.

- Wait for a time, t<sub>NVS</sub>.

- 5. Set the HVEN bit.

MC68HC908QB8 Data Sheet, Rev. 3

When in monitor mode, with security sequence failed (see 17.3.2 Security), write to the FLASH block protect register instead of any FLASH address.

break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

# 3.7 I/O Signals

The ADC10 module shares its pins with general-purpose input/output (I/O) port pins. See Figure 3-1 for port location of these shared pins. The ADC10 on this MCU uses V<sub>DD</sub> and V<sub>SS</sub> as its supply and reference pins. This MCU does not have an external trigger source.

#### 3.7.1 ADC10 Analog Power Pin (V<sub>DDA</sub>)

The ADC10 analog portion uses  $V_{DDA}$  as its power pin. In some packages,  $V_{DDA}$  is connected internally to  $V_{DD}$ . If externally available, connect the  $V_{DDA}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDA}$  for good results.

#### NOTE

If externally available, route  $V_{DDA}$  carefully for maximum noise immunity and place bypass capacitors as near as possible to the package.

#### 3.7.2 ADC10 Analog Ground Pin (V<sub>SSA</sub>)

The ADC10 analog portion uses  $V_{SSA}$  as its ground pin. In some packages,  $V_{SSA}$  is connected internally to  $V_{SS}$ . If externally available, connect the  $V_{SSA}$  pin to the same voltage potential as  $V_{SS}$ .

In cases where separate power supplies are used for analog and digital power, the ground connection between these supplies should be at the  $V_{SSA}$  pin. This should be the only ground connection between these supplies if possible. The  $V_{SSA}$  pin makes a good single point ground location.

# 3.7.3 ADC10 Voltage Reference High Pin (V<sub>REFH</sub>)

$V_{REFH}$  is the power supply for setting the high-reference voltage for the converter. In some packages,  $V_{REFH}$  is connected internally to  $V_{DDA}$ . If externally available,  $V_{REFH}$  may be connected to the same potential as  $V_{DDA}$ , or may be driven by an external source that is between the minimum  $V_{DDA}$  spec and the  $V_{DDA}$  potential ( $V_{REFH}$  must never exceed  $V_{DDA}$ ).

#### NOTE

Route V<sub>REFH</sub> carefully for maximum noise immunity and place bypass capacitors as near as possible to the package.

AC current in the form of current spikes required to supply charge to the capacitor array at each successive approximation step is drawn through the  $V_{REFH}$  and  $V_{REFL}$  loop. The best external component to meet this current demand is a 0.1  $\mu$ F capacitor with good high frequency characteristics. This capacitor is connected between  $V_{REFH}$  and  $V_{REFL}$  and must be placed as close as possible to the package pins. Resistance in the path is not recommended because the current will cause a voltage drop which could result in conversion errors. Inductance in this path must be minimum (parasitic only).

# 3.7.4 ADC10 Voltage Reference Low Pin (V<sub>REFL</sub>)

$V_{REFL}$  is the power supply for setting the low-reference voltage for the converter. In some packages,  $V_{REFL}$  is connected internally to  $V_{SSA}$ . If externally available, connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSA}$ . There will be a brief current associated with  $V_{REFL}$  when the sampling capacitor is

**Auto Wakeup Module (AWU)**

## 4.3 Functional Description

The function of the auto wakeup logic is to generate periodic wakeup requests to bring the microcontroller unit (MCU) out of stop mode. The wakeup requests are treated as regular keyboard interrupt requests, with the difference that instead of a pin, the interrupt signal is generated by an internal logic.

Entering stop mode will enable the auto wakeup generation logic. Writing the AWUIE bit in the keyboard interrupt enable register enables or disables the auto wakeup interrupt input (see Figure 4-1). A 1 applied to the AWUIREQ input with auto wakeup interrupt request enabled, latches an auto wakeup interrupt request.

Auto wakeup latch, AWUL, can be read directly from the bit 6 position of port A data register (PTA). This is a read-only bit which is occupying an empty bit position on PTA. No PTA associated registers, such as PTA6 data direction or PTA6 pullup exist for this bit.

There are two clock sources for the AWU. An internal RC oscillator (INTRCOSC, exclusive for the auto wakeup feature) drives the wakeup request generator provided the OSCENINSTOP bit in the CONFIG2 register Figure 4-1 is cleared. More accurate wakeup periods are possible using the BUSCLKX2 signal (from the oscillator module) which is selected by setting OSCENINSTOP.

Once the overflow count is reached in the generator counter, a wakeup request, AWUIREQ, is latched and sent to the KBI logic. See Figure 4-1.

Wakeup interrupt requests will only be serviced if the associated interrupt enable bit, AWUIE, in KBIER is set. The AWU shares the keyboard interrupt vector.

The overflow count can be selected from two options defined by the COPRS bit in CONFIG1. This bit was "borrowed" from the computer operating properly (COP) using the fact that the COP feature is idle (no MCU clock available) in stop mode. COPRS = 1 selects the short wakeup period while COPRS = 0 selects the long wakeup period.

The auto wakeup RC oscillator is highly dependent on operating voltage and temperature. This feature is not recommended for use as a time-keeping function.

The wakeup request is latched to allow the interrupt source identification. The latched value, AWUL, can be read directly from the bit 6 position of PTA data register. This is a read-only bit which is occupying an empty bit position on PTA. No PTA associated registers, such as PTA6 data, PTA6 direction, and PTA6 pullup exist for this bit. The latch can be cleared by writing to the ACKK bit in the KBSCR register. Reset also clears the latch. AWUIE bit in KBI interrupt enable register (see Figure 4-1) has no effect on AWUL reading.

The AWU oscillator and counters are inactive in normal operating mode and become active only upon entering stop mode.

# 4.4 Interrupts

The AWU can generate an interrupt requests:.

AWU Latch (AWUL) — The AWUL bit is set when the AWU counter overflows. The auto wakeup interrupt mask bit, AWUIE, is used to enable or disable AWU interrupt requests.

The AWU shares its interrupt with the KBI vector.

#### 4.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 4.5.1 Wait Mode

The AWU module remains inactive in wait mode.

#### 4.5.2 Stop Mode

When the AWU module is enabled (AWUIE = 1 in the keyboard interrupt enable register) it is activated automatically upon entering stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode. The AWU counters start from 0 each time stop mode is entered.

## 4.6 Registers

The AWU shares registers with the keyboard interrupt (KBI) module, the port A I/O module and configuration register 2. The following I/O registers control and monitor operation of the AWU:

- Port A data register (PTA)

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

- Configuration register 1 (CONFIG1)

- Configuration register 2 (CONFIG2)

#### 4.6.1 Port A I/O Register

The port A data register (PTA) contains a data latch for the state of the AWU interrupt request, in addition to the data latches for port A.

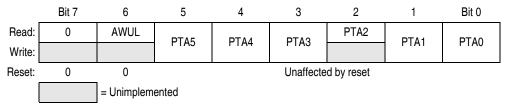

Figure 4-2. Port A Data Register (PTA)

#### AWUL — Auto Wakeup Latch

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally. There is no PTA6 port or any of the associated bits such as PTA6 data direction or pullup bits.

- 1 = Auto wakeup interrupt request is pending

- 0 = Auto wakeup interrupt request is not pending

#### NOTE

PTA5-PTA0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 12.2.1 Port A Data Register.

MC68HC908QB8 Data Sheet, Rev. 3

#### **Auto Wakeup Module (AWU)**

# COPRS (In Stop Mode) — Auto Wakeup Period Selection Bit, depends on OSCSTOPEN in CONFIG2 and bus clock source (BUSCLKX2).

- $1 = \text{Auto wakeup short cycle} = 512 \times (INTRCOSC or BUSCLKX2)$

- $0 = \text{Auto wakeup long cycle} = 16,384 \times (INTRCOSC or BUSCLKX2)$

#### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 BUSCLKX4 cycles instead of a 4096 BUSCLKX4 cycle delay.

- 1 = Stop mode recovery after 32 BUSCLKX4 cycles

- 0 = Stop mode recovery after 4096 BUSCLKX4 cycles

#### NOTE

LVISTOP, LVIRST, LVIPWRD, LVITRIP and COPD bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see Chapter 5 Configuration Register (CONFIG)

# Table 7-1. Instruction Set Summary (Sheet 2 of 6)

| Source                                                                                                | Operation                                         | Description                                                                                                                                                                                                                                                                                                                                                           |   | Effect on CCR |   |   |   | Address Mode |                                                                                              | Opcode                                       |                                                                      | les                             |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------|---|---|---|--------------|----------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------|---------------------------------|

| Form                                                                                                  | Орогиион                                          | Becomplien                                                                                                                                                                                                                                                                                                                                                            | ٧ | Н             | I | N | Z | С            | Add<br>Mod                                                                                   | odo                                          | Оре                                                                  | Cycles                          |

| BHS rel                                                                                               | Branch if Higher or Same (Same as BCC)            | $PC \leftarrow (PC) + 2 + rel? (C) = 0$                                                                                                                                                                                                                                                                                                                               | _ | -             | - | - | _ | -            | REL                                                                                          | 24                                           | rr                                                                   | 3                               |

| BIH rel                                                                                               | Branch if IRQ Pin High                            | PC ← (PC) + 2 + <i>rel</i> ? IRQ = 1                                                                                                                                                                                                                                                                                                                                  | _ | -             | _ | - | _ | _            | REL                                                                                          | 2F                                           | rr                                                                   | 3                               |

| BIL rel                                                                                               | Branch if IRQ Pin Low                             | PC ← (PC) + 2 + rel? <del>IRQ</del> = 0 -                                                                                                                                                                                                                                                                                                                             |   |               |   | - | - | _            | REL                                                                                          | 2E                                           | rr                                                                   | 3                               |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT,X<br>BIT opr,SP<br>BIT opr,SP         | Bit Test                                          | (A) & (M)                                                                                                                                                                                                                                                                                                                                                             | 0 | _             | 1 | 1 | ‡ | _            | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9ED5     | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff                      | 2 3 4 4 3 2 4 5                 |

| BLE opr                                                                                               | Branch if Less Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (Z)   (N \oplus V) = 1$                                                                                                                                                                                                                                                                                                                | _ | -             | - | - | - | -            | REL                                                                                          | 93                                           | rr                                                                   | 3                               |

| BLO rel                                                                                               | Branch if Lower (Same as BCS)                     | $PC \leftarrow (PC) + 2 + rel? (C) = 1$                                                                                                                                                                                                                                                                                                                               | _ | -             | _ | - | _ | _            | REL                                                                                          | 25                                           | rr                                                                   | 3                               |

| BLS rel                                                                                               | Branch if Lower or Same                           | $PC \leftarrow (PC) + 2 + rel? (C) \mid (Z) = 1$                                                                                                                                                                                                                                                                                                                      | _ | -             | _ | - | - | -            | REL                                                                                          | 23                                           | rr                                                                   | 3                               |

| BLT opr                                                                                               | Branch if Less Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 1$                                                                                                                                                                                                                                                                                                                      | - | -             | - | - | - | -            | REL                                                                                          | 91                                           | rr                                                                   | 3                               |

| BMC rel                                                                                               | Branch if Interrupt Mask Clear                    | $PC \leftarrow (PC) + 2 + rel? (I) = 0$                                                                                                                                                                                                                                                                                                                               | _ | -             | - | - | - | -            | REL                                                                                          | 2C                                           | rr                                                                   | 3                               |

| BMI rel                                                                                               | Branch if Minus                                   | PC ← (PC) + 2 + rel? (N) = 1                                                                                                                                                                                                                                                                                                                                          | _ | -             | - | - | - | -            | REL                                                                                          | 2B                                           | rr                                                                   | 3                               |

| BMS rel                                                                                               | Branch if Interrupt Mask Set                      | PC ← (PC) + 2 + <i>rel</i> ? (I) = 1                                                                                                                                                                                                                                                                                                                                  | - | -             | - | - | - | -            | REL                                                                                          | 2D                                           | rr                                                                   | 3                               |

| BNE rel                                                                                               | Branch if Not Equal                               | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                                                                                                                                                                                                                                                                                                                               | _ | -             | - | - | - | _            | REL                                                                                          | 26                                           | rr                                                                   | 3                               |

| BPL rel                                                                                               | Branch if Plus                                    | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                                                                                                                                                                                                                                                                                                                               | _ | -             | - | - | - | _            | REL                                                                                          | 2A                                           | rr                                                                   | 3                               |

| BRA rel                                                                                               | Branch Always                                     | PC ← (PC) + 2 + <i>rel</i>                                                                                                                                                                                                                                                                                                                                            | _ | -             | - | - | - | -            | REL                                                                                          | 20                                           | rr                                                                   | 3                               |

| BRCLR n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Clear                 | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                                                                                                                                                                                                                                                                                                                                 | _ | _             | _ | _ | _ | ‡            | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555                        |

| BRN rel                                                                                               | Branch Never                                      | PC ← (PC) + 2                                                                                                                                                                                                                                                                                                                                                         | _ | _             | _ | _ | _ | _            | REL                                                                                          | 21                                           | rr                                                                   | 3                               |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set                   | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                                                                                                                                                                                                                                                                                                                                 | _ | _             | _ | _ | _ | 1            | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5 5 5 5 5 5 5 5                 |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M                             | Mn ← 1                                                                                                                                                                                                                                                                                                                                                                | _ | _             | _ | _ | _ | _            | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                         | 4<br>4<br>4<br>4<br>4<br>4<br>4 |

| BSR rel                                                                                               | Branch to Subroutine                              | $\begin{array}{c} PC \leftarrow (PC) + 2;  push  (PCL) \\ SP \leftarrow (SP) - 1;  push  (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                                                            | _ | _             | _ | _ | _ | _            | REL                                                                                          | AD                                           | rr                                                                   | 4                               |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal                       | $\begin{array}{l} PC \leftarrow (PC) + 3 + rel \ ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \ ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \ ? \ (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel \ ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel \ ? \ (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel \ ? \ (A) - (M) = \$00 \end{array}$ | _ | _             | - | _ | - | -            | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 61<br>71                                     | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                      | 5<br>4<br>4<br>5<br>4<br>6      |

| CLC                                                                                                   | Clear Carry Bit                                   | C ← 0                                                                                                                                                                                                                                                                                                                                                                 | _ | -             | - | - | - | 0            | INH                                                                                          | 98                                           |                                                                      | 1                               |

| CLI                                                                                                   | Clear Interrupt Mask                              | I ← 0                                                                                                                                                                                                                                                                                                                                                                 | _ | -             | 0 | - | _ | _            | INH                                                                                          | 9A                                           |                                                                      | 2                               |

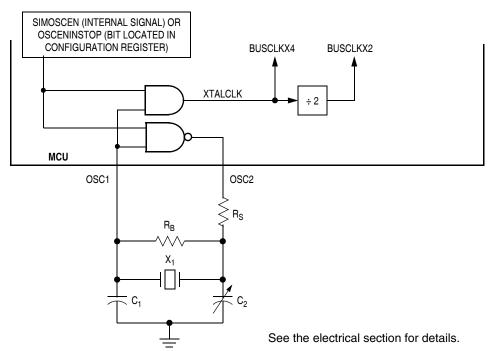

#### 11.3.4 XTAL Oscillator

The XTAL oscillator circuit is designed for use with an external crystal or ceramic resonator to provide an accurate clock source. In this configuration, the OSC2 pin is dedicated to the external crystal circuit. The OSC2EN bit has no effect when this clock mode is selected.

In its typical configuration, the XTAL oscillator is connected in a Pierce oscillator configuration, as shown in Figure 11-2. This figure shows only the logical representation of the internal components and may not represent actual circuitry.

The oscillator configuration uses five components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>B</sub>

- Series resistor, R<sub>s</sub> (optional)

#### NOTE

The series resistor ( $R_s$ ) is included in the diagram to follow strict Pierce oscillator guidelines and may not be required for all ranges of operation, especially with high frequency crystals. Refer to the oscillator characteristics table in the Electricals section for more information.

Figure 11-2. XTAL Oscillator External Connections

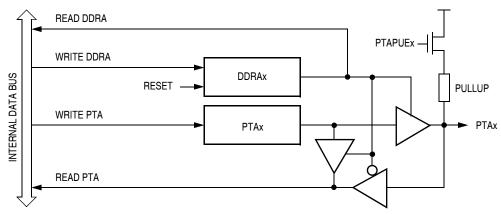

Figure 12-3. Port A I/O Circuit NOTE

Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading PTA reads the PTAx data latch. When DDRAx is a 0, reading PTA reads the logic level on the PTAx pin. The data latch can always be written, regardless of the state of its data direction bit.

#### 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each of the port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

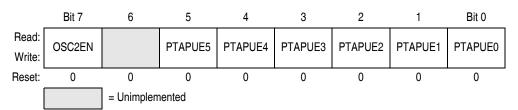

Figure 12-4. Port A Input Pullup Enable Register (PTAPUE)

#### OSC2EN — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

- 1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

- 0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

#### PTAPUE[5:0] — Port A Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port A pins.

- 1 = Corresponding port A pin configured to have internal pullup if its DDRA bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port A pin regardless of the state of its DDRA bit

Input/Output Ports (PORTS)

#### 12.3.3 Port B Input Pullup Enable Register

The port B input pullup enable register (PTBPUE) contains a software configurable pullup device for each of the eight port B pins. Each bit is individually configurable and requires the corresponding data direction register, DDRBx, be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRBx bit is configured as output.

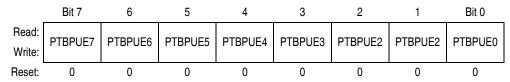

Figure 12-8. Port B Input Pullup Enable Register (PTBPUE)

#### PTBPUE[7:0] — Port B Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port B pins

- 1 = Corresponding port B pin configured to have internal pull if its DDRB bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port B pin regardless of the state of its DDRB bit.

#### 12.3.4 Port B Summary Table

Table 12-2 summarizes the operation of the port A pins when used as a general-purpose input/output pins.

| rabie | 12-2. | Port | ВР | ın F | unctions |  |

|-------|-------|------|----|------|----------|--|

|       |       |      |    |      |          |  |

| DDRB | РТВ              | I/O Pin                    | Accesses to DDRB Accesses |      | ccesses to PTB           |

|------|------------------|----------------------------|---------------------------|------|--------------------------|

| Bit  | Bit              | Mode                       | Read/Write                | Read | Write                    |

| 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRB7-DDRB0               | Pin  | PTB7-PTB0 <sup>(3)</sup> |

| 1    | Х                | Output                     | DDRB7-DDRB0               | Pin  | PTB7-PTB0                |

- 1. X = don't care

- 2. Hi-Z = high impedance

- 3. Writing affects data register, but does not affect the input.

#### **Enhanced Serial Communications Interface (ESCI) Module**

#### **Slow Data Tolerance**

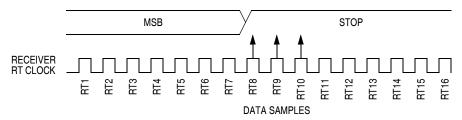

Figure 13-7 shows how much a slow received character can be misaligned without causing a noise error or a framing error. The slow stop bit begins at RT8 instead of RT1 but arrives in time for the stop bit data samples at RT8, RT9, and RT10.

Figure 13-7. Slow Data

For an 8-bit character, data sampling of the stop bit takes the receiver 9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 13-7, the receiver counts 154 RT cycles at the point when the count of the transmitting device is 9 bit times  $\times$  16 RT cycles + 3 RT cycles = 147 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 8-bit character with no errors is:

$$\left| \frac{154 - 147}{154} \right| \times 100 = 4.54\%$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in Figure 13-7, the receiver counts 170 RT cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RT cycles + 3 RT cycles = 163 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 9-bit character with no errors is:

$$\left| \frac{170 - 163}{170} \right| \times 100 = 4.12\%$$

#### **Fast Data Tolerance**

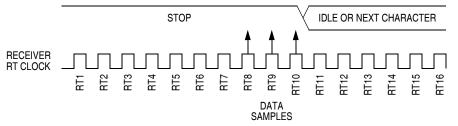

Figure 13-8 shows how much a fast received character can be misaligned without causing a noise error or a framing error. The fast stop bit ends at RT10 instead of RT16 but is still there for the stop bit data samples at RT8, RT9, and RT10.

Figure 13-8. Fast Data

#### Serial Peripheral Interface (SPI) Module

#### 15.3.5 Resetting the SPI

Any system reset completely resets the SPI. Partial resets occur whenever the SPI enable bit (SPE) is 0. Whenever SPE is 0, the following occurs:

- The SPTE flag is set.

- Any transmission currently in progress is aborted.

- The shift register is cleared.

- The SPI state counter is cleared, making it ready for a new complete transmission.

- All the SPI pins revert back to being general-purpose I/O.

These items are reset only by a system reset:

- All control bits in the SPCR register

- All control bits in the SPSCR register (MODFEN, ERRIE, SPR1, and SPR0)

- The status flags SPRF, OVRF, and MODF

By not resetting the control bits when SPE is low, the user can clear SPE between transmissions without having to set all control bits again when SPE is set high for the next transmission.

By not resetting the SPRF, OVRF, and MODF flags, the user can still service these interrupts after the SPI has been disabled. The user can disable the SPI by writing 0 to the SPE bit. The SPI can also be disabled by a mode fault occurring in an SPI that was configured as a master with the MODFEN bit set.

#### 15.3.6 Error Conditions

The following flags signal SPI error conditions:

- Overflow (OVRF) Failing to read the SPI data register before the next full byte enters the shift

register sets the OVRF bit. The new byte does not transfer to the receive data register, and the

unread byte still can be read. OVRF is in the SPI status and control register.

- Mode fault error (MODF) The MODF bit indicates that the voltage on the slave select pin (SS) is inconsistent with the mode of the SPI. MODF is in the SPI status and control register.

#### 15.3.6.1 Overflow Error

The overflow flag (OVRF) becomes set if the receive data register still has unread data from a previous transmission when the capture strobe of bit 1 of the next transmission occurs. The bit 1 capture strobe occurs in the middle of SPSCK cycle 7 (see Figure 15-4 and Figure 15-6.) If an overflow occurs, all data received after the overflow and before the OVRF bit is cleared does not transfer to the receive data register and does not set the SPI receiver full bit (SPRF). The unread data that transferred to the receive data register before the overflow occurred can still be read. Therefore, an overflow error always indicates the loss of data. Clear the overflow flag by reading the SPI status and control register and then reading the SPI data register.

OVRF generates a receiver/error interrupt request if the error interrupt enable bit (ERRIE) is also set. The SPRF, MODF, and OVRF interrupts share the same interrupt vector (see Figure 15-11.) It is not possible to enable MODF or OVRF individually to generate a receiver/error interrupt request. However, leaving MODFEN low prevents MODF from being set.

If the SPRF interrupt is enabled and the OVRF interrupt is not, watch for an overflow condition. Figure 15-9 shows how it is possible to miss an overflow. The first part of Figure 15-9 shows how it is possible to read the SPSCR and SPDR to clear the SPRF without problems. However, as illustrated by the second transmission example, the OVRF bit can be set in between the time that SPSCR and SPDR are read.

#### **MODF** — Mode Fault Bit

This clearable, read-only flag is set in a slave SPI if the  $\overline{SS}$  pin goes high during a transmission with MODFEN set. In a master SPI, the MODF flag is set if the  $\overline{SS}$  pin goes low at any time with the MODFEN bit set. Clear MODF by reading the SPI status and control register (SPSCR) with MODF set and then writing to the SPI control register (SPCR).

- $1 = \overline{SS}$  pin at inappropriate logic level

- $0 = \overline{SS}$  pin at appropriate logic level

#### SPTE — SPI Transmitter Empty Bit

This clearable, read-only flag is set each time the transmit data register transfers a byte into the shift register. SPTE generates an SPTE interrupt request if the SPTIE bit in the SPI control register is also set.

#### NOTE

Do not write to the SPI data register unless SPTE is high.

During an SPTE interrupt, user software can clear SPTE by writing to the transmit data register.

- 1 = Transmit data register empty

- 0 = Transmit data register not empty

#### **MODFEN** — Mode Fault Enable Bit

This read/write bit, when set, allows the MODF flag to be set. If the MODF flag is set, clearing MODFEN does not clear the MODF flag. If the SPI is enabled as a master and the MODFEN bit is 0, then the SS pin is available as a general-purpose I/O.

If the MODFEN bit is 1, then this pin is not available as a general-purpose I/O. When the SPI is enabled as a slave, the  $\overline{SS}$  pin is not available as a general-purpose I/O regardless of the value of MODFEN. See 15.7.4 SS (Slave Select).

If the MODFEN bit is 0, the level of the  $\overline{SS}$  pin does not affect the operation of an enabled SPI configured as a master. For an enabled SPI configured as a slave, having MODFEN low only prevents the MODF flag from being set. It does not affect any other part of SPI operation. See 15.3.6.2 Mode Fault Error.

#### SPR1 and SPR0 — SPI Baud Rate Select Bits

In master mode, these read/write bits select one of four baud rates as shown in Table 15-3. SPR1 and SPR0 have no effect in slave mode.

Table 15-3. SPI Master Baud Rate Selection

| SPR1 and SPR0 | Baud Rate Divisor (BD) |

|---------------|------------------------|

| 00            | 2                      |

| 01            | 8                      |

| 10            | 32                     |

| 11            | 128                    |

Use this formula to calculate the SPI baud rate:

Baud rate =

$$\frac{BUSCLK}{BD}$$

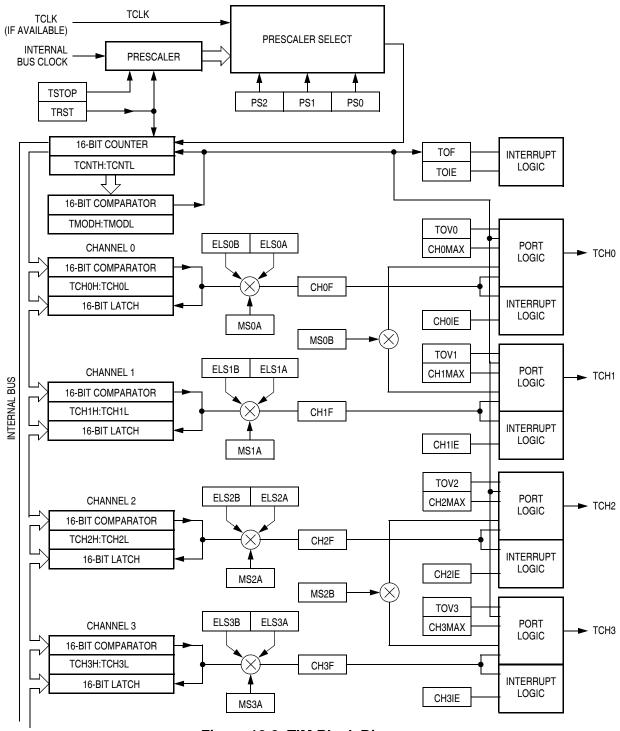

Figure 16-2. TIM Block Diagram

#### 16.3.3 Output Compare

With the output compare function, the TIM can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare

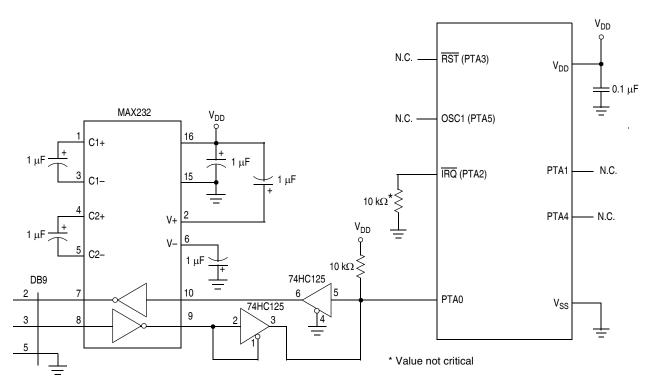

Figure 17-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 9600 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (3.2 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 17-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- IRQ =  $V_{TST}$

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{DD}$  (this can be implemented through the internal  $\overline{IRQ}$  pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- IRQ = V<sub>SS</sub> (internal oscillator is selected, no external clock required)

The rising edge of the internal  $\overline{RST}$  signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

Once out of reset, the MCU waits for the host to send eight security bytes (see 17.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive 0s) to the host, indicating that it is ready to receive a command.

MC68HC908QB8 Data Sheet, Rev. 3

#### 17.3.1.2 Forced Monitor Mode

If entering monitor mode without high voltage on  $\overline{IRQ}$ , then startup port pin requirements and conditions, (PTA1/PTA4) are not in effect. This is to reduce circuit requirements when performing in-circuit programming.

#### NOTE

If the reset vector is blank and monitor mode is entered, the chip will see an additional reset cycle after the initial power-on reset (POR). Once the reset vector has been programmed, the traditional method of applying a voltage,  $V_{TST}$ , to  $\overline{IRQ}$  must be used to enter monitor mode.

If monitor mode was entered as a result of the reset vector being blank, the COP is always disabled regardless of the state of  $\overline{IRQ}$ .

If the voltage applied to the  $\overline{IRQ}$  is less than  $V_{TST}$ , the MCU will come out of reset in user mode. Internal circuitry monitors the reset vector fetches and will assert an internal reset if it detects that the reset vectors are erased (\$FF). When the MCU comes out of reset, it is forced into monitor mode without requiring high voltage on the  $\overline{IRQ}$  pin. Once out of reset, the monitor code is initially executing with the internal clock at its default frequency.

If  $\overline{\text{IRQ}}$  is held high, all pins will default to regular input port functions except for PTA0 and PTA5 which will operate as a serial communication port and OSC1 input respectively (refer to Figure 17-11). That will allow the clock to be driven from an external source through OSC1 pin.

If  $\overline{\text{IRQ}}$  is held low, all pins will default to regular input port function except for PTA0 which will operate as serial communication port. Refer to Figure 17-12.

Regardless of the state of the  $\overline{IRQ}$  pin, it will not function as a port input pin in monitor mode. Bit 2 of the Port A data register will always read 0. The BIH and BIL instructions will behave as if the  $\overline{IRQ}$  pin is enabled, regardless of the settings in the configuration register. See Chapter 5 Configuration Register (CONFIG).

The COP module is disabled in forced monitor mode. Any reset other than a power-on reset (POR) will automatically force the MCU to come back to the forced monitor mode.

#### 17.3.1.3 Monitor Vectors

In monitor mode, the MCU uses different vectors for reset, SWI (software interrupt), and break interrupt than those for user mode. The alternate vectors are in the \$FE page instead of the \$FF page and allow code execution from the internal monitor firmware instead of user code.

#### NOTE

Exiting monitor mode after it has been initiated by having a blank reset vector requires a power-on reset (POR). Pulling RST (when RST pin available) low will not exit monitor mode in this situation.

Table 17-2 summarizes the differences between user mode and monitor mode regarding vectors.

|         |                      | Functions           |                      |                     |                    |                   |  |  |  |  |

|---------|----------------------|---------------------|----------------------|---------------------|--------------------|-------------------|--|--|--|--|

| Modes   | Reset<br>Vector High | Reset<br>Vector Low | Break<br>Vector High | Break<br>Vector Low | SWI<br>Vector High | SWI<br>Vector Low |  |  |  |  |

| User    | \$FFFE               | \$FFFF              | \$FFFC               | \$FFFD              | \$FFFC             | \$FFFD            |  |  |  |  |

| Monitor | \$FEFE               | \$FEFF              | \$FEFC               | \$FEFD              | \$FEFC             | \$FEFD            |  |  |  |  |

Table 17-2. Mode Difference

Freescale Semiconductor 201

MC68HC908QB8 Data Sheet, Rev. 3

#### **Electrical Specifications**

| Characteristic         | Conditions  | Symbol            | Min  | Typ <sup>(1)</sup> | Max  | Unit | Comment                    |

|------------------------|-------------|-------------------|------|--------------------|------|------|----------------------------|

| Integral non-linearity | 10-bit mode | INL               | 0    | ±0.5               | _    | LSB  |                            |

| integral non-linearity | 8-bit mode  | IINL              | 0    | ±0.3               |      |      |                            |

| Zero-scale error       | 10-bit mode | _                 | 0    | ±0.5               | _    | LSB  |                            |

| Zero-scale error       | 8-bit mode  | - E <sub>ZS</sub> | 0    | ±0.3               | _    | LOD  | $V_{ADIN} = V_{SS}$        |

| Full-scale error       | 10-bit mode | Е.                | 0    | ±0.5               | _    | LSB  | V - V                      |

| ruii-scale erroi       | 8-bit mode  | - E <sub>FS</sub> | 0    | ±0.3               | _    | LOD  | $V_{ADIN} = V_{DD}$        |

| Quantization error     | 10-bit mode | - E <sub>Q</sub>  | _    | _                  | ±0.5 | LSB  | 8-bit mode is              |

| Quantization enoi      | 8-bit mode  | LQ                | _    | _                  | ±0.5 | LOD  | not truncated              |

| Input lookage error    | 10-bit mode | _                 | 0    | ±0.2               | ±5   | LSB  | Pad leakage <sup>(5)</sup> |

| Input leakage error    | 8-bit mode  | E <sub>IL</sub>   | 0    | ±0.1               | ±1.2 | LOD  | * R <sub>AS</sub>          |

| Bandgap voltage (3)(6) |             | $V_{BG}$          | 1.17 | 1.245              | 1.32 | V    |                            |

- Typical values assume V<sub>DD</sub> = 5.0 V, temperature = 25•C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

Incremental I<sub>DD</sub> added to MCU mode current.

- 3. Values are based on characterization results, not tested in production.

- 4. Reference the ADC module specification for more information on calculating conversion times.

- 5. Based on typical input pad leakage current.

- 6. LVI must be enabled, (LVIPWRD = 0, in CONFIG1). Voltage input to ADCH4:0 = \$1A, an ADC conversion on this channel allows user to determine supply voltage.

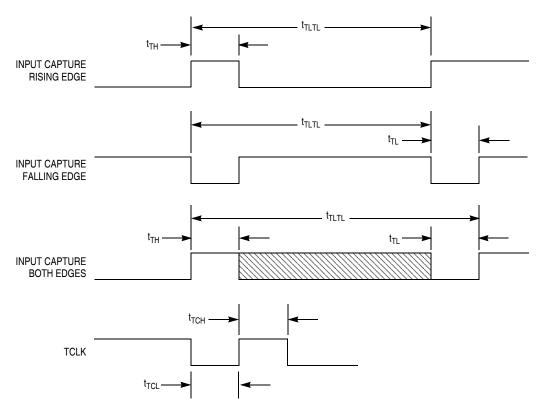

# 18.16 Timer Interface Module Characteristics

| Characteristic                                 | Symbol                              | Min                  | Max | Unit             |

|------------------------------------------------|-------------------------------------|----------------------|-----|------------------|

| Timer input capture pulse width <sup>(1)</sup> | t <sub>TH,</sub> t <sub>TL</sub>    | 2                    | _   | t <sub>cyc</sub> |

| Timer input capture period                     | t <sub>TLTL</sub>                   | Note <sup>(2)</sup>  | _   | t <sub>cyc</sub> |

| Timer input clock pulse width <sup>(1)</sup>   | t <sub>TCL</sub> , t <sub>TCH</sub> | t <sub>cyc</sub> + 5 | _   | ns               |

- 1. Values are based on characterization results, not tested in production.

- 2. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 18-13. Timer Input Timing