Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcl908qb8dte |

|----------------------------|----------------------------------------------------------------------|

| Supplier Device Package    | 16-TSSOP                                                             |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                      |

| Mounting Type              | Surface Mount                                                        |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                      |

| Oscillator Type            | Internal                                                             |

| Data Converters            | A/D 10x10b                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| RAM Size                   | 256 x 8                                                              |

| EEPROM Size                | -                                                                    |

| Program Memory Type        | FLASH                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Number of I/O              | 13                                                                   |

| Peripherals                | LVD, POR, PWM                                                        |

| Connectivity               | SCI, SPI                                                             |

| Speed                      | 8MHz                                                                 |

| Core Size                  | 8-Bit                                                                |

| Core Processor             | HC08                                                                 |

| Product Status             | Obsolete                                                             |

| Details                    |                                                                      |

| 6.1            | Introduction                       | 61 |

|----------------|------------------------------------|----|

| 6.2            | Functional Description             | 61 |

| 6.3            | I/O Signals                        | 62 |

| 6.3.1          | BUSCLKX4                           |    |

| 6.3.2          | STOP Instruction                   |    |

| 6.3.3          | COPCTL Write                       |    |

| 6.3.4          | Power-On Reset.                    |    |

| 6.3.5<br>6.3.6 | Internal Reset                     |    |

| 6.3.7          | COPRS (COP Rate Select)            |    |

| 6.4            | Interrupts                         |    |

| 6.5            | Monitor Mode                       |    |

| 6.6            | Low-Power Modes                    |    |

| 6.6.1          | Wait Mode                          |    |

| 6.6.2          | Stop Mode                          |    |

| 6.7            | COP Module During Break Mode       |    |

| 6.8            | Register                           |    |

| 0.0            | riegistei                          | 00 |

|                | Chapter 7                          |    |

|                | Central Processor Unit (CPU)       |    |

| 7.1            | Introduction                       | 65 |

| 7.2            | Features                           | 65 |

| 7.3            | CPU Registers                      |    |

| 7.3.1          | Accumulator                        |    |

| 7.3.2          | Index Register                     |    |

| 7.3.3          | Stack Pointer                      |    |

| 7.3.4          | Program Counter                    |    |

| 7.3.5          | Condition Code Register            |    |

| 7.4            | Arithmetic/Logic Unit (ALU)        |    |

| 7.5            | Low-Power Modes                    |    |

| 7.5.1          | Wait Mode                          |    |

| 7.5.2          | Stop Mode                          |    |

| 7.6            | CPU During Break Interrupts        |    |

| 7.7            | Instruction Set Summary            |    |

| 7.8            | Opcode Map                         | 75 |

|                | Ohamtan 0                          |    |

|                | Chapter 8 External Interrupt (IRQ) |    |

| 8.1            | Introduction                       | 77 |

| 8.2            | Features                           |    |

| 8.3            |                                    |    |

| 8.3.1          | Functional Description             |    |

| 8.3.2          | MODE = 0                           |    |

| 8.4            | Interrupts                         |    |

| J.7            | monupio                            | 00 |

#### Memory

- 6. Wait for a time, t<sub>PGS</sub>.

- 7. Write data to the FLASH address being programmed<sup>(1)</sup>.

- 8. Wait for time, t<sub>PROG</sub>.

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM bit (1).

- 11. Wait for time, t<sub>NVH</sub>.

- 12. Clear the HVEN bit.

- 13. After time, t<sub>RCV</sub>, the memory can be accessed in read mode again.

## NOTE

The COP register at location \$FFFF should not be written between steps 5-12, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is programmed.

## NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum, see 18.17 Memory Characteristics.

## 2.6.5 FLASH Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

## **NOTE**

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0 s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory. The address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than \$FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF). The FLBPR itself can be erased or programmed only with an external voltage, V<sub>TST</sub>, present on the  $\overline{IRQ}$  pin. This voltage also allows entry from reset into the monitor mode.

MC68HC908QB8 Data Sheet, Rev. 3

<sup>1.</sup> The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

## Analog-to-Digital Converter (ADC10) Module

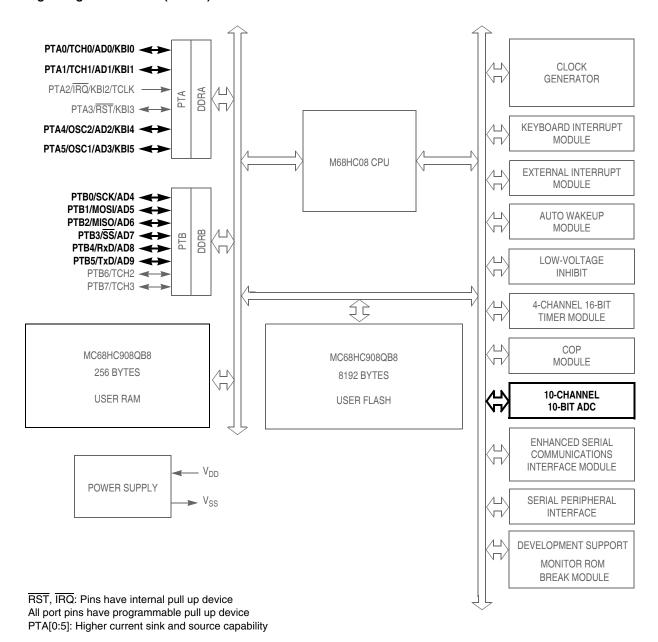

Figure 3-1. Block Diagram Highlighting ADC10 Block and Pins

#### Analog-to-Digital Converter (ADC10) Module

charging. If externally available, connect the  $V_{REFL}$  pin to the same potential as  $V_{SSA}$  at the single point ground location.

## 3.7.5 ADC10 Channel Pins (ADn)

The ADC10 has multiple input channels. Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. 0.01  $\mu$ F capacitors with good high-frequency characteristics are sufficient. These capacitors are not necessary in all cases, but when used they must be placed as close as possible to the package pins and be referenced to  $V_{\rm SSA}$ .

## 3.8 Registers

These registers control and monitor operation of the ADC10:

- ADC10 status and control register, ADSCR

- ADC10 data registers, ADRH and ADRL

- ADC10 clock register, ADCLK

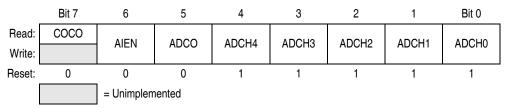

## 3.8.1 ADC10 Status and Control Register

This section describes the function of the ADC10 status and control register (ADSCR). Writing ADSCR aborts the current conversion and initiates a new conversion (if the ADCH[4:0] bits are equal to a value other than all 1s).

Figure 3-3. ADC10 Status and Control Register (ADSCR)

## **COCO** — Conversion Complete Bit

COCO is a read-only bit which is set each time a conversion is completed. This bit is cleared whenever the status and control register is written or whenever the data register (low) is read.

- 1 = Conversion completed

- 0 = Conversion not completed

## **AIEN** — **ADC10** Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of a conversion. The interrupt signal is cleared when the data register is read or the status/control register is written.

- 1 = ADC10 interrupt enabled

- 0 = ADC10 interrupt disabled

## ADCO — ADC10 Continuous Conversion Bit

When this bit is set, the ADC10 will begin to convert samples continuously (continuous conversion mode) and update the result registers at the end of each conversion, provided the ADCH[4:0] bits do not decode to all 1s. The ADC10 will continue to convert until the MCU enters reset, the MCU enters stop mode (if ACLKEN is clear), ADCLK is written, or until ADSCR is written again. If stop is entered

## **Configuration Register (CONFIG)**

## IRQPUD — IRQ Pin Pullup Control Bit

- 1 = Internal pullup is disconnected

- $0 = Internal pullup is connected between <math>\overline{IRQ}$  pin and  $V_{DD}$

## IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

## ESCIBDSRC — ESCI Baud Rate Clock Source Bit

ESCIBDSRC controls the clock source used for the ESCI. The setting of the bit affects the frequency at which the ESCI operates.

- 1 = Internal data bus clock used as clock source for ESCI

- 0 = BUSCLKX4 used as clock source for ESCI

## OSCENINSTOP— Oscillator Enable in Stop Mode Bit

OSCENINSTOP, when set, will allow the clock source to continue to generate clocks in stop mode. This function can be used to keep the auto-wakeup running while the rest of the microcontroller stops. When clear, the clock source is disabled when the microcontroller enters stop mode.

- 1 = Oscillator enabled to operate during stop mode

- 0 = Oscillator disabled during stop mode

## **RSTEN** — RST Pin Function Selection

- 1 = Reset function active in pin

- 0 = Reset function inactive in pin

## NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

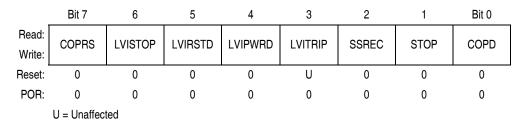

Figure 5-2. Configuration Register 1 (CONFIG1)

## COPRS (Out of Stop Mode) — COP Reset Period Selection Bit

- 1 = COP reset short cycle = 8176 × BUSCLKX4

- 0 = COP reset long cycle = 262,128 × BUSCLKX4

## COPRS (In Stop Mode) — Auto Wakeup Period Selection Bit, depends on OSCSTOPEN in CONFIG2 and external clock source

- $1 = \text{Auto wakeup short cycle} = 512 \times (INTRCOSC or BUSCLKX4)$

- $0 = \text{Auto wakeup long cycle} = 16,384 \times (INTRCOSC or BUSCLKX4)$

## LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

- 1 = LVI enabled during stop mode

- 0 = LVI disabled during stop mode

## MC68HC908QB8 Data Sheet, Rev. 3

## LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

- 1 = LVI module resets disabled

- 0 = LVI module resets enabled

## LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module.

- 1 = LVI module power disabled

- 0 = LVI module power enabled

## LVITRIP — LVI Trip Point Selection Bit

LVITRIP selects the voltage operating mode of the LVI module. The voltage mode selected for the LVI should match the operating  $V_{DD}$  for the LVI's voltage trip points for each of the modes.

- 1 = LVI operates for a 5-V protection

- 0 = LVI operates for a 3-V protection

#### NOTE

The LVITRIP bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

## SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 BUSCLKX4 cycles instead of a 4096 BUSCLKX4 cycle delay.

- 1 = Stop mode recovery after 32 BUSCLKX4 cycles

- 0 = Stop mode recovery after 4096 BUSCLKX4 cycles

#### NOTE

Exiting stop mode by an LVI reset will result in the long stop recovery.

When using the LVI during normal operation but disabling during stop mode, the LVI will have an enable time of  $t_{\rm EN}$ . The system stabilization time for power-on reset and long stop recovery (both 4096 BUSCLKX4 cycles) gives a delay longer than the LVI enable time for these startup scenarios. There is no period where the MCU is not protected from a low-power condition. However, when using the short stop recovery configuration option, the 32 BUSCLKX4 delay must be greater than the LVI's turn on time to avoid a period in startup where the LVI is not protecting the MCU.

## STOP — STOP Instruction Enable Bit

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

#### COPD — COP Disable Bit

COPD disables the COP module.

- 1 = COP module disabled

- 0 = COP module enabled

# **Chapter 7 Central Processor Unit (CPU)**

## 7.1 Introduction

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The *CPU08 Reference Manual* (document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

## 7.2 Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 Family

- 16-bit stack pointer with stack manipulation instructions

- 16-bit index register with x-register manipulation instructions

- 8-MHz CPU internal bus frequency

- 64-Kbyte program/data memory space

- 16 addressing modes

- Memory-to-memory data moves without using accumulator

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- Enhanced binary-coded decimal (BCD) data handling

- Modular architecture with expandable internal bus definition for extension of addressing range beyond 64 Kbytes

- Low-power stop and wait modes

## 7.3 CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

**Central Processor Unit (CPU)**

## 7.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code register.

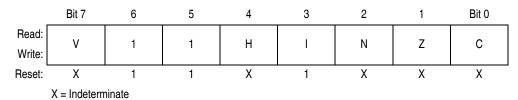

Figure 7-6. Condition Code Register (CCR)

## V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

## H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

- 1 = Carry between bits 3 and 4

- 0 = No carry between bits 3 and 4

## I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

## **NOTE**

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

## N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

- 1 = Negative result

- 0 = Non-negative result

## **Central Processor Unit (CPU)**

## Table 7-1. Instruction Set Summary (Sheet 3 of 6)

| Source                                                                                         | Operation Description            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | Effect<br>on CCF |   |          |          |          | Address<br>Mode                                     | Opcode                                           | Operand                                         | es                                   |

|------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------|---|----------|----------|----------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ٧ | Н                | I | N        | Z        | С        | Add                                                 | obc                                              | Ope                                             | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR,X<br>CLR opr,SP                            | Clear                            | M ← \$00<br>A ← \$00<br>X ← \$00<br>H ← \$00<br>M ← \$00<br>M ← \$00<br>M ← \$00                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 | _                | _ | 0        | 1        | _        | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | dd<br>ff                                        | 3<br>1<br>1<br>1<br>3<br>2<br>4      |

| CMP #opr<br>CMP opr<br>CMP opr<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP  | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 | _                | _ | 1        | ‡        | Į.       | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                   | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                      | 0 | _                | 1 | 1        | ‡        | 1        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                          | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 | -                | 1 | ‡        | 1        | ‡        | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3                                    |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP  | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | î | _                |   | 1        | 1        | <b>1</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff          | 2 3 4 4 3 2 4 5                      |

| DAA                                                                                            | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U | -                | _ | 1        | ‡        | ‡        | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel      | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 1 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 4 + rel? \text{ (result)} \neq 0 \end{array}$ | _ | _                | - | _        | -        | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 533546                               |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                   | Decrement                        | $\begin{array}{c} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                          | 1 | -                | - | <b>‡</b> | <b>‡</b> | -        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                            | Divide                           | $A \leftarrow (H:A)/(X)$<br>$H \leftarrow Remainder$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - | -                | _ | -        | ‡        | ‡        | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 | _                | - | ‡        | <b>‡</b> | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                        | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                          | 1 | _                | Ī | 1        | <b>‡</b> | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

#### **External Interrupt (IRQ)**

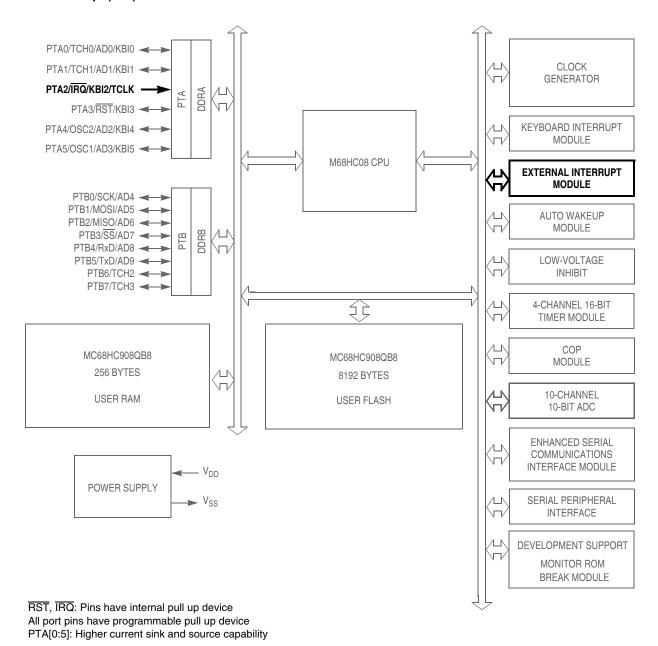

Figure 8-1. Block Diagram Highlighting IRQ Block and Pin

When set, the IMASK bit in INTSCR masks the IRQ interrupt request. A latched interrupt request is not presented to the interrupt priority logic unless IMASK is clear.

## **NOTE**

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including the IRQ interrupt request.

A falling edge on the  $\overline{IRQ}$  pin can latch an interrupt request into the IRQ latch. An IRQ vector fetch, software clear, or reset clears the IRQ latch.

MC68HC908QB8 Data Sheet, Rev. 3

## 11.3.1 Internal Signal Definitions

The following signals and clocks are used in the functional description and figures of the OSC module.

## 11.3.1.1 Oscillator Enable Signal (SIMOSCEN)

The SIMOSCEN signal comes from the system integration module (SIM) and disables the XTAL oscillator circuit, the RC oscillator, or the internal oscillator in stop mode. OSCENINSTOP in the configuration register can be used to override this signal.

## 11.3.1.2 XTAL Oscillator Clock (XTALCLK)

XTALCLK is the XTAL oscillator output signal. It runs at the full speed of the crystal (f<sub>XCLK</sub>) and comes directly from the crystal oscillator circuit. Figure 11-2 shows only the logical relation of XTALCLK to OSC1 and OSC2 and may not represent the actual circuitry. The duty cycle of XTALCLK is unknown and may depend on the crystal and other external factors. The frequency of XTALCLK can be unstable at start up.

## 11.3.1.3 RC Oscillator Clock (RCCLK)

RCCLK is the RC oscillator output signal. Its frequency is directly proportional to the time constant of the external R ( $R_{EXT}$ ) and internal C. Figure 11-3 shows only the logical relation of RCCLK to OSC1 and may not represent the actual circuitry.

## 11.3.1.4 Internal Oscillator Clock (INTCLK)

INTCLK is the internal oscillator output signal. INTCLK is software selectable to be nominally 12.8 MHz, 8.0 MHz, or 4.0 MHz. INTCLK can be digitally adjusted using the oscillator trimming feature of the OSCTRIM register (see 11.3.2.1 Internal Oscillator Trimming).

## 11.3.1.5 Bus Clock Times 4 (BUSCLKX4)

BUSCLKX4 is the same frequency as the input clock (XTALCLK, RCCLK, or INTCLK). This signal is driven to the SIM module and is used during recovery from reset and stop and is the clock source for the COP module.

## 11.3.1.6 Bus Clock Times 2 (BUSCLKX2)

The frequency of this signal is equal to half of the BUSCLKX4. This signal is driven to the SIM for generation of the bus clocks used by the CPU and other modules on the MCU. BUSCLKX2 will be divided by two in the SIM. The internal bus frequency is one fourth of the XTALCLK, RCCLK, or INTCLK frequency.

#### 11.3.2 Internal Oscillator

The internal oscillator circuit is designed for use with no external components to provide a clock source with a tolerance of less than  $\pm 25\%$  untrimmed. An 8-bit register (OSCTRIM) allows the digital adjustment to a tolerance of ACC<sub>INT</sub>. See the oscillator characteristics in the Electrical section of this data sheet.

The internal oscillator is capable of generating clocks of 12.8 MHz, 8.0 MHz, or 4.0 MHz (INTCLK) resulting in a bus frequency (INTCLK divided by 4) of 3.2 MHz, 2.0 MHz, or 1.0 MHz respectively. The bus clock is software selectable and defaults to the 1.0-MHz bus out of reset. Users can increase the bus frequency based on the voltage range of their application.

Freescale Semiconductor 95

MC68HC908QB8 Data Sheet, Rev. 3

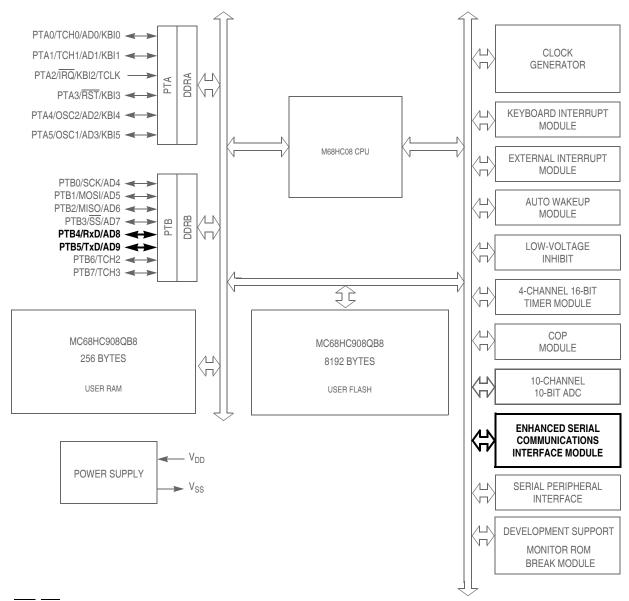

RST, IRQ: Pins have internal pull up device All port pins have programmable pull up device PTA[0:5]: Higher current sink and source capability

Figure 13-1. Block Diagram Highlighting ESCI Block and Pins

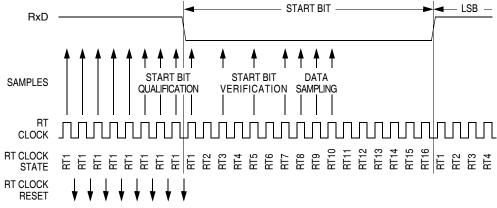

## 13.3.3.3 Data Sampling

The receiver samples the RxD pin at the RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock is resynchronized at these times (see Figure 13-6):

- After every start bit

- After the receiver detects a data bit change from 1 to 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid 0)

To locate the start bit, data recovery logic does an asynchronous search for a 0 preceded by three 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 13-6. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Table 13-1 summarizes the results of the start bit verification samples.

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |  |  |

|---------------------------|------------------------|------------|--|--|

| 000                       | Yes                    | 0          |  |  |

| 001                       | Yes                    | 1          |  |  |

| 010                       | Yes                    | 1          |  |  |

| 011                       | No                     | 0          |  |  |

| 100                       | Yes                    | 1          |  |  |

| 101                       | No                     | 0          |  |  |

| 110                       | No                     | 0          |  |  |

| 111                       | No                     | 0          |  |  |

**Table 13-1. Start Bit Verification**

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 13-2 summarizes the results of the data bit samples.

MC68HC908QB8 Data Sheet, Rev. 3

## 13.4.1 Transmitter Interrupts

These conditions can generate interrupt requests from the ESCI transmitter:

- ESCI transmitter empty (SCTE) The SCTE bit in SCS1 indicates that the SCDR has transferred

a character to the transmit shift register. SCTE can generate a transmitter interrupt request. Setting

the ESCI transmit interrupt enable bit, SCTIE, in SCC2 enables the SCTE bit to generate

transmitter interrupt requests.

- Transmission complete (TC) The TC bit in SCS1 indicates that the transmit shift register and the SCDR are empty and that no break or idle character has been generated. The transmission complete interrupt enable bit, TCIE, in SCC2 enables the TC bit to generate transmitter interrupt requests.

## 13.4.2 Receiver Interrupts

These sources can generate interrupt requests from the ESCI receiver:

- ESCI receiver full (SCRF) The SCRF bit in SCS1 indicates that the receive shift register has

transferred a character to the SCDR. SCRF can generate a receiver interrupt request. Setting the

ESCI receive interrupt enable bit, SCRIE, in SCC2 enables the SCRF bit to generate receiver

interrupts.

- Idle input (IDLE) The IDLE bit in SCS1 indicates that 10 or 11 consecutive 1s shifted in from the RxD pin. The idle line interrupt enable bit, ILIE, in SCC2 enables the IDLE bit to generate interrupt requests.

## 13.4.3 Error Interrupts

These receiver error flags in SCS1 can generate interrupt requests:

- Receiver overrun (OR) The OR bit indicates that the receive shift register shifted in a new

character before the previous character was read from the SCDR. The previous character remains

in the SCDR, and the new character is lost. The overrun interrupt enable bit, ORIE, in SCC3

enables OR to generate ESCI error interrupt requests.

- Noise flag (NF) The NF bit is set when the ESCI detects noise on incoming data or break characters, including start, data, and stop bits. The noise error interrupt enable bit, NEIE, in SCC3 enables NF to generate ESCI error interrupt requests.

- Framing error (FE) The FE bit in SCS1 is set when a 0 occurs where the receiver expects a stop bit. The framing error interrupt enable bit, FEIE, in SCC3 enables FE to generate ESCI error interrupt requests.

- Parity error (PE) The PE bit in SCS1 is set when the ESCI detects a parity error in incoming data. The parity error interrupt enable bit, PEIE, in SCC3 enables PE to generate ESCI error interrupt requests.

## 13.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 13.5.1 Wait Mode

The ESCI module remains active in wait mode. Any enabled interrupt request from the ESCI module can bring the MCU out of wait mode.

If ESCI module functions are not required during wait mode, reduce power consumption by disabling the module before executing the WAIT instruction.

MC68HC908QB8 Data Sheet, Rev. 3

## 13.8.1 ESCI Control Register 1

ESCI control register 1 (SCC1):

- Enables loop mode operation

- Enables the ESCI

- Controls output polarity

- Controls character length

- Controls ESCI wakeup method

- Controls idle character detection

- Enables parity function

- Controls parity type

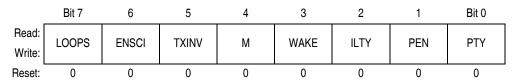

Figure 13-9. ESCI Control Register 1 (SCC1)

## LOOPS — Loop Mode Select Bit

This read/write bit enables loop mode operation. In loop mode the RxD pin is disconnected from the ESCI, and the transmitter output goes into the receiver input. Both the transmitter and the receiver must be enabled to use loop mode.

- 1 = Loop mode enabled

- 0 = Normal operation enabled

## **ENSCI** — Enable ESCI Bit

This read/write bit enables the ESCI and the ESCI baud rate generator. Clearing ENSCI sets the SCTE and TC bits in ESCI status register 1 and disables transmitter interrupts.

- 1 = ESCI enabled

- 0 = ESCI disabled

## TXINV — Transmit Inversion Bit

This read/write bit reverses the polarity of transmitted data.

- 1 = Transmitter output inverted

- 0 = Transmitter output not inverted

## NOTE

Setting the TXINV bit inverts all transmitted values including idle, break, start, and stop bits.

## M — Mode (Character Length) Bit

This read/write bit determines whether ESCI characters are eight or nine bits long (see Table 13-4). The ninth bit can serve as a receiver wakeup signal or as a parity bit.

- 1 = 9-bit ESCI characters

- 0 = 8-bit ESCI characters

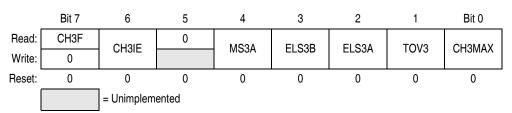

**Timer Interface Module (TIM)**

## 16.8.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers does the following:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- · Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

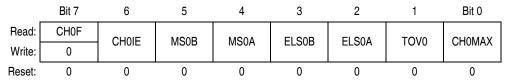

Figure 16-9. TIM Channel 0 Status and Control Register (TSC0)

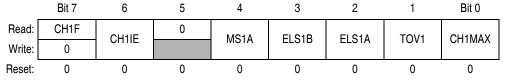

Figure 16-10. TIM Channel 1 Status and Control Register (TSC1)

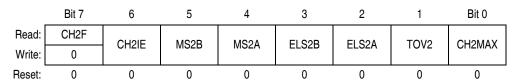

Figure 16-11. TIM Channel 2 Status and Control Register (TSC2)

Figure 16-12. TIM Channel 3 Status and Control Register (TSC3)

## CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the counter registers matches the value in the TIM channel x registers.

Clear CHxF by reading the TSCx register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

MC68HC908QB8 Data Sheet, Rev. 3

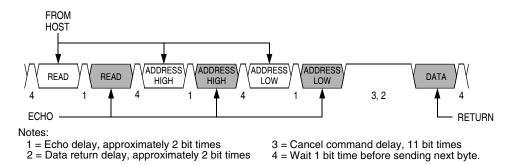

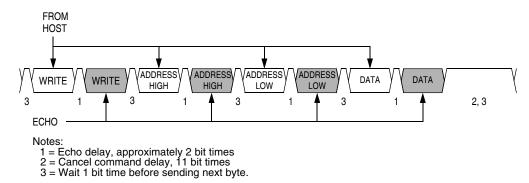

Figure 17-15. Read Transaction

Figure 17-16. Write Transaction

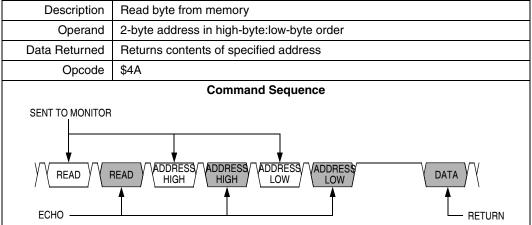

A brief description of each monitor mode command is given in Table 17-3 through Table 17-8.

Table 17-3. READ (Read Memory) Command

Read byte from memory

MC68HC908QB8 Data Sheet, Rev. 3

## **Electrical Specifications**

## 18.8 3-V DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                       | Symbol              | Min                                                                  | Typ <sup>(2)</sup> | Max                   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------|--------------------|-----------------------|------|

| Output high voltage  I <sub>Load</sub> = -0.6 mA, all I/O pins  I <sub>Load</sub> = -4.0 mA, all I/O pins  I <sub>Load</sub> = -10.0 mA, PTA0, PTA1, PTA3-PTA5 only | V <sub>OH</sub>     | V <sub>DD</sub> -0.3<br>V <sub>DD</sub> -1.0<br>V <sub>DD</sub> -0.8 | _<br>_<br>_        | _<br>_<br>_           | V    |

| Maximum combined I <sub>OH</sub> (all I/O pins)                                                                                                                     | I <sub>OHT</sub>    | _                                                                    | _                  | 50                    | mA   |

| Output low voltage $I_{Load} = 0.5$ mA, all I/O pins $I_{Load} = 6.0$ mA, all I/O pins $I_{Load} = 10.0$ mA, PTA0, PTA1, PTA3-PTA5 only                             | V <sub>OL</sub>     | _<br>_<br>_                                                          | _<br>_<br>_        | 0.3<br>1.0<br>0.8     | V    |

| Maximum combined I <sub>OL</sub> (all I/O pins)                                                                                                                     | I <sub>OHL</sub>    | _                                                                    | _                  | 50                    | mA   |

| Input high voltage<br>PTA0–PTA5, PTB0–PTB7                                                                                                                          | V <sub>IH</sub>     | 0.7 x V <sub>DD</sub>                                                | _                  | V <sub>DD</sub>       | V    |

| Input low voltage<br>PTA0-PTA5, PTB0-PTB7                                                                                                                           | V <sub>IL</sub>     | V <sub>SS</sub>                                                      | _                  | 0.3 x V <sub>DD</sub> | V    |

| Input hysteresis <sup>(3)</sup>                                                                                                                                     | V <sub>HYS</sub>    | 0.06 x V <sub>DD</sub>                                               | _                  | _                     | V    |

| DC injection current, all ports <sup>(4)</sup>                                                                                                                      | I <sub>INJ</sub>    | -2                                                                   | _                  | +2                    | mA   |

| Total dc current injection (sum of all I/O) <sup>(4)</sup>                                                                                                          | I <sub>INJTOT</sub> | -25                                                                  | _                  | +25                   | mA   |

| Ports Hi-Z leakage current                                                                                                                                          | I <sub>IL</sub>     | -1                                                                   | ±0.1               | +1                    | μΑ   |

| Capacitance<br>Ports (as input) <sup>(3)</sup>                                                                                                                      | C <sub>IN</sub>     | _                                                                    | _                  | 8                     | pF   |

| POR rearm voltage                                                                                                                                                   | V <sub>POR</sub>    | 750                                                                  | _                  | _                     | mV   |

| POR rise time ramp rate <sup>(3)(5)</sup>                                                                                                                           | R <sub>POR</sub>    | 0.035                                                                | _                  | _                     | V/ms |

| Monitor mode entry voltage (3)                                                                                                                                      | V <sub>TST</sub>    | V <sub>DD</sub> + 2.5                                                | _                  | V <sub>DD</sub> + 4.0 | V    |

| Pullup resistors <sup>(6)</sup><br>PTA0–PTA5, PTB0–PTB7                                                                                                             | R <sub>PU</sub>     | 16                                                                   | 26                 | 36                    | kΩ   |

| Pulldown resistors <sup>(7)</sup><br>PTA0–PTA5                                                                                                                      | R <sub>PD</sub>     | 16                                                                   | 26                 | 36                    | kΩ   |

| Low-voltage inhibit reset, trip falling voltage                                                                                                                     | V <sub>TRIPF</sub>  | 2.40                                                                 | 2.55               | 2.70                  | V    |

| Low-voltage inhibit reset, trip rising voltage <sup>(6)</sup>                                                                                                       | V <sub>TRIPR</sub>  | 2.475                                                                | 2.625              | 2.775                 | V    |

| Low-voltage inhibit reset/recover hysteresis                                                                                                                        | V <sub>HYS</sub>    | _                                                                    | 75                 | _                     | mV   |

- 1.  $V_{DD}$  = 2.7 to 3.3 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted. 2. Typical values reflect average measurements at midpoint of voltage range, 25•C only. Typical values are for reference only and are not tested in production.

- 3. Values are based on characterization results, not tested in production.

- 4. Guaranteed by design, not tested in production.

- 5. If minimum  $V_{DD}$  is not reached before the internal POR reset is released, the LVI will hold the part in reset until minimum  $V_{DD}$  is reached. 6.  $R_{PU}$  is measured at  $V_{DD} = 3.0 \text{ V}$ 7.  $R_{PD}$  is measured at  $V_{DD} = 3.0 \text{ V}$ , Pulldown resistors only available when KBIx is enabled with KBIxPOL =1.

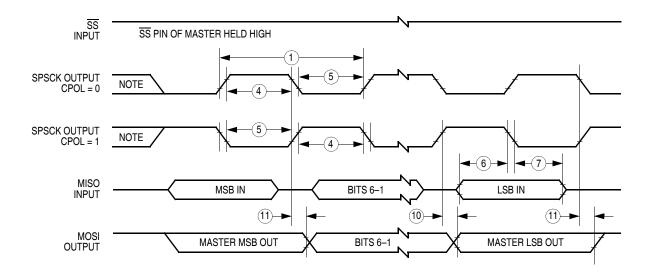

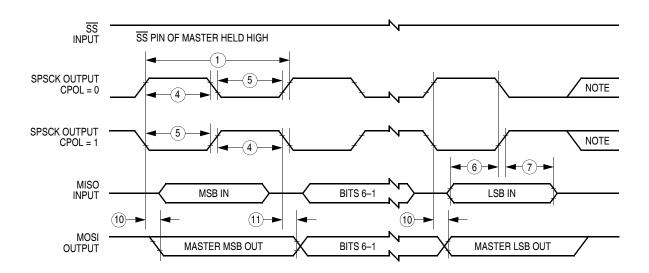

Note: This first clock edge is generated internally, but is not seen at the SPSCK pin.

## a) SPI Master Timing (CPHA = 0)

Note: This last clock edge is generated internally, but is not seen at the SPSCK pin.

## b) SPI Master Timing (CPHA = 1)

Figure 18-11. SPI Master Timing

MC68HC908QB8 Data Sheet, Rev. 3

## **Electrical Specifications**

## **18.17 Memory Characteristics**

| Characteristic                                    | Symbol                          | Min        | Typ <sup>(1)</sup> | Max        | Unit   |

|---------------------------------------------------|---------------------------------|------------|--------------------|------------|--------|

| RAM data retention voltage (2)                    | V <sub>RDR</sub>                | 1.3        | _                  | _          | ٧      |

| FLASH program bus clock frequency                 | _                               | 1          | _                  | _          | MHz    |

| FLASH PGM/ERASE supply voltage (V <sub>DD</sub> ) | V <sub>PGM/ERASE</sub>          | 2.7        | _                  | 5.5        | V      |

| FLASH read bus clock frequency                    | f <sub>Read</sub> (3)           | 0          | _                  | 8 M        | Hz     |

| FLASH page erase time <1 K cycles >1 K cycles     | t <sub>Erase</sub>              | 0.9<br>3.6 | 1<br>4             | 1.1<br>5.5 | ms     |

| FLASH mass erase time                             | t <sub>MErase</sub>             | 4          | _                  | _          | ms     |

| FLASH PGM/ERASE to HVEN setup time                | t <sub>NVS</sub>                | 10         | _                  | _          | μS     |

| FLASH high-voltage hold time                      | t <sub>NVH</sub>                | 5          | _                  | _          | μS     |

| FLASH high-voltage hold time (mass erase)         | t <sub>NVHL</sub>               | 100        | _                  | 1          | μS     |

| FLASH program hold time                           | t <sub>PGS</sub>                | 5          | _                  | _          | μS     |

| FLASH program time                                | t <sub>PROG</sub>               | 30         | _                  | 40         | μS     |

| FLASH return to read time                         | t <sub>RCV</sub> <sup>(4)</sup> | 1          | _                  | _          | μS     |

| FLASH cumulative program HV period                | t <sub>HV</sub> <sup>(5)</sup>  | _          | _                  | 4          | ms     |

| FLASH endurance <sup>(6)</sup>                    | _                               | 10 k       | 100 k              | _          | Cycles |

| FLASH data retention time <sup>(7)</sup>          | _                               | 15         | 100                | _          | Years  |

- 1. Typical values are for reference only and are not tested in production.

- 2. Values are based on characterization results, not tested in production.

- 3.  $f_{\mbox{\scriptsize Read}}$  is defined as the frequency range for which the FLASH memory can be read.

- 4. t<sub>BCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

- 5. t<sub>HV</sub> is defined as the cumulative high voltage programming time to the same row before next erase.

- t<sub>HV</sub> must satisfy this condition: t<sub>NVS</sub> + t<sub>NVH</sub> + t<sub>PGS</sub> + (t<sub>PROG</sub> x 32) ≤ t<sub>HV</sub> maximum.

6. Typical endurance was evaluated for this product family. For additional information on how Freescale Semiconductor defines *Typical Endurance*, please refer to Engineering Bulletin EB619.

- 7. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25•C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines Typical Data Retention, please refer to Engineering Bulletin EB618.