Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | HC08                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | LVD, POR, PWM                                                        |

| Number of I/O              | 13                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | A/D 10x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | 16-SOIC                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcl908qb8dwe |

8.7.1

8.8

9.1

10.1

| Table o | f Contents                         |    |

|---------|------------------------------------|----|

| 8.5     | Low-Power Modes                    | 80 |

|         | Wait Mode                          |    |

| 8.5.2   | Stop Mode                          | 80 |

| 8.6     | IRQ Module During Break Interrupts | 80 |

| 8.7     | I/O Signals                        | 80 |

IRQ Input Pins (IRQ)

80

Registers

81

# Chapter 9 Keyboard Interrupt Module (KBI)

Introduction .....

| 9.2     | Features                                     | 83 |

|---------|----------------------------------------------|----|

| 9.3     | Functional Description                       | 83 |

| 9.3.1   | Keyboard Operation                           | 83 |

| 9.3.1.1 | MODEK = 1                                    | 84 |

| 9.3.1.2 | MODEK = 0                                    | 85 |

| 9.3.2   | Keyboard Initialization                      | 86 |

| 9.4     | Interrupts                                   | 86 |

| 9.5     | Low-Power Modes                              | 86 |

| 9.5.1   | Wait Mode                                    | 86 |

| 9.5.2   | Stop Mode                                    | 86 |

| 9.6     | KBI During Break Interrupts                  | 86 |

| 9.7     | I/O Signals                                  | 87 |

| 9.7.1   | KBI Input Pins (KBIx:KBI0)                   | 87 |

| 9.8     | Registers                                    | 87 |

| 9.8.1   | Keyboard Status and Control Register (KBSCR) | 87 |

| 9.8.2   | Keyboard Interrupt Enable Register (KBIER)   | 88 |

| 9.8.3   | Keyboard Interrupt Polarity Register (KBIPR) | 88 |

|         |                                              |    |

# Chapter 10 Low-Voltage Inhibit (LVI)

Introduction .....

89

| 10.2   | reatures                              | 9  |

|--------|---------------------------------------|----|

| 10.3   | Functional Description                | 9  |

| 10.3.1 | Polled LVI Operation                  | 0  |

| 10.3.2 | · · · · · · · · · · · · · · · · · · · | 0  |

|        |                                       |    |

| 10.3.4 | LVI Trip Selection9                   | 0  |

| 10.4   | LVI Interrupts                        | 1  |

|        | Low-Power Modes                       |    |

| 10.5.1 | Wait Mode                             | 11 |

| 10.5.2 | Stop Mode                             | 1  |

| 10.6   | Registers                             | 1  |

MC68HC908QB8 Data Sheet, Rev. 3

#### **Table of Contents**

| 18.13 | ADC10 Characteristics                                         | . 219 |

|-------|---------------------------------------------------------------|-------|

| 18.14 | 5.0-Volt SPI Characteristics                                  | . 221 |

| 18.15 | 3.0-Volt SPI Characteristics                                  | . 222 |

| 18.16 | Timer Interface Module Characteristics                        | . 225 |

| 18.17 | Memory Characteristics                                        | . 226 |

|       | Chapter 19 Ordering Information and Mechanical Specifications |       |

| 19.1  | Introduction                                                  | . 227 |

| 19.2  | MC Order Numbers                                              | . 227 |

| 19.3  | Package Dimensions                                            | . 227 |

MC68HC908QB8 Data Sheet, Rev. 3

Freescale Semiconductor

#### Analog-to-Digital Converter (ADC10) Module

Whichever clock is selected, its frequency must fall within the acceptable frequency range for ADCK. If the available clocks are too slow, the ADC10 will not perform according to specifications. If the available clocks are too fast, then the clock must be divided to the appropriate frequency. This divider is specified by the ADIV[1:0] bits and can be divide-by 1, 2, 4, or 8.

#### 3.3.2 Input Select and Pin Control

Only one analog input may be used for conversion at any given time. The channel select bits in ADSCR are used to select the input signal for conversion.

#### 3.3.3 Conversion Control

Conversions can be performed in either 10-bit mode or 8-bit mode as determined by the MODE bits. Conversions can be initiated by either a software or hardware trigger. In addition, the ADC10 module can be configured for low power operation, long sample time, and continuous conversion.

#### 3.3.3.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADSCR (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADSCR is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

#### 3.3.3.2 Completing Conversions

A conversion is completed when the result of the conversion is transferred into the data result registers, ADRH and ADRL. This is indicated by the setting of the COCO bit. An interrupt is generated if AIEN is high at the time that COCO is set.

A blocking mechanism prevents a new result from overwriting previous data in ADRH and ADRL if the previous data is in the process of being read while in 10-bit mode (ADRH has been read but ADRL has not). In this case the data transfer is blocked, COCO is not set, and the new result is lost. When a data transfer is blocked, another conversion is initiated regardless of the state of ADCO (single or continuous conversions enabled). If single conversions are enabled, this could result in several discarded conversions and excess power consumption. To avoid this issue, the data registers must not be read after initiating a single conversion until the conversion completes.

#### 3.3.3.3 Aborting Conversions

Any conversion in progress will be aborted when:

- A write to ADSCR occurs (the current conversion will be aborted and a new conversion will be initiated, if ADCH are not all 1s).

- A write to ADCLK occurs.

- The MCU is reset.

- The MCU enters stop mode with ACLK not enabled.

MC68HC908QB8 Data Sheet, Rev. 3

#### 4.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 4.5.1 Wait Mode

The AWU module remains inactive in wait mode.

#### 4.5.2 Stop Mode

When the AWU module is enabled (AWUIE = 1 in the keyboard interrupt enable register) it is activated automatically upon entering stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode. The AWU counters start from 0 each time stop mode is entered.

## 4.6 Registers

The AWU shares registers with the keyboard interrupt (KBI) module, the port A I/O module and configuration register 2. The following I/O registers control and monitor operation of the AWU:

- Port A data register (PTA)

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

- Configuration register 1 (CONFIG1)

- Configuration register 2 (CONFIG2)

#### 4.6.1 Port A I/O Register

The port A data register (PTA) contains a data latch for the state of the AWU interrupt request, in addition to the data latches for port A.

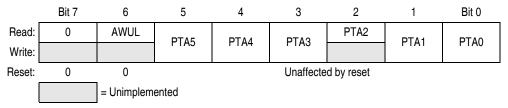

Figure 4-2. Port A Data Register (PTA)

#### AWUL — Auto Wakeup Latch

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally. There is no PTA6 port or any of the associated bits such as PTA6 data direction or pullup bits.

- 1 = Auto wakeup interrupt request is pending

- 0 = Auto wakeup interrupt request is not pending

#### NOTE

PTA5-PTA0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 12.2.1 Port A Data Register.

MC68HC908QB8 Data Sheet, Rev. 3

**Auto Wakeup Module (AWU)**

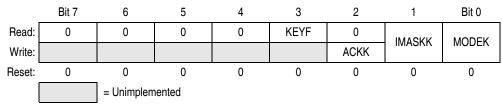

### 4.6.2 Keyboard Status and Control Register

The keyboard status and control register (KBSCR):

- Flags keyboard/auto wakeup interrupt requests

- Acknowledges keyboard/auto wakeup interrupt requests

- Masks keyboard/auto wakeup interrupt requests

Figure 4-3. Keyboard Status and Control Register (KBSCR)

#### Bits 7-4 — Not used

These read-only bits always read as 0s.

#### **KEYF** — Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending on port A or auto wakeup. Reset clears the KEYF bit.

- 1 = Keyboard/auto wakeup interrupt pending

- 0 = No keyboard/auto wakeup interrupt pending

#### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard/auto wakeup interrupt request on port A and auto wakeup logic. ACKK always reads as 0. Reset clears ACKK.

#### **IMASKK**— Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests on port A or auto wakeup. Reset clears the IMASKK bit.

- 1 = Keyboard/auto wakeup interrupt requests masked

- 0 = Keyboard/auto wakeup interrupt requests not masked

#### NOTE

MODEK is not used in conjuction with the auto wakeup feature. To see a description of this bit, see 9.8.1 Keyboard Status and Control Register (KBSCR).

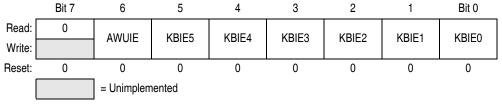

#### 4.6.3 Keyboard Interrupt Enable Register

The keyboard interrupt enable register (KBIER) enables or disables the auto wakeup to operate as a keyboard/auto wakeup interrupt input.

Figure 4-4. Keyboard Interrupt Enable Register (KBIER)

MC68HC908QB8 Data Sheet, Rev. 3

Table 7-1. Instruction Set Summary (Sheet 4 of 6)

| Source                                                                                         | Operation                           | Description                                                                                                                                                                                           |   | Effect on CCR |   |          |   | Address<br>Mode | Opcode                                              | Operand                                          | les                        |                                      |

|------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------|---|----------|---|-----------------|-----------------------------------------------------|--------------------------------------------------|----------------------------|--------------------------------------|

| Form                                                                                           |                                     | 23334                                                                                                                                                                                                 | ٧ | Н             | ı | N        | Z | С               | Add                                                 | obc                                              | Ope                        | Cycles                               |

| JMP opr<br>JMP opr<br>JMP opr,X<br>JMP opr,X<br>JMP ,X                                         | Jump                                | PC ← Jump Address                                                                                                                                                                                     | _ | _             | _ | -        | - | _               | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC<br>CC<br>DC<br>EC<br>FC                       | dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>3<br>2                |

| JSR opr<br>JSR opr<br>JSR opr,X<br>JSR opr,X<br>JSR ,X                                         | Jump to Subroutine                  | $PC \leftarrow (PC) + n (n = 1, 2, \text{ or } 3)$<br>$Push (PCL); SP \leftarrow (SP) - 1$<br>$Push (PCH); SP \leftarrow (SP) - 1$<br>$PC \leftarrow Unconditional Address$                           | _ | -             | _ | _        | _ | _               | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BD<br>CD<br>DD<br>ED<br>FD                       | dd<br>hh II<br>ee ff<br>ff | 4<br>5<br>6<br>5<br>4                |

| LDA #opr<br>LDA opr<br>LDA opr,X<br>LDA opr,X<br>LDA opr,X<br>LDA opr,SP<br>LDA opr,SP         | Load A from M                       | A ← (M)                                                                                                                                                                                               | 0 | -             | _ | <b>‡</b> | 1 | _               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A6<br>B6<br>C6<br>D6<br>E6<br>F6<br>9EE6<br>9ED6 |                            | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| LDHX #opr<br>LDHX opr                                                                          | Load H:X from M                     | H:X ← (M:M + 1)                                                                                                                                                                                       | 0 | -             | - | 1        | 1 | _               | IMM<br>DIR                                          | 45<br>55                                         | ii jj<br>dd                | 3<br>4                               |

| LDX #opr<br>LDX opr<br>LDX opr,<br>LDX opr,X<br>LDX opr,X<br>LDX,X<br>LDX opr,SP<br>LDX opr,SP | Load X from M                       | X ← (M)                                                                                                                                                                                               | 0 | _             | _ | 1        | ‡ | _               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AE<br>BE<br>CE<br>DE<br>EE<br>FE<br>9EEE<br>9EDE |                            | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| LSL opr<br>LSLA<br>LSLX<br>LSL opr,X<br>LSL ,X<br>LSL opr,SP                                   | Logical Shift Left<br>(Same as ASL) | © 0 b7 b0                                                                                                                                                                                             | 1 | _             | _ | 1        | 1 | ‡               | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff             | 4<br>1<br>1<br>4<br>3<br>5           |

| LSR opr<br>LSRA<br>LSRX<br>LSR opr,X<br>LSR ,X<br>LSR opr,SP                                   | Logical Shift Right                 | 0                                                                                                                                                                                                     | t | _             | - | 0        | 1 | ‡               | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 34<br>44<br>54<br>64<br>74<br>9E64               | dd<br>ff<br>ff             | 4<br>1<br>1<br>4<br>3<br>5           |

| MOV opr,opr<br>MOV opr,X+<br>MOV #opr,opr<br>MOV X+,opr                                        | Move                                | $(M)_{Destination} \leftarrow (M)_{Source}$ $H:X \leftarrow (H:X) + 1 (IX+D, DIX+)$                                                                                                                   | 0 | _             | _ | ţ        | Î | -               | DD<br>DIX+<br>IMD<br>IX+D                           | 4E<br>5E<br>6E<br>7E                             | dd dd<br>dd<br>ii dd<br>dd | 5<br>4<br>4<br>4                     |

| MUL                                                                                            | Unsigned multiply                   | $X:A \leftarrow (X) \times (A)$                                                                                                                                                                       | - | 0             | - | -        | _ | 0               | INH                                                 | 42                                               |                            | 5                                    |

| NEG opr<br>NEGA<br>NEGX<br>NEG opr,X<br>NEG ,X<br>NEG opr,SP                                   | Negate (Two's Complement)           | $\begin{array}{l} M \leftarrow -(M) = \$00 - (M) \\ A \leftarrow -(A) = \$00 - (A) \\ X \leftarrow -(X) = \$00 - (X) \\ M \leftarrow -(M) = \$00 - (M) \\ M \leftarrow -(M) = \$00 - (M) \end{array}$ | 1 | _             | _ | 1        | 1 | 1               | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 30<br>40<br>50<br>60<br>70<br>9E60               | dd<br>ff<br>ff             | 4<br>1<br>1<br>4<br>3<br>5           |

| NOP                                                                                            | No Operation                        | None                                                                                                                                                                                                  | - | _             | - | -        | - | -               | INH                                                 | 9D                                               |                            | 1                                    |

| NSA                                                                                            | Nibble Swap A                       | A ← (A[3:0]:A[7:4])                                                                                                                                                                                   | - | _             | _ | _        | _ | _               | INH                                                 | 62                                               |                            | 3                                    |

| ORA #opr<br>ORA opr<br>ORA opr<br>ORA opr,X<br>ORA opr,X<br>ORA opr,SP<br>ORA opr,SP           | Inclusive OR A and M                | A ← (A)   (M)                                                                                                                                                                                         | 0 | _             | _ | 1        | Î | _               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AA<br>BA<br>CA<br>DA<br>EA<br>FA<br>9EEA<br>9EDA |                            | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| PSHA                                                                                           | Push A onto Stack                   | Push (A); SP ← (SP) – 1                                                                                                                                                                               | _ | _             | _ | _        | _ | -               | INH                                                 | 87                                               |                            | 2                                    |

| PSHH                                                                                           | Push H onto Stack                   | Push (H); SP ← (SP) – 1                                                                                                                                                                               | - | _             | _ | _        | _ | -               | INH                                                 | 8B                                               |                            | 2                                    |

| PSHX                                                                                           | Push X onto Stack                   | Push (X); $SP \leftarrow (SP) - 1$                                                                                                                                                                    | - | _             | _ | _        | _ | -               | INH                                                 | 89                                               |                            | 2                                    |

# **Central Processor Unit (CPU)**

Table 7-1. Instruction Set Summary (Sheet 5 of 6)

| Source                                                                                         | Operation                                                      | Effect<br>On CCR                                                                                                                                                                                                                |   |   |   | tion Description Effect on CCR |          |          |                                                     |                                                  |                                           |                                      |  |  | Operand | es |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|--------------------------------|----------|----------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|--|--|---------|----|

| Form                                                                                           | operation .                                                    | Boothplion                                                                                                                                                                                                                      | ٧ | Н | I | N                              | z        | С        | Add                                                 | Opcode                                           | Ope                                       | Cycles                               |  |  |         |    |

| PULA                                                                                           | Pull A from Stack                                              | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                                              | - | - | - | -                              | -        | -        | INH                                                 | 86                                               |                                           | 2                                    |  |  |         |    |

| PULH                                                                                           | Pull H from Stack                                              | SP ← (SP + 1); Pull (H)                                                                                                                                                                                                         | - | - | - | -                              | -        | -        | INH                                                 | 8A                                               |                                           | 2                                    |  |  |         |    |

| PULX                                                                                           | Pull X from Stack                                              | $SP \leftarrow (SP + 1); Pull(X)$                                                                                                                                                                                               | _ | _ | _ | -                              | -        | -        | INH                                                 | 88                                               |                                           | 2                                    |  |  |         |    |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                   | Rotate Left through Carry                                      | b7 b0                                                                                                                                                                                                                           | 1 | ı | _ | 1                              | ‡        | 1        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |  |  |         |    |

| ROR opr<br>RORA<br>RORX<br>ROR opr,X<br>ROR ,X<br>ROR opr,SP                                   | Rotate Right through Carry                                     | b7 b0                                                                                                                                                                                                                           | 1 | - | _ | ‡                              | <b>‡</b> | 1        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |  |  |         |    |

| RSP                                                                                            | Reset Stack Pointer                                            | SP ← \$FF                                                                                                                                                                                                                       | - | - | - | -                              | -        | -        | INH                                                 | 9C                                               |                                           | 1                                    |  |  |         |    |

| RTI                                                                                            | Return from Interrupt                                          | $\begin{array}{c} SP \leftarrow (SP) + 1;  Pull  (CCR) \\ SP \leftarrow (SP) + 1;  Pull  (A) \\ SP \leftarrow (SP) + 1;  Pull  (X) \\ SP \leftarrow (SP) + 1;  Pull  (PCH) \\ SP \leftarrow (SP) + 1;  Pull  (PCL) \end{array}$ | 1 | 1 | ţ | ţ                              | 1        | ţ        | INH                                                 | 80                                               |                                           | 7                                    |  |  |         |    |

| RTS                                                                                            | Return from Subroutine                                         | $SP \leftarrow SP + 1$ ; Pull (PCH)<br>$SP \leftarrow SP + 1$ ; Pull (PCL)                                                                                                                                                      | - | - | _ | -                              | -        | -        | INH                                                 | 81                                               |                                           | 4                                    |  |  |         |    |

| SBC #opr<br>SBC opr<br>SBC opr,X<br>SBC opr,X<br>SBC opr,X<br>SBC opr,SP<br>SBC opr,SP         | Subtract with Carry                                            | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                  | 1 | _ | _ | ţ                              | <b>‡</b> | <b>1</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A2<br>B2<br>C2<br>D2<br>E2<br>F2<br>9EE2<br>9ED2 |                                           | 23443245                             |  |  |         |    |

| SEC                                                                                            | Set Carry Bit                                                  | C ← 1                                                                                                                                                                                                                           | - | _ | _ | -                              | _        | 1        | INH                                                 | 99                                               |                                           | 1                                    |  |  |         |    |

| SEI                                                                                            | Set Interrupt Mask                                             | I ← 1                                                                                                                                                                                                                           | - | _ | 1 | -                              | _        | _        | INH                                                 | 9B                                               |                                           | 2                                    |  |  |         |    |

| STA opr<br>STA opr,<br>STA opr,X<br>STA opr,X<br>STA ,X<br>STA opr,SP<br>STA opr,SP            | Store A in M                                                   | M ← (A)                                                                                                                                                                                                                         | 0 | _ | _ | ţ                              | 1        | _        | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | B7<br>C7<br>D7<br>E7<br>F7<br>9EE7<br>9ED7       | dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 3<br>4<br>4<br>3<br>2<br>4<br>5      |  |  |         |    |

| STHX opr                                                                                       | Store H:X in M                                                 | (M:M + 1) ← (H:X)                                                                                                                                                                                                               | 0 | _ | _ | 1                              | 1        | -        | DIR                                                 | 35                                               | dd                                        | 4                                    |  |  |         |    |

| STOP                                                                                           | Enable Interrupts, Stop Processing, Refer to MCU Documentation | $I \leftarrow 0$ ; Stop Processing                                                                                                                                                                                              | - | - | 0 | -                              | -        | -        | INH                                                 | 8E                                               |                                           | 1                                    |  |  |         |    |

| STX opr<br>STX opr<br>STX opr,X<br>STX opr,X<br>STX ,X<br>STX opr,SP<br>STX opr,SP             | Store X in M                                                   | $M \leftarrow (X)$                                                                                                                                                                                                              | 0 | _ | _ | 1                              | ‡        | _        | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | BF<br>CF<br>DF<br>EF<br>FF<br>9EEF<br>9EDF       |                                           | 3<br>4<br>4<br>3<br>2<br>4<br>5      |  |  |         |    |

| SUB #opr<br>SUB opr<br>SUB opr,<br>SUB opr,X<br>SUB opr,X<br>SUB,X<br>SUB opr,SP<br>SUB opr,SP | Subtract                                                       | $A \leftarrow (A) - (M)$                                                                                                                                                                                                        | 1 | _ | _ | 1                              | ‡        | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A0<br>B0<br>C0<br>D0<br>E0<br>F0<br>9EE0<br>9ED0 |                                           | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |  |  |         |    |

# Table 7-1. Instruction Set Summary (Sheet 6 of 6)

| Source                                                       | Operation                             | Description                                                                                                                                                                                                                                                                                                                                                                  |   |        | Effect on CCR |          |     |     | Address<br>Mode                       | Opcode                             | Operand        | es                         |

|--------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|---------------|----------|-----|-----|---------------------------------------|------------------------------------|----------------|----------------------------|

| Form                                                         | Operation                             | <u>-</u>                                                                                                                                                                                                                                                                                                                                                                     |   | HIINZC |               | Add      | Opc | Ope | Cycles                                |                                    |                |                            |

| SWI                                                          | Software Interrupt                    | $\begin{array}{c} PC \leftarrow (PC) + 1;  Push  (PCL) \\ SP \leftarrow (SP) - 1;  Push  (PCH) \\ SP \leftarrow (SP) - 1;  Push  (X) \\ SP \leftarrow (SP) - 1;  Push  (A) \\ SP \leftarrow (SP) - 1;  Push  (CCR) \\ SP \leftarrow (SP) - 1;  I \leftarrow 1 \\ PCH \leftarrow Interrupt  Vector  High  Byte \\ PCL \leftarrow Interrupt  Vector  Low  Byte \\ \end{array}$ | _ | _      | 1             | _        | _   | _   | INH                                   | 83                                 |                | 9                          |

| TAP                                                          | Transfer A to CCR                     | CCR ← (A)                                                                                                                                                                                                                                                                                                                                                                    | 1 | 1      | 1             | ‡        | 1   | ‡   | INH                                   | 84                                 |                | 2                          |

| TAX                                                          | Transfer A to X                       | X ← (A)                                                                                                                                                                                                                                                                                                                                                                      | - | -      | _             | -        | -   | -   | INH                                   | 97                                 |                | 1                          |

| TPA                                                          | Transfer CCR to A                     | $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                         | - | -      | _             | -        | -   | -   | INH                                   | 85                                 |                | 1                          |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP | Test for Negative or Zero             | (A) – \$00 or (X) – \$00 or (M) – \$00                                                                                                                                                                                                                                                                                                                                       | 0 | _      | _             | <b>‡</b> | Î   | -   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D | dd<br>ff<br>ff | 3<br>1<br>1<br>3<br>2<br>4 |

| TSX                                                          | Transfer SP to H:X                    | H:X ← (SP) + 1                                                                                                                                                                                                                                                                                                                                                               | - | -      | -             | -        | -   | -   | INH                                   | 95                                 |                | 2                          |

| TXA                                                          | Transfer X to A                       | A ← (X)                                                                                                                                                                                                                                                                                                                                                                      | - | -      | _             | -        | _   | -   | INH                                   | 9F                                 |                | 1                          |

| TXS                                                          | Transfer H:X to SP                    | (SP) ← (H:X) – 1                                                                                                                                                                                                                                                                                                                                                             | - | -      | _             | _        | _   | -   | INH                                   | 94                                 |                | 2                          |

| WAIT                                                         | Enable Interrupts; Wait for Interrupt | I bit ← 0; Inhibit CPU clocking until interrupted                                                                                                                                                                                                                                                                                                                            | - | _      | 0             | -        | -   | _   | INH                                   | 8F                                 |                | 1                          |

| Α     | Accumulator                                                         | n               | Any bit                                     |

|-------|---------------------------------------------------------------------|-----------------|---------------------------------------------|

| С     | Carry/borrow bit                                                    | opr             | Operand (one or two bytes)                  |

| CCR   | Condition code register                                             | PC              | Program counter                             |

| dd    | Direct address of operand                                           | PCH             | Program counter high byte                   |

| dd rr | Direct address of operand and relative offset of branch instruction | PCL             | Program counter low byte                    |

| DD    | Direct to direct addressing mode                                    | REL             | Relative addressing mode                    |

| DIR   | Direct addressing mode                                              | rel             | Relative program counter offset byte        |

| DIX+  | Direct to indexed with post increment addressing mode               | rr              | Relative program counter offset byte        |

| ee ff | High and low bytes of offset in indexed, 16-bit offset addressing   | SP1             | Stack pointer, 8-bit offset addressing mode |

| EXT   | Extended addressing mode                                            |                 | Stack pointer 16-bit offset addressing mode |

| ff    | Offset byte in indexed, 8-bit offset addressing                     | SP              | Stack pointer                               |

| Н     | Half-carry bit                                                      | U               | Undefined                                   |

| Н     | Index register high byte                                            | V               | Overflow bit                                |

| hh II | High and low bytes of operand address in extended addressing        | Χ               | Index register low byte                     |

|       | Interrupt mask                                                      | Z               | Zero bit                                    |

| ii    | Immediate operand byte                                              | &               | Logical AND                                 |

| IMD   | Immediate source to direct destination addressing mode              |                 | Logical OR                                  |

| IMM   | Immediate addressing mode                                           | $\oplus$        | Logical EXCLUSIVE OR                        |

| INH   | Inherent addressing mode                                            | ()              | Contents of                                 |

| IX    | Indexed, no offset addressing mode                                  | <del>-</del> () | Negation (two's complement)                 |

| IX+   | Indexed, no offset, post increment addressing mode                  | #`              | Immediate value                             |

| IX+D  | Indexed with post increment to direct addressing mode               | **              | Sign extend                                 |

| IX1   | Indexed, 8-bit offset addressing mode                               | $\leftarrow$    | Loaded with                                 |

| IX1+  | Indexed, 8-bit offset, post increment addressing mode               | ?               | If                                          |

| IX2   | Indexed, 16-bit offset addressing mode                              | :               | Concatenated with                           |

| M     | Memory location                                                     | <b>‡</b>        | Set or cleared                              |

| N     | Negative bit                                                        | _               | Not affected                                |

|       | -                                                                   |                 |                                             |

# 7.8 Opcode Map

See Table 7-2.

#### **Oscillator Module (OSC)**

Figure 11-3 shows how BUSCLKX4 is derived from INTCLK and OSC2 can output BUSCLKX4 by setting OSC2EN.

#### 11.3.2.1 Internal Oscillator Trimming

OSCTRIM allows a clock period adjustment of +127 and -128 steps. Increasing the OSCTRIM value increases the clock period, which decreases the clock frequency. Trimming allows the internal clock frequency to be fine tuned to the target frequency.

All devices are factory programmed with a trim value that is stored in FLASH memory at location \$FFC0. The trim value is not automatically loaded into the OSCTRIM register. User software must copy the trim value from \$FFC0 into OSCTRIM if needed. The factory trim value provides the accuracy required for communication using forced monitor mode. Some production programmers erase the factory trim value, so confirm with your programmer vendor that the trim value at \$FFC0 is preserved, or is re-trimmed. Trimming the device in the user application board will provide the most accurate trim value.

#### 11.3.2.2 Internal to External Clock Switching

When external clock source (external OSC, RC, or XTAL) is desired, the user must perform the following steps:

- 1. For external crystal circuits only, configure OSCOPT[1:0] to external crystal. To help precharge an external crystal oscillator, momentarily configure OSC2 as an output and drive it high for several cycles. This can help the crystal circuit start more robustly.

- 2. Configure OSCOPT[1:0] and ECFS[1:0] according to 11.8.1 Oscillator Status and Control Register. The oscillator module control logic will then enable OSC1 as an external clock input and, if the external crystal option is selected, OSC2 will also be enabled as the clock output. If RC oscillator option is selected, enabling the OSC2 output may change the bus frequency.

- Create a software delay to provide the stabilization time required for the selected clock source (crystal, resonator, RC). A good rule of thumb for crystal oscillators is to wait 4096 cycles of the crystal frequency; i.e., for a 4-MHz crystal, wait approximately 1 ms.

- 4. After the stabilization delay has elapsed, set ECGON.

After ECGON set is detected, the OSC module checks for oscillator activity by waiting two external clock rising edges. The OSC module then switches to the external clock. Logic provides a coherent transition. The OSC module first sets ECGST and then stops the internal oscillator.

#### 11.3.2.3 External to Internal Clock Switching

After following the procedures to switch to an external clock source, it is possible to go back to the internal source. By clearing the OSCOPT[1:0] bits and clearing the ECGON bit, the external circuit will be disengaged. The bus clock will be derived from the selected internal clock source based on the ICFS[1:0] bits.

#### 11.3.3 External Oscillator

The external oscillator option is designed for use when a clock signal is available in the application to provide a clock source to the MCU. The OSC1 pin is enabled as an input by the oscillator module. The clock signal is used directly to create BUSCLKX4 and also divided by two to create BUSCLKX2.

In this configuration, the OSC2 pin cannot output BUSCLKX4. The OSC2EN bit will be forced clear to enable alternative functions on the pin.

MC68HC908QB8 Data Sheet, Rev. 3

# **Chapter 12 Input/Output Ports (PORTS)**

#### 12.1 Introduction

The MC68HC908QB8, MC68HC908QB4 and MC68HC908QY8 have thirteen bidirectional pins and one input only pin.

#### NOTE

Connect any unused I/O pins to an appropriate logic level, either  $V_{\rm DD}$  or  $V_{\rm SS}$ . Although the I/O ports do not require termination for proper operation, termination reduces excess current consumption and the possibility of electrostatic damage.

#### 12.2 Port A

Port A is an 6-bit special function port that shares its pins with the keyboard interrupt (KBI) module (see Chapter 9 Keyboard Interrupt Module (KBI), the 4-channel timer interface module (TIM) (see Chapter 16 Timer Interface Module (TIM)), the 10-bit ADC (see Chapter 3 Analog-to-Digital Converter (ADC10) Module), the external interrupt (IRQ) pin (see Chapter 8 External Interrupt (IRQ)), the reset (RST) pin enabled using a configuration register (see Chapter 5 Configuration Register (CONFIG)) and the oscillator pins (see Chapter 11 Oscillator Module (OSC)).

Each port A pin also has a software configurable pullup device if the corresponding port pin is configured as an input port.

#### NOTE

PTA2 is input only.

When the IRQ function is enabled in the configuration register 2 (CONFIG2), bit 2 of the port A data register (PTA) will always read a logic 0. In this case, the BIH and BIL instructions can be used to read the logic level on the PTA2 pin. When the IRQ function is disabled, these instructions will behave as if the PTA2 pin is a logic 1. However, reading bit 2 of PTA will read the actual logic level on the pin.

#### **Enhanced Serial Communications Interface (ESCI) Module**

RST, IRQ: Pins have internal pull up device All port pins have programmable pull up device PTA[0:5]: Higher current sink and source capability

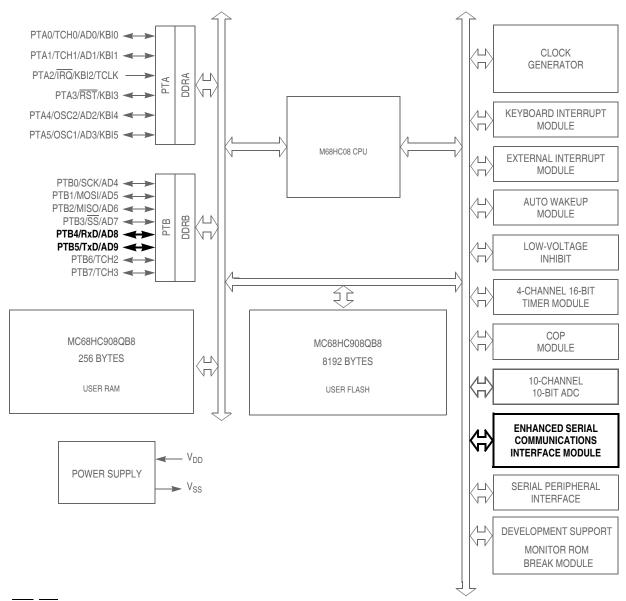

Figure 13-1. Block Diagram Highlighting ESCI Block and Pins

| RT8, RT9, and RT10 Samples | Data Bit Determination | Noise Flag |

|----------------------------|------------------------|------------|

| 000                        | 0                      | 0          |

| 001                        | 0                      | 1          |

| 010                        | 0                      | 1          |

| 011                        | 1                      | 1          |

| 100                        | 0                      | 1          |

| 101                        | 1                      | 1          |

Table 13-2. Data Bit Recovery

#### NOTE

1

1

1

0

110

111

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 13-3 summarizes the results of the stop bit samples.

| RT8, RT9, and RT10 Samples | Framing Error Flag | Noise Flag |

|----------------------------|--------------------|------------|

| 000                        | 1                  | 0          |

| 001                        | 1                  | 1          |

| 010                        | 1                  | 1          |

| 011                        | 0                  | 1          |

| 100                        | 1                  | 1          |

| 101                        | 0                  | 1          |

| 110                        | 0                  | 1          |

| 111                        | 0                  | 0          |

Table 13-3. Stop Bit Recovery

#### 13.3.3.4 Framing Errors

If the data recovery logic does not detect a 1 where the stop bit should be in an incoming character, it sets the framing error bit, FE, in SCS1. A break character also sets the FE bit because a break character has no stop bit. The FE bit is set at the same time that the SCRF bit is set.

#### 13.3.3.5 Baud Rate Tolerance

A transmitting device may be operating at a baud rate below or above the receiver baud rate. Accumulated bit time misalignment can cause one of the three stop bit data samples to fall outside the actual stop bit. Then a noise error occurs. If more than one of the samples is outside the stop bit, a framing error occurs. In most applications, the baud rate tolerance is much more than the degree of misalignment that is likely to occur.

As the receiver samples an incoming character, it resynchronizes the RT clock on any valid falling edge within the character. Resynchronization within characters corrects misalignments between transmitter bit times and receiver bit times.

MC68HC908QB8 Data Sheet, Rev. 3

#### TC — Transmission Complete Bit

This read-only bit is set when the SCTE bit is set, and no data, preamble, or break character is being transmitted. TC generates an ESCI transmitter interrupt request if the TCIE bit in SCC2 is also set. TC is cleared automatically when data, preamble, or break is queued and ready to be sent. There may be up to 1.5 transmitter clocks of latency between queueing data, preamble, and break and the transmission actually starting.

- 1 = No transmission in progress

- 0 = Transmission in progress

#### SCRF — ESCI Receiver Full Bit

This clearable, read-only bit is set when the data in the receive shift register transfers to the ESCI data register. SCRF can generate an ESCI receiver interrupt request. When the SCRIE bit in SCC2 is set the SCRF generates a interrupt request. In normal operation, clear the SCRF bit by reading SCS1 with SCRF set and then reading the SCDR.

- 1 = Received data available in SCDR

- 0 = Data not available in SCDR

#### IDLE — Receiver Idle Bit

This clearable, read-only bit is set when 10 or 11 consecutive 1s appear on the receiver input. IDLE generates an ESCI receiver interrupt request if the ILIE bit in SCC2 is also set. Clear the IDLE bit by reading SCS1 with IDLE set and then reading the SCDR. After the receiver is enabled, it must receive a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit.

- 1 = Receiver input idle

- 0 = Receiver input active (or idle since the IDLE bit was cleared)

#### **OR** — Receiver Overrun Bit

This clearable, read-only bit is set when software fails to read the SCDR before the receive shift register receives the next character. The OR bit generates an ESCI error interrupt request if the ORIE bit in SCC3 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading SCS1 with OR set and then reading the SCDR.

- 1 = Receive shift register full and SCRF = 1

- 0 = No receiver overrun

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 13-13 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

In applications that are subject to software latency or in which it is important to know which byte is lost due to an overrun, the flag-clearing routine can check the OR bit in a second read of SCS1 after reading the data register.

#### NF — Receiver Noise Flag Bit

This clearable, read-only bit is set when the ESCI detects noise on the RxD pin. NF generates an NF interrupt request if the NEIE bit in SCC3 is also set. Clear the NF bit by reading SCS1 and then reading the SCDR.

- 1 = Noise detected

- 0 = No noise detected

#### **Enhanced Serial Communications Interface (ESCI) Module**

# **Table 13-10. ESCI Baud Rate Selection Examples**

| PDS[2:1:0] | PSSB[4:3:2:1:0] | SCP[1:0] | Prescaler<br>Divisor<br>(BPD) | SCR[2:1:0] | Baud Rate<br>Divisor<br>(BD) | Baud Rate<br>(f <sub>Bus</sub> = 4.9152 MHz) |

|------------|-----------------|----------|-------------------------------|------------|------------------------------|----------------------------------------------|

| 0 0 0      | XXXXX           | 0 0      | 1                             | 0 0 0      | 1                            | 76,800                                       |

| 1 1 1      | 0 0 0 0 0       | 0 0      | 1                             | 0 0 0      | 1                            | 9600                                         |

| 1 1 1      | 0 0 0 0 1       | 0 0      | 1                             | 0 0 0      | 1                            | 9562.65                                      |

| 1 1 1      | 0 0 0 1 0       | 0 0      | 1                             | 0 0 0      | 1                            | 9525.58                                      |

| 1 1 1      | 11111           | 0 0      | 1                             | 0 0 0      | 1                            | 8563.07                                      |

| 0 0 0      | XXXXX           | 0 0      | 1                             | 0 0 1      | 2                            | 38,400                                       |

| 0 0 0      | XXXXX           | 0 0      | 1                             | 0 1 0      | 4                            | 19,200                                       |

| 0 0 0      | XXXXX           | 0 0      | 1                             | 0 1 1      | 8                            | 9600                                         |

| 0 0 0      | XXXXX           | 0 0      | 1                             | 1 0 0      | 16                           | 4800                                         |

| 0 0 0      | XXXXX           | 0 0      | 1                             | 1 0 1      | 32                           | 2400                                         |

| 0 0 0      | XXXXX           | 0 0      | 1                             | 1 1 0      | 64                           | 1200                                         |

| 0 0 0      | XXXXX           | 0 0      | 1                             | 1 1 1      | 128                          | 600                                          |

| 0 0 0      | XXXXX           | 0 1      | 3                             | 0 0 0      | 1                            | 25,600                                       |

| 0 0 0      | X X X X X       | 0 1      | 3                             | 0 0 1      | 2                            | 12,800                                       |

| 0 0 0      | XXXXX           | 0 1      | 3                             | 0 1 0      | 4                            | 6400                                         |

| 0 0 0      | XXXXX           | 0 1      | 3                             | 0 1 1      | 8                            | 3200                                         |

| 0 0 0      | XXXXX           | 0 1      | 3                             | 1 0 0      | 16                           | 1600                                         |

| 0 0 0      | XXXXX           | 0 1      | 3                             | 1 0 1      | 32                           | 800                                          |

| 0 0 0      | XXXXX           | 0 1      | 3                             | 1 1 0      | 64                           | 400                                          |

| 0 0 0      | X X X X X       | 0 1      | 3                             | 1 1 1      | 128                          | 200                                          |

| 0 0 0      | XXXXX           | 1 0      | 4                             | 0 0 0      | 1                            | 19,200                                       |

| 0 0 0      | XXXXX           | 1 0      | 4                             | 0 0 1      | 2                            | 9600                                         |

| 0 0 0      | X X X X X       | 1 0      | 4                             | 0 1 0      | 4                            | 4800                                         |

| 0 0 0      | XXXXX           | 1 0      | 4                             | 0 1 1      | 8                            | 2400                                         |

| 0 0 0      | XXXXX           | 1 0      | 4                             | 1 0 0      | 16                           | 1200                                         |

| 0 0 0      | XXXXX           | 1 0      | 4                             | 1 0 1      | 32                           | 600                                          |

| 0 0 0      | XXXXX           | 1 0      | 4                             | 1 1 0      | 64                           | 300                                          |

| 0 0 0      | XXXXX           | 1 0      | 4                             | 1 1 1      | 128                          | 150                                          |

| 0 0 0      | XXXXX           | 1 1      | 13                            | 0 0 0      | 1                            | 5908                                         |

| 0 0 0      | XXXXX           | 1 1      | 13                            | 0 0 1      | 2                            | 2954                                         |

| 0 0 0      | XXXXX           | 1 1      | 13                            | 0 1 0      | 4                            | 1477                                         |

| 0 0 0      | XXXXX           | 1 1      | 13                            | 0 1 1      | 8                            | 739                                          |

| 0 0 0      | XXXXX           | 1 1      | 13                            | 1 0 0      | 16                           | 369                                          |

| 0 0 0      | XXXXX           | 1 1      | 13                            | 1 0 1      | 32                           | 185                                          |

| 0 0 0      | XXXXX           | 1 1      | 13                            | 1 1 0      | 64                           | 92                                           |

| 0 0 0      | XXXXX           | 1 1      | 13                            | 1 1 1      | 128                          | 46                                           |

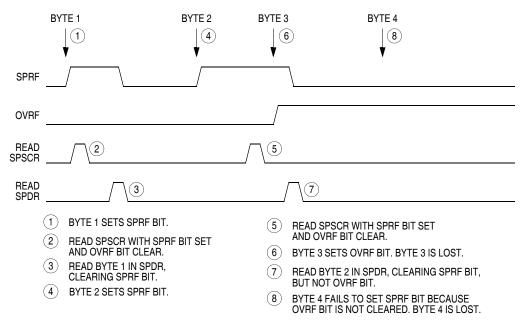

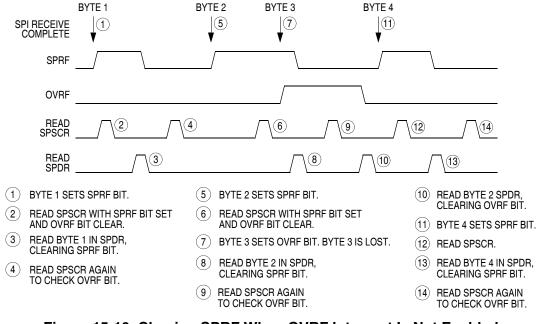

In this case, an overflow can be missed easily. Because no more SPRF interrupts can be generated until this OVRF is serviced, it is not obvious that bytes are being lost as more transmissions are completed. To prevent this, either enable the OVRF interrupt or do another read of the SPSCR following the read of the SPDR. This ensures that the OVRF was not set before the SPRF was cleared and that future transmissions can set the SPRF bit. Figure 15-10 illustrates this process. Generally, to avoid this second SPSCR read, enable OVRF by setting the ERRIE bit.

Figure 15-9. Missed Read of Overflow Condition

Figure 15-10. Clearing SPRF When OVRF Interrupt Is Not Enabled

MC68HC908QB8 Data Sheet, Rev. 3

Freescale Semiconductor

165

In a slave SPI (MSTR = 0), MODF generates an SPI receiver/error interrupt request if the ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort the SPI transmission by clearing the SPE bit of the slave.

#### NOTE

A high on the  $\overline{SS}$  pin of a slave SPI puts the MISO pin in a high impedance state. Also, the slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

To clear the MODF flag, read the SPSCR with the MODF bit set and then write to the SPCR register. This entire clearing mechanism must occur with no MODF condition existing or else the flag is not cleared.

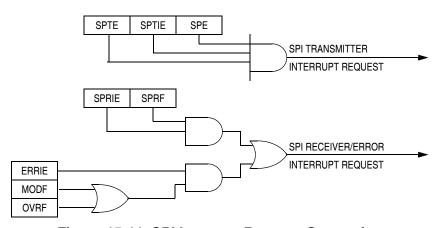

# 15.4 Interrupts

Four SPI status flags can be enabled to generate interrupt requests. See Table 15-1.

| Flag                      | Request                                                |

|---------------------------|--------------------------------------------------------|

| SPTE<br>Transmitter empty | SPI transmitter interrupt request (SPTIE = 1, SPE = 1) |

| SPRF<br>Receiver full     | SPI receiver interrupt request (SPRIE = 1)             |

| OVRF<br>Overflow          | SPI receiver/error interrupt request (ERRIE = 1)       |

| MODF<br>Mode fault        | SPI receiver/error interrupt request (ERRIE = 1)       |

Table 15-1. SPI Interrupts

Reading the SPI status and control register with SPRF set and then reading the receive data register clears SPRF. The clearing mechanism for the SPTE flag is requires only a write to the transmit data register.

The SPI transmitter interrupt enable bit (SPTIE) enables the SPTE flag to generate transmitter interrupt requests, provided that the SPI is enabled (SPE = 1).

The SPI receiver interrupt enable bit (SPRIE) enables SPRF to generate receiver interrupt requests, regardless of the state of SPE. See Figure 15-11.

Figure 15-11. SPI Interrupt Request Generation

MC68HC908QB8 Data Sheet, Rev. 3

#### **MODF** — Mode Fault Bit

This clearable, read-only flag is set in a slave SPI if the  $\overline{SS}$  pin goes high during a transmission with MODFEN set. In a master SPI, the MODF flag is set if the  $\overline{SS}$  pin goes low at any time with the MODFEN bit set. Clear MODF by reading the SPI status and control register (SPSCR) with MODF set and then writing to the SPI control register (SPCR).

- $1 = \overline{SS}$  pin at inappropriate logic level

- $0 = \overline{SS}$  pin at appropriate logic level

#### SPTE — SPI Transmitter Empty Bit

This clearable, read-only flag is set each time the transmit data register transfers a byte into the shift register. SPTE generates an SPTE interrupt request if the SPTIE bit in the SPI control register is also set.

#### NOTE

Do not write to the SPI data register unless SPTE is high.

During an SPTE interrupt, user software can clear SPTE by writing to the transmit data register.

- 1 = Transmit data register empty

- 0 = Transmit data register not empty

#### **MODFEN** — Mode Fault Enable Bit

This read/write bit, when set, allows the MODF flag to be set. If the MODF flag is set, clearing MODFEN does not clear the MODF flag. If the SPI is enabled as a master and the MODFEN bit is 0, then the SS pin is available as a general-purpose I/O.

If the MODFEN bit is 1, then this pin is not available as a general-purpose I/O. When the SPI is enabled as a slave, the  $\overline{SS}$  pin is not available as a general-purpose I/O regardless of the value of MODFEN. See 15.7.4 SS (Slave Select).

If the MODFEN bit is 0, the level of the  $\overline{SS}$  pin does not affect the operation of an enabled SPI configured as a master. For an enabled SPI configured as a slave, having MODFEN low only prevents the MODF flag from being set. It does not affect any other part of SPI operation. See 15.3.6.2 Mode Fault Error.

#### SPR1 and SPR0 — SPI Baud Rate Select Bits

In master mode, these read/write bits select one of four baud rates as shown in Table 15-3. SPR1 and SPR0 have no effect in slave mode.

Table 15-3. SPI Master Baud Rate Selection

| SPR1 and SPR0 | Baud Rate Divisor (BD) |

|---------------|------------------------|

| 00            | 2                      |

| 01            | 8                      |

| 10            | 32                     |

| 11            | 128                    |

Use this formula to calculate the SPI baud rate:

Baud rate =

$$\frac{BUSCLK}{BD}$$

#### **Timer Interface Module (TIM)**

channel, the TIM can set, clear, or toggle the channel pin. Output compares can be enabled to generate interrupt requests.

#### 16.3.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 16.3.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

- When changing to a smaller value, enable channel x output compare interrupts and write the new

value in the output compare interrupt routine. The output compare interrupt occurs at the end of

the current output compare pulse. The interrupt routine has until the end of the counter overflow

period to write the new value.

- When changing to a larger output compare value, enable TIM overflow interrupts and write the new

value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the

current counter overflow period. Writing a larger value in an output compare interrupt routine (at

the end of the current pulse) could cause two output compares to occur in the same counter

overflow period.

#### 16.3.3.2 Buffered Output Compare

Channels 0 and 1 can be linked to form a buffered output compare channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The output compare value in the TIM channel 0 registers initially controls the output on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the output after the TIM overflows. At each subsequent overflow, the TIM channel registers (0 or 1) that control the output are the ones written to last. TSC0 controls and monitors the buffered output compare function, and TIM channel 1 status and control register (TSC1) is unused. While the MS0B bit is set, the channel 1 pin, TCH1, is available as a general-purpose I/O pin.

Channels 2 and 3 can be linked to form a buffered output compare channel whose output appears on the TCH2 pin. The TIM channel registers of the linked pair alternately control the output.

Setting the MS2B bit in TIM channel 2 status and control register (TSC2) links channel 2 and channel 3. The output compare value in the TIM channel 2 registers initially controls the output on the TCH2 pin. Writing to the TIM channel 3 registers enables the TIM channel 3 registers to synchronously control the output after the TIM overflows. At each subsequent overflow, the TIM channel registers (2 or 3) that control the output are the ones written to last. TSC2 controls and monitors the buffered output compare function, and TIM channel 3 status and control register (TSC3) is unused. While the MS2B bit is set, the channel 3 pin, TCH3, is available as a general-purpose I/O pin.

#### NOTE

In buffered output compare operation, do not write new output compare values to the currently active channel registers. User software should track

MC68HC908QB8 Data Sheet, Rev. 3

**Timer Interface Module (TIM)**

# 16.4 Interrupts

The following TIM sources can generate interrupt requests:

- TIM overflow flag (TOF) The TOF bit is set when the counter reaches the modulo value programmed in the TIM counter modulo registers. The TIM overflow interrupt enable bit, TOIE, enables TIM overflow interrupt requests. TOF and TOIE are in the TSC register.

- TIM channel flags (CH3F:CH0F) The CHxF bit is set when an input capture or output compare

occurs on channel x. Channel x TIM interrupt requests are controlled by the channel x interrupt

enable bit, CHxIE. Channel x TIM interrupt requests are enabled when CHxIE =1. CHxF and

CHxIE are in the TSCx register.

#### 16.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 16.5.1 Wait Mode

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

#### 16.5.2 Stop Mode

The TIM module is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions. TIM operation resumes after an external interrupt. If stop mode is exited by reset, the TIM is reset.

# 16.6 TIM During Break Interrupts

A break interrupt stops the counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

182 Freescale Semiconductor

MC68HC908QB8 Data Sheet, Rev. 3

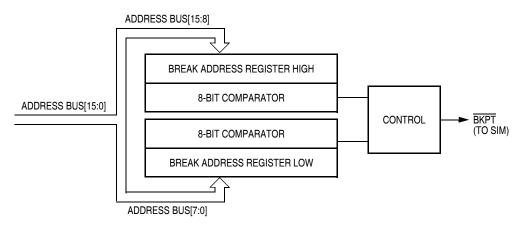

Figure 17-2. Break Module Block Diagram

The break interrupt timing is:

- When a break address is placed at the address of the instruction opcode, the instruction is not executed until after completion of the break interrupt routine.