Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                     |  |  |  |

|----------------------------|---------------------------------------------------------------------|--|--|--|

| Product Status             | Obsolete                                                            |  |  |  |

| Core Processor             | HC08                                                                |  |  |  |

| Core Size                  | 8-Bit                                                               |  |  |  |

| Speed                      | 8MHz                                                                |  |  |  |

| Connectivity               | SCI, SPI                                                            |  |  |  |

| Peripherals                | LVD, POR, PWM                                                       |  |  |  |

| Number of I/O              | 13                                                                  |  |  |  |

| Program Memory Size        | 8KB (8K x 8)                                                        |  |  |  |

| Program Memory Type        | FLASH                                                               |  |  |  |

| EEPROM Size                | -                                                                   |  |  |  |

| RAM Size                   | 256 x 8                                                             |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                         |  |  |  |

| Data Converters            | A/D 10x10b                                                          |  |  |  |

| Oscillator Type            | Internal                                                            |  |  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                     |  |  |  |

| Mounting Type              | Through Hole                                                        |  |  |  |

| Package / Case             | 16-DIP (0.300", 7.62mm)                                             |  |  |  |

| Supplier Device Package    | 16-PDIP                                                             |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcl908qb8pe |  |  |  |

# Chapter 11 Oscillator Module (OSC)

| 11.3 Functional Description       93         11.3.1 Internal Signal Definitions       95         11.3.1.1 Oscillator Enable Signal (SIMOSCEN)       95         11.3.1.2 XTAL Oscillator Clock (XTALCLK)       95         11.3.1.3 RC Oscillator Clock (RCCLK)       95         11.3.1.4 Internal Oscillator Clock (INTCLK)       95         11.3.1.5 Bus Clock Times 4 (BUSCLKX4)       95         11.3.1.6 Bus Clock Times 2 (BUSCLKX2)       95         11.3.2 Internal Oscillator       95         11.3.2.1 Internal Oscillator Trimming       96         11.3.2.2 Internal to External Clock Switching       96         11.3.2.3 External to Internal Clock Switching       96         11.3.4 XTAL Oscillator       96         11.3.5 RC Oscillator       97         11.3.5 RC Oscillator       98         11.5 Low-Power Modes       98         11.5.1 Wait Mode       98         11.5.2 Stop Mode       98                                                                                                                                                                                                                                                                                                | 11.1 Introduction                           | . 93 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|

| 11.3.1       Internal Signal Definitions       95         11.3.1.1       Oscillator Enable Signal (SIMOSCEN)       95         11.3.1.2       XTAL Oscillator Clock (XTALCLK)       95         11.3.1.3       RC Oscillator Clock (RCCLK)       95         11.3.1.4       Internal Oscillator Clock (INTCLK)       95         11.3.1.6       Bus Clock Times 2 (BUSCLKX4)       95         11.3.2.1       Internal Oscillator       95         11.3.2.2       Internal Oscillator       95         11.3.2.2.2       Internal to External Clock Switching       96         11.3.2.3       External Sternal Oscillator       96         11.3.4       XTAL Oscillator       96         11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       98         11.5.1       Wait Mode       98         11.5.1       Wait Mode       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.7.2       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Status and Control Register       100         11.8.1       Oscillator Trim Register (OSCTRIM)       101         Chapter 12                                                       | 11.2 Features                               | . 93 |

| 11.3.1       Internal Signal Definitions       95         11.3.1.1       Oscillator Enable Signal (SIMOSCEN)       95         11.3.1.2       XTAL Oscillator Clock (XTALCLK)       95         11.3.1.3       RC Oscillator Clock (RCCLK)       95         11.3.1.4       Internal Oscillator Clock (INTCLK)       95         11.3.1.6       Bus Clock Times 2 (BUSCLKX4)       95         11.3.2.1       Internal Oscillator       95         11.3.2.2       Internal Oscillator       95         11.3.2.2.2       Internal to External Clock Switching       96         11.3.2.3       External Sternal Oscillator       96         11.3.4       XTAL Oscillator       96         11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       98         11.5.1       Wait Mode       98         11.5.1       Wait Mode       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.7.2       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Status and Control Register       100         11.8.1       Oscillator Trim Register (OSCTRIM)       101         Chapter 12                                                       | 11.3 Functional Description                 | . 93 |

| 11.3.1.1 Oscillator Enable Signal (SIMOSCEN)       95         11.3.1.2 XTAL Oscillator Clock (XTALCLK)       95         11.3.1.3 RC Oscillator Clock (RCCLK)       95         11.3.1.4 Internal Oscillator Clock (INTCLK)       95         11.3.1.5 Bus Clock Times 2 (BUSCLKX4)       95         11.3.1.6 Bus Clock Times 2 (BUSCLKX2)       95         11.3.2.1 Internal Oscillator       95         11.3.2.2 Internal Oscillator Trimming       96         11.3.2.3 External to Internal Clock Switching       96         11.3.2.3 External to Internal Clock Switching       96         11.3.4 XTAL Oscillator       96         11.3.5 RC Oscillator       96         11.4 Interrupts       98         11.5 Low-Power Modes       98         11.5.1 Wait Mode       98         11.5.2 Stop Mode       98         11.6 OSC During Break Interrupts       99         11.7.1 Oscillator Input Pin (OSC1)       99         11.8 Registers       100         11.8.1 Oscillator Status and Control Register       100         11.8.2 Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1 Introduction       103         12.2.2 Port A       104     < | · · · · · · · · · · · · · · · · · · ·       |      |

| 11.3.1.2       XTAL Oscillator Clock (XTALCLK)       95         11.3.1.3       RC Oscillator Clock (RCCLK)       95         11.3.1.4       Internal Oscillator Clock (INTCLK)       95         11.3.1.5       Bus Clock Times 4 (BUSCLKX4)       95         11.3.1.6       Bus Clock Times 2 (BUSCLKX2)       95         11.3.2.1       Internal Oscillator       95         11.3.2.2.1       Internal Oscillator Trimming       96         11.3.2.2.2       Internal to External Clock Switching       96         11.3.3.3       External Oscillator       96         11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       97         11.4.       Interrupts       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.5.1       Wait Mode       98         11.6       OSC During Break Interrupts       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Status and Control Register       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Port A Data Register       104         12.2.1       Port A                                          |                                             |      |

| 11.3.1.4       Internal Oscillator Clock (INTCLK)       95         11.3.1.5       Bus Clock Times 4 (BUSCLKX4)       95         11.3.2       Internal Oscillator       95         11.3.2.1       Internal Oscillator Trimming       96         11.3.2.2.1       Internal to External Clock Switching       96         11.3.2.3       External to Internal Clock Switching       96         11.3.4       XTAL Oscillator       96         11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       97         11.3.1       Value Mode       98         11.5.1       Wait Mode       98         11.5.1       Wait Mode       98         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.1       Oscillator Status and Control Register       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12 Input/Output Ports (PORTS)         12.2.1       Port A Data Register       104         12.2.2       Port A Input Pullup Enable Register       105         12.3.3                                       |                                             |      |

| 11.3.1.5       Bus Clock Times 4 (BUSCLKX4)       95         11.3.1.6       Bus Clock Times 2 (BUSCLKX2)       95         11.3.2.1       Internal Oscillator Trimming       96         11.3.2.2.1       Internal to External Clock Switching       96         11.3.2.3       External to Internal Clock Switching       96         11.3.3       External Oscillator       96         11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       97         11.3.1       Interrupts       98         11.5       Low-Power Modes       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.5       Vait Mode       98         11.5       Vos During Break Interrupts       99         11.7       Oscillator Input Pin (OSC1)       99         11.7       Oscillator Oscillator Input Pin (OSC2)       99         11.8.1       Oscillator Status and Control Regi                                                                                      | 11.3.1.3 RC Oscillator Clock (RCCLK)        | . 95 |

| 11.3.1.6       Bus Clock Times 2 (BUSCLKX2)       95         11.3.2       Internal Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11.3.1.4 Internal Oscillator Clock (INTCLK) | . 95 |

| 11.3.2 Internal Oscillator Trimming       95         11.3.2.2 Internal Oscillator Trimming       96         11.3.2.3 External to Internal Clock Switching       96         11.3.3 External Oscillator       96         11.3.4 XTAL Oscillator       97         11.3.5 RC Oscillator       97         11.4 Interrupts       98         11.5 Low-Power Modes       98         11.5.1 Wait Mode       98         11.5.2 Stop Mode       98         11.6 OSC During Break Interrupts       99         11.7 I/O Signals       99         11.7.1 Oscillator Input Pin (OSC1)       99         11.8 Registers       100         11.8.1 Oscillator Status and Control Register       100         11.8.2 Oscillator Trim Register (OSCTRIM)       101         Chapter 12 Input/Output Ports (PORTS)         12.1 Introduction       103         12.2.2 Port A       103         12.2.3 Port A Data Register       104         12.2.4 Port A Data Register A       104         12.2.3 Port B Input Pullup Enable Register       105         12.3.1 Port B Data Register       106         12.3.2 Data Direction Register B       106         12.3.3 Port B Input Pullup Enable Register       106                         | 11.3.1.5 Bus Clock Times 4 (BUSCLKX4)       | . 95 |

| 11.3.2.1       Internal Oscillator Trimming       96         11.3.2.2       Internal to External Clock Switching       96         11.3.2.3       External to Internal Clock Switching       96         11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       98         11.4       Interrupts       98         11.5       Low-Power Modes       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.5.1       Vo Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12 Input/Output Ports (PORTS)         12.1       Introduction       103         12.2.2       Port A       103         12.2.3       Port A Data Register       104         12.2.3       Port A Summary Table       105         12.3.1       Port B Data Register       106         12.3.2       Port B D                                                                                | 11.3.1.6 Bus Clock Times 2 (BUSCLKX2)       | . 95 |

| 11.3.2.2       Internal to External Clock Switching.       96         11.3.2.3       External Oscillator       96         11.3.3       External Oscillator       96         11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       98         11.4       Interrupts       98         11.5       Low-Power Modes       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.6       OSC During Break Interrupts       99         11.7       Vo Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2.1       Port A       103         12.2.2       Data Direction Register       104         12.2.3       Port A Input Pullup Enable Register       105         12.3.1       Port B Data Register       106                                                                                                | 11.3.2 Internal Oscillator                  | . 95 |

| 11.3.2.3       External Oscillator       96         11.3.3       External Oscillator       96         11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       98         11.4       Interrupts       98         11.5       Low-Power Modes       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.6       OSC During Break Interrupts       99         11.7       Vo Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12 Input/Output Ports (PORTS)         12.1       Introduction       103         12.2.1       Port A Data Register       104         12.2.2       Port A Input Pullup Enable Register       105         12.2.4       Port A Summary Table       106         12.3.1       Port B Data Register       106         12.3.2       Port B Data Register </td <td>11.3.2.1 Internal Oscillator Trimming</td> <td>. 96</td>                | 11.3.2.1 Internal Oscillator Trimming       | . 96 |

| 11.3.3       External Oscillator       96         11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       98         11.4       Interrupts       98         11.5       Low-Power Modes       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.6       OSC During Break Interrupts       99         11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A       104         12.2.3       Port B Input Pullup Enable Register       105         12.3.1       Port B Data Register       106         12.3.2 <t< td=""><td></td><td></td></t<>                                                                             |                                             |      |

| 11.3.4       XTAL Oscillator       97         11.3.5       RC Oscillator       98         11.4       Interrupts       98         11.5       Low-Power Modes       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.6       OSC During Break Interrupts       99         11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A       104         12.2.3       Port A Input Pullup Enable Register       105         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B       107         12.3.3       Port B Input Pullup Enable Register       108 </td <td></td> <td></td>                                                                  |                                             |      |

| 11.3.5       RC Oscillator       98         11.4       Interrupts       98         11.5       Low-Power Modes       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.6       OSC During Break Interrupts       99         11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12 Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A       104         12.2.3       Port A Input Pullup Enable Register       105         12.2.4       Port B Data Register       106         12.3.1       Port B Data Register B       106         12.3.2       Data Direction Register B       107         12.3.3       Port B Input Pull                                                                                |                                             |      |

| 11.4       Interrupts       98         11.5       Low-Power Modes       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.6       OSC During Break Interrupts       99         11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A       104         12.2.3       Port B Input Pullup Enable Register       105         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B       106         12.3.3       Port B Input Pullup Enable Register       108                                                                                                                                              |                                             |      |

| 11.5       Low-Power Modes       98         11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.6       OSC During Break Interrupts       99         11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3.1       Port B Data Register       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108<                                                                       | 11.3.5 RC Oscillator                        | . 98 |

| 11.5.1       Wait Mode       98         11.5.2       Stop Mode       98         11.6       OSC During Break Interrupts       99         11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A       104         12.2.1       Port A Input Pullup Enable Register       105         12.2.4       Port A Summary Table       106         12.3       Port B       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B       107         12.3.3       Port B Input Pullup Enable Register       108                                                                                                                                         | 11.4 Interrupts                             | . 98 |

| 11.5.2       Stop Mode       98         11.6       OSC During Break Interrupts       99         11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A       104         12.2.3       Port A Input Pullup Enable Register       105         12.3.4       Port B Summary Table       106         12.3.5       Port B Data Register       106         12.3.2       Data Direction Register B       107         12.3.3       Port B Input Pullup Enable Register       108                                                                                                                                                                                                                     | 11.5 Low-Power Modes                        | . 98 |

| 11.6       OSC During Break Interrupts       99         11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Data Direction Register A       104         12.2.3       Port A Input Pullup Enable Register       105         12.2.4       Port A Summary Table       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B       107         12.3.3       Port B Input Pullup Enable Register       108                                                                                                                                                                                                                                                        | 11.5.1 Wait Mode                            | . 98 |

| 11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                | 11.5.2 Stop Mode                            | . 98 |

| 11.7       I/O Signals       99         11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                | 11.6 OSC During Break Interrupts            | . 99 |

| 11.7.1       Oscillator Input Pin (OSC1)       99         11.7.2       Oscillator Output Pin (OSC2)       99         11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         11.8.2       Oscillator Trim Register (OSCTRIM)       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A       104         12.2.3       Port A Input Pullup Enable Register       105         12.2.4       Port A Summary Table       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B       107         12.3.3       Port B Input Pullup Enable Register       108                                                                                                                                                                                                                                                                                                                                                             | ·                                           |      |

| 11.7.2       Oscillator Output Pin (OSC2).       99         11.8       Registers.       100         11.8.1       Oscillator Status and Control Register.       100         11.8.2       Oscillator Trim Register (OSCTRIM).       101         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A.       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                        |                                             |      |

| 11.8       Registers       100         11.8.1       Oscillator Status and Control Register       100         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A.       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |      |

| 11.8.1       Oscillator Status and Control Register       100         Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A       104         12.2.3       Port A Input Pullup Enable Register       105         12.2.4       Port A Summary Table       106         12.3       Port B       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B       107         12.3.3       Port B Input Pullup Enable Register       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                             |      |

| Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A       104         12.2.3       Port A Input Pullup Enable Register       105         12.2.4       Port A Summary Table       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B       107         12.3.3       Port B Input Pullup Enable Register       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                             |      |

| Chapter 12         Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A.       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |      |

| Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Those Community (Continuity)                |      |

| Input/Output Ports (PORTS)         12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Chanter 12                                  |      |

| 12.1       Introduction       103         12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • • • • • • • • • • • • • • • • • • •       |      |

| 12.2       Port A       103         12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,                                           | 102  |

| 12.2.1       Port A Data Register       104         12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |      |

| 12.2.2       Data Direction Register A.       104         12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                             |      |

| 12.2.3       Port A Input Pullup Enable Register.       105         12.2.4       Port A Summary Table.       106         12.3       Port B.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |      |

| 12.2.4       Port A Summary Table.       106         12.3       Port B.       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register.       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             |      |

| 12.3       Port B       106         12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B       107         12.3.3       Port B Input Pullup Enable Register       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |      |

| 12.3.1       Port B Data Register       106         12.3.2       Data Direction Register B.       107         12.3.3       Port B Input Pullup Enable Register       108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |      |

| 12.3.2Data Direction Register B.10712.3.3Port B Input Pullup Enable Register.108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |      |

| 12.3.3 Port B Input Pullup Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $oldsymbol{\circ}$                          |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                             |      |

| 12.3.4 Port B Summary Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12.5.4 POIL B Summary Table                 | 108  |

# Chapter 13

MC68HC908QB8 Data Sheet, Rev. 3

#### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module.

- 1 = LVI module resets disabled

- 0 = LVI module resets enabled

#### LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module.

- 1 = LVI module power disabled

- 0 = LVI module power enabled

## LVITRIP — LVI Trip Point Selection Bit

LVITRIP selects the voltage operating mode of the LVI module. The voltage mode selected for the LVI should match the operating  $V_{DD}$  for the LVI's voltage trip points for each of the modes.

- 1 = LVI operates for a 5-V protection

- 0 = LVI operates for a 3-V protection

#### NOTE

The LVITRIP bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

#### SSREC — Short Stop Recovery Bit

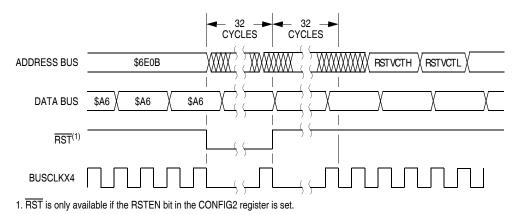

SSREC enables the CPU to exit stop mode with a delay of 32 BUSCLKX4 cycles instead of a 4096 BUSCLKX4 cycle delay.

- 1 = Stop mode recovery after 32 BUSCLKX4 cycles

- 0 = Stop mode recovery after 4096 BUSCLKX4 cycles

#### NOTE

Exiting stop mode by an LVI reset will result in the long stop recovery.

When using the LVI during normal operation but disabling during stop mode, the LVI will have an enable time of  $t_{\rm EN}$ . The system stabilization time for power-on reset and long stop recovery (both 4096 BUSCLKX4 cycles) gives a delay longer than the LVI enable time for these startup scenarios. There is no period where the MCU is not protected from a low-power condition. However, when using the short stop recovery configuration option, the 32 BUSCLKX4 delay must be greater than the LVI's turn on time to avoid a period in startup where the LVI is not protecting the MCU.

#### STOP — STOP Instruction Enable Bit

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

#### COPD — COP Disable Bit

COPD disables the COP module.

- 1 = COP module disabled

- 0 = COP module enabled

#### **Keyboard Interrupt Module (KBI)**

## 9.3.2 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pullup or pulldown device to pull the pin to its deasserted level. Therefore a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting IMASKK in KBSCR.

- 2. Enable the KBI polarity by setting the appropriate KBIPx bits in KBIPR.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in KBIER.

- 4. Write to ACKK in KBSCR to clear any false interrupts.

- 5. Clear IMASKK.

An interrupt signal on an edge sensitive pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge and level sensitive pin must be acknowledged after a delay that depends on the external load.

## 9.4 Interrupts

The following KBI source can generate interrupt requests:

Keyboard flag (KEYF) — The KEYF bit is set when any enabled KBI pin is asserted based on the KBI mode and pin polarity. The keyboard interrupt mask bit, IMASKK, is used to enable or disable KBI interrupt requests.

## 9.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 9.5.1 Wait Mode

The KBI module remains active in wait mode. Clearing IMASKK in KBSCR enables keyboard interrupt requests to bring the MCU out of wait mode.

## 9.5.2 Stop Mode

The KBI module remains active in stop mode. Clearing IMASKK in KBSCR enables keyboard interrupt requests to bring the MCU out of stop mode.

# 9.6 KBI During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

#### **Oscillator Module (OSC)**

Figure 11-3 shows how BUSCLKX4 is derived from INTCLK and OSC2 can output BUSCLKX4 by setting OSC2EN.

## 11.3.2.1 Internal Oscillator Trimming

OSCTRIM allows a clock period adjustment of +127 and -128 steps. Increasing the OSCTRIM value increases the clock period, which decreases the clock frequency. Trimming allows the internal clock frequency to be fine tuned to the target frequency.

All devices are factory programmed with a trim value that is stored in FLASH memory at location \$FFC0. The trim value is not automatically loaded into the OSCTRIM register. User software must copy the trim value from \$FFC0 into OSCTRIM if needed. The factory trim value provides the accuracy required for communication using forced monitor mode. Some production programmers erase the factory trim value, so confirm with your programmer vendor that the trim value at \$FFC0 is preserved, or is re-trimmed. Trimming the device in the user application board will provide the most accurate trim value.

## 11.3.2.2 Internal to External Clock Switching

When external clock source (external OSC, RC, or XTAL) is desired, the user must perform the following steps:

- 1. For external crystal circuits only, configure OSCOPT[1:0] to external crystal. To help precharge an external crystal oscillator, momentarily configure OSC2 as an output and drive it high for several cycles. This can help the crystal circuit start more robustly.

- 2. Configure OSCOPT[1:0] and ECFS[1:0] according to 11.8.1 Oscillator Status and Control Register. The oscillator module control logic will then enable OSC1 as an external clock input and, if the external crystal option is selected, OSC2 will also be enabled as the clock output. If RC oscillator option is selected, enabling the OSC2 output may change the bus frequency.

- Create a software delay to provide the stabilization time required for the selected clock source (crystal, resonator, RC). A good rule of thumb for crystal oscillators is to wait 4096 cycles of the crystal frequency; i.e., for a 4-MHz crystal, wait approximately 1 ms.

- 4. After the stabilization delay has elapsed, set ECGON.

After ECGON set is detected, the OSC module checks for oscillator activity by waiting two external clock rising edges. The OSC module then switches to the external clock. Logic provides a coherent transition. The OSC module first sets ECGST and then stops the internal oscillator.

## 11.3.2.3 External to Internal Clock Switching

After following the procedures to switch to an external clock source, it is possible to go back to the internal source. By clearing the OSCOPT[1:0] bits and clearing the ECGON bit, the external circuit will be disengaged. The bus clock will be derived from the selected internal clock source based on the ICFS[1:0] bits.

#### 11.3.3 External Oscillator

The external oscillator option is designed for use when a clock signal is available in the application to provide a clock source to the MCU. The OSC1 pin is enabled as an input by the oscillator module. The clock signal is used directly to create BUSCLKX4 and also divided by two to create BUSCLKX2.

In this configuration, the OSC2 pin cannot output BUSCLKX4. The OSC2EN bit will be forced clear to enable alternative functions on the pin.

MC68HC908QB8 Data Sheet, Rev. 3

## 11.6 OSC During Break Interrupts

There are no status flags associated with the OSC module.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

# 11.7 I/O Signals

The OSC shares its pins with general-purpose input/output (I/O) port pins. See Figure 11-1 for port location of these shared pins.

## 11.7.1 Oscillator Input Pin (OSC1)

The OSC1 pin is an input to the crystal oscillator amplifier, an input to the RC oscillator circuit, or an input from an external clock source.

When the OSC is configured for internal oscillator, the OSC1 pin can be used as a general-purpose input/output (I/O) port pin or other alternative pin function.

## 11.7.2 Oscillator Output Pin (OSC2)

For the XTAL oscillator option, the OSC2 pin is the output of the crystal oscillator amplifier.

When the OSC is configured for internal oscillator, external clock, or RC, the OSC2 pin can be used as a general-purpose I/O port pin or other alternative pin function. When the oscillator is configured for internal or RC, the OSC2 pin can be used to output BUSCLKX4.

Option

XTAL oscillator

External clock

Inverting OSC1

External clock

Internal oscillator

or

RC oscillator

OSC2EN = 0: General-purpose I/O or alternative pin function

OSC2EN = 1: BUSCLKX4 output

Table 11-1. OSC2 Pin Function

# **Chapter 13 Enhanced Serial Communications Interface (ESCI) Module**

## 13.1 Introduction

The enhanced serial communications interface (ESCI) module allows asynchronous communications with peripheral devices and other microcontroller units (MCU).

The ESCI module shares its pins with general-purpose input/output (I/O) port pins. See Figure 13-1 for port location of these shared pins. The ESCI baud rate clock source is controlled by a bit (ESCIBDSRC) located in the configuration register.

## 13.2 Features

Features include:

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- Programmable baud rates

- Programmable 8-bit or 9-bit character length

- Separately enabled transmitter and receiver

- Separate receiver and transmitter interrupt requests

- Programmable transmitter output polarity

- Receiver wakeup methods

- Idle line

- Address mark

- Interrupt-driven operation with eight interrupt flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

#### **Enhanced Serial Communications Interface (ESCI) Module**

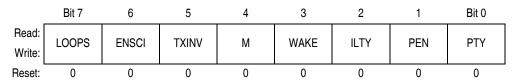

## 13.8.1 ESCI Control Register 1

ESCI control register 1 (SCC1):

- Enables loop mode operation

- Enables the ESCI

- Controls output polarity

- Controls character length

- Controls ESCI wakeup method

- Controls idle character detection

- Enables parity function

- Controls parity type

Figure 13-9. ESCI Control Register 1 (SCC1)

## LOOPS — Loop Mode Select Bit

This read/write bit enables loop mode operation. In loop mode the RxD pin is disconnected from the ESCI, and the transmitter output goes into the receiver input. Both the transmitter and the receiver must be enabled to use loop mode.

- 1 = Loop mode enabled

- 0 = Normal operation enabled

#### **ENSCI** — Enable ESCI Bit

This read/write bit enables the ESCI and the ESCI baud rate generator. Clearing ENSCI sets the SCTE and TC bits in ESCI status register 1 and disables transmitter interrupts.

- 1 = ESCI enabled

- 0 = ESCI disabled

#### TXINV — Transmit Inversion Bit

This read/write bit reverses the polarity of transmitted data.

- 1 = Transmitter output inverted

- 0 = Transmitter output not inverted

## NOTE

Setting the TXINV bit inverts all transmitted values including idle, break, start, and stop bits.

## M — Mode (Character Length) Bit

This read/write bit determines whether ESCI characters are eight or nine bits long (see Table 13-4). The ninth bit can serve as a receiver wakeup signal or as a parity bit.

- 1 = 9-bit ESCI characters

- 0 = 8-bit ESCI characters

| ( | Control Bits | Character Format |           |        |           |                  |  |

|---|--------------|------------------|-----------|--------|-----------|------------------|--|

| M | PEN:PTY      | Start Bits       | Data Bits | Parity | Stop Bits | Character Length |  |

| 0 | 0 X          | 1                | 8         | None   | 1         | 10 bits          |  |

| 1 | 0 X          | 1                | 9         | None   | 1         | 11 bits          |  |

| 0 | 1 0          | 1                | 7         | Even   | 1         | 10 bits          |  |

| 0 | 1 1          | 1                | 7         | Odd    | 1         | 10 bits          |  |

| 1 | 1 0          | 1                | 8         | Even   | 1         | 11 bits          |  |

| 1 | 1 1          | 1                | 8         | Odd    | 1         | 11 bits          |  |

**Table 13-4. Character Format Selection**

#### WAKE — Wakeup Condition Bit

This read/write bit determines which condition wakes up the ESCI: a 1 (address mark) in the MSB position of a received character or an idle condition on the RxD pin.

- 1 = Address mark wakeup

- 0 = Idle line wakeup

## ILTY — Idle Line Type Bit

This read/write bit determines when the ESCI starts counting 1s as idle character bits. The counting begins either after the start bit or after the stop bit. If the count begins after the start bit, then a string of 1s preceding the stop bit may cause false recognition of an idle character. Beginning the count after the stop bit avoids false idle character recognition, but requires properly synchronized transmissions.

- 1 = Idle character bit count begins after stop bit

- 0 = Idle character bit count begins after start bit

## PEN — Parity Enable Bit

This read/write bit enables the ESCI parity function (see Table 13-4). When enabled, the parity function inserts a parity bit in the MSB position (see Table 13-2).

- 1 = Parity function enabled

- 0 = Parity function disabled

## PTY — Parity Bit

This read/write bit determines whether the ESCI generates and checks for odd parity or even parity (see Table 13-4).

- 1 = Odd parity

- 0 = Even parity

#### NOTE

Changing the PTY bit in the middle of a transmission or reception can generate a parity error.

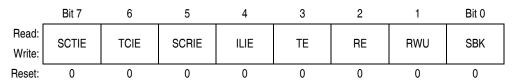

## 13.8.2 ESCI Control Register 2

ESCI control register 2 (SCC2):

- Enables these interrupt requests:

- SCTE bit to generate transmitter interrupt requests

- TC bit to generate transmitter interrupt requests

- SCRF bit to generate receiver interrupt requests

- IDLE bit to generate receiver interrupt requests

- Enables the transmitter

#### **Enhanced Serial Communications Interface (ESCI) Module**

- · Enables the receiver

- Enables ESCI wakeup

- Transmits ESCI break characters

Figure 13-10. ESCI Control Register 2 (SCC2)

## SCTIE — ESCI Transmit Interrupt Enable Bit

This read/write bit enables the SCTE bit to generate ESCI transmitter interrupt requests. Setting the SCTIE bit in SCC2 enables the SCTE bit to generate interrupt requests.

- 1 = SCTE enabled to generate interrupt

- 0 = SCTE not enabled to generate interrupt

## TCIE — Transmission Complete Interrupt Enable Bit

This read/write bit enables the TC bit to generate ESCI transmitter interrupt requests.

- 1 = TC enabled to generate interrupt requests

- 0 = TC not enabled to generate interrupt requests

## SCRIE — ESCI Receive Interrupt Enable Bit

This read/write bit enables the SCRF bit to generate ESCI receiver interrupt requests. Setting the SCRIE bit in SCC2 enables the SCRF bit to generate interrupt requests.

- 1 = SCRF enabled to generate interrupt

- 0 = SCRF not enabled to generate interrupt

#### ILIE — Idle Line Interrupt Enable Bit

This read/write bit enables the IDLE bit to generate ESCI receiver interrupt requests.

- 1 = IDLE enabled to generate interrupt requests

- 0 = IDLE not enabled to generate interrupt requests

#### TE — Transmitter Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 1s from the transmit shift register to the TxD pin. If software clears the TE bit, the transmitter completes any transmission in progress before the TxD returns to the idle condition (high). Clearing and then setting TE during a transmission queues an idle character to be sent after the character currently being transmitted.

- 1 = Transmitter enabled

- 0 = Transmitter disabled

## NOTE

Writing to the TE bit is not allowed when the enable ESCI bit (ENSCI) is clear. ENSCI is in ESCI control register 1.

## RE — Receiver Enable Bit

Setting this read/write bit enables the receiver. Clearing the RE bit disables the receiver but does not affect receiver interrupt flag bits.

- 1 = Receiver enabled

- 0 = Receiver disabled

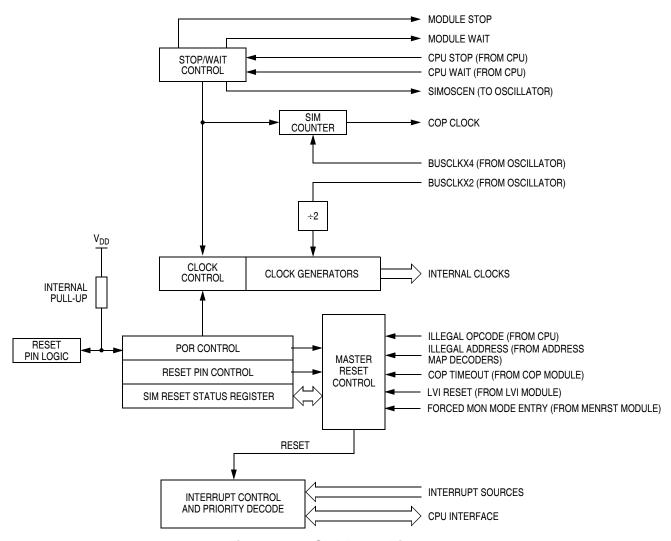

#### **System Integration Module (SIM)**

Figure 14-1. SIM Block Diagram

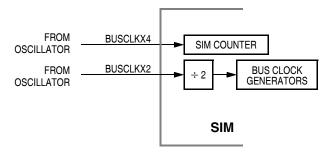

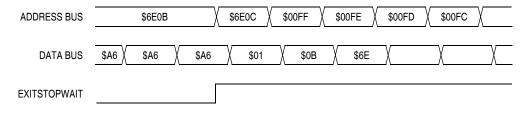

## 14.3 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 14-2.

Figure 14-2. SIM Clock Signals

MC68HC908QB8 Data Sheet, Rev. 3

# 14.6 Exception Control

Normal sequential program execution can be changed in three different ways:

- 1. Interrupts

- a. Maskable hardware CPU interrupts

- b. Non-maskable software interrupt instruction (SWI)

- 2. Reset

- 3. Break interrupts

## 14.6.1 Interrupts

An interrupt temporarily changes the sequence of program execution to respond to a particular event. Figure 14-7 flow charts the handling of system interrupts.

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared).

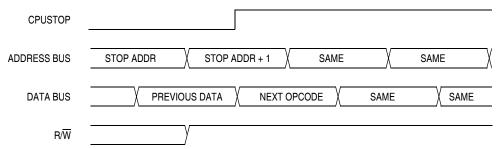

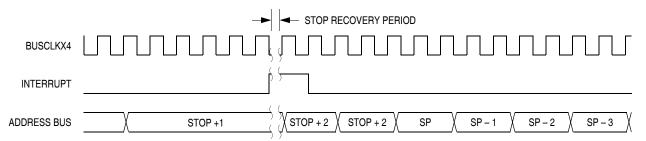

At the beginning of an interrupt, the CPU saves the CPU register contents on the stack and sets the interrupt mask (I bit) to prevent additional interrupts. At the end of an interrupt, the RTI instruction recovers the CPU register contents from the stack so that normal processing can resume. Figure 14-8 shows interrupt entry timing. Figure 14-9 shows interrupt recovery timing.

## 14.6.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register), and if the corresponding interrupt enable bit is set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

If more than one interrupt is pending at the end of an instruction execution, the highest priority interrupt is serviced first. Figure 14-10 demonstrates what happens when two interrupts are pending. If an interrupt is pending upon exit from the original interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

The LDA opcode is prefetched by both the INT1 and INT2 return-from-interrupt (RTI) instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

#### NOTE

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

149

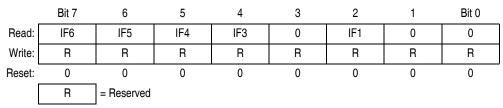

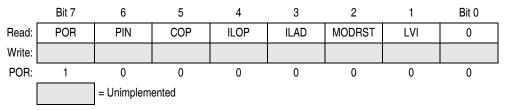

## 14.6.2.1 Interrupt Status Register 1

Figure 14-11. Interrupt Status Register 1 (INT1)

## IF1 and IF3-IF6 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 14-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

## Bit 0, 1, and 3— Always read 0

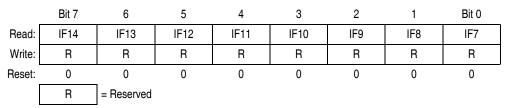

## 14.6.2.2 Interrupt Status Register 2

Figure 14-12. Interrupt Status Register 2 (INT2)

## IF7-IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 14-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

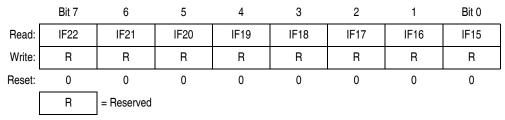

## 14.6.2.3 Interrupt Status Register 3

Figure 14-13. Interrupt Status Register 3 (INT3)

MC68HC908QB8 Data Sheet, Rev. 3

## IF15-IF22 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 14-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.