#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | SH-3 DSP                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 100MHz                                                                            |

| Connectivity               | FIFO, SCI, SIO, SmartCard, USB                                                    |

| Peripherals                | DMA, LCD, POR, WDT                                                                |

| Number of I/O              | 104                                                                               |

| Program Memory Size        | -                                                                                 |

| Program Memory Type        | ROMIess                                                                           |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 2.05V                                                                      |

| Data Converters            | A/D 6x10b; D/A 2x8b                                                               |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 240-LFBGA                                                                         |

| Supplier Device Package    | 240-LFBGA (13x13)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd6417727bp100cv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | 28.4.2   | Multi Mode (MULTI = 1, SCN = 0)                                          | 869 |

|--------------|----------|--------------------------------------------------------------------------|-----|

|              | 28.4.3   | Scan Mode (MULTI = 1, SCN = 1)                                           | 871 |

|              | 28.4.4   | Input Sampling and A/D Conversion Time                                   | 873 |

|              | 28.4.5   | External Trigger Input Timing                                            | 874 |

| 28.5         | Interrup | ots                                                                      | 875 |

| 28.6         | Definit  | ions of A/D Conversion Accuracy                                          | 875 |

| 28.7         | Usage l  | Notes                                                                    | 876 |

|              | 28.7.1   | Setting Analog Input Voltage                                             | 876 |

|              | 28.7.2   | Processing of Analog Input Pins                                          | 876 |

|              | 28.7.3   | Access Size and Read Data                                                | 877 |

| Secti        | on 29    | D/A Converter                                                            | 879 |

| 29.1         |          |                                                                          |     |

|              |          | Features                                                                 |     |

|              |          | Block Diagram                                                            |     |

|              |          | I/O Pins                                                                 |     |

|              |          | Register Configuration                                                   |     |

| 29.2         |          | r Descriptions                                                           |     |

|              |          | D/A Data Registers 0 and 1 (DADR0/1)                                     |     |

|              |          | D/A Control Register (DACR)                                              |     |

| 29.3         |          | on                                                                       |     |

| Secti        | on 30    | PC Card Controller (PCC)                                                 | 885 |

| 30.1         |          | ew                                                                       |     |

| 50.1         |          | Features                                                                 |     |

|              |          | Block Diagram                                                            |     |

|              |          | Register Configuration                                                   |     |

|              |          | PCMCIA Support                                                           |     |

| 30.2         |          | r Descriptions                                                           |     |

| 50.2         | -        | Area 6 Interface Status Register (PCC0ISR)                               |     |

|              |          | Area 6 General Control Register (PCC0GCR)                                |     |

|              |          | Area 6 Card Status Change Register (PCC0CSCR)                            |     |

|              |          | Area 6 Card Status Change Interrupt Enable Register (PCC0CSCIER)         |     |

| 30.3         |          | on                                                                       |     |

| 50.5         | -        | PC card Connection Specification (Interface Diagram, Pin Correspondence) |     |

|              |          | PC Card Interface Timing                                                 |     |

|              |          | Usage Notes                                                              |     |

| Cast         | on 21    | User Debugging Interface (ILUDI)                                         | 015 |

|              |          | User-Debugging Interface (H-UDI)                                         |     |

| 31.1<br>31.2 |          | ew<br>ebugging Interface (H-UDI)                                         |     |

| 51.2         |          |                                                                          | 915 |

| D 0          | 00 Mar   | . 27, 2009 Page xxxiv of lvi                                             |     |

REJ09B0254-0600

| ltem                                         | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus state<br>controller (BSC)                | <ul> <li>Physical address space divided into six areas (area 0, areas 2 to 6), each of up to 64 Mbytes, with the following features settable for each area:         <ul> <li>Bus size (8, 16, or 32 bits)</li> <li>Number of wait cycles (hardware wait function also waited)</li> <li>Direct connection of SRAM, synchronous DRAM, and burst ROM possible by designating memory to be connected to each area</li> <li>Supports PCMCIA interface (2 channels)</li> <li>Chip select signals (CS0, CS2–CS6) for relevant area</li> </ul> </li> <li>Synchronous DRAM refresh function         <ul> <li>Programmable refresh interval</li> <li>Supports CAS-before-RAS refresh and self-refresh modes</li> <li>Supports power-down DRAM</li> </ul> </li> <li>Synchronous DRAM burst access function</li> <li>Big endian or little endian can be specified</li> </ul> |

| Li bus state<br>controller (LBSC)            | <ul> <li>Bus State Controller for LCDC or USB Host</li> <li>Supports synchronous DRAM</li> <li>Synchronous DRAM access function (area 3)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| User debug<br>Interface (H-UDI)              | <ul> <li>E10A emulator support</li> <li>Pin arrangement conforming to JTAG specification</li> <li>Realtime branch trace</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Timer (TMU)                                  | <ul> <li>3-channel auto-reload-type 32-bit timer</li> <li>Choice of six counter input clocks</li> <li>Maximum resolution: 2 MHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Realtime clock<br>(RTC)                      | <ul> <li>Built-in clock, calendar functions, and alarm functions</li> <li>On-chip 32-kHz crystal oscillator circuit with a maximum resolution (cycle interrupt) of 1/256 second</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Serial communi-<br>cation interface<br>(SCI) | <ul> <li>Asynchronous mode or clock synchronous mode can be selected</li> <li>Full-duplex communication</li> <li>Supports smart card interface</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Item           | Features                                                                                 |

|----------------|------------------------------------------------------------------------------------------|

| LCD controller | From 16 x 1 to 1024 x 1024 pixels can be supported                                       |

| (LCDC)         | • 4/8/15/16 bpp (bit per pixel) color modes                                              |

|                | <ul> <li>1/2/4/6 bpp (bit per pixel) gray scale</li> </ul>                               |

|                | 8-bit Frame rate controller                                                              |

|                | TFT/DSTN/STN                                                                             |

|                | Signal polarity setting function                                                         |

|                | Hardware panel rotation                                                                  |

|                | Power control function                                                                   |

|                | - Selectable clock source (LCLK, bus clock (B $\phi$ ), or peripheral clock (P $\phi$ )) |

| AFE I/F        | ST7550 direct interface                                                                  |

|                | Telephone line control                                                                   |

|                | 128-word FIFO for transfer                                                               |

|                | 128-word FIFO for receive                                                                |

| I/O port       | Thirteen 8-bit I/O ports                                                                 |

| A/D converter  | • 10 bits ± 4 LSB, 6 channels                                                            |

| (ADC)          | Conversion time: 15 µs                                                                   |

|                | • Input range: 0–Vcc (max. 3.6 V)                                                        |

| D/A converter  | • 8 bits ± 4 LSB, 2 channels                                                             |

| (DAC)          | Conversion time: 10 µs                                                                   |

|                | • Output range: 0–Vcc (max. 3.6 V)                                                       |

| Product lineup | Power Supply                                                                             |

| roduct lineup |                     | Power S<br>Voltage | supply              | Operating |                 |                                        |

|---------------|---------------------|--------------------|---------------------|-----------|-----------------|----------------------------------------|

|               | SH7727              | I/O                | Internal            | Frequency | Model Name      | Package                                |

|               | 160 MHz<br>products | 3.0 V to<br>3.6 V  | 1.70 V to<br>2.05 V | 160 MHz   | HD6417727F160C  | 240-pin plastic HQFP<br>(PRQP0240KC-B) |

|               |                     |                    |                     |           | HD6417727BP160C | 240-pin CSP<br>(PLBG0240JA-A)          |

|               | 100 MHz<br>products | 2.6 V to<br>3.6 V  | 1.60 V to<br>2.05 V | 100 MHz   | HD6417727F100C  | 240-pin plastic HQFP<br>(PRQP0240KC-B) |

|               |                     |                    |                     |           | HD6417727BP100C | 240-pin CSP<br>(PLBG0240JA-A)          |

|               |                     |                    |                     |           |                 |                                        |

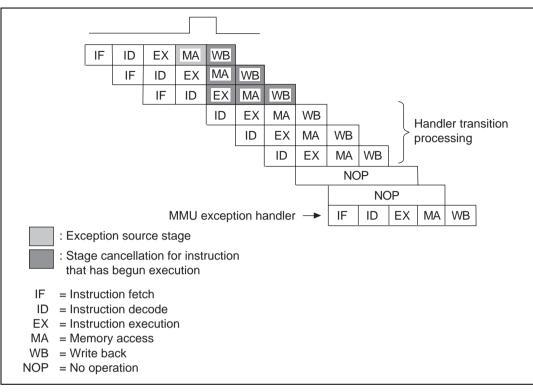

MMU Exception in the Data Access Mode

Figure 3.13 MMU Exception Signals in Data Access

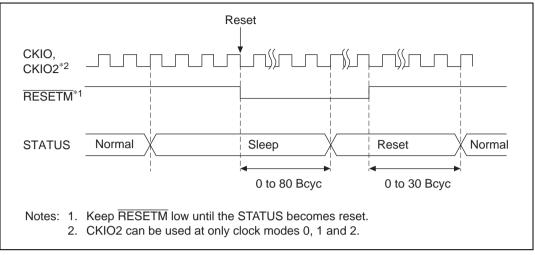

- Manual Reset

- Conditions: RESETM low

- Operations: EXPEVT set to H'020, VBR and SR initialized, branch to PC = H'A0000000. Initialization sets the VBR register to H'000000000. In SR, the MD, RB, and BL bits are set to 1 and the interrupt mask bits (I3 to I0) is set to 11111. The CPU and on-chip supporting modules are initialized. See the register descriptions in the relevant sections for details. A high level is output from the STATUS0 and STATUS1 pins.

- H-UDI Reset

- Conditions: H-UDI reset command input (see section 31.4.3, H-UDI Reset)

- Operations: EXPEVT set to H'000, VBR and SR initialized, branch to PC = H'A0000000. Initialization sets the VBR register to H'0000000. In SR, the MD, RB and BL bits are set to 1 and the interrupt mask bits (I3 to I0) is set to 1111. The CPU and on-chip supporting modules are initialized. See the register descriptions in the relevant sections for details.

|                 | Conditions for Transition | Internal State |                                                   |  |  |

|-----------------|---------------------------|----------------|---------------------------------------------------|--|--|

| Туре            | to Reset State            | CPU            | On-Chip Supporting Modules                        |  |  |

| Power-on reset  | RESETP = Low              | Initialized    | (See register configuration in relevant sections) |  |  |

| Manual<br>reset | RESETM = Low              | Initialized    |                                                   |  |  |

| H-UDI<br>reset  | H-UDI reset command input | Initialized    |                                                   |  |  |

#### Table 4.4Types of Reset

#### 4.5.2 General Exceptions

- TLB miss exception

- --- Conditions: Comparison of TLB addresses shows no address match

- Operations: The logical address (32 bits) that caused the exception is set in TEA and the corresponding virtual page number (22 bits) is set in PTEH (31 to 10). The ASID of PTEH indicates the ASID at the time the exception occurred. The RC bit in MMUCR is incremented by 1 when all ways are enabled, and if there is a disabled way, setting is prioritized starting from way 0.

The PC and SR of the instruction that generated the exception are saved to the SPC and SSR, respectively. If the exception occurred during a read, H'040 is set in EXPEVT; if the exception occurred during a write, H'060 is set in EXPEVT. The BL, MD and RB bits in SR are set to 1 and a branch occurs to PC = VBR + H'0400.

#### **Sleep to Manual Reset**

Figure 9.9 Sleep to Manual Reset STATUS Output

fill operation in the event of a cache miss, the missed data is read first, then 16-byte boundary data including the missed data is read in wraparound mode.

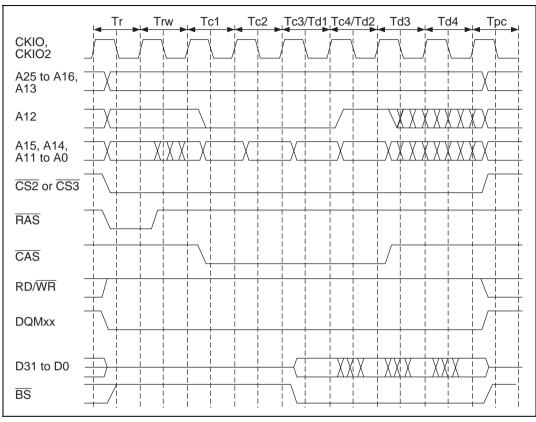

Figure 12.14 Synchronous DRAM Burst Read Wait Specification Timing

**Single Read:** Figure 12.15 shows the timing when a single address read is performed. As the burst length is set to 1 in synchronous DRAM burst read/single write mode, only the required data is output. Consequently, no unnecessary bus cycles are generated even when a cache-through area is accessed.

| Channel | Name                               | Abbrevi-<br>ation | R/W   | Initial<br>Value | Address                                  | Register<br>Size | Access<br>Size          |

|---------|------------------------------------|-------------------|-------|------------------|------------------------------------------|------------------|-------------------------|

| 2       | DMA source address register 2      | SAR2              | R/W   | Undefined        | H'04000040<br>(H'A4000040) <sup>*4</sup> | 32 bits          | 16, 32 <sup>*2</sup>    |

|         | DMA destination address register 2 | DAR2              | R/W   | Undefined        | H'04000044<br>(H'A4000044) <sup>*4</sup> | 32 bits          | 16, 32 <sup>*2</sup>    |

|         | DMA transfer count register 2      | DMATCR2           | R/W   | Undefined        | H'04000048<br>(H'A4000048) <sup>*4</sup> | 24 bits          | 16, 32 <sup>*3</sup>    |

|         | DMA channel control register 2     | CHCR2             | R/W*1 | H'00000000       | H'0400004C<br>(H'A400004C) <sup>*4</sup> | 32 bits          | 8, 16, 32 <sup>*2</sup> |

| 3       | DMA source address register 3      | SAR3              | R/W   | Undefined        | H'0400050<br>(H'A4000050) <sup>*4</sup>  | 32 bits          | 16, 32 <sup>*2</sup>    |

|         | DMA destination address register 3 | DAR3              | R/W   | Undefined        | H'04000054<br>(H'A4000054) <sup>*4</sup> | 32 bits          | 16, 32 <sup>*2</sup>    |

|         | DMA transfer count register 3      | DMATCR3           | R/W   | Undefined        | H'04000058<br>(H'A4000058) <sup>*4</sup> | 24 bits          | 16, 32 <sup>*3</sup>    |

|         | DMA channel control register 3     | CHCR3             | R/W*1 | H'00000000       | H'0400005C<br>(H'A400005C) <sup>*4</sup> | 32 bits          | 8, 16, 32 <sup>*2</sup> |

| Shared  | DMA operation register             | DMAOR             | R/W*1 | H'0000           | H'04000060<br>(H'A4000060) <sup>*4</sup> | 16 bits          | 8, 16 <sup>*2</sup>     |

|         | DMA channel assign<br>register     | CHRAR             | R/W   | H'0000           | H'0400022A<br>(H'A400022A) <sup>*4</sup> | 16 bits          | 16                      |

Notes: These registers are located in area 1 of physical space. Therefore, when the cache is on, either access these registers from the P2 area of logical space or else make an appropriate setting using the MMU so that these registers are not cached.

- 1. Only a write of 0 after a read of 1 to clear a flag is enabled for bit 1 in CHCR0 to CHCR3 and bits 1 and 2 in DMAOR.

- 2. If SAR0 to SAR3, DAR0 to DAR3, and CHCR0 to CHCR3 are accessed in 16 bits, the 16 bit values that were not accessed are held.

- 3. DMATCR comprises the 24 bits from bit 0 to bit 23. The upper 8 bits, bits 24 to 31, cannot be written with 1 and are always read as 0.

- 4. When address translation by the MMU does not apply, the address in parentheses should be used.

#### Table 14.6 Relationship of Request Modes and Bus Modes

| Address<br>Mode | Transfer Areas                                                  | Request<br>Mode   | Bus<br>Mode | Transfer<br>Size (bits) | Usable<br>Channels |

|-----------------|-----------------------------------------------------------------|-------------------|-------------|-------------------------|--------------------|

| Dual            | External device with DACK and external memory                   | External          | B/C         | 8/16/32/128             | 0                  |

|                 | External device with DACK and memory-mapped external device     | External          | B/C         | 8/16/32/128             | 0                  |

|                 | External memory and external memory                             | All <sup>*1</sup> | B/C         | 8/16/32/128             | 0–3*5              |

|                 | External memory and memory-<br>mapped external device           | All <sup>*1</sup> | B/C         | 8/16/32/128             | 0–3*5              |

|                 | Memory-mapped external device and memory-mapped external device | All <sup>*1</sup> | B/C         | 8/16/32/128             | 0–3 <sup>*5</sup>  |

|                 | External memory and on-chip supporting module                   | All <sup>*2</sup> | B/C*3       | 8/16/32*4               | 0–3*5              |

|                 | Memory-mapped external device and on-chip supporting module     | All <sup>*2</sup> | B/C*3       | 8/16/32*4               | 0–3*5              |

|                 | On-chip supporting module and on-<br>chip supporting module     | All <sup>*2</sup> | B/C*3       | 8/16/32*4               | 0–3*5              |

|                 | X/Y memory and X/Y memory                                       | All               | B/C         | 8/16/32/128             | 0–3                |

|                 | X/Y memory and memory-mapped external device                    | All <sup>*1</sup> | B/C         | 8/16/32/128             | 0–3                |

|                 | X/Y memory and on-chip supporting module                        | All <sup>*2</sup> | B/C*3       | 8/16/32                 | 0–3                |

|                 | X/Y memory and external memory                                  | All               | B/C         | 8/16/32/128             | 0–3                |

| Single          | External device with DACK and external memory                   | External          | B/C         | 8/16/32/128             | 0                  |

|                 | External device with DACK and memory-mapped external device     | External          | B/C         | 8/16/32/128             | 0                  |

#### B: Burst

C: Cycle steal

- Notes: 1. External requests, auto requests and on-chip supporting module (CMT) requests are all available.

- External requests, auto requests and on-chip supporting module requests are all available. When the SIOF, USBF, SCIF, or A/D converter is the transfer request source, the transfer destination or transfer source must be also the SIOF, USBF, SCIF, or A/D converter, respectively.

- 3. The SIOF, USBF, SCIF, or A/D converter can be specified for the transfer request source in the cycle-steal mode only.

- 4. The access size permitted when the transfer destination or source is an on-chip supporting module register.

- 5. If the transfer request is an external request, only channel 0 is available.

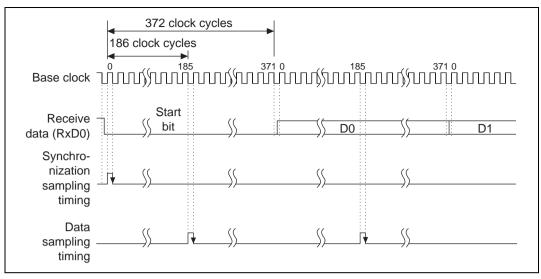

Figure 18.8 Receive Data Sampling Timing in Smart Card Mode

The receive margin is found from the following equation:

For smart card mode:

$$M = \left| (0.5 - \frac{1}{2N}) - (L - 0.5)F - \frac{|D - 0.5|}{N} (1 + F) \right| \times 100\%$$

Where: M = Receive margin (%)

N = Ratio of bit rate to clock (N = 372)

D = Clock duty (D = 0 to 1.0)

L = Frame length (L = 10)

F = Absolute value of clock frequency deviation

Using this equation, the receive margin when F = 0 and D = 0.5 is as follows:

$M = (0.5 - 1/2 \times 372) \times 100\% = 49.866\%$

#### 20.3.9 Transmit or Receive Timing

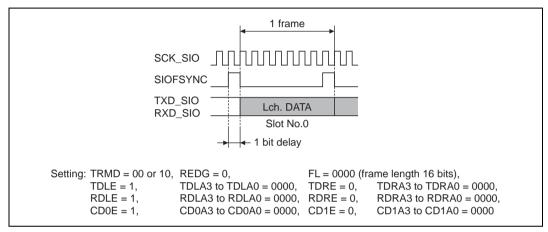

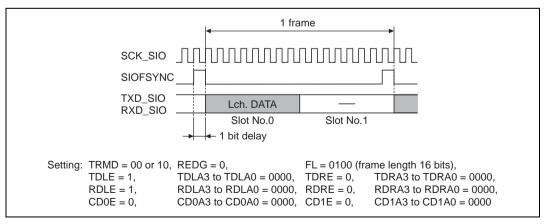

Figures 20.13 to 20.19 show examples of serial transmit or receive of SIOF.

#### (1) A Case of 8 bits Monaural (No.1)

Sync pulse method, falling edge sampling, transmit data and receive data are assigned to slot No. 0, frame length is 8 bits.

Figure 20.13 Transmit or Receive Timing (8 bits monaural—1)

#### (2) A Case of 8 bits Monaural (No.2)

Sync pulse method, falling edge sampling, transmit data and receive data are assigned to slot No.0, frame length is 16 bits.

Figure 20.14 Transmit or Receive Timing (8 bits monaural—2)

Rev.6.00 Mar. 27, 2009 Page 648 of 1036 REJ09B0254-0600

## Section 24 USB HOST Module

### 24.1 General Description

The USB Host Controller module incorporated in SH7727 supports Open Host Controller (Open HCI) Specification for the Universal Serial Bus (USB) as well as the Universal Serial Bus specification ver.1.1.

The Open HCI Specification for the USB is a register-level description of Host Controller for the USB which in turn is described by the USB specification.

It is necessary to refer Open HCI specification to develop drivers for this USB Host Controller and hardware. Also refer to the restrictions on the use of the module listed at the end of this section.

#### 24.1.1 Features

- Support open HCI standard ver.1.0 register set

- Support Universal Serial Bus standard ver.1.1

- Root Hub function

- Support Full speed (12Mbps) mode and Low speed (1.5Mbps) mode

- Support Overcurrent detection

- Support 127 endpoints control in maximum

- The whole area of the synchronous DRAM in area 3 connected to the CPU can be used for transfer data and descriptor.

#### 24.2.2 HcControl

#### HcControl Register (H'04000404)

The HcControl register defines the operation mode for the host controller. Most of bits of this register are amended only by the host controller driver other than HostController Function State and Remote Wakeup Command.

| Register | r: HcContro | ol  | Offset: 04–07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits     | Reset       | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 31–11    | 0h          |     | Reserved. Read/Write 0's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10       | 0b          | R/W | RemoteWakeupEnable (RWE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |             |     | This bit is used by HCD to enable/disable the remote wakeup<br>function at the same time as the detection of an upstream<br>resume signal. This function is not supported. Be sure to write<br>0.                                                                                                                                                                                                                                                                                                                             |

| 9        | 0b          | R/W | RemoteWakeupConnected (RWC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |             |     | This bit indicates whether the host controller supports a remote<br>wakeup signal or not. When the remote wakeup is supported<br>and used in the system, the host controller must set this bit<br>between POST in the system firmware. The host controller<br>clears the bit at the same time of the hardware reset, however,<br>does not change at the same time as the software reset. The<br>remote wakeup signal to the system of the host is specific for<br>the host bus, so it is not described in this specification. |

|          |             |     | <ul><li>0: Remote wakeup signal is not supported. (initial value)</li><li>1: Remote wakeup signal is supported.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8        | 0b          | R/W | InterruptRouting (IR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |             |     | This bit determines the routing of interrupts generated by the<br>event registered in HcInterruptStatus. HCD clears this bit at the<br>same time as the hardware reset, however, does not clear at<br>the same time as the software reset. HCD uses this bit as a tag<br>to indicate the ownership of the host controller.                                                                                                                                                                                                    |

|          |             |     | <ul><li>0: All interrupts are routed to normal bus interrupt mechanism.<br/>(initial value)</li><li>1: Interrupts are routed to SMI.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                |

### 27.5 Ports F, M

Each pin has an input pullup MOS, which is controlled by Ports F, M Control Register (PFDR, PMDR) in PFC.

#### 27.5.1 Ports F, M Data Register (PFDR, PMDR)

| Bit:              | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|

|                   | Px7DT | Px6DT | Px5DT | Px4DT | Px3DT | Px2DT | Px1DT | Px0DT |

| Initial value:    | *     | *     | *     | *     | *     | *     | *     | *     |

| R/W:              | R     | R     | R     | R     | R     | R     | R     | R     |

| Note: * Undefined |       |       |       |       |       |       |       |       |

Ports F, M Data Register (PFDR, PMDR) is an 8-bit read register that stores data for pins PTx7 to PTx0. Px7DT to Px0DT bit corresponds to PTx7 to PTx0 pin. When the pin function is general input port, if the port is read, the corresponding pin level is read. Table 27.4 shows the function of PFDR and PMDR.

PFDR and PMDR are initialized by a power-on reset. After initialization, the general input port function (pullup MOS: on) is set as the initial pin function, and the corresponding pin levels are read.

| <b>Table 27.4</b> | Read/Write Operation of the Ports F | F, M Data Register (PFDR, PMDR) |

|-------------------|-------------------------------------|---------------------------------|

|-------------------|-------------------------------------|---------------------------------|

| PxnMD1                                                                     | PxnMD0 | Pin State                 | Read      | Write                            |          |

|----------------------------------------------------------------------------|--------|---------------------------|-----------|----------------------------------|----------|

| 0                                                                          | 0      | Other function            | H'00      | Ignored (no affect on pin state) | <u> </u> |

|                                                                            | 1      | Reserved*                 | _         | _                                |          |

| 1                                                                          | 0      | Input (Pullup<br>MOS on)  | Pin state | Ignored (no affect on pin state) |          |

|                                                                            | 1      | Input (Pullup<br>MOS off) | Pin state | Ignored (no affect on pin state) |          |

| Note: * Operation cannot be guaranteed when this bit it set to "reserved." |        |                           |           |                                  |          |

(x = F, M)

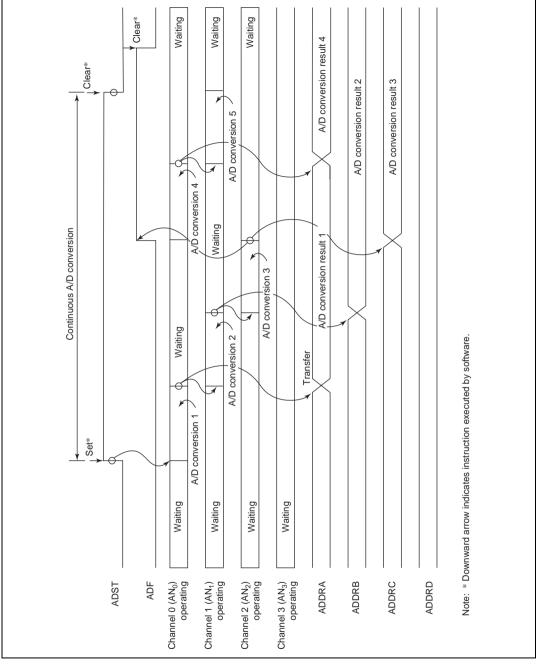

#### 28.4.3 Scan Mode (MULTI = 1, SCN = 1)

Scan mode is useful for monitoring analog inputs in a group of one or more channels including channel 1. When the ADST bit in the A/D control/status register (ADCSR) is set to 1 by software or external trigger input, A/D conversion starts on the first channel in the group (AN2 when CH2 = 0, AN4 when CH2 = 1). When two or more channels are selected, after conversion of the first channel ends, conversion of the second channel (AN3 or AN5) starts immediately. A/D conversion is repeated continuously on the selected channels until the ADST bit is cleared to 0.

The conversion results are transferred for storage into the A/D data registers corresponding to the channels.

When the mode or analog input channel must be changed during analog conversion, to prevent incorrect operation, first clear the ADST bit to 0 to halt A/D conversion. After making the necessary changes, set the ADST bit to 1. A/D conversion will start again from the first channel in the group. The ADST bit can be set at the same time as the mode or channel selection is changed.

Typical operations when three channels (AN4 to AN6) are selected in scan mode are described next. Figure 28.5 shows a timing diagram for this example.

- 1. Scan mode is selected (MULTI = 1, SCN = 1), channel group 1 is selected (CH2 = 1), analog input channels AN4 to AN6 are selected (CH1 = 1, CH0 = 0), and A/D conversion is started (ADST = 1).

- 2. When A/D conversion of the first channel (AN4) is completed, the result is transferred into ADDRA. Next, conversion of the second channel (AN5) starts automatically.

- 3. Conversion proceeds in the same way through the third channel (AN6).

- 4. When conversion of all the selected channels (AN4 to AN6) is completed, the ADF flag is set to 1 and conversion of the first channel (AN4) starts again. If the ADIE bit is set to 1, an ADI interrupt is requested at this time.

- 5. Steps 2 to 4 are repeated as long as the ADST bit remains set to 1. When the ADST bit is cleared to 0, A/D conversion stops. After that, if the ADST bit is set to 1, A/D conversion starts again from the first channel (AN4).

Figure 28.5 Example of A/D Converter Operation (Scan Mode, Channels AN4 to AN6 Selected)

### **31.4 H-UDI Operations**

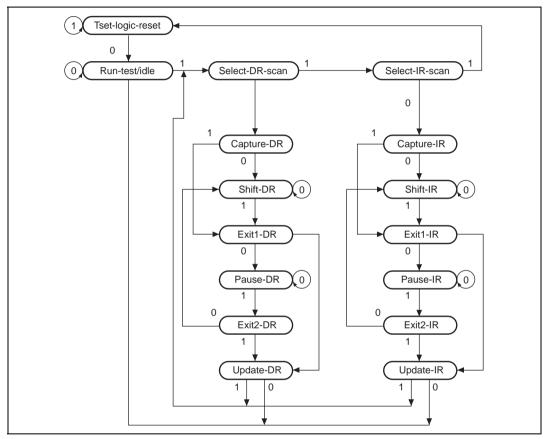

### 31.4.1 TAP Controller

Figure 31.2 shows the internal states of TAP controller. State transitions basically conform with the JTAG standard.

Figure 31.2 TAP Controller State Transitions

Note: The transition condition is the TMS value on the rising edge of TCK. The TDI value is sampled on the rising edge of TCK; shifting occurs on the falling edge of TCK. The TDO value changes on the TCK falling edge. The TDO is at high impedance, except with shift-DR (shift-SR) and shift-IR states. During the change to  $\overline{\text{TRST}} = 0$ , there is a transition to test-logic-reset asynchronously with TCK.

#### Table 32.6Clock Timing (2)

Conditions: VccQ = 3.0 to 3.6 V, Vcc = 1.70 to 2.05 V,  $AVcc = 3.3 \pm 0.3$  V, Ta = -20 to 75°C, 100 MHz products

| Item                                                                  | Symbol              | Min | Max   | Unit             | Figure          |

|-----------------------------------------------------------------------|---------------------|-----|-------|------------------|-----------------|

| EXTAL clock input frequency                                           | f <sub>EX</sub>     | 6   | 50    | MHz              | 32.3            |

| EXTAL clock input cycle time                                          | t <sub>EXcyc</sub>  | 20  | 166.7 | ns               |                 |

| EXTAL clock input low pulse width                                     | t <sub>EXL</sub>    | 4   | _     | ns               |                 |

| EXTAL clock input high pulse width                                    | t <sub>EXH</sub>    | 4   | —     | ns               |                 |

| EXTAL clock input rise time                                           | t <sub>EXR</sub>    | —   | 6     | ns               |                 |

| EXTAL clock input fall time                                           | t <sub>EXF</sub>    | _   | 6     | ns               |                 |

| CKIO clock input frequency                                            | f <sub>скі</sub>    | 24  | 50    | MHz              | 32.4            |

| CKIO clock input cycle time                                           | t <sub>CKIcyc</sub> | 20  | 41.7  | ns               |                 |

| CKIO clock input low pulse width                                      | t <sub>CKIL</sub>   | 4   | _     | ns               |                 |

| CKIO clock input high pulse width                                     | t <sub>CKIH</sub>   | 4   | _     | ns               |                 |

| CKIO clock input rise time                                            | t <sub>CKIR</sub>   | _   | 6     | ns               |                 |

| CKIO clock input fall time                                            | t <sub>CKIF</sub>   | _   | 6     | ns               |                 |

| CKIO clock output frequency                                           | f <sub>OP</sub>     | 24  | 50    | MHz              | 32.5            |

| CKIO clock output cycle time                                          | t <sub>cyc</sub>    | 20  | 41.7  | ns               |                 |

| CKIO clock output low pulse width                                     | t <sub>CKOL</sub>   | 3   | _     | ns               |                 |

| CKIO clock output high pulse width                                    | t <sub>скон</sub>   | 3   | _     | ns               |                 |

| CKIO clock output rise time                                           | t <sub>CKOR</sub>   | _   | 5     | ns               |                 |

| CKIO clock output fall time                                           | t <sub>CKOF</sub>   | _   | 5     | ns               |                 |

| CKIO2 clock output delay time                                         | t <sub>CK2D</sub>   | _   | 2.5   | ns               |                 |

| CKIO2 clock output rise time                                          | t <sub>CK2OR</sub>  | _   | 7     | ns               |                 |

| CKIO2 clock output fall time                                          | t <sub>CK2OF</sub>  | _   | 7     | ns               |                 |

| Power-on oscillation settling time                                    | t <sub>OSC1</sub>   | 10  | _     | ms               | 32.6            |

| RESETP setup time<br>(At power on and cancellation of standby mode)   | t <sub>RESPS</sub>  | 20  | —     | ns               | 32.6, 32.7      |

| RESETM setup time (At cancellation of standby mode)                   | t <sub>RESMS</sub>  | 0   | _     | ns               |                 |

| RESETP assert time<br>(At power on and cancellation of standby mode)  | t <sub>RESPW</sub>  | 20  | —     | t <sub>cyc</sub> |                 |

| RESETM assert time (At cancellation of standby mode)                  | t <sub>RESMW</sub>  | 20  | _     | t <sub>cyc</sub> |                 |

| Standby return oscillation settling time 1                            | t <sub>OSC2</sub>   | 10  | _     | ms               | 32.7            |

| Standby return oscillation settling time 2                            | t <sub>osc3</sub>   | 10  | _     | ms               | 32.8            |

| Standby return oscillation settling time 3                            | t <sub>OSC4</sub>   | 11  | _     | ms               | 32.9            |

| PLL synchronization settling time 1 (At cancellation of standby mode) | t <sub>PLL1</sub>   | 100 | —     | μs               | 32.10,<br>32.11 |

| PLL synchronization settling time 2 (At multiplier change)            | t <sub>PLL2</sub>   | 100 | _     | μS               | 32.12           |

| IRQ/IRL interrupt determination time<br>(RTC used and standby mode)   | t <sub>IRQSTB</sub> | 100 |       | μs               | 32.11           |

Rev.6.00 Mar. 27, 2009 Page 938 of 1036 REJ09B0254-0600

| Туре                               | Signal Name<br>(Initial Status: Bold)                                                                                                  | Pin No.<br>(HQFP)                                                    | I/O          | Power-<br>On<br>Reset | Manual<br>Reset | Standby            | Release/<br>Open Bus<br>Privileges |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------|-----------------------|-----------------|--------------------|------------------------------------|

| Bus<br>functions                   | A0 to A25                                                                                                                              | 61 to 63, 65,<br>67 to 74, 76,<br>78 to 85, 87,<br>89, 90, 92,<br>94 | 0            | Z                     | 0               | Z(L)               | Z                                  |

|                                    | BS/PTK[4]                                                                                                                              | 95                                                                   | O/IO         | н                     | O/P             | Z(H)/K             | Z/P                                |

|                                    | RD                                                                                                                                     | 96                                                                   | 0            | Н                     | 0               | Z(H)               | Z                                  |

|                                    | WE0/DQMLL                                                                                                                              | 97                                                                   | O/O          | Н                     | O/O             | Z(H)/Z(H)          | Z/Z                                |

|                                    | WE1/DQMLU/WE                                                                                                                           | 98                                                                   | 0/0/0        | Н                     | 0/0/0           | Z(H)/Z(H)/<br>Z(H) | Z/Z/Z                              |

|                                    | WE2/DQMUL/ICIORD/<br>PTK[6],<br>WE3/DQMUU/ICIOWR/<br>PTK[7]                                                                            | 99, 101                                                              | 0/0/0/<br>I0 | Н                     | 0/0/0/P         | Z(H)/Z(H)/<br>O/K  | Z/Z/Z/P                            |

|                                    | RDWR                                                                                                                                   | 103                                                                  | 0            | Н                     | 0               | Z(H)               | Z                                  |

|                                    | <u>CS0, CS2, CS3</u>                                                                                                                   | 105, 106,<br>107                                                     | 0            | Н                     | 0               | Z(H)               | Z                                  |

|                                    | CS4/PTK[2]                                                                                                                             | 108                                                                  | O/IO         | Н                     | O/P             | Z(H)/K             | Z/P                                |

|                                    | CS5/CE1A/PTK[3]                                                                                                                        | 109                                                                  | 0/0/10       | н                     | O/O/P           | Z(H)/Z(H)/<br>K    | Z/Z/P                              |

|                                    | CS6/CE1B                                                                                                                               | 110                                                                  | O/O          | Н                     | O/O             | Z(H)/Z(H)          | Z/Z                                |

|                                    | CE2A/PTE[4],<br>CE2B/PTE[5]                                                                                                            | 111, 112                                                             | O/IO         | V                     | O/P             | Z(H)/K             | Z/P                                |

|                                    | CKE/PTK[5]                                                                                                                             | 128                                                                  | O/IO         | Н                     | O/P             | O/K                | O/P                                |

|                                    | Reserved/CAS/PTJ[2]                                                                                                                    | 131                                                                  | 0/0/10       | н                     | O/O/P           | O/Z(H)/K           | O/Z(H)/P                           |

|                                    | WAIT                                                                                                                                   | 146                                                                  | I            | Z                     | Z               | Z                  | Z                                  |

|                                    | IOIS16/PTG[7]                                                                                                                          | 149                                                                  | I/I          | V                     | I/I             | Z/Z(V)             | I/I                                |

|                                    | RAS/PTJ[0],<br>Reserved/PTJ[1],<br>Reserved/PTJ[3] <sup>*3</sup> ,<br>Reserved/PTJ[4] <sup>*3</sup> ,<br>Reserved/PTJ[5] <sup>*3</sup> | 129, 130,<br>133, 135,<br>136                                        | O/IO         | H                     | O/P             | Z(H)/K             | Z(H)/P                             |

| AFE/USB<br>digital/port<br>related | AFE_HC1/<br>USB1d_DPLS/PTK[0]                                                                                                          | 113                                                                  | 0/1/10       | L                     | O/I/P           | Z/Z/K              | O/I/P                              |

|                                    | AFE_RLYCNT/<br>USB1d_DMNS/PTK[1]                                                                                                       | 114                                                                  | 0/1/10       | L                     | O/I/P           | O/Z/K              | O/I/P                              |

|                                    | AFE_SCLK/<br>USB1d_TXDPLS                                                                                                              | 116                                                                  | I/O          | I                     | I/O             | Z/O                | I/O                                |

# Appendix C Product Lineup

### Table C.1 SH7727 Group Product Lineup

| Abbreviation | Power Supply Voltages |               | Operation |                 |                                        |

|--------------|-----------------------|---------------|-----------|-----------------|----------------------------------------|

|              | I/O                   | Internal      | Frequency | Model Name      | Package                                |

| SH7727       | 3.3±0.3 V             | 1.7 to 2.05 V | 160 MHz   | HD6417727F160C  | 240-pin plastic HQFP<br>(PRQP0240KC-B) |

|              | 3.3±0.3 V             | 1.7 to 2.05 V | 160 MHz   | HD6417727BP160C | 240-pin CSP<br>(PLBG0240JA-A)          |

|              | 3.1±0.5 V             | 1.6 to 2.05 V | 100 MHz   | HD6417727F100C  | 240-pin plastic HQFP<br>(PRQP0240KC-B) |

|              | 3.1±0.5 V             | 1.6 to 2.05 V | 100 MHz   | HD6417727BP100C | 240-pin CSP<br>(PLBG0240JA-A)          |

|              |                       |               |           |                 |                                        |