#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, SPI, UART/USART                                                |

| Peripherals                | PWM, WDT                                                                        |

| Number of I/O              | 79                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                    |

| Data Converters            | ·                                                                               |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | PG-TQFP-100-16                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc164d-16f40f-bb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

# **Table of Contents**

| 1                                                                                                                                       | Summary of Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                                                                  | General Device Information         Introduction         Pin Configuration and Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                                                                                      |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17 | Functional Description       Amemory Subsystem and Organization         External Bus Controller       External Bus Controller         Central Processing Unit (CPU)       Interrupt System         Interrupt System       On-Chip Debug Support (OCDS)         Capture/Compare Units (CAPCOM1/2)       Z         The Capture/Compare Unit (CAPCOM6)       General Purpose Timer Unit (GPT12E)         Real Time Clock       Asynchronous/Synchronous Serial Interfaces (ASC0/ASC1)         High Speed Synchronous Serial Channels (SSC0/SSC1)       Z         TwinCAN Module       Z         Watchdog Timer       Z         Clock Generation       Z         Parallel Ports       Z         Power Management       Z         Instruction Set Summary       Z | 19<br>21<br>22<br>29<br>29<br>29<br>33<br>37<br>39<br>40<br>41<br>43<br>44<br>44<br>44 |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5                                                              | External Clock Drive XTAL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50<br>53<br>58                                                                         |

| <b>5</b><br>5.1<br>5.2                                                                                                                  | Package and Reliability       Packaging         Packaging       Packaging         Flash Memory Parameters       Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

### **Summary of Features**

- Programmable External Bus Characteristics for Different Address Ranges

- Multiplexed or Demultiplexed External Address/Data Buses

- Selectable Address Bus Width

- 16-Bit or 8-Bit Data Bus Width

- Four Programmable Chip-Select Signals

- Up to 79 General Purpose I/O Lines,

- partly with Selectable Input Thresholds and Hysteresis

- On-Chip Bootstrap Loader

- Supported by a Large Range of Development Tools like C-Compilers, Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Debug Support via JTAG Interface

- 100-Pin Green TQFP Package, 0.5 mm (19.7 mil) pitch (RoHS compliant)

### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery.

For the available ordering codes for the XC164D please refer to your responsible sales representative or your local distributor.

# Note: The ordering codes for Mask-ROM versions are defined for each product after verification of the respective ROM code.

This document describes several derivatives of the XC164D group. **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

For simplicity all versions are referred to by the term **XC164D** throughout this document.

### **Summary of Features**

| Table 1 XC164D           | Table 1 XC164D Derivative Synopsis |                     |                                    |                       |        |        |  |  |  |

|--------------------------|------------------------------------|---------------------|------------------------------------|-----------------------|--------|--------|--|--|--|

| Derivative <sup>1)</sup> | Temp.<br>Range                     | Program<br>Memory   | On-Chip RAM                        | Inter-<br>faces       | Clock  |        |  |  |  |

| SAF-XC164D-16F40F        | -40 °C to<br>85 °C                 | 128 Kbytes<br>Flash | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM, | ASC0,<br>ASC1,        | 40 MHz |        |  |  |  |

| SAF-XC164D-16F20F        | -40 °C to<br>85 °C                 | SSC1,               |                                    | SSC0,<br>SSC1,        | 20 MHz |        |  |  |  |

| SAF-XC164D-8F40F         | -40 °C to<br>85 °C                 | 64 Kbytes<br>Flash  | 2 Kbytes DPRAM,<br>2 Kbytes DSRAM, | CAN0,<br>CAN1,<br>CC6 |        | 40 MHz |  |  |  |

| SAF-XC164D-8F20F         | -40 °C to<br>85 °C                 |                     | 2 Kbytes PSRAM                     |                       | 20 MHz |        |  |  |  |

| SAF-XC164D-16R40F        | -40 °C to<br>85 °C                 | 128 Kbytes<br>ROM   | 2 Kbytes DPRAM,<br>4 Kbytes DSRAM, | -                     | 40 MHz |        |  |  |  |

| SAF-XC164D-16R20F        | -40 °C to<br>85 °C                 |                     | 2 Kbytes PSRAM                     |                       | -      | 20 MHz |  |  |  |

| SAF-XC164D-8R40F         | -40 °C to<br>85 °C                 | 64 Kbytes<br>ROM    | 2 Kbytes DPRAM,<br>2 Kbytes DSRAM, |                       |        | 40 MHz |  |  |  |

| SAF-XC164D-8R20F         | -40 °C to<br>85 °C                 |                     | 2 Kbytes PSRAM                     |                       | 20 MHz |        |  |  |  |

### Table 1 XC164D Derivative Synopsis

1) This Data Sheet is valid for devices starting with and including design step BB.

### **General Device Information**

## Table 2Pin Definitions and Functions (cont'd)

| Symbol | Pin<br>Num. | Input<br>Outp. | Function                                                                                                                                                                                                                                                            |

|--------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRST   | 36          | 1              | Test-System Reset Input. For normal system operation, pin<br>TRST should be held low. A high level at this pin at the rising<br>edge of RSTIN activates the XC164CM's debug system. In<br>this case, pin TRST must be driven low once to reset the<br>debug system. |

### **General Device Information**

| Table 2          | Pii         | n Definit      | ions and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                          |

|------------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Pin<br>Num. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                             |

| PORT0            |             | Ю              | PORT0 consists of the two 8-bit bidirectional I/O ports P0L and P0H. Each pin can be programmed for input (output                                                                                                                                                                                                                                                                    |

| P0L.0 -<br>P0L.7 | 67 -<br>74  |                | driver in high-impedance state) or output.<br>In case of an external bus configuration, PORT0 serves as<br>the address (A) and address/data (AD) bus in multiplexed                                                                                                                                                                                                                  |

| P0H.0 -<br>P0L.3 | 4 -<br>7    |                | bus modes and as the data (D) bus in demultiplexed bus modes.                                                                                                                                                                                                                                                                                                                        |

| P0H.4 -<br>P0L.7 | 75 -<br>78  |                | Demultiplexed bus modes:<br>8-bit data bus: P0H = I/O, P0L = D7 - D0<br>16-bit data bus: P0H = D15 - D8, P0L = D7 - D0<br>Multiplexed bus modes:<br>8-bit data bus: P0H = A15 - A8, P0L = AD7 - AD0<br>16-bit data bus: P0H = AD15 - AD8, P0L = AD7 - AD0                                                                                                                            |

|                  |             |                | Note: At the end of an external reset ( $\overline{EA} = 0$ ) PORT0 also may input configuration values                                                                                                                                                                                                                                                                              |

| PORT1            |             | 10             | PORT1 consists of the two 8-bit bidirectional I/O ports P1L<br>and P1H. Each pin can be programmed for input (output<br>driver in high-impedance state) or output.<br>PORT1 is used as the 16-bit address bus (A) in<br>demultiplexed bus modes (also after switching from a<br>demultiplexed to a multiplexed bus mode).<br>The following PORT1 pins also serve for alt. functions: |

| P1L.0            | 79          | I/O            | CC60 CAPCOM6: Input / Output of Channel 0                                                                                                                                                                                                                                                                                                                                            |

| P1L.1<br>P1L.2   | 80<br>81    | 0<br>I/O       | COUT60 CAPCOM6: Output of Channel 0<br>CC61 CAPCOM6: Input / Output of Channel 1                                                                                                                                                                                                                                                                                                     |

| P1L.3            | 82          | 0              | COUT61 CAPCOM6: Output of Channel 1                                                                                                                                                                                                                                                                                                                                                  |

| P1L.4            | 83          | I/O            | CC62 CAPCOM6: Input / Output of Channel 2                                                                                                                                                                                                                                                                                                                                            |

| P1L.5            | 84          | 0              | COUT62 CAPCOM6: Output of Channel 2                                                                                                                                                                                                                                                                                                                                                  |

| P1L.6<br>P1L.7   | 85<br>86    | 0              | COUT63 Output of 10-bit Compare Channel<br>CTRAP CAPCOM6: Trap Input                                                                                                                                                                                                                                                                                                                 |

| ΓΙ <b>Ε.</b> Ι   | 00          |                | CTRAP is an input pin with an internal pull-up resistor. A low<br>level on this pin switches the CAPCOM6 compare outputs to<br>the logic level defined by software (if enabled).                                                                                                                                                                                                     |

| DALL             |             | I/O            | CC22IO CAPCOM2: CC22 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                      |

| P1H              |             |                | continued                                                                                                                                                                                                                                                                                                                                                                            |

### Table 4XC164D Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAPCOM6 Timer T12                             | CCU6_T12IC          | xx'0134 <sub>H</sub>             | 4D <sub>H</sub> / 77 <sub>D</sub> |

| CAPCOM6 Timer T13                             | CCU6_T13IC          | xx'0138 <sub>H</sub>             | 4E <sub>H</sub> / 78 <sub>D</sub> |

| CAPCOM6 Emergency                             | CCU6_EIC            | xx'013C <sub>H</sub>             | 4F <sub>H</sub> / 79 <sub>D</sub> |

| CAPCOM6                                       | CCU6_IC             | xx'0140 <sub>H</sub>             | 50 <sub>H</sub> / 80 <sub>D</sub> |

| SSC1 Transmit                                 | SSC1_TIC            | xx'0144 <sub>H</sub>             | 51 <sub>H</sub> / 81 <sub>D</sub> |

| SSC1 Receive                                  | SSC1_RIC            | xx'0148 <sub>H</sub>             | 52 <sub>H</sub> / 82 <sub>D</sub> |

| SSC1 Error                                    | SSC1_EIC            | xx'014C <sub>H</sub>             | 53 <sub>H</sub> / 83 <sub>D</sub> |

| CAN0                                          | CAN_0IC             | xx'0150 <sub>H</sub>             | 54 <sub>H</sub> / 84 <sub>D</sub> |

| CAN1                                          | CAN_1IC             | xx'0154 <sub>H</sub>             | 55 <sub>H</sub> / 85 <sub>D</sub> |

| CAN2                                          | CAN_2IC             | xx'0158 <sub>H</sub>             | 56 <sub>H</sub> / 86 <sub>D</sub> |

| CAN3                                          | CAN_3IC             | xx'015C <sub>H</sub>             | 57 <sub>H</sub> / 87 <sub>D</sub> |

| CAN4                                          | CAN_4IC             | xx'0164 <sub>H</sub>             | 59 <sub>H</sub> / 89 <sub>D</sub> |

| CAN5                                          | CAN_5IC             | xx'0168 <sub>H</sub>             | 5A <sub>H</sub> / 90 <sub>D</sub> |

| CAN6                                          | CAN_6IC             | xx'016C <sub>H</sub>             | 5B <sub>H</sub> / 91 <sub>D</sub> |

| CAN7                                          | CAN_7IC             | xx'0170 <sub>H</sub>             | 5C <sub>H</sub> / 92 <sub>D</sub> |

| RTC                                           | RTC_IC              | xx'0174 <sub>H</sub>             | 5D <sub>H</sub> / 93 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0100 <sub>H</sub>             | 40 <sub>H</sub> / 64 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |

| Unassigned node                               | -                   | xx'012C <sub>H</sub>             | 4B <sub>H</sub> / 75 <sub>D</sub> |

| Unassigned node                               | -                   | xx'00FC <sub>H</sub>             | 3F <sub>H</sub> / 63 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0160 <sub>H</sub>             | 58 <sub>H</sub> / 88 <sub>D</sub> |

Register VECSEG defines the segment where the vector table is located to. Bitfield VECSC in register CPUCON1 defines the distance between two adjacent vectors. This table

represents the default setting, with a distance of 4 (two words) between two vectors.

compare function.

12 registers of the CAPCOM2 module have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

| Compare Modes           | Function                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mode 0                  | Interrupt-only compare mode;<br>several compare interrupts per timer period are possible                                        |

| Mode 1                  | Pin toggles on each compare match;<br>several compare events per timer period are possible                                      |

| Mode 2                  | Interrupt-only compare mode;<br>only one compare interrupt per timer period is generated                                        |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>only one compare event per timer period is generated          |

| Double Register<br>Mode | Two registers operate on one pin;<br>pin toggles on each compare match;<br>several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses;<br>can be used with any compare mode                                                          |

Table 6Compare Modes (CAPCOM1/2)

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

### Summary of Features

- CAN functionality according to CAN specification V2.0 B active.

- Data transfer rate up to 1 Mbit/s

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality and Basic CAN functionality for each message object

- 32 flexible message objects

- Assignment to one of the two CAN nodes

- Configuration as transmit object or receive object

- Concatenation to a 2-, 4-, 8-, 16-, or 32-message buffer with FIFO algorithm

- Handling of frames with 11-bit or 29-bit identifiers

- Individual programmable acceptance mask register for filtering for each object

- Monitoring via a frame counter

- Configuration for Remote Monitoring Mode

- Up to eight individually programmable interrupt nodes can be used

- CAN Analyzer Mode for bus monitoring is implemented

- Note: When a CAN node has the interface lines assigned to Port 4, the segment address output on Port 4 must be limited. CS lines can be used to increase the total amount of addressable external memory.

### 3.17 Instruction Set Summary

Table 8 lists the instructions of the XC164D in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "Instruction Set Manual".

This document also provides a detailed description of each instruction.

| Mnemonic      | Description                                                                                       | Bytes |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------|-------|--|--|--|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4   |  |  |  |

| ADDC(B)       | Add word (byte) operands with Carry                                                               | 2/4   |  |  |  |

| SUB(B)        | Subtract word (byte) operands                                                                     |       |  |  |  |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4   |  |  |  |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- $\times$ 16-bit)                                | 2     |  |  |  |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |  |  |  |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |  |  |  |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2     |  |  |  |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2     |  |  |  |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4   |  |  |  |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4   |  |  |  |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4   |  |  |  |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2     |  |  |  |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4     |  |  |  |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |  |  |  |

| BCMP          | Compare direct bit to direct bit                                                                  | 4     |  |  |  |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |  |  |  |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4   |  |  |  |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |  |  |  |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |  |  |  |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |  |  |  |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2     |  |  |  |

### Table 8 Instruction Set Summary

### 4.1 General Parameters

### Table 9 Absolute Maximum Ratings

| Parameter                                                                   | Symbol           | Limit Values |                        | Unit | Notes      |

|-----------------------------------------------------------------------------|------------------|--------------|------------------------|------|------------|

|                                                                             |                  | Min.         | Max.                   | 1    |            |

| Storage temperature                                                         | T <sub>ST</sub>  | -65          | 150                    | °C   | 1)         |

| Junction temperature                                                        | TJ               | -40          | 150                    | °C   | under bias |

| Voltage on $V_{\text{DDI}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DDI</sub> | -0.5         | 3.25                   | V    | -          |

| Voltage on $V_{\text{DDP}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DDP</sub> | -0.5         | 6.2                    | V    | -          |

| Voltage on any pin with respect to ground ( $V_{SS}$ )                      | V <sub>IN</sub>  | -0.5         | V <sub>DDP</sub> + 0.5 | V    | 2)         |

| Input current on any pin during overload condition                          | -                | -10          | 10                     | mA   | -          |

| Absolute sum of all input<br>currents during overload<br>condition          | -                | -            | 100                    | mA   | _          |

1) Moisture Sensitivity Level (MSL) 3, conforming to Jedec J-STD-020C for 260 °C for PG-TQFP-100-5, and 240 °C for P-TQFP-100-16.

2) Input pin XTAL1 belongs to the core voltage domain. Therefore, input voltages must be within the range defined for  $V_{\text{DDI}}$ .

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

### 4.2 DC Parameters

## Table 11DC Characteristics (Operating Conditions apply)<sup>1)</sup>

| Parameter                                                      | Symbol                           |    | Limit                             | Values                               | Unit | <b>Test Condition</b>                                                |  |

|----------------------------------------------------------------|----------------------------------|----|-----------------------------------|--------------------------------------|------|----------------------------------------------------------------------|--|

|                                                                |                                  |    | Min.                              | Max.                                 | -    |                                                                      |  |

| Input low voltage TTL<br>(all except XTAL1)                    | V <sub>IL</sub>                  | SR | -0.5                              | $0.2 \times V_{\text{DDP}}$<br>- 0.1 | V    | -                                                                    |  |

| Input low voltage<br>XTAL1 <sup>2)</sup>                       | V <sub>ILC</sub>                 | SR | -0.5                              | $0.3 	imes V_{ m DDI}$               | V    | -                                                                    |  |

| Input low voltage<br>(Special Threshold)                       | V <sub>ILS</sub>                 | SR | -0.5                              | $0.45 \times V_{\text{DDP}}$         | V    | 3)                                                                   |  |

| Input high voltage TTL<br>(all except XTAL1)                   | V <sub>IH</sub>                  | SR | $0.2 \times V_{\text{DDP}} + 0.9$ | V <sub>DDP</sub> + 0.5               | V    | -                                                                    |  |

| Input high voltage<br>XTAL1 <sup>2)</sup>                      | V <sub>IHC</sub>                 | SR | $0.7 \times V_{\text{DDI}}$       | V <sub>DDI</sub> + 0.5               | V    | -                                                                    |  |

| Input high voltage<br>(Special Threshold)                      | V <sub>IHS</sub>                 | SR | 0.8 × V <sub>DDP</sub><br>- 0.2   | V <sub>DDP</sub> + 0.5               | V    | 3)                                                                   |  |

| Input Hysteresis<br>(Special Threshold)                        | HYS                              |    | $0.04 \times V_{\text{DDP}}$      | -                                    | V    | $V_{\text{DDP}}$ in [V],<br>Series resis-<br>tance = 0 $\Omega^{3)}$ |  |

| Output low voltage                                             | V <sub>OL</sub>                  | CC | -                                 | 1.0                                  | V    | $I_{\rm OL} \leq I_{\rm OLmax}^{4)}$                                 |  |

|                                                                |                                  |    | -                                 | 0.45                                 | V    | $I_{\rm OL} \leq I_{\rm OLnom}^{4)5)}$                               |  |

| Output high voltage <sup>6)</sup>                              | V <sub>OH</sub>                  | CC | V <sub>DDP</sub> - 1.0            | -                                    | V    | $I_{\rm OH} \ge I_{\rm OHmax}^{4)}$                                  |  |

|                                                                |                                  |    | V <sub>DDP</sub> -<br>0.45        | -                                    | V    | $I_{\rm OH} \ge I_{\rm OHnom}^{4)5)$                                 |  |

| Input leakage current<br>(Port 5) <sup>7)</sup>                | I <sub>OZ1</sub>                 | CC | -                                 | ±300                                 | nA   | $0 V < V_{IN} < V_{DDP},$<br>$T_A \le 125 \text{ °C}$                |  |

|                                                                |                                  |    |                                   | ±200                                 | nA   | $0 V < V_{IN} < V_{DDP},$<br>$T_A \le 85 \ ^{\circ}C^{14)}$          |  |

| Input leakage current (all other <sup>8)</sup> ) <sup>7)</sup> | I <sub>OZ2</sub>                 | CC | -                                 | ±500                                 | nA   | 0.45 V < V <sub>IN</sub> <<br>V <sub>DDP</sub>                       |  |

| Configuration pull-up                                          | $I_{\rm CPUH}^{10)}$             |    | -                                 | -10                                  | μA   | $V_{\rm IN} = V_{\rm IHmin}$                                         |  |

| current <sup>9)</sup>                                          | $I_{\rm CPUL}^{11)}$             |    | -100                              | -                                    | μA   | $V_{\rm IN} = V_{\rm ILmax}$                                         |  |

| Configuration pull-                                            | $I_{\rm CPDL}^{10)}$             |    | -                                 | 10                                   | μA   | $V_{\rm IN} = V_{\rm ILmax}$                                         |  |

| down current <sup>12)</sup>                                    | I <sub>CPDH</sub> <sup>11)</sup> |    | 120                               | -                                    | μA   | $V_{\rm IN} = V_{\rm IHmin}$                                         |  |

| Table 11 | DC Characteristics ( | Operating | Conditions | apply) <sup>1)</sup> | (cont'd) |

|----------|----------------------|-----------|------------|----------------------|----------|

|----------|----------------------|-----------|------------|----------------------|----------|

| Parameter                                                  | Symbol                                 |    | Limit Values |      | Unit | Test Condition                      |  |

|------------------------------------------------------------|----------------------------------------|----|--------------|------|------|-------------------------------------|--|

|                                                            |                                        |    | Min.         | Max. |      |                                     |  |

| Level inactive hold current <sup>13)</sup>                 | <i>I</i> <sub>LHI</sub> <sup>10)</sup> |    | _            | -10  | μA   | $V_{\rm OUT}$ = 0.5 × $V_{\rm DDP}$ |  |

| Level active hold current <sup>13)</sup>                   | $I_{LHA}^{11)}$                        |    | -100         | -    | μA   | V <sub>OUT</sub> = 0.45 V           |  |

| XTAL1 input current                                        | I <sub>IL</sub>                        | CC | -            | ±20  | μA   | $0 V < V_{IN} < V_{DDI}$            |  |

| Pin capacitance <sup>14)</sup><br>(digital inputs/outputs) | C <sub>IO</sub>                        | CC | -            | 10   | pF   | -                                   |  |

1) Keeping signal levels within the limits specified in this table, ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

2) If XTAL1 is driven by a crystal, reaching an amplitude (peak to peak) of  $0.4 \times V_{DDI}$  is sufficient.

3) This parameter is tested for P3, P4, P9.

4) The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 12, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

- 5) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are guaranteed.

- 6) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- 7) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{OV}$ .

- 8) The driver of P3.15 is designed for faster switching, because this pin can deliver the reference clock for the bus interface (CLKOUT). The maximum leakage current for P3.15 is, therefore, increased to 1  $\mu$ A.

- 9) This specification is valid during Reset for configuration on RD, WR, EA, PORTO

- 10) The maximum current may be drawn while the respective signal line remains inactive.

- 11) The minimum current must be drawn to drive the respective signal line active.

- 12) This specification is valid during Reset for configuration on ALE.

- 13) This specification is valid during Reset for pins P4.3-0, which can act as  $\overline{CS}$  outputs, and for P3.12.

- 14) Not subject to production test verified by design/characterization.

| Port Output Driver<br>Mode | Maximum Output Current $(I_{OLmax}, -I_{OHmax})^{1)}$ | Nominal Output Current<br>(I <sub>OLnom</sub> , -I <sub>OHnom</sub> )<br>2.5 mA<br>1.0 mA |  |  |

|----------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|

| Strong driver              | 10 mA                                                 |                                                                                           |  |  |

| Medium driver              | 4.0 mA                                                |                                                                                           |  |  |

| Weak driver                | 0.5 mA                                                | 0.1 mA                                                                                    |  |  |

#### Table 12 Current Limits for Port Output Drivers

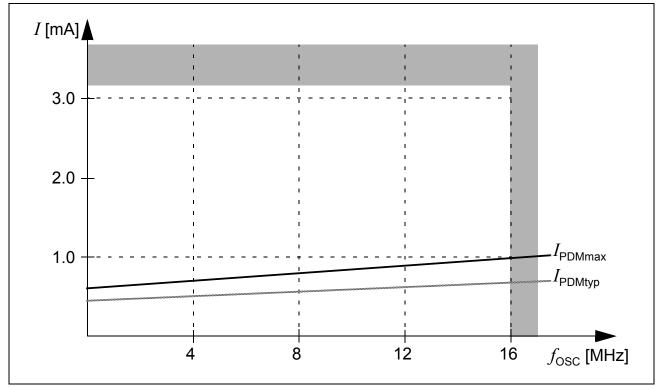

Figure 12 Sleep and Power Down Supply Current due to RTC and Oscillator Running, as a Function of Oscillator Frequency

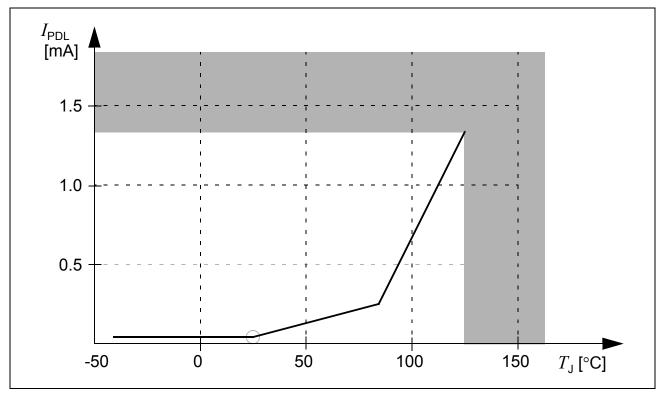

Figure 13 Sleep and Power Down Leakage Supply Current as a Function of Temperature

### 4.3 AC Parameters

### 4.3.1 Definition of Internal Timing

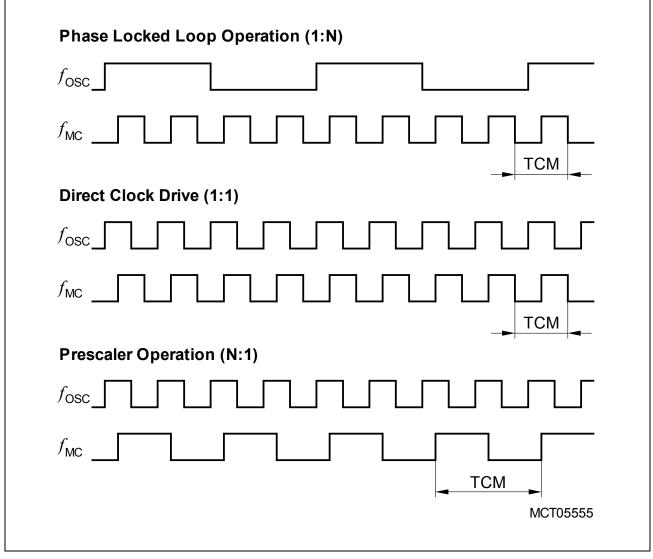

The internal operation of the XC164D is controlled by the internal master clock  $f_{MC}$ .

The master clock signal  $f_{\rm MC}$  can be generated from the oscillator clock signal  $f_{\rm OSC}$  via different mechanisms. The duration of master clock periods (TCMs) and their variation (and also the derived external timing) depend on the used mechanism to generate  $f_{\rm MC}$ . This influence must be regarded when calculating the timings for the XC164D.

Figure 14 Generation Mechanisms for the Master Clock

Note: The example for PLL operation shown in **Figure 14** refers to a PLL factor of 1:4, the example for prescaler operation refers to a divider factor of 2:1.

The used mechanism to generate the master clock is selected by register PLLCON.

CPU and EBC are clocked with the CPU clock signal  $f_{CPU}$ . The CPU clock can have the same frequency as the master clock ( $f_{CPU} = f_{MC}$ ) or can be the master clock divided by two:  $f_{CPU} = f_{MC}$  / 2. This factor is selected by bit CPSYS in register SYSCON1.

The specification of the external timing (AC Characteristics) depends on the period of the CPU clock, called "TCP".

The other peripherals are supplied with the system clock signal  $f_{SYS}$  which has the same frequency as the CPU clock signal  $f_{CPU}$ .

### **Bypass Operation**

When bypass operation is configured (PLLCTRL =  $0x_B$ ) the master clock is derived from the internal oscillator (input clock signal XTAL1) through the input- and output-prescalers:

$f_{MC} = f_{OSC} / ((PLLIDIV+1) \times (PLLODIV+1)).$

If both divider factors are selected as '1' (PLLIDIV = PLLODIV = '0') the frequency of  $f_{MC}$  directly follows the frequency of  $f_{OSC}$  so the high and low time of  $f_{MC}$  is defined by the duty cycle of the input clock  $f_{OSC}$ .

The lowest master clock frequency is achieved by selecting the maximum values for both divider factors:

$f_{\rm MC} = f_{\rm OSC} / ((3 + 1) \times (14 + 1)) = f_{\rm OSC} / 60.$

### Phase Locked Loop (PLL)

When PLL operation is configured (PLLCTRL =  $11_B$ ) the on-chip phase locked loop is enabled and provides the master clock. The PLL multiplies the input frequency by the factor **F** ( $f_{MC} = f_{OSC} \times F$ ) which results from the input divider, the multiplication factor, and the output divider (**F** = PLLMUL+1 / (PLLIDIV+1 × PLLODIV+1)). The PLL circuit synchronizes the master clock to the input clock. This synchronization is done smoothly, i.e. the master clock frequency does not change abruptly.

Due to this adaptation to the input clock the frequency of  $f_{\rm MC}$  is constantly adjusted so it is locked to  $f_{\rm OSC}$ . The slight variation causes a jitter of  $f_{\rm MC}$  which also affects the duration of individual TCMs.

The timing listed in the AC Characteristics refers to TCPs. Because  $f_{\rm CPU}$  is derived from  $f_{\rm MC}$ , the timing must be calculated using the minimum TCP possible under the respective circumstances.

The actual minimum value for TCP depends on the jitter of the PLL. As the PLL is constantly adjusting its output frequency so it corresponds to the applied input frequency (crystal or oscillator) the relative deviation for periods of more than one TCP is lower than for one single TCP (see formula and **Figure 15**).

This is especially important for bus cycles using waitstates and e.g. for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train

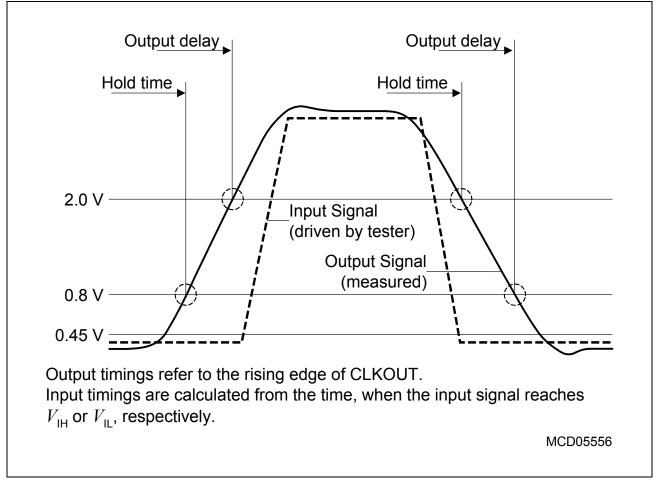

### 4.3.4 Testing Waveforms

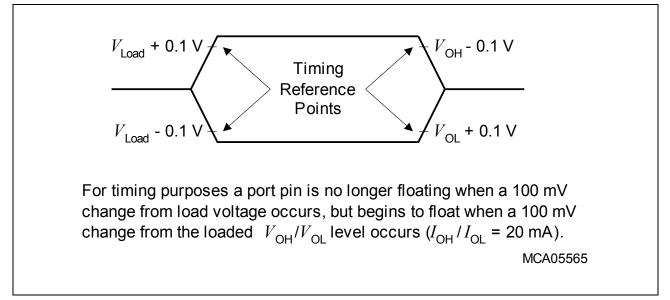

### Figure 17 Input Output Waveforms

### Figure 18 Float Waveforms

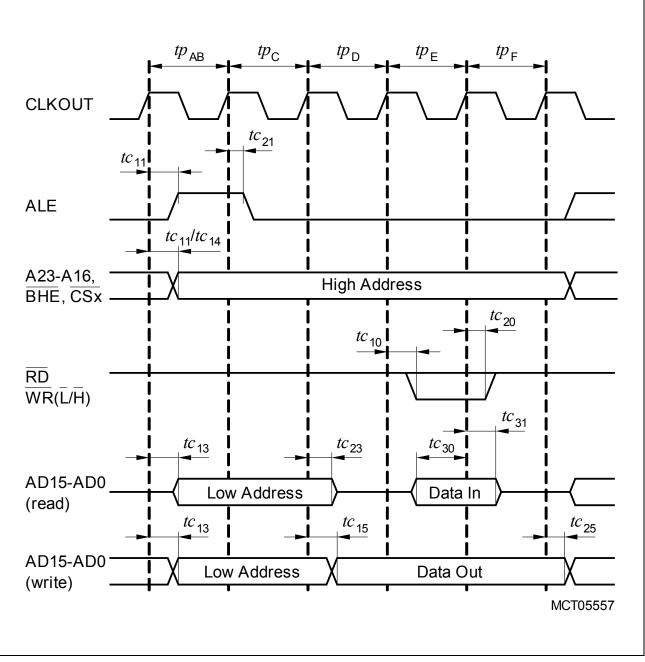

### Variable Memory Cycles

External bus cycles of the XC164D are executed in five subsequent cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

This table provides a summary of the phases and the respective choices for their duration.

| Bus Cycle Phase                                                                                                                                | Parameter              | Valid Values | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------|------|

| Address setup phase, the standard duration of this phase (1 $\dots$ 2 TCP) can be extended by 0 $\dots$ 3 TCP if the address window is changed | tp <sub>AB</sub>       | 1 2 (5)      | TCP  |

| Command delay phase                                                                                                                            | tp <sub>C</sub>        | 03           | TCP  |

| Write Data setup/MUX Tristate phase                                                                                                            | tp <sub>D</sub>        | 0 1          | TCP  |

| Access phase                                                                                                                                   | <i>tp</i> <sub>E</sub> | 1 32         | TCP  |

| Address/Write Data hold phase                                                                                                                  | tp <sub>F</sub>        | 03           | TCP  |

### Table 19 Programmable Bus Cycle Phases (see timing diagrams)

Note: The bandwidth of a parameter (minimum and maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

### Table 20 External Bus Cycle Timing (Operating Conditions apply)

| Parameter                                                    | Symbol                  |    | Limit Values |      | Unit |

|--------------------------------------------------------------|-------------------------|----|--------------|------|------|

|                                                              |                         |    | Min.         | Max. |      |

| Output valid delay for:<br>RD, WR(L/H)                       | <i>tc</i> <sub>10</sub> | CC | 1            | 13   | ns   |

| Output valid delay for:<br>BHE, ALE                          | <i>tc</i> <sub>11</sub> | CC | -1           | 7    | ns   |

| Output valid delay for:<br>A23 A16, A15 A0 (on PORT1)        | <i>tc</i> <sub>12</sub> | СС | 1            | 16   | ns   |

| Output valid delay for:<br>A15 … A0 (on PORT0)               | <i>tc</i> <sub>13</sub> | CC | 3            | 16   | ns   |

| Output valid delay for:<br>CS                                | <i>tc</i> <sub>14</sub> | СС | 1            | 14   | ns   |

| Output valid delay for:<br>D15 … D0 (write data, MUX-mode)   | <i>tc</i> <sub>15</sub> | СС | 3            | 17   | ns   |

| Output valid delay for:<br>D15 … D0 (write data, DEMUX-mode) | <i>tc</i> <sub>16</sub> | СС | 3            | 17   | ns   |

| Output hold time for:<br>RD, WR(L/H)                         | <i>tc</i> <sub>20</sub> | СС | -3           | 3    | ns   |

| Output hold time for:<br>BHE, ALE                            | <i>tc</i> <sub>21</sub> | СС | 0            | 8    | ns   |

| Output hold time for:<br>A23 A16, A15 A0 (on PORT0)          | <i>tc</i> <sub>23</sub> | СС | 1            | 13   | ns   |

| Output hold time for:<br>CS                                  | <i>tc</i> <sub>24</sub> | СС | -3           | 3    | ns   |

| Output hold time for:<br>D15 … D0 (write data)               | <i>tc</i> <sub>25</sub> | CC | 1            | 13   | ns   |

| Input setup time for:<br>D15 … D0 (read data)                | <i>tc</i> <sub>30</sub> | SR | 24           | -    | ns   |

| Input hold time<br>D15 … D0 (read data) <sup>1)</sup>        | <i>tc</i> <sub>31</sub> | SR | -5           | -    | ns   |

Read data are latched with the same (internal) clock edge that triggers the address change and the rising edge of RD. Therefore address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can be removed after the rising edge of RD.

Note: The shaded parameters have been verified by characterization. They are not subject to production test.

Figure 20 Multiplexed Bus Cycle

# 5 Package and Reliability

## 5.1 Packaging

### Table 21Package Parameters

| Parameter                            | Symbol             | Limit Values |         | Unit | Notes       |

|--------------------------------------|--------------------|--------------|---------|------|-------------|

|                                      |                    | Min.         | Max.    |      |             |

| Green Package PG-TQ                  | FP-100-5           | 1            | - I     |      |             |

| Thermal resistance junction to case  | $R_{\Theta JC}$    | -            | 8 / 11  | K/W  | Flash / ROM |

| Thermal resistance junction to leads | $R_{ m \Theta JL}$ | -            | 32 / 37 | K/W  | Flash / ROM |

| Standard Package P-T                 | QFP-100-16         |              | ·       | •    | - <b>·</b>  |

| Thermal resistance junction to case  | $R_{\Theta JC}$    | -            | 7       | K/W  | Flash       |

| Thermal resistance junction to leads | $R_{ m \Theta JL}$ | -            | 24      | K/W  | Flash       |