#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20MHz                                                                          |

| Connectivity               | CANbus, EBI/EMI, SPI, UART/USART                                               |

| Peripherals                | PWM, WDT                                                                       |

| Number of I/O              | 79                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 6K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                   |

| Data Converters            | ·                                                                              |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-LQFP                                                                       |

| Supplier Device Package    | PG-TQFP-100-5                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc164d-8f20f-bb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2006-08 Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2006. All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Data Sheet, V1.2, Aug. 2006

# XC164D-16F/16R XC164D-8F/8R

16-Bit Single-Chip Microcontroller with C166SV2 Core

# Microcontrollers

Never stop thinking

#### **General Device Information**

# 2 General Device Information

#### 2.1 Introduction

The XC164D derivatives are high-performance members of the Infineon XC166 Family of full featured single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 40 million instructions per second) with high peripheral functionality and enhanced IO-capabilities. They also provide clock generation via PLL and various on-chip memory modules such as program Flash, program RAM, and data RAM.

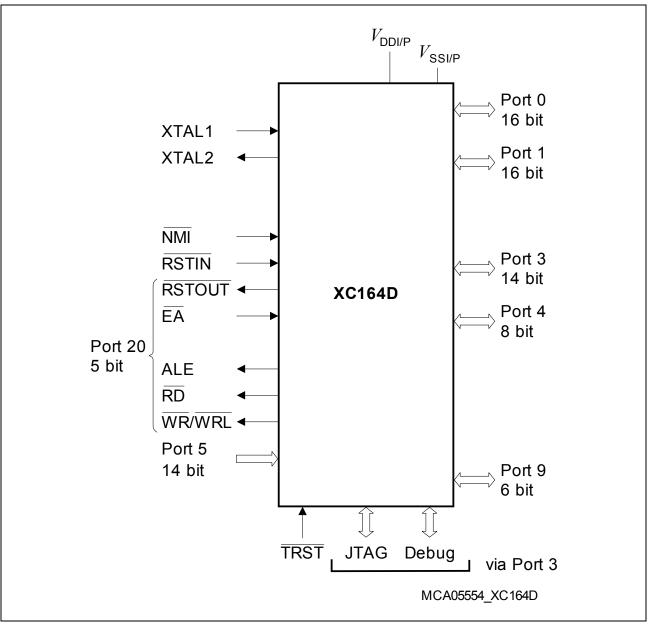

Figure 1 Logic Symbol

#### **General Device Information**

| Table 2           | Piı         | n Definit            | ions and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Pin<br>Num. | Input<br>Outp.       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PORT1             |             | Ю                    | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (cont'd)<br>P1H.0 | 89          | 1                    | CC6POS0CAPCOM6: Position 0 Input,EX0INFast External Interrupt 0 Input (default pin),                                                                                                                                                                                                                                                                                                                                                                                                    |

| P1H.1             | 90          | I/O<br>I<br>I        | CC23IOCAPCOM2: CC23 Capture Inp./Compare Outp.CC6POS1CAPCOM6: Position 1 Input,EX1INFast External Interrupt 1 Input (default pin),MD0T12021 Market Press (2010)                                                                                                                                                                                                                                                                                                                         |

| P1H.2             | 91          | I/O<br>I<br>I        | MRST1SSC1 Master-Receive/Slave-Transmit In/Out.CC6POS2CAPCOM6: Position 2 Input,EX2INFast External Interrupt 2 Input (default pin),                                                                                                                                                                                                                                                                                                                                                     |

| P1H.3             | 92          | I/O<br>I<br>I/O<br>I | MTSR1SSC1 Master-Transmit/Slave-Receive Out/Inp.T7INCAPCOM2: Timer T7 Count Input,SCLK1SSC1 Master Clock Output / Slave Clock Input,EX3INFast External Interrupt 3 Input (default pin),                                                                                                                                                                                                                                                                                                 |

| P1H.4             | 93          | <br> /O<br>          | <ul><li>EX0IN Fast External Interrupt 0 Input (alternate pin A)</li><li>CC24IO CAPCOM2: CC24 Capture Inp./Compare Outp.,</li><li>EX4IN Fast External Interrupt 4 Input (default pin)</li></ul>                                                                                                                                                                                                                                                                                          |

| P1H.5             | 94          | I/O<br>I             | CC25IO CAPCOM2: CC25 Capture Inp./Compare Outp.,<br>EX5IN Fast External Interrupt 5 Input (default pin)                                                                                                                                                                                                                                                                                                                                                                                 |

| P1H.6             | 95          | I/O<br>I             | CC26IO CAPCOM2: CC26 Capture Inp./Compare Outp.,<br>EX6IN Fast External Interrupt 6 Input (default pin)                                                                                                                                                                                                                                                                                                                                                                                 |

| P1H.7             | 96          | I/O<br>I             | CC27IOCAPCOM2: CC27 Capture Inp./Compare Outp.,EX7INFast External Interrupt 7 Input (default pin)                                                                                                                                                                                                                                                                                                                                                                                       |

| XTAL2<br>XTAL1    | 99<br>100   | O<br>I               | XTAL2:Output of the oscillator amplifier circuitXTAL1:Input to the oscillator amplifier and input to the<br>internal clock generatorTo clock the device from an external source, drive XTAL1,<br>while leaving XTAL2 unconnected. Minimum and maximum<br>high/low and rise/fall times specified in the AC<br>Characteristics must be observed.Note:Input pin XTAL1 belongs to the core voltage domain.<br>Therefore, input voltages must be within the range<br>defined for $V_{DDI}$ . |

| res               | 28          | -                    | Pin is reserved and should be connected to $V_{\text{DDP}}$ or $V_{\text{SSP}}$                                                                                                                                                                                                                                                                                                                                                                                                         |

| res               | 29          | -                    | Pin is reserved and should be connected to $V_{\rm SSP}$                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### 3.4 Interrupt System

With an interrupt response time of typically 8 CPU clocks (in case of internal program execution), the XC164D is capable of reacting very fast to the occurrence of non-deterministic events.

The architecture of the XC164D supports several mechanisms for fast and flexible response to service requests that can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source, or the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source related vector location. PEC services are very well suited, for example, for supporting the transmission or reception of blocks of data. The XC164D has 8 PEC channels each of which offers such fast interrupt-driven data transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield exists for each of the possible interrupt nodes. Via its related register, each node can be programmed to one of sixteen interrupt priority levels. Once having been accepted by the CPU, an interrupt service can only be interrupted by a higher prioritized service request. For the standard interrupt processing, each of the possible interrupt nodes has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge, or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

**Table 4** shows all of the possible XC164D interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not assigned to peripherals (unassigned nodes), may be used to generate software controlled interrupt requests by setting the respective interrupt request bit (xIR).

#### Table 4XC164D Interrupt Nodes

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAPCOM Register 0                             | CC1_CC0IC           | xx'0040 <sub>H</sub>             | 10 <sub>H</sub> / 16 <sub>D</sub> |

| CAPCOM Register 1                             | CC1_CC1IC           | xx'0044 <sub>H</sub>             | 11 <sub>H</sub> / 17 <sub>D</sub> |

| CAPCOM Register 2                             | CC1_CC2IC           | xx'0048 <sub>H</sub>             | 12 <sub>H</sub> / 18 <sub>D</sub> |

| CAPCOM Register 3                             | CC1_CC3IC           | xx'004C <sub>H</sub>             | 13 <sub>H</sub> / 19 <sub>D</sub> |

| CAPCOM Register 4                             | CC1_CC4IC           | xx'0050 <sub>H</sub>             | 14 <sub>H</sub> / 20 <sub>D</sub> |

| CAPCOM Register 5                             | CC1_CC5IC           | xx'0054 <sub>H</sub>             | 15 <sub>H</sub> / 21 <sub>D</sub> |

| CAPCOM Register 6                             | CC1_CC6IC           | xx'0058 <sub>H</sub>             | 16 <sub>H</sub> / 22 <sub>D</sub> |

| CAPCOM Register 7                             | CC1_CC7IC           | xx'005C <sub>H</sub>             | 17 <sub>H</sub> / 23 <sub>D</sub> |

| CAPCOM Register 8                             | CC1_CC8IC           | xx'0060 <sub>H</sub>             | 18 <sub>H</sub> / 24 <sub>D</sub> |

| CAPCOM Register 9                             | CC1_CC9IC           | xx'0064 <sub>H</sub>             | 19 <sub>H</sub> / 25 <sub>D</sub> |

| CAPCOM Register 10                            | CC1_CC10IC          | xx'0068 <sub>H</sub>             | 1A <sub>H</sub> / 26 <sub>D</sub> |

| CAPCOM Register 11                            | CC1_CC11IC          | xx'006C <sub>H</sub>             | 1B <sub>H</sub> / 27 <sub>D</sub> |

| CAPCOM Register 12                            | CC1_CC12IC          | xx'0070 <sub>H</sub>             | 1C <sub>H</sub> / 28 <sub>D</sub> |

| CAPCOM Register 13                            | CC1_CC13IC          | xx'0074 <sub>H</sub>             | 1D <sub>H</sub> / 29 <sub>D</sub> |

| CAPCOM Register 14                            | CC1_CC14IC          | xx'0078 <sub>H</sub>             | 1E <sub>H</sub> / 30 <sub>D</sub> |

| CAPCOM Register 15                            | CC1_CC15IC          | xx'007C <sub>H</sub>             | 1F <sub>H</sub> / 31 <sub>D</sub> |

| CAPCOM Register 16                            | CC2_CC16IC          | xx'00C0 <sub>H</sub>             | 30 <sub>H</sub> / 48 <sub>D</sub> |

| CAPCOM Register 17                            | CC2_CC17IC          | xx'00C4 <sub>H</sub>             | 31 <sub>H</sub> / 49 <sub>D</sub> |

| CAPCOM Register 18                            | CC2_CC18IC          | xx'00C8 <sub>H</sub>             | 32 <sub>H</sub> / 50 <sub>D</sub> |

| CAPCOM Register 19                            | CC2_CC19IC          | xx'00CC <sub>H</sub>             | 33 <sub>H</sub> / 51 <sub>D</sub> |

| CAPCOM Register 20                            | CC2_CC20IC          | xx'00D0 <sub>H</sub>             | 34 <sub>H</sub> / 52 <sub>D</sub> |

| CAPCOM Register 21                            | CC2_CC21IC          | xx'00D4 <sub>H</sub>             | 35 <sub>H</sub> / 53 <sub>D</sub> |

| CAPCOM Register 22                            | CC2_CC22IC          | xx'00D8 <sub>H</sub>             | 36 <sub>H</sub> / 54 <sub>D</sub> |

| CAPCOM Register 23                            | CC2_CC23IC          | xx'00DC <sub>H</sub>             | 37 <sub>H</sub> / 55 <sub>D</sub> |

| CAPCOM Register 24                            | CC2_CC24IC          | xx'00E0 <sub>H</sub>             | 38 <sub>H</sub> / 56 <sub>D</sub> |

| CAPCOM Register 25                            | CC2_CC25IC          | xx'00E4 <sub>H</sub>             | 39 <sub>H</sub> / 57 <sub>D</sub> |

| CAPCOM Register 26                            | CC2_CC26IC          | xx'00E8 <sub>H</sub>             | 3A <sub>H</sub> / 58 <sub>D</sub> |

| CAPCOM Register 27                            | CC2_CC27IC          | xx'00EC <sub>H</sub>             | 3B <sub>H</sub> / 59 <sub>D</sub> |

| CAPCOM Register 28                            | CC2_CC28IC          | xx'00F0 <sub>H</sub>             | 3C <sub>H</sub> / 60 <sub>D</sub> |

# 3.8 General Purpose Timer Unit (GPT12E)

The GPT12E unit represents a very flexible multifunctional timer/counter structure which may be used for many different time related tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers which are organized in two separate modules, GPT1 and GPT2. Each timer in each module may operate independently in a number of different modes, or may be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation, which are Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock, divided by a programmable prescaler, while Counter Mode allows a timer to be clocked in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes, each timer has one associated port pin (TxIN) which serves as gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD) to facilitate e.g. position tracking.

In Incremental Interface Mode the GPT1 timers (T2, T3, T4) can be directly connected to the incremental position sensor signals A and B via their respective inputs TxIN and TxEUD. Direction and count signals are internally derived from these two input signals, so the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload or capture registers for timer T3. When used as capture or reload registers, timers T2 and T4 are stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of T2 or T4 triggered either by an external signal or by a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be constantly generated without software intervention.

count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD). Concatenation of the timers is supported via the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

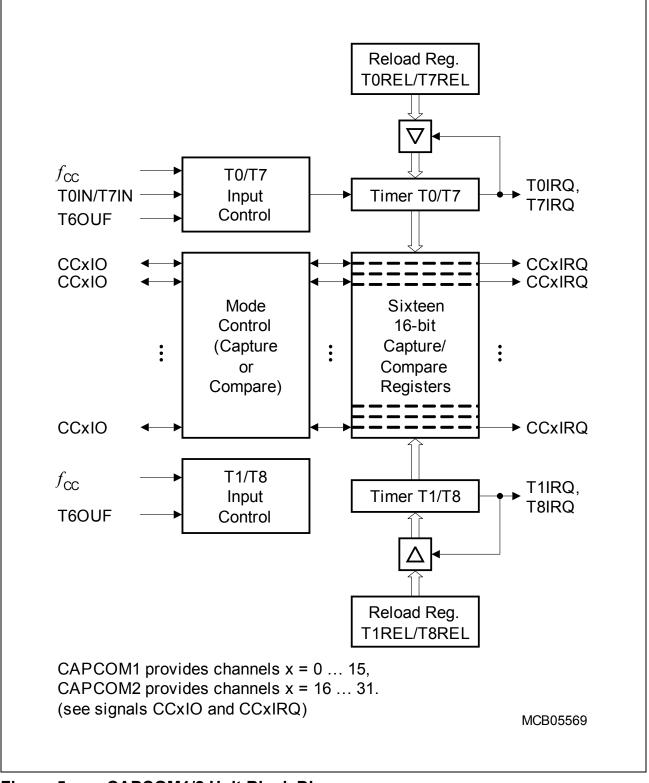

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can additionally be used to clock the CAPCOM1/2 timers, and to cause a reload from the CAPREL register.

The CAPREL register may capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN), and timer T5 may optionally be cleared after the capture procedure. This allows the XC164D to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer T3's inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

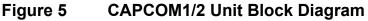

## 3.9 Real Time Clock

The Real Time Clock (RTC) module of the XC164D is directly clocked via a separate clock driver with the prescaled on-chip main oscillator frequency ( $f_{\rm RTC} = f_{\rm OSCm}/32$ ). It is therefore independent from the selected clock generation mode of the XC164D.

The RTC basically consists of a chain of divider blocks:

- a selectable 8:1 divider (on off)

- the reloadable 16-bit timer T14

- the 32-bit RTC timer block (accessible via registers RTCH and RTCL), made of:

- a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

#### Figure 9 RTC Block Diagram

Note: The registers associated with the RTC are not affected by a reset in order to maintain the correct system time even when intermediate resets are executed.

The RTC module can be used for different purposes:

- System clock to determine the current time and date, optionally during idle mode, sleep mode, and power down mode.

- Cyclic time based interrupt, to provide a system time tick independent of CPU frequency and other resources, e.g. to wake up regularly from idle mode.

- 48-bit timer for long term measurements (maximum timespan is >> 100 years).

- Alarm interrupt for wake-up on a defined time.

### 3.13 Watchdog Timer

The Watchdog Timer represents one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after a reset of the chip, and can be disabled until the EINIT instruction has been executed (compatible mode), or it can be disabled and enabled at any time by executing instructions DISWDT and ENWDT (enhanced mode). Thus, the chip's start-up procedure is always monitored. The software has to be designed to restart the Watchdog Timer before it overflows. If, due to hardware or software related failures, the software fails to do so, the Watchdog Timer overflows and generates an internal hardware reset and pulls the RSTOUT pin low in order to allow external hardware components to be reset.

The Watchdog Timer is a 16-bit timer, clocked with the system clock divided by 2/4/128/256. The high byte of the Watchdog Timer register can be set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the high byte of the Watchdog Timer is reloaded and the low byte is cleared. Thus, time intervals between 13 µs and 419 ms can be monitored (@ 40 MHz).

The default Watchdog Timer interval after reset is 3.28 ms (@ 40 MHz).

| Table 8Instruction Set Summary (cont'd) |                                     |       |  |  |

|-----------------------------------------|-------------------------------------|-------|--|--|

| Mnemonic                                | Description                         | Bytes |  |  |

| NOP                                     | Null operation                      | 2     |  |  |

| CoMUL/CoMAC                             | Multiply (and accumulate)           | 4     |  |  |

| CoADD/CoSUB                             | Add/Subtract                        | 4     |  |  |

| Co(A)SHR                                | (Arithmetic) Shift right            | 4     |  |  |

| CoSHL                                   | Shift left                          | 4     |  |  |

| CoLOAD/STORE                            | Load accumulator/Store MAC register | 4     |  |  |

| CoCMP                                   | Compare                             | 4     |  |  |

| CoMAX/MIN                               | Maximum/Minimum                     | 4     |  |  |

| CoABS/CoRND                             | Absolute value/Round accumulator    | 4     |  |  |

| CoMOV                                   | Data move                           | 4     |  |  |

| CoNEG/NOP                               | Negate accumulator/Null operation   | 4     |  |  |

#### 4.1 General Parameters

#### Table 9 Absolute Maximum Ratings

| Parameter                                                                   | Symbol Limit Values |      | Values                 | Unit | Notes      |  |

|-----------------------------------------------------------------------------|---------------------|------|------------------------|------|------------|--|

|                                                                             |                     | Min. | Max.                   |      |            |  |

| Storage temperature                                                         | T <sub>ST</sub>     | -65  | 150                    | °C   | 1)         |  |

| Junction temperature                                                        | TJ                  | -40  | 150                    | °C   | under bias |  |

| Voltage on $V_{\text{DDI}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DDI</sub>    | -0.5 | 3.25                   | V    | -          |  |

| Voltage on $V_{\text{DDP}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DDP</sub>    | -0.5 | 6.2                    | V    | -          |  |

| Voltage on any pin with respect to ground $(V_{SS})$                        | V <sub>IN</sub>     | -0.5 | V <sub>DDP</sub> + 0.5 | V    | 2)         |  |

| Input current on any pin during overload condition                          | -                   | -10  | 10                     | mA   | -          |  |

| Absolute sum of all input<br>currents during overload<br>condition          | -                   | -    | 100                    | mA   | _          |  |

1) Moisture Sensitivity Level (MSL) 3, conforming to Jedec J-STD-020C for 260 °C for PG-TQFP-100-5, and 240 °C for P-TQFP-100-16.

2) Input pin XTAL1 belongs to the core voltage domain. Therefore, input voltages must be within the range defined for  $V_{\text{DDI}}$ .

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### **Operating Conditions**

The following operating conditions must not be exceeded to ensure correct operation of the XC164D. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

| Parameter                                 | Symbol              | Limit Values |                        | Unit | Notes                                            |

|-------------------------------------------|---------------------|--------------|------------------------|------|--------------------------------------------------|

|                                           |                     | Min.         | Max.                   |      |                                                  |

| Digital supply voltage for the core       | V <sub>DDI</sub>    | 2.35         | 2.7                    | V    | Active mode,<br>$f_{CPU} = f_{CPUmax}^{1)2)}$    |

| Digital supply voltage for<br>IO pads     | V <sub>DDP</sub>    | 4.4          | 5.5                    | V    | Active mode <sup>2)3)</sup>                      |

| Supply Voltage Difference                 | $\Delta V_{\rm DD}$ | -0.5         | -                      | V    | $V_{\rm DDP}$ - $V_{\rm DDI}^{4)}$               |

| Digital ground voltage                    | V <sub>SS</sub>     |              | 0                      | V    | Reference voltage                                |

| Overload current                          | I <sub>OV</sub>     | -5           | 5                      | mA   | Per IO pin <sup>5)6)</sup>                       |

|                                           |                     | -2           | 5                      | mA   | Per Port 5 input<br>pin <sup>5)6)</sup>          |

| Overload current coupling                 | K <sub>OVA</sub>    | -            | 1.0 × 10 <sup>-4</sup> | -    | <i>I</i> <sub>OV</sub> > 0                       |

| factor for Port 5 inputs <sup>7)</sup>    |                     | _            | 1.5 × 10 <sup>-3</sup> | -    | I <sub>OV</sub> < 0                              |

| Overload current coupling                 | K <sub>OVD</sub>    | -            | 5.0 × 10 <sup>-3</sup> | -    | I <sub>OV</sub> > 0                              |

| factor for digital I/O pins <sup>7)</sup> |                     | _            | 1.0 × 10 <sup>-2</sup> | -    | I <sub>OV</sub> < 0                              |

| Absolute sum of overload currents         | $\Sigma  I_{OV} $   | -            | 50                     | mA   | 6)                                               |

| External Load<br>Capacitance              | CL                  | -            | 50                     | pF   | Pin drivers in <b>default</b> mode <sup>8)</sup> |

| Ambient temperature                       | T <sub>A</sub>      | _            | _                      | °C   | see Table 1                                      |

#### Table 10 Operating Condition Parameters

1)  $f_{CPUmax}$  = 40 MHz for devices marked ... 40F,  $f_{CPUmax}$  = 20 MHz for devices marked ... 20F.

2) External circuitry must guarantee low-level at the RSTIN pin at least until both power supply voltages have reached the operating range.

- 3) The specified voltage range is allowed for operation. The range limits may be reached under extreme operating conditions. However, specified parameters, such as leakage currents, refer to the standard operating voltage range of  $V_{\text{DDP}}$  = 4.75 V to 5.25 V.

- 4) This limitation must be fulfilled under all operating conditions including power-ramp-up, power-ramp-down, and power-save modes.

5) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range:  $V_{OV} > V_{DDP} + 0.5 \vee (I_{OV} > 0)$  or  $V_{OV} < V_{SS} - 0.5 \vee (I_{OV} < 0)$ . The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltages must remain within the specified limits.

Proper operation is not guaranteed if overload conditions occur on functional pins such as XTAL1,  $\overline{RD}$ ,  $\overline{WR}$ , etc.

- 6) Not subject to production test verified by design/characterization.

- 7) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it.

The total current through a pin is  $|I_{\text{TOT}}| = |I_{\text{OZ}}| + (|I_{\text{OV}}| \times K_{\text{OV}}).$

8) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability ( $C_L$ ).

#### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the XC164D and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the XC164D will provide signals with the respective characteristics.

#### **SR** (System Requirement):

The external system must provide signals with the respective characteristics to the XC164D.

| PLLCON.PLLVB | VCO Frequency Range | Base Frequency Range |

|--------------|---------------------|----------------------|

| 00           | 100 150 MHz         | 20 80 MHz            |

| 01           | 150 200 MHz         | 40 130 MHz           |

| 10           | 200 250 MHz         | 60 180 MHz           |

| 11           | Reserved            | · · ·                |

#### Table 14VCO Bands for PLL Operation<sup>1)</sup>

1) Not subject to production test - verified by design/characterization.

# 4.3.3 External Clock Drive XTAL1

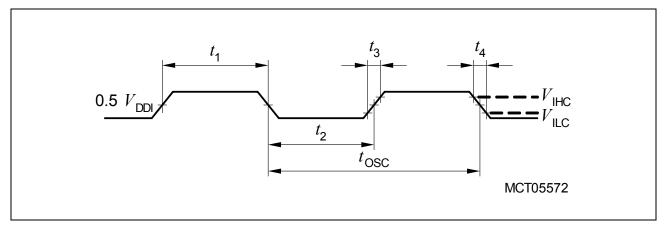

#### Table 17 External Clock Drive Characteristics (Operating Conditions apply)

| Parameter               | Symbol           |    | Limit Values |                   | Unit |

|-------------------------|------------------|----|--------------|-------------------|------|

|                         |                  |    | Min.         | Max.              |      |

| Oscillator period       | t <sub>OSC</sub> | SR | 25           | 250 <sup>1)</sup> | ns   |

| High time <sup>2)</sup> | t <sub>1</sub>   | SR | 6            | _                 | ns   |

| Low time <sup>2)</sup>  | t <sub>2</sub>   | SR | 6            | _                 | ns   |

| Rise time <sup>2)</sup> | t <sub>3</sub>   | SR | _            | 8                 | ns   |

| Fall time <sup>2)</sup> | t <sub>4</sub>   | SR | _            | 8                 | ns   |

1) The maximum limit is only relevant for PLL operation to ensure the minimum input frequency for the PLL.

2) The clock input signal must reach the defined levels  $V_{\rm ILC}$  and  $V_{\rm IHC}$ .

#### Figure 16 External Clock Drive XTAL1

Note: If the on-chip oscillator is used together with a crystal or a ceramic resonator, the oscillator frequency is limited to a range of 4 MHz to 16 MHz.

It is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the limits specified by the crystal supplier.

When driven by an external clock signal it will accept the specified frequency range. Operation at lower input frequencies is possible but is verified by design only (not subject to production test).

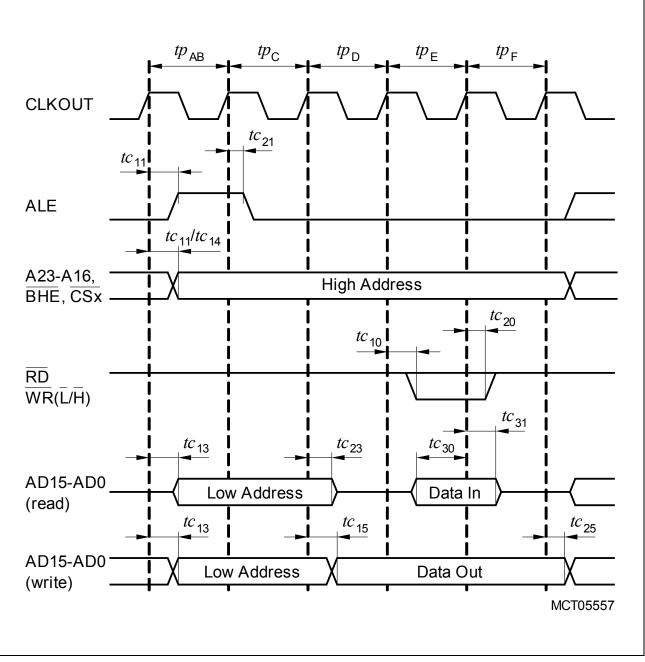

Figure 20 Multiplexed Bus Cycle

www.infineon.com