Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                     |

|----------------------------|--------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                         |

| Speed                      | 180MHz                                                                                     |

| Connectivity               | CANbus, CSIO, EBI/EMI, Ethernet, I <sup>2</sup> C, LINbus, SmartCard, SPI, UART/USART, USB |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                                  |

| Number of I/O              | 153                                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                                               |

| Program Memory Type        | FLASH                                                                                      |

| EEPROM Size                | -                                                                                          |

| RAM Size                   | 192K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                                |

| Data Converters            | A/D 32x12b                                                                                 |

| Oscillator Type            | Internal                                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                              |

| Package / Case             | 176-LQFP                                                                                   |

| Supplier Device Package    | 176-LQFP (24x24)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e2g28jhagv2000a               |

|                            |                                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- □ LIN break delimiter generation (can change to 1- to 4-bit length)

- Various error detect functions available (parity errors, framing errors, and overrun errors)

- I<sup>2</sup>C

- □ Standard mode (Max 100 kbps)/Fast mode (Max 400 kbps) supported

- $\square$  Fast mode Plus (Fm+) (Max 1000 kbps, only for ch 3 = ch A and ch 7 = ch B) supported

- I<sup>2</sup>S

□ Using CSIO (SPI) (ch 1 only) and I<sup>2</sup>S clock generator □ Supports two transfer protocol: I<sup>2</sup>S and MSB-justified □ Master mode only

# DMA Controller (Eight Channels)

DMA controller has an independent bus, so the CPU and DMA controller can process simultaneously.

- Eight independently configured and operated channels

- Transfer can be started by software or request from the built-in peripherals

- Transfer address area: 32-bit (4 GB)

- Transfer mode: Block transfer/Burst transfer/Demand transfer

- Transfer data type: bytes/half-word/word

- Transfer block count: 1 to 16

- Number of transfers: 1 to 65536

# DSTC (Descriptor System Data Transfer Controller; 256 channels)

The DSTC can transfer data at high-speed without going via the CPU. The DSTC adopts the descriptor system and, following the specified contents of the descriptor that has already been constructed on the memory, can access directly the memory/peripheral device and perform the data-transfer operation.

It supports the software activation, the hardware activation, and the chain activation functions.

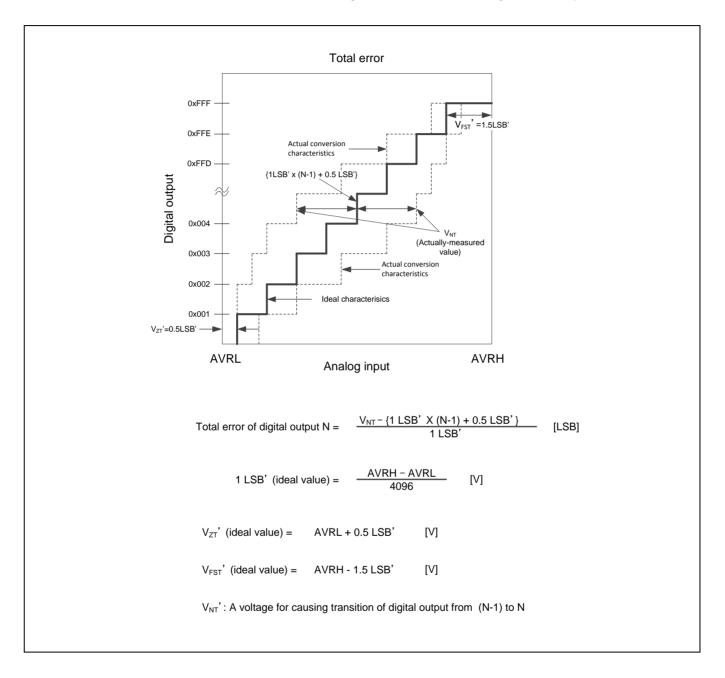

# A/D Converter (Max 32 Channels)

- 12-bit A/D Converter

- □ Successive approximation type

- Built-in three units

- □ Conversion time: 0.5 µs at 5 V

- □ Priority conversion available (priority at two levels)

- □ Scanning conversion mode

- Built-in FIFO for conversion data storage (for SCAN conversion: 16 steps, for priority conversion: 4 steps)

### Base Timer (Max 16 channels)

Operation mode is selected from the following for each channel:

16-bit PWM timer

- 16-bit PPG timer

- 16-/32-bit reload timer

- 16-/32-bit PWC timer

- Event counter mode (External clock mode)

#### **General Purpose I/O Port**

This series can use its pins as general purpose I/O ports when they are not used for external bus or peripherals; moreover, the port relocate function is built in. It can set the I/O port to which the peripheral function can be allocated.

- Capable of pull-up control per pin

- Capable of reading pin level directly

- Built-in port-relocate function

- Up to 121 high-speed general-purpose I/O ports in 144-pin package

- Some pins 5 V tolerant I/O. See 6. Pin Descriptions and 7. I/O Circuit Type for the corresponding pins.

#### Multi-function Timer (Max two units)

The multi-function timer is composed of the following blocks: Minimum resolution: 5.56 ns

- 16-bit free-run timer × 3 ch/unit

- Input capture × 4 ch/unit

- Output compare × 6 ch/unit

- A/D activation compare × 6 ch/unit

- Waveform generator × 3 ch/unit

- 16-bit PPG timer × 3 ch/unit

The following functions can be used to achieve the motor control:

- PWM signal output function

- DC chopper waveform output function

- Dead time function

- Input capture function

- A/D convertor activate function

- DTIF (motor emergency stop) interrupt function

#### **Real-Time Clock (RTC)**

The real-time clock can count year, month, day, hour, minute, second, or day of the week from 00 to 99.

- Interrupt function with specifying date and time (year/month/day/hour/minute) is available. This function is also available by specifying only year, month, day, hour, or minute.

- Timer interrupt function after set time or each set time.

- Capable of rewriting the time with continuing the time count.

- Leap year automatic count is available.

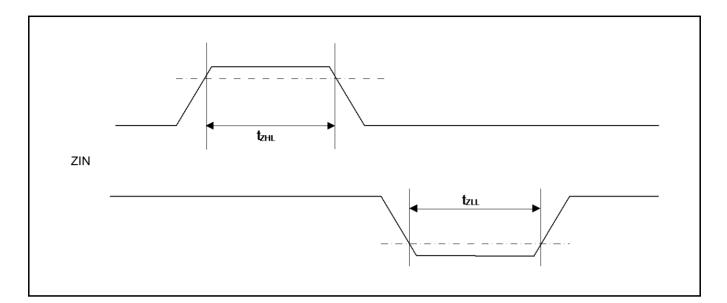

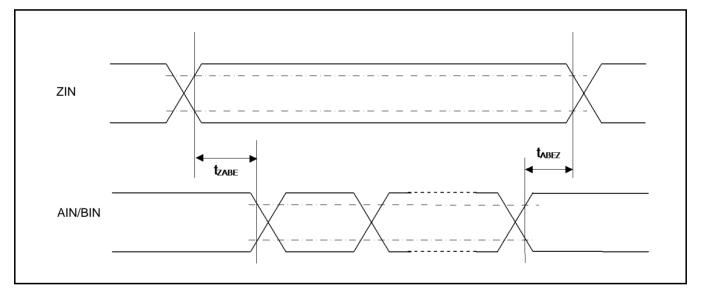

# Quadrature Position/Revolution Counter (QPRC; Max two channels)

The Quadrature Position/Revolution Counter (QPRC) is used to measure the position of the position encoder. It is also possible to use up/down counter.

- The detection edge of the three external event input pins AIN, BIN and ZIN is configurable.

- 16-bit position counter

- 16-bit revolution counter

- Two 16-bit compare registers

#### Dual Timer (32-/16-bit Down Counter)

The dual timer consists of two programmable 32-/16-bit down counters.

Operation mode is selectable from the following for each channel:

- Free-running

- Periodic (= Reload)

- One shot

#### Watch Counter

The watch counter is used for wake up from low-power consumption mode. It is possible to select the main clock, sub clock, built-in High-speed CR clock, or built-in low-speed CR clock as the clock source.

Interval timer: up to 64 s (max) with a sub clock of 32.768 kHz

#### **External Interrupt Controller Unit**

- External interrupt input pin: Max 32 pins

Both edges(Rise edge and Fall edge) detect

- Include one non-maskable interrupt (NMI)

#### Watchdog Timer (Two channels)

A watchdog timer can generate interrupts or a reset when a time-out value is reached.

This series consists of two different watchdogs: a "hardware" watchdog and a "software" watchdog.

The hardware watchdog timer is clocked by low-speed internal CR oscillator. The hardware watchdog is thus active in any power saving mode except RTC mode and Stop mode.

### Cyclic Redundancy Check (CRC) Accelerator

The CRC accelerator helps to verify data transmission or storage integrity.

CCITT CRC16 and IEEE-802.3 CRC32 are supported.

- CCITT CRC16 generator polynomial: 0x1021

- IEEE-802.3 CRC32 generator polynomial: 0x04C11DB7

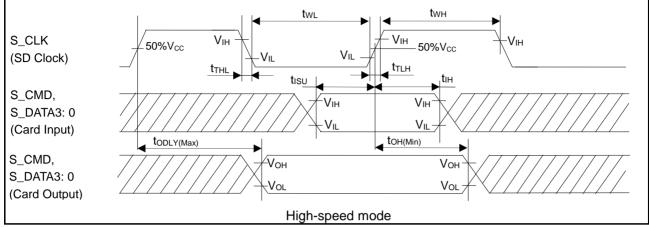

# SD Card Interface Available on S6E2GM, S6E2GH, and S6E2GK Devices Only

It is possible to use the SD card that conforms to the following standards.

- Part 1 Physical Layer Specification version 3.01

- Part E1 SDIO Specification version 3.00

- Part A2 SD Host Controller Standard Specification version 3.00

- 1-bit or 4-bit data bus

# Ethernet-MAC Available on S6E2GM, S6E2GK, and S6E2G2 Devices only

- Compliant with IEEE802.3 specification

- 10 Mbps/100 Mbps data transfer rates supported

- MII/RMII for external PHY device supported.

- MII: Max one channel

- RMII: Max one channel

- Full-duplex and half-duplex mode supported.

- Wake-ON-LAN supported

- Built-in dedicated descriptor-system DMAC

- Built-in 2 Kbytes transmit FIFO and 2 Kbytes receive FIFO.

- Compliant IEEE1558-2008 (PTP)

#### Smartcard Interface (Max 2 channels)

- Compliant with ISO7816-3 specification

- Card Reader only/B class card only

- Available protocols

Transmitter: 8E2, 8O2, 8N2

Receiver: 8E1, 8O1, 8N2, 8N1, 9N1

Inverse mode

- TX/RX FIFO integrated (RX: 16-bytes, TX:16-bytes)

#### **Clock and Reset**

#### Clocks

Five clock sources (two external oscillators, two internal CR oscillators, and Main PLL) that are dynamically selectable.

□ Main clock: 4 MHz to 48 MHz

□ Sub clock: 30 kHz to 100 kHz

□ High-speed internal CR clock: 4 MHz

□ Low-speed internal CR clock: 100 kHz

□ Main PLL Clock

| Pin Number |          | Pin Name             | I/O<br>Circuit | Pin State |  |

|------------|----------|----------------------|----------------|-----------|--|

| LQFP-176   | LQFP-144 |                      | Туре           | Туре      |  |

|            |          | P41                  |                |           |  |

|            |          | SOT7_1<br>(SDA7_1)   |                |           |  |

| 47         | 39       | RTO11_0<br>(PPG11_0) | G              | I.        |  |

|            |          | TIOA1_0              |                |           |  |

|            |          | BIN0_0               | _              |           |  |

|            |          | MCSX6_0              |                |           |  |

|            |          | P42                  |                |           |  |

|            |          | SCK7_1<br>(SCL7_1)   |                |           |  |

| 48         | 40       | RTO12_0<br>(PPG12_0) | G              | I         |  |

|            |          | TIOA2_0              |                |           |  |

|            |          | ZIN0_0               |                |           |  |

|            |          | MCSX5_0              |                |           |  |

|            |          | P43                  | _              |           |  |

|            | 41       | SCS70_1              |                |           |  |

| 49         |          | RTO13_0<br>(PPG13_0) | G              | к         |  |

|            |          | TIOA3_0              | -              |           |  |

|            |          | INT04_0              |                |           |  |

|            |          | MCSX4_0              |                |           |  |

|            | 42       | P44                  | _              |           |  |

|            |          | SCS71_1              |                |           |  |

| 50         |          | RTO14_0<br>(PPG14_0) | G              | I.        |  |

|            |          | TIOA4_0              |                |           |  |

|            |          | MCSX3_0              |                |           |  |

|            |          | P45                  |                |           |  |

|            |          | SCS72_1              |                |           |  |

| 51         | 43       | RTO15_0<br>(PPG15_0) | G              | I.        |  |

|            |          | TIOA5_0              |                |           |  |

|            |          | MCSX2_0              |                |           |  |

| 52         | 44       | С                    | -              | -         |  |

| 53         | 45       | VSS                  | -              | -         |  |

| 54         | 46       | VCC                  | -              | -         |  |

| 55         | 47       | P46                  | D              | S         |  |

|            | 4/       | X0A                  |                | 3         |  |

| 56         | 48       | P47                  | D              | Т         |  |

|            |          | X1A                  |                |           |  |

| 57         | 49       | INITX                | В              | С         |  |

| Pin Number |          | Dia Mara           | I/O             | Pin State |

|------------|----------|--------------------|-----------------|-----------|

| LQFP-176   | LQFP-144 | Pin Name           | Circuit<br>Type | Туре      |

|            |          | P14                |                 | 1         |

|            | -        | AN04               |                 |           |

|            |          | SOT9_1             |                 |           |

| 98         | 82       | (SDA9_1)           | F               | N         |

|            |          | TIOA2_2            |                 |           |

|            |          | IC1_DATA_0         |                 |           |

|            |          | TRACED0            |                 |           |

|            | _        | P15                |                 |           |

|            | _        | AN05               |                 |           |

| 00         | 00       | SCK9_1<br>(SCL9_1) | _               | N         |

| 99         | 83       | TIOB2_2            | F               | Ν         |

|            | -        | IC1_CIN_0          | —               |           |

|            | -        | TRACED1            | —               |           |

|            |          | P16                |                 |           |

|            | -        | AN06               | _               |           |

|            | -        | SIN6_1             |                 |           |

| 100        | 84 -     | RX0_0              | F               | 0         |

|            | -        | INT09_0            |                 |           |

|            | -        | TRACED2            |                 |           |

|            |          | P17                |                 |           |

|            | -        | AN07               |                 |           |

|            | 85       | SOT6_1             | _               |           |

| 101        |          | (SDA6_1)           | F               | N         |

|            |          | TX0_0              |                 |           |

|            |          | TRACED3            |                 |           |

|            |          | PB0                |                 | N         |

|            |          | AN16               |                 |           |

| 102        | -        | SCK6_1             | F               |           |

|            | -        | (SCL6_1)           |                 |           |

|            | -        | TIOA9_1            |                 |           |

|            |          | TRACED8            |                 |           |

|            | -        | PB1                |                 |           |

|            |          | AN17               |                 |           |

| 400        |          | SCS60_1            |                 | ~         |

| 103        | -        | TIOB9_1            | F               | 0         |

|            |          | AIN0_2             | -               |           |

|            |          | INT08_1            |                 |           |

|            |          | TRACED9            |                 |           |

|            |          | PB2                |                 |           |

|            |          | AN18               |                 |           |

| 104        |          | SCS61_1            |                 | ~         |

| 104        |          | TIOA10_1           | F               | 0         |

|            |          | BIN0_2             |                 |           |

|            |          | INT09_1            |                 |           |

|            |          | TRACED10           |                 | <u> </u>  |

| Pin Number |          | <b>D</b> 1 11  | I/O             | Pin State |  |

|------------|----------|----------------|-----------------|-----------|--|

| LQFP-176   | LQFP-144 | Pin Name       | Circuit<br>Type | Туре      |  |

|            |          | PB6            |                 |           |  |

|            |          | AN22           |                 |           |  |

|            |          | SOT8_1         | _               |           |  |

| 112        | -        | (SDA8_1)       | F               | Ν         |  |

|            |          | TIOA12_1       |                 |           |  |

|            |          | BIN1_2         | _               |           |  |

|            |          | TRACED14       |                 |           |  |

|            |          | PB7            |                 |           |  |

|            |          | AN23           |                 |           |  |

|            |          | SCK8_1         |                 |           |  |

| 113        | -        | (SCL8_1)       | F               | N         |  |

|            |          | TIOB12_1       |                 |           |  |

|            |          | ZIN1_2         |                 |           |  |

|            |          | TRACED15       |                 |           |  |

|            |          | P1C            |                 |           |  |

|            |          | AN12           |                 |           |  |

| 114        | 90       | SCK0_1         | F               | Ν         |  |

|            |          | (SCL0_1)       |                 |           |  |

|            |          | TIOA5_2        |                 |           |  |

|            |          | TRACECLK       |                 |           |  |

|            |          | P1D            |                 | L         |  |

|            |          | AN13           |                 |           |  |

| 115        | 91       | SOT0_1         | F               |           |  |

|            |          | (SDA0_1)       | _               |           |  |

|            |          | TIOB5_2        | _               |           |  |

|            |          | MAD09_0<br>P1E |                 |           |  |

|            |          |                | _               |           |  |

|            |          | AN14<br>SIN0_1 |                 |           |  |

| 116        | 92       |                | F               | М         |  |

|            |          | TIOA8_1        | _               |           |  |

|            |          | INT26_1        | _               |           |  |

|            |          | MAD10_0<br>P1F |                 |           |  |

|            |          | AN15           |                 |           |  |

|            |          |                | _               |           |  |

| 117        | 93       | RTS5_0         | F               | М         |  |

|            |          | TIOB8_1        | _               |           |  |

|            |          | INT27_1        | _               |           |  |

|            |          | MAD11_0        |                 |           |  |

|            |          | P2A            | _               |           |  |

| 110        | 0.1      | AN24           |                 | ь.a       |  |

| 118        | 94       | CTS5_0         | F               | М         |  |

|            |          | INT08_2        | _               |           |  |

|            |          | MAD12_0        |                 |           |  |

| Pin Number |          | <b>-</b>     | 1/0             | Pin State |

|------------|----------|--------------|-----------------|-----------|

| LQFP-176   | LQFP-144 | Pin Name     | Circuit<br>Type | Туре      |

|            |          | PC6          |                 |           |

| 151        | 121      | TIOA14_0     | K               | V         |

|            |          | E_MDIO       |                 |           |

|            |          | PC7          |                 |           |

| 152        | 122      | INT13_0      | E               | W         |

| 102        | 122      | E_MDC        | _               |           |

|            |          | CROUT_1      |                 |           |

| 153        | 123      | PC8          | ĸ               | V         |

|            |          | E_RXCK_REFCK |                 | -         |

|            | -        | PC9          | _               |           |

| 154        | 124      | TIOB15_0     | K               | V         |

|            |          | E_COL        |                 |           |

|            |          | PCA          | 4               |           |

| 155        | 125      | TIOA15_0     | K               | V         |

|            |          | E_CRS        |                 |           |

| 156        | 126      | ETHVCC       | -               | -         |

| 157        | 127      | VSS          | -               | -         |

|            |          | PCB          |                 |           |

| 158        | 128      | INT28_0      | L               | W         |

|            |          | E_COUT       |                 |           |

| 159        | 129      | PCC          | ĸ               | V         |

| 159        | 129      | E_TCK        |                 | V         |

|            |          | PCD          | L               |           |

|            |          | SOT4_1       |                 |           |

| 160        | 130      | (SDA4_1)     |                 | W         |

|            |          | INT14_0      |                 |           |

|            |          | E_TXER       |                 |           |

|            | -        | PCE          | _               |           |

| 161        | 131      | SIN4_1       | L               | W         |

| _          | -        | INT15_0      | 4               |           |

|            |          | E_TX03       |                 |           |

|            |          | PCF          | 4               |           |

| 162        | 132      | RTS4_1       | L               | W         |

| -          | -        | INT12_0      | 4               |           |

|            |          | E_TX02       |                 |           |

|            |          | PD0          | -               |           |

| 163        | 133      | INT30_1      | L               | W         |

|            |          | E_TX01       |                 |           |

|            |          | PD1          | ·               |           |

| 164        | 134      | INT31_1      | L               | W         |

|            |          | E_TX00       |                 |           |

|            |          | PD2          | 4               |           |

| 165        | 135      | CTS4_1       | L               | V         |

|            |          | E_TXEN       |                 |           |

| Modula                       | Din Nome           | Function                                                                                                                                                              | Pin Number |          |  |  |

|------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|--|--|

| Module                       | Pin Name           | Function                                                                                                                                                              | LQFP 176   | LQFP 144 |  |  |

|                              | SIN2_0             | Multi-function serial interface ch 2 input                                                                                                                            | 106        | 86       |  |  |

|                              | SIN2_1             | pin                                                                                                                                                                   | 38         | 33       |  |  |

|                              | SOT2_0<br>(SDA2_0) | Multi-function serial interface ch 2 output pin                                                                                                                       | 107        | 87       |  |  |

| Multi-<br>Function<br>Serial | SOT2_1<br>(SDA2_1) | This pin operates as SOT2 when it is<br>used in a UART/CSIO/LIN (operation<br>modes 0 to 3) and as SDA2 when it is<br>used in an I <sup>2</sup> C (operation mode 4). | 39         | 34       |  |  |

| 2                            | SCK2_0<br>(SCL2_0) | Multi-function serial interface ch 2 clock I/O pin                                                                                                                    | 108        | 88       |  |  |

|                              | SCK2_1<br>(SCL2_1) | This pin operates as SCK2 when it is<br>used in a CSIO (operation mode 2) and<br>as SCL2 when it is used in an I <sup>2</sup> C<br>(operation mode 4).                | 40         | 35       |  |  |

|                              | SIN3_0             | Multi-function serial interface ch 3 input                                                                                                                            | 20         | 17       |  |  |

|                              | SIN3_1             | pin                                                                                                                                                                   | 81         | -        |  |  |

|                              | SOT3_0<br>(SDA3_0) | Multi-function serial interface ch 3 output pin                                                                                                                       | 19         | 16       |  |  |

| Multi-<br>Function<br>Serial | SOT3_1<br>(SDA3_1) | This pin operates as SOT3 when it is<br>used in a UART/CSIO/LIN (operation<br>modes 0 to 3) and as SDA3 when it is<br>used in an I <sup>2</sup> C (operation mode 4). | 82         | -        |  |  |

| 3                            | SCK3_0<br>(SCL3_0) | Multi-function serial interface ch 3 clock                                                                                                                            | 18         | 15       |  |  |

|                              | SCK3_1<br>(SCL3_1) | This pin operates as SCK3 when it is<br>used in a CSIO (operation modes 2) and<br>as SCL3 when it is used in an I <sup>2</sup> C<br>(operation mode 4).               | 83         | -        |  |  |

|                              | SIN4_0             | Multi-function serial interface ch 4 input                                                                                                                            | 172        | 140      |  |  |

|                              | SIN4_1             | pin                                                                                                                                                                   | 161        | 131      |  |  |

|                              | SOT4_0<br>(SDA4_0) | Multi-function serial interface ch 4 output pin                                                                                                                       | 171        | 139      |  |  |

| Multi-                       | SOT4_1<br>(SDA4_1) | This pin operates as SOT4 when it is<br>used in a UART/CSIO/LIN (operation<br>modes 0 to 3) and as SDA4 when it is<br>used in an I <sup>2</sup> C (operation mode 4). | 160        | 130      |  |  |

| Function<br>Serial           | SCK4_0<br>(SCL4_0) | Multi-function serial interface ch 4 clock<br>I/O pin                                                                                                                 | 170        | 138      |  |  |

| 4                            | SCK4_1<br>(SCL4_1) | This pin operates as SCK4 when it is<br>used in a CSIO (operation mode 2) and<br>as SCL4 when it is used in an I <sup>2</sup> C<br>(operation mode 4).                | 166        | 136      |  |  |

|                              | CTS4_0             | Multi-function serial interface ch 4 CTS                                                                                                                              | 168        | -        |  |  |

|                              | CTS4_1             | input pin                                                                                                                                                             | 165        | 135      |  |  |

|                              | RTS4_0             | Multi-function serial interface ch 4 RTS                                                                                                                              | 169        | 137      |  |  |

|                              | RTS4_1             | output pin                                                                                                                                                            | 162        | 132      |  |  |

| Madula                        | Din Nome             | Function                                                         | Pin Number |          |  |  |

|-------------------------------|----------------------|------------------------------------------------------------------|------------|----------|--|--|

| Module                        | Pin Name             | Function                                                         | LQFP 176   | LQFP 144 |  |  |

|                               | DTTI1X_0             | Input signal controlling waveform                                | 60         | 50       |  |  |

| -                             | DTTI1X_1             | generator outputs RTO10 to RTO15 of<br>Multi-Function Timer 1.   | 78         | -        |  |  |

|                               | FRCK1_0              | 16-bit free-run timer ch 1 external                              | 65         | 55       |  |  |

|                               | FRCK1_1              | clock input pin                                                  | 79         | -        |  |  |

|                               | IC10_0               |                                                                  | 61         | 51       |  |  |

|                               | IC10_1               |                                                                  | 80         | -        |  |  |

|                               | IC11_0               |                                                                  | 62         | 52       |  |  |

|                               | IC11_1               | 16-bit input capture input pin of<br>Multi-Function Timer 1.     | 81         | -        |  |  |

|                               | IC12_0               | ICxx describes channel number.                                   | 63         | 53       |  |  |

|                               | IC12_1               |                                                                  | 82         | -        |  |  |

|                               | IC13_0               |                                                                  | 64         | 54       |  |  |

|                               | IC13_1               |                                                                  | 83         | -        |  |  |

|                               | RTO10_0<br>(PPG10_0) | Waveform generator output pin of<br>Multi-Function Timer 1.      | 46         | 38       |  |  |

|                               | RTO10_1<br>(PPG10_1) | This pin operates as PPG10 when it is used in PPG1 output modes. | 139        | -        |  |  |

| Multi-<br>Function<br>Timer 1 | RTO11_0<br>(PPG10_0) | Waveform generator output pin of<br>Multi-Function Timer 1.      | 47         | 39       |  |  |

|                               | RTO11_1<br>(PPG10_1) | This pin operates as PPG10 when it is used in PPG1 output modes. | 140        | -        |  |  |

|                               | RTO12_0<br>(PPG12_0) | Waveform generator output pin of<br>Multi-Function Timer 1.      | 48         | 40       |  |  |

|                               | RTO12_1<br>(PPG12_1) | This pin operates as PPG12 when it is used in PPG1 output modes. | 141        | -        |  |  |

|                               | RTO13_0<br>(PPG12_0) | Waveform generator output pin of<br>Multi-Function Timer 1.      | 49         | 41       |  |  |

|                               | RTO13_1<br>(PPG12_1) | This pin operates as PPG12 when it is used in PPG1 output modes. | 142        | -        |  |  |

|                               | RTO14_0<br>(PPG14_0) | Waveform generator output pin of Multi-Function Timer 1.         | 50         | 42       |  |  |

|                               | RTO14_1<br>(PPG14_1) | This pin operates as PPG14 when it is used in PPG1 output modes. | 143        | -        |  |  |

|                               | RTO15_0<br>(PPG14_0) | Waveform generator output pin of<br>Multi-Function Timer 1.      | 51         | 43       |  |  |

|                               | RTO15_1<br>(PPG14_1) | This pin operates as PPG14 when it is used in PPG1 output modes. | 144        | -        |  |  |

#### Latch-Up

Semiconductor devices are constructed by the formation of p-type and n-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic pnpn junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred milliamps to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- 1. Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- 2. Be sure that abnormal current flows do not occur during the power-on sequence.

#### **Observance of Safety Regulations and Standards**

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### Fail-Safe Design

As previously mentioned, all semiconductor devices have inherent rates of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

#### **Precautions Related to Usage of Devices**

Cypress semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

#### 8.2 Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should only mount under Cypress' recommended conditions. For detailed information about mount conditions, contact your sales representative.

#### Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to Cypress recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

#### 8.3 Precautions for Use Environment

Reliability of semiconductor devices depends on ambient temperature and other conditions as described above.

For reliable performance, do the following:

1. Humidity

Prolonged use in high humidity can lead to leakage in devices as well as printed circuit boards. If high humidity levels are anticipated, consider anti-humidity processing.

2. Discharge of static electricity

When high-voltage charges exist close to semiconductor devices, discharges can cause abnormal operation. In such cases, use anti-static measures or processing to prevent discharges.

3. Corrosive gases, dust, or oil

Exposure to corrosive gases or contact with dust or oil may lead to chemical reactions that will adversely affect the device. If you use devices in such conditions, consider ways to prevent such exposure or to protect the devices.

4. Radiation, including cosmic radiation

Most devices are not designed for environments involving exposure to radiation or cosmic radiation. Users should provide shielding as appropriate.

5. Smoke, flame

CAUTION: Plastic molded devices are flammable and therefore should not be used near combustible substances. If devices begin to smoke or burn, there is danger of the release of toxic gases.

Customers considering the use of Cypress products in other special environmental conditions should consult with sales representatives.

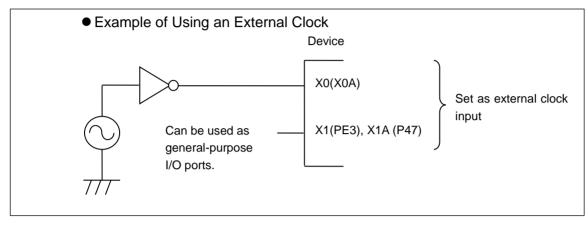

### **Using an External Clock**

When using an external clock as an input of the main clock, set X0/X1 to the external clock input, and input the clock to X0. X1(PE3) can be used as a general-purpose I/O port. Similarly, when using an external clock as an input of the sub clock, set X0A/X1A to the external clock input and input the clock to X0A. X1A (P47) can be used as a general-purpose I/O port.

#### Handling When Using Multi-Function Serial Pin as I<sup>2</sup>C Pin

If the application uses the multi-function serial pin as an I<sup>2</sup>C pin, the P-channel transistor of the digital output must be disabled. I<sup>2</sup>C pins need to conform to electrical limitations like other pins, however, and avoid connecting to live external systems with the MCU power off.

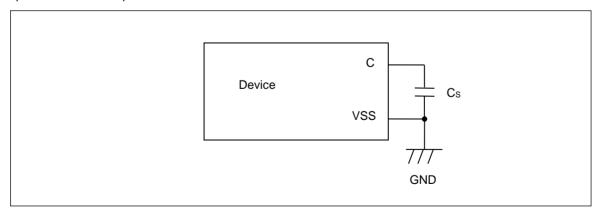

#### C Pin

Devices in this series contain a regulator. Be sure to connect a smoothing capacitor (Cs) for the regulator between the C pin and the GND pin. Please use a ceramic capacitor or a capacitor of equivalent frequency characteristics as a smoothing capacitor. Some laminated ceramic capacitors have a large capacitance variation due to thermal fluctuation. Please select a capacitor that meets the specifications in the operating conditions to use by evaluating the temperature characteristics of the device. A smoothing capacitor of about 4.7  $\mu$ F would be recommended for this series.

#### Mode Pins (MD0)

Connect the MD pin (MD0) directly to VCC or VSS pins. Design the printed circuit board such that the pull-up/down resistance stays low, the distance between the mode pins and VCC pins or VSS pins is as short as possible, and the connection impedance is low when the pins are pulled up/down such as for switching the pin level and rewriting the flash memory data. This is important to prevent the device from erroneously switching to test mode as a result of noise.

|           | Demonstration Ormatical           |            | Pin Conditions |     | <b>-</b> *4        | Va          | Value             |                                       | <b>D</b>            |                     |         |       |                |    |      |

|-----------|-----------------------------------|------------|----------------|-----|--------------------|-------------|-------------------|---------------------------------------|---------------------|---------------------|---------|-------|----------------|----|------|

| Parameter | Parameter Symbol                  | Name       | Conditions     |     | Frequency*4        | Typ*1       | Max* <sup>2</sup> | Unit                                  | Remarks             |                     |         |       |                |    |      |

|           |                                   |            |                | *5  | 180 MHz            | 82          | 140               | mA                                    |                     |                     |         |       |                |    |      |

|           |                                   |            |                |     | 160 MHz            | 74          | 132               | mA                                    |                     |                     |         |       |                |    |      |

|           |                                   |            |                |     | 144 MHz            | 68          | 126               | mA                                    |                     |                     |         |       |                |    |      |

|           |                                   |            |                |     | 120 MHz            | 58          | 116               | mA                                    |                     |                     |         |       |                |    |      |

|           |                                   |            |                |     | 100 MHz            | 49          | 107               | mA                                    | *3                  |                     |         |       |                |    |      |

|           |                                   |            |                | *6  | 80 MHz             | 40          | 98                | mA                                    | When all peripheral |                     |         |       |                |    |      |

|           |                                   |            |                | 0   | 60 MHz             | 31          | 89                | mA                                    | clocks are on       |                     |         |       |                |    |      |

|           |                                   |            |                |     | 40 MHz             | 22          | 80                | mA                                    |                     |                     |         |       |                |    |      |

|           | Power<br>supply Icc VC<br>current |            |                |     |                    |             | 20 MHz            | 13                                    | 71                  | mA                  |         |       |                |    |      |

|           |                                   |            | lcc            |     | Icc VCC            | Icc VCC ope |                   | Normal<br>operation<br>*7,*8<br>(PLL) | operation<br>*7,*8  |                     |         | 8 MHz | 7.5            | 65 | mA   |

|           |                                   |            |                |     |                    |             |                   |                                       |                     |                     |         | 4 MHz | 5.6            | 63 | 3 mA |

|           |                                   |            |                |     |                    |             | *7,*8<br>(PLL)    |                                       |                     | *5                  | 180 MHz | 48    | 106            | mA |      |

|           |                                   |            |                |     |                    | (PLL)       |                   |                                       |                     | 160 MHz             | 44      | 102   | mA             |    |      |

|           |                                   |            |                |     |                    |             |                   |                                       |                     |                     | 144 MHz | 41    | 99             | mA |      |

|           |                                   |            |                |     | 120 MHz<br>100 MHz | 120 MHz     |                   |                                       |                     |                     | 35      | 93    | mA             | ]  |      |

|           |                                   |            |                |     |                    |             |                   | 30                                    | 88                  | mA                  | *3      |       |                |    |      |

|           |                                   |            |                |     | *6                 | 80 MHz      | 25                | 83                                    | mA                  | When all peripheral |         |       |                |    |      |

|           |                                   |            |                |     |                    | *6          | *6                | 0                                     | 60 MHz              | 20                  | 78      | mA    | clocks are off |    |      |

|           |                                   |            |                |     |                    |             |                   | 40 MHz                                | 14                  | 72                  | mA      |       |                |    |      |

|           |                                   | 20 MHz 8.7 |                | 8.7 | 66                 | mA          |                   |                                       |                     |                     |         |       |                |    |      |

|           |                                   |            |                |     | 8 MHz              | 5.6         | 63                | mA                                    |                     |                     |         |       |                |    |      |

|           |                                   |            |                |     | 4 MHz              | 4.5         | 62                | mA                                    |                     |                     |         |       |                |    |      |

# Table 12-2 Typical and Maximum Current Consumption in Normal Operation (PLL), Code with Data Accessing Running from Flash Memory (Flash Accelerator Mode and Trace Buffer Function Disabled)

1: T<sub>A</sub> = +25 °C, V<sub>CC</sub> = 3.3 V

2:  $T_J$  = +125 °C,  $V_{CC}$  = 5.5 V

3: When all ports are input and are fixed at 0

4: Frequency is a value of HCLK when PCLK0 = PCLK1 = PCLK2 = HCLK

5: When stopping flash accelerator mode and trace buffer function (FRWTR.RWT = 11, FBFCR.BE = 0)

6: When stopping flash accelerator mode and trace buffer function (FRWTR.RWT = 10, FBFCR.BE = 0)

7: With data access to a MainFlash memory.

8: When using the crystal oscillator of 4 MHz (including the current consumption of the oscillation circuit)

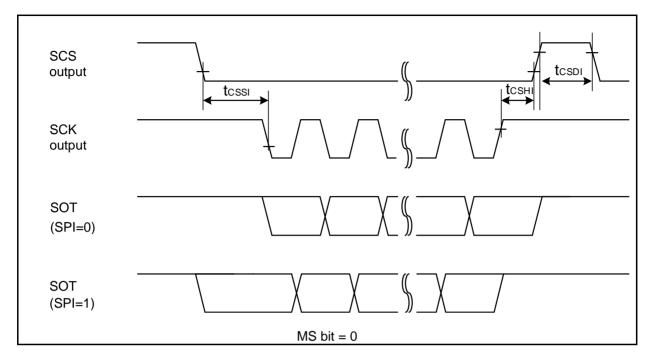

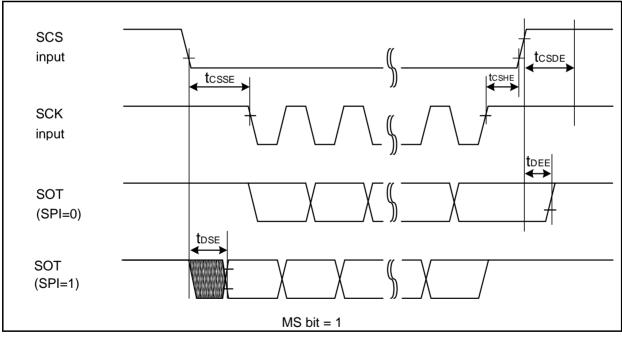

# When Using Synchronous Serial Chip Select (SCINV = 0, CSLVL = 0)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Parameter            | Cumhal            | Conditions                           | Vcc <                          | V <sub>cc</sub> < 4.5 V        |                                | V <sub>cc</sub> ≥ 4.5 V        |        |  |

|----------------------|-------------------|--------------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------|--|

| Faidilleter          | Symbol            | Conditions                           | Min                            | Мах                            | Min                            | Мах                            | - Unit |  |

| SCS↑→SCK↓ setup time | tcssi             |                                      | (*1)-50                        | (*1)+0                         | (*1)-50                        | (*1)+0                         | ns     |  |

| SCK↑→SCS↓ hold time  | tcsнi             | Internal shift<br>clock              | (*2)+0                         | (*2)+50                        | (*2)+0                         | (*2)+50                        | ns     |  |

| SCS deselect time    | tcsDI             | operation                            | (*3)-50<br>+5t <sub>CYCP</sub> | (*3)+50<br>+5t <sub>CYCP</sub> | (*3)-50<br>+5t <sub>СҮСР</sub> | (*3)+50<br>+5t <sub>CYCP</sub> | ns     |  |

| SCS↑→SCK↓ setup time | t <sub>CSSE</sub> |                                      | 3t <sub>CYCP</sub> +30         | -                              | 3t <sub>CYCP</sub> +30         | -                              | ns     |  |

| SCK↑→SCS↓ hold time  | tcshe             |                                      | 0                              | -                              | 0                              | -                              | ns     |  |

| SCS deselect time    | tcsde             | External shift<br>clock<br>operation | 3tcycp+30                      | -                              | 3tcycp+30                      | -                              | ns     |  |

| SCS∱→SOT delay time  | tDSE              |                                      | -                              | 40                             | -                              | 40                             | ns     |  |

| SCS↓→SOT delay time  | <b>t</b> DEE      |                                      | 0                              | -                              | 0                              | -                              | ns     |  |

(\*1): CSSU bit valuexserial chip select timing operating clock cycle [ns]

(\*2): CSHD bit valuexserial chip select timing operating clock cycle [ns]

(\*3): CSDS bit valuexserial chip select timing operating clock cycle [ns]

#### Notes:

- tcycp indicates the APB bus clock cycle time. For more information about the APB bus number to which the multi-function serial is connected, see 1. S6E2G Series Block Diagram in this data sheet.

- For more information about CSSU, CSHD, CSDS, and the serial chip select timing operating clock, see FM4 Family Peripheral Manual Main Part (002-04856).

- When the external load capacitance  $C_L = 30 \text{ pF}$ .

#### Notes:

- The Card Input corresponds to the Host Output and the Card Output corresponds to the Host Input because this model is the Host.

- For more information about clock frequency (f<sub>PP</sub>), see Chapter 15: SD card Interface in FM4 Family Peripheral Manual Main Part (002-04856).

#### 12.4.17 ETM/ HTM Timing

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Parameter               | Cumula al          | Din Nome      | Conditions              | Value |     | 11   | Doworko |

|-------------------------|--------------------|---------------|-------------------------|-------|-----|------|---------|

|                         | Symbol             | Pin Name      | Conditions              | Min   | Max | Unit | Remarks |

| Data hold               | •                  | TRACECLK,     | V <sub>CC</sub> ≥ 4.5 V | 2     | 9   | ns   |         |

|                         | tетмн              | TRACED[15: 0] | $V_{CC}$ <4.5 V         | 2     | 15  |      |         |

| TRACECLK                | 1/ttrace           | TRACECLK      | V <sub>CC</sub> ≥ 4.5 V |       | 50  | MHz  |         |

| frequency               |                    |               | Vcc <4.5 V              |       | 32  | MHz  |         |

| TRACECLK<br>clock cycle | t <sub>TRACE</sub> |               | V <sub>CC</sub> ≥ 4.5 V | 20    | -   | ns   |         |

|                         |                    |               | $V_{CC}$ <4.5 V         | 31.25 | -   | ns   |         |

Note:

- When the external load capacitance  $C_L = 30 \text{ pF}$ .

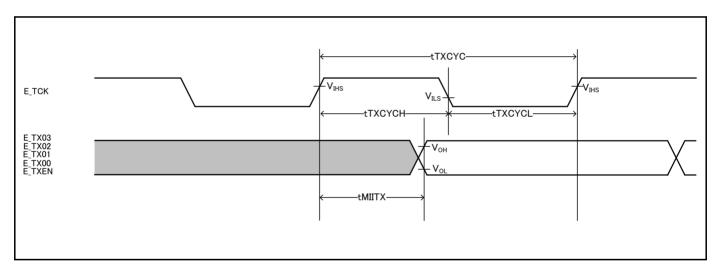

# MII Transmission (100 Mbps/10 Mbps)

(ETHV<sub>CC</sub> = 3.0V to 3.6V, 4.5V to  $5.5V^{*1}$ , V<sub>SS</sub> = 0V, C<sub>L</sub> = 25 pF)

| Parameter                                               | Symbol Pin Name |                                              | Conditions                   | Va  | Unit |      |

|---------------------------------------------------------|-----------------|----------------------------------------------|------------------------------|-----|------|------|

| Farameter                                               |                 |                                              | Conditions                   | Min | Max  | Unit |

| Transmission clock<br>Cycle time*2                      |                 |                                              | 100 Mbps<br>40 ns (typical)  | -   | -    | ns   |

|                                                         | tтхсүс          | E_TCK                                        | 100 Mbps<br>400 ns (typical) | -   | -    | ns   |

| Transmission clock<br>High-pulse-width duty cycle       | tтхсүсн         | E_TCK                                        | tтхсусн/tтхсус               | 35  | 65   | %    |

| Transmission clock<br>Low-pulse-width duty cycle        | t⊤xcyc∟         | E_TCK                                        | tтхсүс⊔/tтхсүс               | 35  | 65   | %    |

| TXCK $\uparrow \rightarrow$ Transmitted data delay time | tміітх          | E_TX03, E_TX02,<br>E_TX01, E_TX00,<br>E_TXEN | -                            | -   | 24   | ns   |

1: When ETHV = 4.5 V to 5.5 V, it is recommended to add a series resistor at the output pin to suppress the output current.

2: The transmission clock is fixed to 25 MHz or 2.5 MHz in the MII specifications. The clock accuracy should meet the PHY-device specifications.

■ Total error: A difference between actual value and theoretical value.

The overall error includes zero-transition voltage, full-scale transition voltage and linearity error.

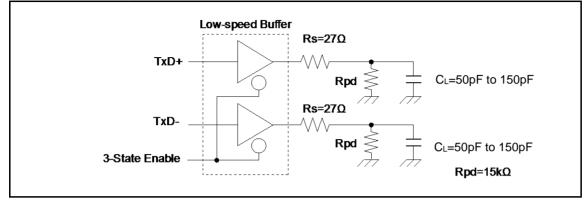

#### Low-Speed Load (Upstream Port Load) - Reference 1

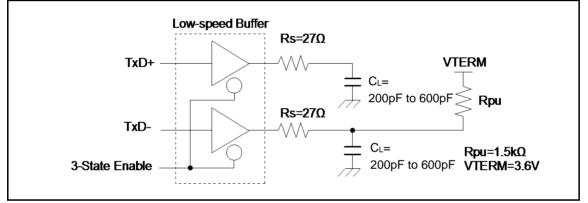

# Low-Speed Load (Downstream Port Load) - Reference 2

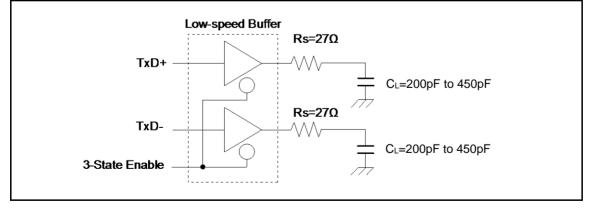

#### Low-Speed Load (Compliance Load)

# Internal Resource RST Internal RST RST Active tront CPU Operation Start

#### Example of Standby Recovery Operation (when in Internal Resource Reset Recovery\*)

\*: Depending on the low-power consumption mode, the reset issue from the internal resource is not included in the recovery cause.

#### Notes:

- The return factor is different in each low power consumption mode.

See Chapter 6: Low Power Consumption mode and Operations of Standby modes in "FM4 Family Peripheral Manual Main Part (002-04856).

- The recovery process is unique for each operating mode. See Chapter 6: Low Power Consumption mode in FM4 Family Peripheral Manual Main Part (002-04856).

- When the power-on reset/low-voltage detection reset, they are not included in the return factor. See 12.4.8 Power-On Reset Timing.

- In recovering from reset, CPU changes to High-speed Run mode. In the case of using the main clock and PLL clock, they need further main clock oscillation stabilization wait time and oscillation stabilization wait time of Main PLL clock.

- Internal resource reset indicates Watchdog reset and CSV reset.