Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 180MHz                                                                       |

| Connectivity               | CSIO, EBI/EMI, I <sup>2</sup> C, LINbus, SD, SmartCard, SPI, UART/USART, USB |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 153                                                                          |

| Program Memory Size        | 512KB (512K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                  |

| Data Converters            | A/D 32x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 176-LQFP                                                                     |

| Supplier Device Package    | 176-LQFP (24x24)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e2gk6jhagv2000a |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             |                                |            |                    |                    | Product Name         |                    |                    |  |  |  |  |  |

|-------------|--------------------------------|------------|--------------------|--------------------|----------------------|--------------------|--------------------|--|--|--|--|--|

|             | Descr                          | iption     | S6E2GM6<br>S6E2GM8 | S6E2GK6<br>S6E2GK8 | S6E2GH6<br>S6E2GH8   | S6E2G36<br>S6E2G38 | S6E2G26<br>S6E2G28 |  |  |  |  |  |

| (PW         | e timer<br>C/Reload<br>r/PWM/P |            |                    | 16 ch (Max)        |                      |                    |                    |  |  |  |  |  |

| á           | A/D<br>activation<br>compare   | n 6 ch     |                    |                    |                      |                    |                    |  |  |  |  |  |

| 0           | Input<br>capture               | 4 ch       |                    |                    |                      |                    |                    |  |  |  |  |  |

|             | Free-run<br>timer              | 3 ch       |                    |                    | 2 units (Max)        |                    |                    |  |  |  |  |  |

|             | Output<br>compare              | 6 ch       |                    |                    |                      |                    |                    |  |  |  |  |  |

|             | Waveforn<br>generator          | 12 ch      |                    |                    |                      |                    |                    |  |  |  |  |  |

| I           | PPG                            | 3 ch       |                    |                    |                      |                    |                    |  |  |  |  |  |

| Sma         | artcard (IS                    | SO7816)    | 2 ch (Max)         |                    |                      |                    |                    |  |  |  |  |  |

| QPF         | RC                             |            | 2 ch (Max)         |                    |                      |                    |                    |  |  |  |  |  |

| Dua         | l timer                        |            | 1 unit             |                    |                      |                    |                    |  |  |  |  |  |

| Rea         | I-time clo                     | ck         | 1 unit             |                    |                      |                    |                    |  |  |  |  |  |

| Wate        | ch counte                      | er         |                    |                    | 1 unit               |                    |                    |  |  |  |  |  |

| CRC         | C accelera                     | ator       |                    |                    | Yes (fixed)          |                    |                    |  |  |  |  |  |

| Wate        | chdog tirr                     | ner        |                    |                    | 1 ch (SW) + 1 ch (HV | V)                 |                    |  |  |  |  |  |

| Exte        | ernal inter                    | rupts      |                    |                    | 32 pins (Max)+ NMI × | : 1                |                    |  |  |  |  |  |

| CSV         | (clock s                       | upervisor) |                    |                    | Yes                  |                    |                    |  |  |  |  |  |

| LVD<br>dete | (low-volt<br>ctor)             | age        | 2 ch               |                    |                      |                    |                    |  |  |  |  |  |

| D           |                                | High-speed | 4 MHz              |                    |                      |                    |                    |  |  |  |  |  |

| Built       | -in CR                         | Low-speed  | 100 kHz            |                    |                      |                    |                    |  |  |  |  |  |

| Deb         | ug functio                     | on         | SWJ-DP/ETM/HTM     |                    |                      |                    |                    |  |  |  |  |  |

| Unic        | que ID                         |            |                    | Yes                |                      |                    |                    |  |  |  |  |  |

\*1: Crypto Assist Function is built in following products. S6E2GM6HHA, S6E2GM8HHA, S6E2GM6JHA, S6E2GM8JHA

### Notes:

Because of package pin limitations, not all functions within the device can be brought out to external pins. You must carefully

work out the pin allocation needed for your design.

You must use the port relocate function of the I/O port according to your function use.

- See 12.4.3 Built-In CR Oscillation Characteristics for the accuracy of the built-in CR.

| Pin N    | umber    | <b>-</b>         | 1/0             | Pin State |  |

|----------|----------|------------------|-----------------|-----------|--|

| LQFP-176 | LQFP-144 | Pin Name         | Circuit<br>Type | Туре      |  |

|          |          | PAD              |                 |           |  |

|          |          | SCK3_0           |                 |           |  |

| 18       | 15       | (SCL3_0)         | N               | I.        |  |

|          | -        | TIOB9_0          | _               |           |  |

|          |          | MADATA13_0       |                 |           |  |

|          | -        | PAE              | _               |           |  |

|          | -        | ADTG_0<br>SOT3_0 | _               |           |  |

| 19       | 16       | (SDA3_0)         | Ν               | I.        |  |

|          | ŀ        | TIOB10_0         | _               |           |  |

|          |          | MADATA14_0       |                 |           |  |

|          |          | PAF              |                 |           |  |

|          |          | SIN3_0           |                 |           |  |

| 20       | 17       | TIOB11_0         | I               | К         |  |

|          |          | INT16_0          |                 |           |  |

|          |          | MADATA15_0       |                 |           |  |

|          |          | P08              |                 |           |  |

| 21       | 18       | TIOB12_0         | E               | к         |  |

| 21       | 10       | INT17_0          | _               |           |  |

|          | -        | MDQM0_0          |                 |           |  |

|          |          | P09              |                 |           |  |

| 22       | 19       | TIOB13_0         | E               | к         |  |

|          |          | INT18_0          |                 |           |  |

|          |          | MDQM1_0          |                 |           |  |

|          |          | P0A              |                 |           |  |

| 23       | 20       | ADTG_1           | L               | I.        |  |

|          |          | MCLKOUT_0        |                 |           |  |

|          |          | P30              | _               |           |  |

|          |          | MI2SWS1_1        |                 |           |  |

| 24       | -        | RX0_1            | Е               | к         |  |

|          |          | TIOB11_2         |                 |           |  |

|          |          | INT01_2          |                 |           |  |

|          |          | P31              |                 |           |  |

| 25       |          | MI2SMCK1_1       | Е               | 1         |  |

| 20       | -        | TX0_1            | E               | '         |  |

|          |          | TIOA12_2         |                 |           |  |

|          |          | P32              |                 |           |  |

| 26       | 21       | INT19_0          | L               | K         |  |

|          |          | S_DATA1_0        |                 |           |  |

|          |          | P33              |                 |           |  |

| 27       | 22       | FRCK0_0          | L               | I         |  |

|          |          | S_DATA0_0        |                 |           |  |

| Mashala    | Dia Mara     | Pin N                     | n Number                                                                                                    |          |  |

|------------|--------------|---------------------------|-------------------------------------------------------------------------------------------------------------|----------|--|

| Module     | Pin Name     | Function                  | LQFP 176                                                                                                    | LQFP 144 |  |

|            | TIOA7_0      |                           | 149                                                                                                         | 119      |  |

|            | TIOA7_1      | Base Timer ch 7 TIOA pin  | 80                                                                                                          | -        |  |

| Base Timer | TIOA7_2      |                           | 171                                                                                                         | 139      |  |

| 7          | TIOB7_0      |                           | 148                                                                                                         | 118      |  |

|            | TIOB7_1      | Base Timer ch 7 TIOB pin  | 81                                                                                                          | -        |  |

|            | TIOB7_2      |                           | 170                                                                                                         | 138      |  |

|            | TIOA8_0      |                           | 2                                                                                                           | 2        |  |

|            | TIOA8_1      | Base Timer ch 8 TIOA pin  | 116                                                                                                         | 92       |  |

| Base Timer | TIOA8_2      | -                         | 10                                                                                                          | -        |  |

| 8          | TIOB8_0      |                           | 17                                                                                                          | 14       |  |

|            | TIOB8_1      | Base Timer ch 8 TIOB pin  | 117                                                                                                         | 93       |  |

|            | TIOB8_2      |                           | 11                                                                                                          | -        |  |

|            | TIOA9_0      |                           | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                      | 3        |  |

|            | TIOA9_1      | Base Timer ch 9 TIOA pin  | 102                                                                                                         | -        |  |

| Base Timer | TIOA9_2      |                           | 12                                                                                                          | -        |  |

| 9          | TIOB9_0      |                           | 18                                                                                                          | 15       |  |

|            | TIOB9_1      | Base Timer ch 9 TIOB pin  | 103                                                                                                         | -        |  |

|            | TIOA10_0     |                           | 4                                                                                                           | 4        |  |

| Base Timer | TIOA10_1     | Base Timer ch 10 TIOA pin | 104                                                                                                         | -        |  |

| 10         | TIOB10_0     |                           | 19                                                                                                          | 16       |  |

| -          | TIOB10_1     | Base Timer ch 10 TIOB pin | 104       19       105       5                                                                              | -        |  |

|            | TIOA11_0     |                           | 5                                                                                                           | 5        |  |

| -          | TIOA11_1     | Base Timer ch 11 TIOA pin | 19         16           105         -           5         5           110         -           20         17 | -        |  |

| Base Timer | TIOB11_0     |                           |                                                                                                             | 17       |  |

| 11         | TIOB11_1     | Base Timer ch 11 TIOB pin | 111                                                                                                         | -        |  |

| -          | TIOB11_2     |                           | 24                                                                                                          | -        |  |

|            | TIOA12_0     |                           | 6                                                                                                           | 6        |  |

|            | TIOA12_1     | Base Timer ch 12 TIOA pin | 112                                                                                                         | -        |  |

| Base Timer | TIOA12_2     |                           | 25                                                                                                          | -        |  |

| 12         | TIOB12_0     |                           | 21                                                                                                          | 18       |  |

| •          | TIOB12_1     | Base Timer ch 12 TIOB pin | 113                                                                                                         | -        |  |

| •          | TIOB12_2     |                           | 41                                                                                                          | -        |  |

|            | TIOA13_0     |                           | 7                                                                                                           | 7        |  |

|            |              | Base Timer ch 13 TIOA pin | 124                                                                                                         | 100      |  |

| Base Timer |              | 1                         | 42                                                                                                          | -        |  |

| 13         |              |                           | 22                                                                                                          | 19       |  |

| 13 T<br>T  |              | Base Timer ch 13 TIOB pin | 125                                                                                                         | 101      |  |

|            |              | 1                         | 43                                                                                                          | -        |  |

|            |              |                           | 151                                                                                                         | 121      |  |

| Base Timer |              | Base Timer ch 14 TIOA pin | 82                                                                                                          | -        |  |

| 14         | <br>TIOB14_0 |                           | 150                                                                                                         | 120      |  |

|            | TIOB14_1     | Base Timer ch 14 TIOB pin | 83                                                                                                          | -        |  |

|            |              | 1                         |                                                                                                             |          |  |

| Madula | Dia Mara | Franction                  | Pin N    | umber    |

|--------|----------|----------------------------|----------|----------|

| Module | Pin Name | Function                   | LQFP 176 | LQFP 144 |

|        | P70      |                            | 67       | 57       |

|        | P71      |                            | 68       | 58       |

|        | P72      |                            | 69       | 59       |

|        | P73      |                            | 70       | 60       |

|        | P74      |                            | 71       | 61       |

|        | P75      | General-purpose I/O port 7 | 72       | 62       |

|        | P76      |                            | 73       | 63       |

|        | P77      |                            | 74       | 64       |

|        | P78      |                            | 75       | 65       |

|        | P79      |                            | 76       | 66       |

|        | P7A      |                            | 77       | 67       |

|        | P80      |                            | 174      | 142      |

|        | P81      |                            | 175      | 143      |

| GPIO   | P82      | General-purpose I/O port 8 | 130      | 106      |

|        | P83      |                            | 131      | 107      |

|        | P90      |                            | 139      | -        |

|        | P91      |                            | 140      | -        |

|        | P92      |                            | 141      | -        |

| GPIO   | P93      | General-purpose I/O port 9 | 142      | -        |

|        | P94      |                            | 143      | -        |

|        | P95      |                            | 144      | -        |

|        | PA0      |                            | 2        | 2        |

|        | PA1      |                            | 3        | 3        |

| GPIO   | PA2      |                            | 4        | 4        |

|        | PA3      |                            | 5        | 5        |

|        | PA4      |                            | 6        | 6        |

|        | PA5      |                            | 7        | 7        |

|        | PA6      | 7                          | 8        | 8        |

|        | PA7      |                            | 9        | 9        |

|        | PA8      | General-purpose I/O port A | 13       | 10       |

|        | PA9      | 1                          | 14       | 11       |

|        | PAA      | 1                          | 15       | 12       |

|        | PAB      | -                          | 16       | 13       |

|        | PAC      |                            | 17       | 14       |

|        | PAD      | 1                          | 18       | 15       |

|        | PAE      | 1                          | 19       | 16       |

|        | PAF      |                            | 20       | 17       |

### Latch-Up

Semiconductor devices are constructed by the formation of p-type and n-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic pnpn junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred milliamps to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- 1. Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- 2. Be sure that abnormal current flows do not occur during the power-on sequence.

#### **Observance of Safety Regulations and Standards**

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### Fail-Safe Design

As previously mentioned, all semiconductor devices have inherent rates of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

#### **Precautions Related to Usage of Devices**

Cypress semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

### 8.2 Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should only mount under Cypress' recommended conditions. For detailed information about mount conditions, contact your sales representative.

#### Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to Cypress recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

# 9. Handling Devices

### **Power-Supply Pins**

In products with multiple VCC and VSS pins, respective pins at the same potential are interconnected within the device in order to prevent malfunctions such as latch-up. All of these pins should be connected externally to the power supply or ground lines, however, in order to reduce electromagnetic emission levels, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Be sure to connect the current-supply source with the power pins and GND pins of this device at low impedance. It is also advisable that a ceramic capacitor of approximately 0.1  $\mu$ F be connected as a bypass capacitor between VCC and VSS near this device.

A malfunction may occur when the power-supply voltage fluctuates rapidly even though the fluctuation is within the guaranteed operating range of the VCC power supply voltage. As a rule of voltage stabilization, suppress voltage fluctuation so that the fluctuation in VCC ripple (peak-to-peak value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the standard VCC value, and the transient fluctuation rate does not exceed 0.1V/µs at a momentary fluctuation such as switching the power supply.

### **Crystal Oscillator Circuit**

Noise near the X0/X1 and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1, X0A/X1A pins, the crystal oscillator (or ceramic oscillator), and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended that the PC board artwork be designed such that the X0/X1 and X0A/X1A pins are surrounded by ground plane, as this is expected to produce stable operation.

Evaluate the oscillation introduced by the use of the crystal oscillator by your mount board.

### Sub Crystal Oscillator

The sub-oscillator circuit for devices in this family is low gain to keep current consumption low. To stabilize the oscillation, Cypress recommends a crystal oscillator that meets the following conditions:

- Surface mount type

Size: More than 3.2 mm × 1.5 mm

Load capacitance: approximately 6 pF to 7 pF

- Lead type Load capacitance: approximately 6 pF to 7 pF

| Status Type | Function<br>Group                           | Power-On<br>Reset or<br>Low-<br>Voltage<br>Detection<br>State     | INITX<br>Input<br>State                                                    | Device<br>Internal<br>Reset<br>State                                       | Run mode<br>or Sleep<br>mode State                                   | RTC mode, or mode or Deep<br>Stop mode State Stop mode                  |                                                                      | eep Standby                                                             | Return from<br>Deep<br>Standby<br>mode State                         |                                                                         |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

|-------------|---------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-------------------------------|---------------------------|----------------------------------------------|--------------------------------------|------------------|

| Pin S       |                                             | Power<br>Supply<br>Unstable                                       | Power Supply<br>Stable                                                     |                                                                            | Power<br>Supply<br>Stable                                            | Supply Power Supply Stable                                              |                                                                      | Power Supply<br>Stable                                                  |                                                                      | Power<br>Supply<br>Stable                                               |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

|             |                                             | -                                                                 | INITX=0                                                                    | INITX=1                                                                    | INITX=1                                                              | INI                                                                     | INITX=1                                                              |                                                                         | ГХ=1                                                                 | INITX=1                                                                 |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

|             |                                             | -                                                                 | -                                                                          | -                                                                          | -                                                                    | SPL=0                                                                   | SPL=1                                                                | SPL=0                                                                   | SPL=1                                                                | -                                                                       |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

|             | Analog output<br>selected                   |                                                                   |                                                                            |                                                                            |                                                                      | *2                                                                      | *3                                                                   |                                                                         |                                                                      |                                                                         |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

| J           | External<br>interrupt<br>enable<br>selected | interrupt<br>enable                                               | Hi-Z/<br>input                                                             | Hi-Z/<br>input                                                             | Maintain<br>previous                                                 |                                                                         | Maintain<br>previous<br>state                                        | GPIO<br>selected,<br>internal input                                     | Hi-Z/internal input fixed                                            | GPIO<br>selected                                                        |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

|             | Resource<br>other than<br>above<br>selected | 111-2                                                             | enabled                                                                    | enabled                                                                    | state                                                                | Maintain<br>previous<br>state                                           | Hi-Z/internal<br>input fixed<br>at 0                                 | fixed<br>at 0                                                           | at 0                                                                 | Selected                                                                |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

|             | GPIO<br>selected                            |                                                                   |                                                                            |                                                                            |                                                                      |                                                                         | alu                                                                  |                                                                         |                                                                      |                                                                         |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

|             | External<br>interrupt<br>enable<br>selected | External<br>interrupt Setting Setting<br>enable disabled disabled |                                                                            |                                                                            | Maintain<br>previous<br>state                                        | GPIO                                                                    |                                                                      |                                                                         |                                                                      |                                                                         |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

| к           | Resource<br>other than<br>above<br>selected | Hi-Z                                                              | Hi-Z/<br>input                                                             | Hi-Z/<br>input                                                             | previous<br>state                                                    | previous                                                                | previous                                                             | previous                                                                | previous                                                             | •                                                                       | previous | Maintain<br>previous<br>state | Hi-Z/internal input fixed | selected,<br>internal input<br>fixed<br>at 0 | Hi-Z/internal<br>input fixed<br>at 0 | GPIO<br>selected |

|             | GPIO<br>selected                            |                                                                   | enabled                                                                    | enabled                                                                    |                                                                      |                                                                         | at 0                                                                 |                                                                         |                                                                      |                                                                         |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

| L           | Analog input<br>selected                    | Hi-Z                                                              | Hi-Z/<br>internal<br>input<br>fixed at<br>0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal<br>input<br>fixed at<br>0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input<br>enabled |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

|             | Resource<br>other than<br>above<br>selected | Setting<br>disabled                                               | Setting<br>disabled                                                        | Setting<br>disabled                                                        | Maintain<br>previous<br>state                                        | Maintain<br>previous<br>state                                           | Hi-Z/internal<br>input fixed                                         | GPIO<br>selected,<br>internal input                                     | Hi-Z/internal<br>input fixed<br>at 0                                 | GPIO<br>selected                                                        |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

|             | GPIO<br>selected                            |                                                                   |                                                                            |                                                                            | Sidio                                                                | Sidio                                                                   |                                                                      | at 0 fixed<br>at 0                                                      |                                                                      |                                                                         |          |          |          |          |          |          |          |          |          |                               |                           |                                              |                                      |                  |

| Pin Status Type | Function<br>Group                           | Power-On<br>Reset or<br>Low-<br>Voltage<br>Detection<br>State | INITX<br>Input<br>State                                                    | Device<br>Internal<br>Reset<br>State                                       | Run mode<br>or Sleep<br>mode State                                   | Timer mode, Deep Standby RTC<br>RTC mode, or mode or Deep Standk<br>Stop mode State Stop mode State |                                                                      | eep Standby                                                             | Return from<br>Deep<br>Standby<br>mode State                         |                                                                         |

|-----------------|---------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------|

| Pin S           |                                             | Power<br>Supply<br>Unstable                                   | Power Supply<br>Stable                                                     |                                                                            | Power<br>Supply<br>Stable                                            |                                                                                                     | Supply<br>able                                                       | Power Supply<br>Stable                                                  |                                                                      | Power<br>Supply<br>Stable                                               |

|                 |                                             | -                                                             | INITX=0                                                                    | INITX=1                                                                    | INITX=1                                                              | INI                                                                                                 | ГХ=1                                                                 | INI                                                                     | ГХ=1                                                                 | INITX=1                                                                 |

|                 |                                             | -                                                             | -                                                                          | -                                                                          | -                                                                    | SPL=0                                                                                               | SPL=1                                                                | SPL=0                                                                   | SPL=1                                                                | -                                                                       |

|                 | Analog input<br>selected                    | Hi-Z                                                          | Hi-Z/<br>internal<br>input<br>fixed<br>at 0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal<br>input<br>fixed<br>at 0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input<br>enabled                             | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input<br>enabled |

|                 | Trace<br>selected                           | Setting                                                       |                                                                            |                                                                            |                                                                      |                                                                                                     | Trace<br>output                                                      |                                                                         |                                                                      |                                                                         |

| 0               | External<br>interrupt<br>enable<br>selected |                                                               | Setting S                                                                  | Setting S                                                                  | Setting                                                              | Maintain<br>previous                                                                                | Maintain<br>previous                                                 | Maintain<br>previous state                                              | GPIO<br>selected,<br>internal input                                  | Hi-Z/internal input fixed                                               |

|                 | Resource<br>other than<br>above<br>selected | disabled disabled                                             | state                                                                      | state                                                                      | Hi-Z/internal<br>input fixed<br>at 0                                 | fixed<br>at 0                                                                                       | at 0                                                                 | selected                                                                |                                                                      |                                                                         |

|                 | GPIO<br>selected                            |                                                               |                                                                            |                                                                            |                                                                      |                                                                                                     |                                                                      |                                                                         |                                                                      |                                                                         |

|                 | Analog input<br>selected                    | Hi-Z                                                          | Hi-Z/<br>internal<br>input<br>fixed at<br>0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal<br>input<br>fixed at<br>0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input<br>enabled                             | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input<br>enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input enabled | Hi-Z/<br>internal input<br>fixed<br>at 0/<br>analog<br>input<br>enabled |

| Ρ               | WKUP<br>enabled                             |                                                               |                                                                            |                                                                            |                                                                      |                                                                                                     | Maintain<br>previous state                                           | WKUP<br>input<br>enabled                                                | Hi-Z/<br>WKUP input<br>enabled                                       |                                                                         |

|                 | Resource<br>other than<br>above<br>selected | Setting<br>disabled                                           | Setting<br>disabled                                                        | Setting<br>disabled                                                        | Maintain<br>previous<br>state                                        | Maintain<br>previous<br>state                                                                       | Hi-Z/internal<br>input fixed                                         | GPIO<br>selected,<br>internal input                                     | Hi-Z/internal<br>input fixed                                         | GPIO<br>selected                                                        |

|                 | GPIO<br>selected                            |                                                               |                                                                            |                                                                            |                                                                      |                                                                                                     | at 0                                                                 | fixed<br>at 0                                                           | at 0                                                                 |                                                                         |

Package thermal resistance and maximum permissible power for each package are shown below. The operation is guaranteed maximum permissible power or less for semiconductor devices.

| Package        | Printed                         | Thermal<br>Resistance | Maximum Permissible Power<br>(mW) |                          |  |  |

|----------------|---------------------------------|-----------------------|-----------------------------------|--------------------------|--|--|

| T ackage       | Circuit Board                   | θja<br>(°C/W)         | T <sub>A</sub> = +85 °C           | T <sub>A</sub> = +105 °C |  |  |

| LQS144         | Single-layered<br>both sides 48 |                       | 833                               | 417                      |  |  |

| (0.5-mm pitch) | 4 layers                        | 33                    | 1212                              | 606                      |  |  |

| LQP176         | Single-layered both sides       | 45                    | 889                               | 444                      |  |  |

| (0.5-mm pitch) | 4 layers                        | 31                    | 1290                              | 645                      |  |  |

#### Table for Package Thermal Resistance and Maximum Permissible Power

#### WARNING:

- The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All

of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may

adversely affect reliability and could result in device failure.

- No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

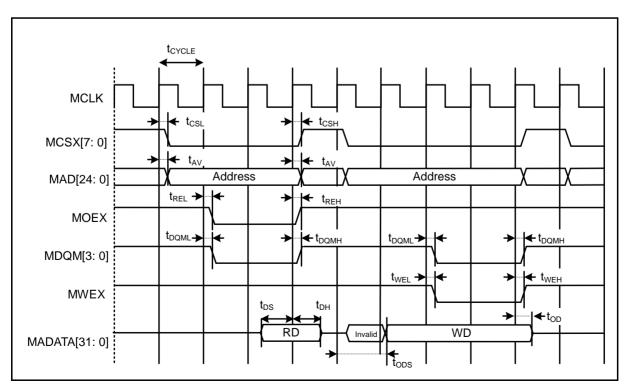

## Separate Bus Access Synchronous SRAM Mode

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Devenueter                   | Cumula al         | Din Nama               | Conditions | Va     | lue     | 11   | Remarks |

|------------------------------|-------------------|------------------------|------------|--------|---------|------|---------|

| Parameter                    | Symbol            | Pin Name               | Conditions | Min    | Max     | Unit | Remarks |

| Address delay time           | t <sub>AV</sub>   | MCLK,<br>MAD[24: 0]    | -          | 1      | 9       | ns   |         |

|                              | tcs∟              | MCLK,                  | -          | 1      | 9       | ns   |         |

| MCSX delay time              | t <sub>сsн</sub>  | MCSX[7: 0]             | -          | 1      | 9       | ns   |         |

|                              | t <sub>REL</sub>  | MCLK,                  | -          | 1      | 9       | ns   |         |

| MOEX delay time              | t <sub>REH</sub>  | MOEX                   | -          | 1      | 9       | ns   |         |

| Data set up<br>→MCLK ↑ time  | t <sub>DS</sub>   | MCLK,<br>MADATA[31: 0] | -          | 19     | -       | ns   |         |

| MCLK ↑ →<br>Data hold time   | t <sub>DH</sub>   | MCLK,<br>MADATA[31: 0] | -          | 0      | -       | ns   |         |

|                              | twel              | MCLK,                  | -          | 1      | 9       | ns   |         |

| MWEX delay time              | t <sub>WEH</sub>  | MWEX                   | -          | 1      | 9       | ns   |         |

| MDQM[1: 0]                   | <b>t</b> DQML     | MCLK,                  | -          | 1      | 9       | ns   |         |

| delay time                   | t <sub>DQMH</sub> | MDQM[3: 0]             | -          | 1      | 9       | ns   |         |

| MCLK ↑ →<br>Data output time | t <sub>ODS</sub>  | MCLK,<br>MADATA[31: 0] | -          | MCLK+1 | MCLK+18 | ns   |         |

| MCLK                         | top               | MCLK,<br>MADATA[31: 0] | -          | 1      | 18      | ns   |         |

Note:

- When the external load capacitance  $C_L = 30 \, pF$

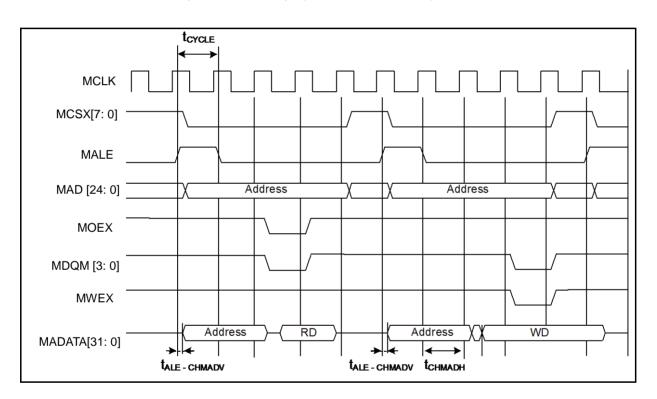

## Multiplexed Bus Access Asynchronous SRAM Mode

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Parameter                         | Cumple of           | Pin Name   | Conditions | Va       | alue      | Unit | Remarks |

|-----------------------------------|---------------------|------------|------------|----------|-----------|------|---------|

| Parameter                         | Symbol              | Pin Name   | Conditions | Min      | Max       | Unit |         |

| Multiplexed<br>address delay time | tale-chmadv         | MALE,      | -          | 0        | 10        | ns   |         |

| Multiplexed address hold time     | t <sub>CHMADH</sub> | MAD[24: 0] | -          | MCLK×n+0 | MCLK×n+10 | ns   |         |

Note:

- When the external load capacitance  $C_L = 30 \text{ pF}$  (m = 0 to 15, n = 1 to 16)

## Synchronous Serial (SPI = 1, SCINV = 1)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| <b>D</b>                   |                    | Pin           |                                   | Vcc <                   | 4.5 V | Vcc≥                    | 4.5 V | l l mit |

|----------------------------|--------------------|---------------|-----------------------------------|-------------------------|-------|-------------------------|-------|---------|

| Parameter                  | Symbol             | Name          | Conditions                        | Min                     | Max   | Min                     | Мах   | Unit    |

| Baud rate                  | -                  | -             | -                                 | -                       | 8     | -                       | 8     | Mbps    |

| Serial clock cycle time    | tscyc              | SCKx          |                                   | 4tcycp                  | -     | 4t <sub>CYCP</sub>      | -     | ns      |

| SCK↓→SOT delay time        | tslovi             | SCKx,<br>SOTx | Internal shift<br>clock operation | - 30                    | + 30  | - 20                    | + 20  | ns      |

| SIN→SCK↑ setup time        | t <sub>IVSHI</sub> | SCKx,<br>SINx |                                   | 50                      | -     | 30                      | -     | ns      |

| SCK∱→SIN hold time         | tshixi             | SCKx,<br>SINx |                                   | 0                       | -     | 0                       | -     | ns      |

| SOT→SCK↑ delay time        | t <sub>sovнi</sub> | SCKx,<br>SOTx |                                   | 2t <sub>CYCP</sub> - 30 | -     | 2t <sub>CYCP</sub> - 30 | -     | ns      |

| Serial clock L pulse width | t <sub>SLSH</sub>  | SCKx          |                                   | 2t <sub>CYCP</sub> - 10 | -     | 2t <sub>CYCP</sub> - 10 | -     | ns      |

| Serial clock H pulse width | ts∺s∟              | SCKx          |                                   | tcycp + 10              | -     | tcycp + 10              | -     | ns      |

| SCK↓→SOT delay time        | tslove             | SCKx,<br>SOTx |                                   | -                       | 50    | -                       | 30    | ns      |

| SIN→SCK↑ setup time        | t <sub>IVSHE</sub> | SCKx,<br>SINx | External shift clock operation    | 10                      | -     | 10                      | -     | ns      |

| SCK∱→SIN hold time         | tshixe             | SCKx,<br>SINx |                                   | 20                      | -     | 20                      | -     | ns      |

| SCK fall time              | t⊧                 | SCKx          | ]                                 | -                       | 5     | -                       | 5     | ns      |

| SCK rise time              | t <sub>R</sub>     | SCKx          |                                   | -                       | 5     | -                       | 5     | ns      |

#### Notes:

- The above characteristics apply to CLK synchronous mode.

- t<sub>CYCP</sub> indicates the APB bus clock cycle time. For more information about the APB bus number to which the multi-function serial is connected, see 1. S6E2G Series Block Diagram in this data sheet.

- These characteristics only guarantee the same relocate port number; for example, the combination of SCLKx\_0 and SOTx\_1 is not guaranteed.

- When the external load capacitance  $C_L = 30 \text{ pF}$ .

## When Using Synchronous Serial Chip Select (SCINV = 0, CSLVL = 1)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Parameter             | Symbol            | Conditions -            | Vcc <                          | 4.5 V                          | V <sub>cc</sub> ≥              | 4.5 V                          | Unit |

|-----------------------|-------------------|-------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|------|

| Parameter             | Symbol            | Conditions              | Min                            | Max                            | Min                            | Мах                            | Unit |

| SCS↓→SCK↓ setup time  | t <sub>CSSI</sub> |                         | (*1)-50                        | (*1)+0                         | (*1)-50                        | (*1)+0                         | ns   |

| SCK↑→SCS↑ hold time   | t <sub>CSHI</sub> | Internal shift<br>clock | (*2)+0                         | (*2)+50                        | (*2)+0                         | (*2)+50                        | ns   |

| SCS deselect time     | t <sub>CSDI</sub> | operation               | (*3)-50<br>+5t <sub>CYCP</sub> | (*3)+50<br>+5t <sub>CYCP</sub> | (*3)-50<br>+5t <sub>CYCP</sub> | (*3)+50<br>+5t <sub>CYCP</sub> | ns   |

| SCS↓→SCK↓ setup time  | tcsse             |                         | 3tcycp+30                      | -                              | 3tcycp+30                      | -                              | ns   |

| SCK↑→SCS↑ hold time   | tcshe             |                         | 0                              | -                              | 0                              | -                              | ns   |

| SCS deselect time     | t <sub>CSDE</sub> | External shift<br>clock | 3t <sub>CYCP</sub> +30         | -                              | 3t <sub>CYCP</sub> +30         | -                              | ns   |

| SCS ↓ →SOT delay time | tDSE              | operation               | -                              | 40                             | -                              | 40                             | ns   |

| SCS ↑ →SOT delay time | tDEE              |                         | 0                              | -                              | 0                              | -                              | ns   |

(\*1): CSSU bit valuexserial chip select timing operating clock cycle [ns]

(\*2): CSHD bit valuexserial chip select timing operating clock cycle [ns]

(\*3): CSDS bit valuexserial chip select timing operating clock cycle [ns]

#### Notes:

- tcycp indicates the APB bus clock cycle time. For more information about the APB bus number to which the multi-function serial is connected, see 1. S6E2G Series Block Diagram in this data sheet.

- For more information about CSSU, CSHD, CSDS, and the serial chip select timing operating clock, see FM4 Family Peripheral Manual Main Part (002-04856).

- When the external load capacitance  $C_L = 30 \text{ pF}$ .

## High-Speed Synchronous Serial (SPI = 0, SCINV = 0)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Parameter                  |                    | Pin           | Conditions                        | Vcc < 4.5 V            |      | V <sub>CC</sub> ≥ 4.5 V |      |      |

|----------------------------|--------------------|---------------|-----------------------------------|------------------------|------|-------------------------|------|------|

|                            | Symbol             | Name          |                                   | Min                    | Max  | Min                     | Max  | Unit |

| Serial clock cycle time    | tscyc              | SCKx          |                                   | 4tcycp                 | -    | 4tcycp                  | -    | ns   |

| SCK↓→SOT delay time        | t <sub>SLOVI</sub> | SCKx,<br>SOTx | Internal shift<br>clock operation | - 10                   | + 10 | - 10                    | + 10 | ns   |

| SIN→SCK↑ setup time        | tivshi             | SCKx,         |                                   | 14                     |      | 12.5                    | -    | ns   |

|                            | tivoni             | SINx          |                                   | 12.5*                  |      |                         |      |      |

| SCK∱→SIN hold time         | tsнixi             | SCKx,<br>SINx |                                   | 5                      | -    | 5                       | -    | ns   |

| Serial clock L pulse width | t <sub>SLSH</sub>  | SCKx          | External shift clock operation    | 2t <sub>CYCP</sub> - 5 | -    | 2t <sub>CYCP</sub> - 5  | -    | ns   |

| Serial clock H pulse width | t <sub>SHSL</sub>  | SCKx          |                                   | t <sub>CYCP</sub> + 10 | -    | t <sub>CYCP</sub> + 10  | -    | ns   |

| SCK↓→SOT delay time        | <b>t</b> SLOVE     | SCKx,<br>SOTx |                                   | -                      | 15   | -                       | 15   | ns   |

| SIN→SCK↑ setup time        | tivsн⊧             | SCKx,<br>SINx |                                   | 5                      | -    | 5                       | -    | ns   |

| SCK↑→SIN hold time         | tshixe             | SCKx,<br>SINx |                                   | 5                      | -    | 5                       | -    | ns   |

| SCK fall time              | tF                 | SCKx          |                                   | -                      | 5    | -                       | 5    | ns   |

| SCK rise time              | t <sub>R</sub>     | SCKx          |                                   | -                      | 5    | -                       | 5    | ns   |

#### Notes:

- The above characteristics apply to CLK synchronous mode.

- t<sub>CYCP</sub> indicates the APB bus clock cycle time. For more information about the APB bus number to which the multi-function serial is connected, see 1. S6E2G Series Block Diagram in this data sheet.

- These characteristics only guarantee the following pins:

No chip select: SIN4\_0, SOT4\_0, SCK4\_0 Chip select: SIN6\_0, SOT6\_0, SCK6\_0, SCS60\_0, SCS61\_0, SCS62\_0, SCS63\_0

- When the external load capacitance  $C_L = 30 \text{ pF}$ . (For \*, when  $C_L = 10 \text{ pF}$ )

## High-Speed Synchronous Serial (SPI = 0, SCINV = 1)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Parameter                  |                    | Pin           |                                   | <b>V</b> cc <          | 4.5 V | Vcc≥                   | 4.5 V |      |

|----------------------------|--------------------|---------------|-----------------------------------|------------------------|-------|------------------------|-------|------|

|                            | Symbol             | Name          | Conditions                        | Min                    | Max   | Min                    | Max   | Unit |

| Serial clock cycle time    | tscyc              | SCKx          |                                   | 4t <sub>CYCP</sub>     | -     | 4tcycp                 | -     | ns   |

| SCK∱→SOT delay time        | t <sub>SHOVI</sub> | SCKx,<br>SOTx | Internal shift<br>clock operation | - 10                   | + 10  | - 10                   | + 10  | ns   |

| SIN→SCK↓ setup time        | ti∨s⊔i             | SCKx,         |                                   | 14                     |       | 12.5                   | -     | ns   |

|                            | UVSLI              | SINx          |                                   | 12.5*                  | -     | 12.0                   | -     | 115  |

| SCK↓→SIN hold time         | ts∟ıxı             | SCKx,<br>SINx | -                                 | 5                      | -     | 5                      | -     | ns   |

| Serial clock L pulse width | tslsh              | SCKx          | External shift clock operation    | 2tcycp - 5             | -     | 2tcycp - 5             | -     | ns   |

| Serial clock H pulse width | t <sub>SHSL</sub>  | SCKx          |                                   | t <sub>CYCP</sub> + 10 | -     | t <sub>CYCP</sub> + 10 | -     | ns   |

| SCK∱→SOT delay time        | <b>t</b> SHOVE     | SCKx,<br>SOTx |                                   | -                      | 15    | -                      | 15    | ns   |

| SIN→SCK↓ setup time        | t <sub>IVSLE</sub> | SCKx,<br>SINx |                                   | 5                      | -     | 5                      | -     | ns   |

| SCK↓→SIN hold time         | tslixe             | SCKx,<br>SINx |                                   | 5                      | -     | 5                      | -     | ns   |

| SCK fall time              | t⊧                 | SCKx          |                                   | -                      | 5     | -                      | 5     | ns   |

| SCK rise time              | t <sub>R</sub>     | SCKx          |                                   | -                      | 5     | -                      | 5     | ns   |

### Notes:

- The above characteristics apply to CLK synchronous mode.

- t<sub>CYCP</sub> indicates the APB bus clock cycle time. For more information about the APB bus number to which the multi-function serial is connected, see 1. S6E2G Series Block Diagram in this data sheet.

- These characteristics only guarantee the following pins:

No chip select: SIN4\_0, SOT4\_0, SCK4\_0 Chip select: SIN6\_0, SOT6\_0, SCK6\_0, SCS60\_0, SCS61\_0, SCS62\_0, SCS63\_0

- When the external load capacitance  $C_L = 30 \text{ pF}$ . (For \*, when  $C_L = 10 \text{ pF}$ )

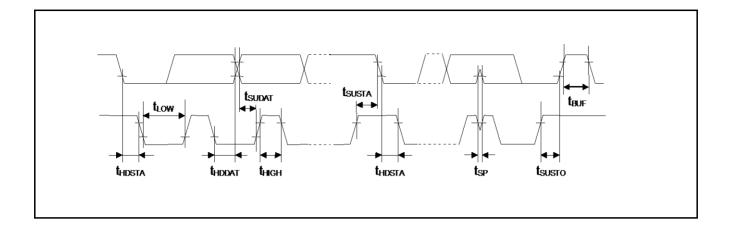

## Fast mode Plus (Fm+)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Parameter                                                                          |                    |                                        | Fast mode F            | Plus (Fm+)*6           |      |         |

|------------------------------------------------------------------------------------|--------------------|----------------------------------------|------------------------|------------------------|------|---------|

|                                                                                    | Symbol             | Conditions                             | Min                    | Max                    | Unit | Remarks |

| SCL clock frequency                                                                | f <sub>SCL</sub>   | -                                      | 0                      | 1000                   | kHz  |         |

| (Repeated) START condition hold time SDA $\downarrow \rightarrow$ SCL $\downarrow$ | <b>t</b> hdsta     |                                        | 0.26                   | -                      | μs   |         |

| SCL clock L width                                                                  | tLOW               |                                        | 0.5                    | -                      | μs   |         |

| SCL clock H width                                                                  | tнідн              |                                        | 0.26                   | -                      | μs   |         |

| (Repeated) START condition setup time SCL $\uparrow \rightarrow$ SDA $\downarrow$  | t <sub>susta</sub> | CL = 30 pF,<br>R = (Vp/IoL)*1          | 0.26                   | -                      | μs   |         |

| Data hold time SCL $\downarrow \rightarrow$ SDA $\downarrow \uparrow$              | thddat             |                                        | 0                      | 0.45 <sup>*2, *3</sup> | μs   |         |

| Data setup time SDA $\downarrow \uparrow \rightarrow$ SCL $\uparrow$               | <b>t</b> sudat     |                                        | 50                     | -                      | ns   |         |

| Stop condition setup time SCL $\uparrow \rightarrow$ SDA $\uparrow$                | tsusтo             |                                        | 0.26                   | -                      | μs   |         |

| Bus free time between<br>Stop condition and<br>START condition                     | tвuғ               |                                        | 0.5                    | -                      | μs   |         |

|                                                                                    |                    | 60 MHz ≤<br>tcycp<80 MHz               | 6 t <sub>CYCP</sub> *4 | -                      | ns   | *5      |

| Noise filter                                                                       | ts₽                | 80 MHz ≤<br>t <sub>CYCP</sub> ≤100 MHz | 8 tcycp <sup>*4</sup>  | -                      | ns   | *5      |

1: R and C<sub>L</sub> represent the pull-up resistance and load capacitance of the SCL and SDA lines, respectively. V<sub>P</sub> indicates the power supply voltage of the pull-up resistance and I<sub>OL</sub> indicates V<sub>OL</sub> guaranteed current.

2: The maximum t<sub>HDDAT</sub> must not extend beyond the low period (t<sub>LOW</sub>) of the device's SCL signal.

3: The Fast mode I<sup>2</sup>C bus device can be used on a Standard-mode I<sup>2</sup>C bus system as long as the device satisfies the requirement of "t<sub>SUDAT</sub> ≥ 250 ns."

4: t<sub>CYCP</sub> is the APB bus clock cycle time. For more information about the APB bus number to which the I<sup>2</sup>C is connected, see 1.S6E2G Series Block Diagram in this data sheet.

To use fast mode plus (Fm+), set the peripheral bus clock at 64 MHz or more.

5: The noise filter time can be changed by register settings. Change the number of the noise filter steps according to the APB bus clock frequency.

6: When using fast mode plus (Fm+), set the I/O pin to the mode corresponding to I<sup>2</sup>C Fm+ in the EPFR register. See Chapter 12: I/O Port in FM4 Family Peripheral Manual Main Part (002-04856) for the details.

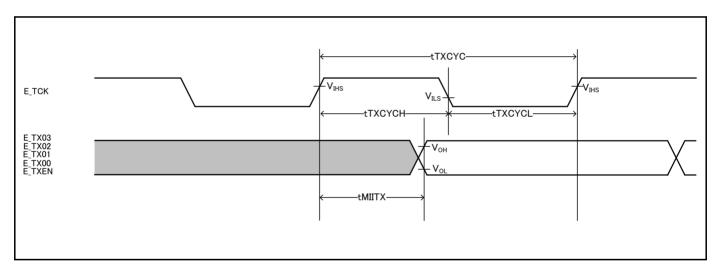

## MII Transmission (100 Mbps/10 Mbps)

(ETHV<sub>CC</sub> = 3.0V to 3.6V, 4.5V to  $5.5V^{*1}$ , V<sub>SS</sub> = 0V, C<sub>L</sub> = 25 pF)

| Parameter                                               | Symphol | Pin Name                                     | Conditions                   | Value |     | Unit |  |

|---------------------------------------------------------|---------|----------------------------------------------|------------------------------|-------|-----|------|--|

| Farameter                                               | Symbol  | Pin Name                                     | Conditions                   |       | Max | Unit |  |

| Transmission clock<br>Cycle time*2                      | tтхсус  |                                              | 100 Mbps<br>40 ns (typical)  | -     | -   | ns   |  |

|                                                         |         | E_TCK                                        | 100 Mbps<br>400 ns (typical) | -     | -   | ns   |  |

| Transmission clock<br>High-pulse-width duty cycle       | tтхсүсн | E_TCK                                        | tтхсүсн/tтхсүс               | 35    | 65  | %    |  |

| Transmission clock<br>Low-pulse-width duty cycle        | t⊤xcyc∟ | E_TCK                                        | tтхсүс⊔/tтхсүс               | 35    | 65  | %    |  |

| TXCK $\uparrow \rightarrow$ Transmitted data delay time | tміітх  | E_TX03, E_TX02,<br>E_TX01, E_TX00,<br>E_TXEN | -                            | -     | 24  | ns   |  |

1: When ETHV = 4.5 V to 5.5 V, it is recommended to add a series resistor at the output pin to suppress the output current.