Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                         |

|----------------------------|------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                             |

| Speed                      | 180MHz                                                                                         |

| Connectivity               | CANbus, CSIO, EBI/EMI, Ethernet, I <sup>2</sup> C, LINbus, SD, SmartCard, SPI, UART/USART, USB |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 153                                                                                            |

| Program Memory Size        | 1MB (1M x 8)                                                                                   |

| Program Memory Type        | FLASH                                                                                          |

| EEPROM Size                | -                                                                                              |

| RAM Size                   | 192K x 8                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                                    |

| Data Converters            | A/D 32x12b                                                                                     |

| Oscillator Type            | Internal                                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                  |

| Package / Case             | 176-LQFP                                                                                       |

| Supplier Device Package    | 176-LQFP (24x24)                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e2gm8j0agv2000a                   |

|                            |                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin N    | umber    | <b>D</b> . <b>N</b>  | !/O             | Pin State |  |

|----------|----------|----------------------|-----------------|-----------|--|

| LQFP-176 | LQFP-144 | Pin Name             | Circuit<br>Type | Туре      |  |

|          |          | P21                  |                 |           |  |

|          |          | ADTG_4               |                 |           |  |

| 127      | 103      | SIN0_0               | I               | K         |  |

|          |          | INT27_0              |                 |           |  |

|          |          | CROUT_0              |                 |           |  |

|          |          | P20                  |                 |           |  |

| 128      | 104      | NMIX                 | I               | F         |  |

|          |          | WKUP0                |                 |           |  |

| 129      | 105      | USBVCC1              | -               | -         |  |

| 130      | 106      | P82                  | н               | R         |  |

| 130      | 100      | UDM1                 | 11              | N         |  |

| 131      | 107      | P83                  | н               | R         |  |

| 151      | 107      | UDP1                 |                 | IX        |  |

| 132      | 108      | VSS                  | -               | -         |  |

| 133      | 109      | VCC                  | -               | -         |  |

| 134      | 110      | P00                  | E               | G         |  |

| 134      | 110      | TRSTX                | L               | 9         |  |

|          |          | P01                  |                 |           |  |

| 135      | 111      | TCK                  | E               | G         |  |

|          |          | SWCLK                |                 |           |  |

| 136      | 112      | P02                  | E               | G         |  |

| 130      | 112      | TDI                  | L               | 0         |  |

|          |          | P03                  |                 |           |  |

| 137      | 113      | TMS                  | E               | G         |  |

|          |          | SWDIO                |                 |           |  |

|          |          | P04                  | _               |           |  |

| 138      | 114      | TDO                  | E               | G         |  |

|          |          | SWO                  |                 |           |  |

|          |          | P90                  | _               |           |  |

|          |          | RTO10_1              |                 |           |  |

| 139      |          | (PPG10_1)            | E               | к         |  |

|          |          | TIOB0_1              | -               |           |  |

|          |          | INT12_1              |                 |           |  |

|          |          | IC0_CLK_1            | -               |           |  |

|          |          | P91                  | -               |           |  |

|          |          | SIN5_1               | -               |           |  |

| 140      | -        | RTO11_1<br>(PPG11_1) | Е               | к         |  |

|          |          | TIOB1_1              |                 |           |  |

|          | [        | INT13_1              |                 |           |  |

|          |          | IC0_VCC_1            |                 |           |  |

| Madula                        | Din Nome             | Function                                                         | Pin N    | umber    |

|-------------------------------|----------------------|------------------------------------------------------------------|----------|----------|

| Module                        | Pin Name             | Function                                                         | LQFP 176 | LQFP 144 |

|                               | DTTI0X_0             | Input signal controlling waveform                                | 34       | 29       |

|                               | DTTI0X_1             | generator outputs RTO00 to RTO05 of Multi-Function Timer 0.      | 8        | 8        |

|                               | FRCK0_0              | 16-bit free-run timer ch 0 external                              | 27       | 22       |

|                               | FRCK0_1              | clock input pin                                                  | 13       | 10       |

|                               | IC00_0               |                                                                  | 33       | 28       |

|                               | IC00_1               |                                                                  | 9        | 9        |

|                               | IC01_0               |                                                                  | 32       | 27       |

|                               | IC01_1               | 16-bit input capture input pin of<br>Multi-Function Timer 0.     | 10       | -        |

|                               | IC02_0               | ICxx describes channel number.                                   | 31       | 26       |

|                               | IC02_1               |                                                                  | 11       | -        |

|                               | IC03_0               |                                                                  | 28       | 23       |

|                               | IC03_1               |                                                                  | 12       | -        |

|                               | RTO00_0<br>(PPG00_0) | Waveform generator output pin of<br>Multi-Function Timer 0.      | 35       | 30       |

|                               | RTO00_1<br>(PPG00_1) | This pin operates as PPG00 when it is used in PPG0 output modes. | 2        | 2        |

| Multi-<br>Function<br>Timer 0 | RTO01_0<br>(PPG00_0) | Waveform generator output pin of<br>Multi-Function Timer 0.      | 36       | 31       |

|                               | RTO01_1<br>(PPG00_1) | This pin operates as PPG00 when it is used in PPG0 output modes. | 3        | 3        |

|                               | RTO02_0<br>(PPG02_0) | Waveform generator output pin of Multi-Function Timer 0.         | 37       | 32       |

|                               | RTO02_1<br>(PPG02_1) | This pin operates as PPG02 when it is used in PPG0 output modes. | 4        | 4        |

|                               | RTO03_0<br>(PPG02_0) | Waveform generator output pin of Multi-Function Timer 0.         | 38       | 33       |

|                               | RTO03_1<br>(PPG02_1) | This pin operates as PPG02 when it is used in PPG0 output modes. | 5        | 5        |

|                               | RTO04_0<br>(PPG04_0) | Waveform generator output pin of<br>Multi-Function Timer 0.      | 39       | 34       |

|                               | RTO04_1<br>(PPG04_1) | This pin operates as PPG04 when it is used in PPG0 output modes. | 6        | 6        |

|                               | RTO05_0<br>(PPG04_0) | Waveform generator output pin of Multi-Function Timer 0.         | 40       | 35       |

|                               | RTO05_1<br>(PPG04_1) | This pin operates as PPG04 when it is used in PPG0 output modes. | 7        | 7        |

# 9. Handling Devices

#### **Power-Supply Pins**

In products with multiple VCC and VSS pins, respective pins at the same potential are interconnected within the device in order to prevent malfunctions such as latch-up. All of these pins should be connected externally to the power supply or ground lines, however, in order to reduce electromagnetic emission levels, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Be sure to connect the current-supply source with the power pins and GND pins of this device at low impedance. It is also advisable that a ceramic capacitor of approximately 0.1  $\mu$ F be connected as a bypass capacitor between VCC and VSS near this device.

A malfunction may occur when the power-supply voltage fluctuates rapidly even though the fluctuation is within the guaranteed operating range of the VCC power supply voltage. As a rule of voltage stabilization, suppress voltage fluctuation so that the fluctuation in VCC ripple (peak-to-peak value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the standard VCC value, and the transient fluctuation rate does not exceed 0.1V/µs at a momentary fluctuation such as switching the power supply.

#### **Crystal Oscillator Circuit**

Noise near the X0/X1 and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1, X0A/X1A pins, the crystal oscillator (or ceramic oscillator), and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended that the PC board artwork be designed such that the X0/X1 and X0A/X1A pins are surrounded by ground plane, as this is expected to produce stable operation.

Evaluate the oscillation introduced by the use of the crystal oscillator by your mount board.

#### Sub Crystal Oscillator

The sub-oscillator circuit for devices in this family is low gain to keep current consumption low. To stabilize the oscillation, Cypress recommends a crystal oscillator that meets the following conditions:

- Surface mount type Size: More than 3.2 mm × 1.5 mm Load capacitance: approximately 6 pF to 7 pF

- Lead type Load capacitance: approximately 6 pF to 7 pF

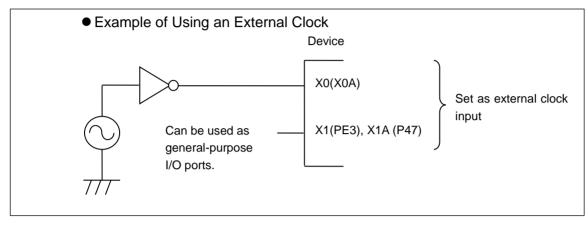

### **Using an External Clock**

When using an external clock as an input of the main clock, set X0/X1 to the external clock input, and input the clock to X0. X1(PE3) can be used as a general-purpose I/O port. Similarly, when using an external clock as an input of the sub clock, set X0A/X1A to the external clock input and input the clock to X0A. X1A (P47) can be used as a general-purpose I/O port.

#### Handling When Using Multi-Function Serial Pin as I<sup>2</sup>C Pin

If the application uses the multi-function serial pin as an I<sup>2</sup>C pin, the P-channel transistor of the digital output must be disabled. I<sup>2</sup>C pins need to conform to electrical limitations like other pins, however, and avoid connecting to live external systems with the MCU power off.

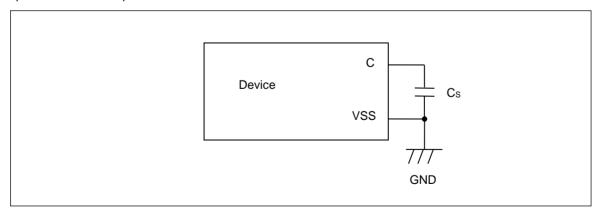

#### C Pin

Devices in this series contain a regulator. Be sure to connect a smoothing capacitor (Cs) for the regulator between the C pin and the GND pin. Please use a ceramic capacitor or a capacitor of equivalent frequency characteristics as a smoothing capacitor. Some laminated ceramic capacitors have a large capacitance variation due to thermal fluctuation. Please select a capacitor that meets the specifications in the operating conditions to use by evaluating the temperature characteristics of the device. A smoothing capacitor of about 4.7  $\mu$ F would be recommended for this series.

#### Mode Pins (MD0)

Connect the MD pin (MD0) directly to VCC or VSS pins. Design the printed circuit board such that the pull-up/down resistance stays low, the distance between the mode pins and VCC pins or VSS pins is as short as possible, and the connection impedance is low when the pins are pulled up/down such as for switching the pin level and rewriting the flash memory data. This is important to prevent the device from erroneously switching to test mode as a result of noise.

## List of Pin Behavior by Mode State

| Pin Status Type | Function<br>Group                                                                    | Power-On<br>Reset or<br>Low-<br>Voltage<br>Detection<br>State    | INITX<br>Input<br>State                     | Device<br>Internal<br>Reset<br>State        | Run mode<br>or Sleep<br>mode State | RTC mode, or                  |                                                      | Deep Standby RTC<br>mode or Deep Standby<br>Stop mode State |                                      | Return from<br>Deep<br>Standby<br>mode State |

|-----------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------|---------------------------------------------|------------------------------------|-------------------------------|------------------------------------------------------|-------------------------------------------------------------|--------------------------------------|----------------------------------------------|

| Pin St          |                                                                                      | Power<br>Supply<br>Unstable                                      |                                             | Supply<br>ble                               | Power<br>Supply<br>Stable          | Power Supply<br>Stable        |                                                      |                                                             | Supply<br>able                       | Power<br>Supply<br>Stable                    |

|                 |                                                                                      | -                                                                | INITX=0                                     | INITX=1                                     | INITX=1                            | INI                           | TX=1                                                 | INITX=1                                                     |                                      | INITX=1                                      |

|                 |                                                                                      | -                                                                | -                                           | -                                           | -                                  | SPL=0                         | SPL=1                                                | SPL=0                                                       | SPL=1                                | -                                            |

|                 | GPIO<br>selected                                                                     | Setting<br>disabled                                              | Setting<br>disabled                         | Setting<br>disabled                         | Maintain<br>previous<br>state      | Maintain<br>previous<br>state | Hi-Z/internal<br>input fixed<br>at 0                 | GPIO<br>selected,<br>internal input<br>fixed<br>at 0        | Hi-Z/internal<br>input fixed<br>at 0 | GPIO<br>selected                             |

| A               | Main crystal<br>oscillator<br>input pin/<br>external main<br>clock input<br>selected | Input<br>enabled                                                 | Input<br>enabled                            | Input<br>enabled                            | Input<br>enabled                   | Input<br>enabled              |                                                      |                                                             | Input<br>enabled                     | Input<br>Enabled                             |

|                 | GPIO<br>selected                                                                     | Setting<br>disabled                                              | Setting<br>disabled                         | Setting<br>disabled                         | Maintain<br>previous<br>state      | Maintain<br>previous<br>state | previous input fixed                                 |                                                             | Hi-Z/internal<br>input fixed<br>at 0 | GPIO<br>selected                             |

| в               | External main<br>clock input<br>selected                                             | Setting<br>disabled                                              | Setting<br>disabled                         | Setting<br>disabled                         | Maintain<br>previous<br>state      | Maintain<br>previous<br>state | Hi-Z/internal<br>input fixed<br>at 0                 | Maintain<br>previous<br>state                               | Hi-Z/internal<br>input fixed<br>at 0 | Maintain<br>previous<br>State                |

|                 | Main crystal<br>oscillator<br>output pin                                             | Hi-Z/<br>internal<br>input fixed<br>at 0/<br>or input<br>enabled | Hi-Z/<br>internal<br>input<br>fixed<br>at 0 | Hi-Z/<br>internal<br>input<br>fixed<br>at 0 |                                    |                               | ain previous sta<br>hen oscillation s<br>Internal in |                                                             |                                      |                                              |

| с               | INITX<br>input pin                                                                   | Pull-up/<br>input<br>enabled                                     | Pull-up/<br>Input<br>enabled                | Pull-up/<br>Input<br>enabled                | Pull-up/<br>Input enabled          | Pull-up/<br>Input<br>enabled  | Pull-up/<br>Input enabled                            | Pull-up/<br>Input<br>enabled                                | Pull-up/<br>Input enabled            | Pull-up/<br>Input<br>enabled                 |

| D               | Mode<br>input pin                                                                    | Input<br>enabled                                                 | Input<br>enabled                            | Input<br>enabled                            | Input<br>enabled                   | Input<br>enabled              | Input<br>enabled                                     | Input<br>enabled                                            | Input<br>enabled                     | Input<br>enabled                             |

|                 | Mode<br>input pin                                                                    | Input<br>enabled                                                 | Input<br>enabled                            | Input<br>enabled                            | Input<br>enabled                   | Input<br>enabled              | Input<br>enabled                                     | Input<br>enabled                                            | Input<br>enabled                     | Input<br>enabled                             |

| E               | GPIO<br>selected                                                                     | Setting<br>disabled                                              | Setting disabled                            | Setting disabled                            | Maintain<br>previous<br>state      | Maintain<br>previous<br>state | Hi-Z/<br>input<br>enabled                            | GPIO<br>selected                                            | Hi-Z/<br>input<br>enabled            | GPIO<br>selected                             |

- 1: Oscillation is stopped at Sub Timer mode, sub CR Timer mode, RTC mode, Stop mode, Deep Standby RTC mode, and Deep Standby Stop mode.

- 2: Maintain previous state at Timer mode. GPIO selected internal input fixed at 0 at RTC mode, Stop mode.

- 3: Maintain previous state at Timer mode. Hi-Z/internal input fixed at 0 at RTC mode, Stop mode.4: It shows the case selected by EPFR14.E\_SPLC register.

| Demonster         | O mark at | Pin  | O a malliti a m  | _      | <b>F</b> *4 | Va    | lue               | Unit | Dementer                              |

|-------------------|-----------|------|------------------|--------|-------------|-------|-------------------|------|---------------------------------------|

| Parameter         | Symbol    | Name | Conditions       |        | Frequency*4 | Typ*1 | Max* <sup>2</sup> | Unit | Remarks                               |

|                   |           |      |                  | 72 MHz | 54          | 112   | mA                |      |                                       |

|                   |           |      |                  |        | 60 MHz      | 47    | 105               | mA   |                                       |

|                   |           |      |                  | 48 MHz | 39          | 97    | mA                |      |                                       |

|                   |           |      |                  | *5     | 36 MHz      | 31    | 89                | mA   | *3                                    |

|                   |           |      |                  | *5     | 24 MHz      | 23    | 81                | mA   | When all peripheral clocks are on     |

|                   |           |      |                  | 12 MHz | 14          | 72    | mA                |      |                                       |

|                   |           | VCC  | Normal operation |        | 8 MHz       | 11    | 69                | mA   |                                       |

| Power             |           |      |                  |        | 4 MHz       | 7.2   | 65                | mA   |                                       |

| supply<br>current | Icc       |      | (PLL)            |        | 72 MHz      | 37    | 95                | mA   |                                       |

| ounon             |           |      | (FLL)            |        | 60 MHz      | 33    | 91                | mA   |                                       |

|                   |           |      |                  |        | 48 MHz      | 28    | 86                | mA   |                                       |

|                   |           |      |                  |        | 36 MHz      | 23    | 81                | mA   | *3                                    |

|                   |           |      |                  | *5     | 24 MHz      | 17    | 75                | mA   | When all peripheral<br>clocks are off |

|                   |           |      |                  |        | 12 MHz      | 11    | 69                | mA   |                                       |

|                   |           |      |                  |        | 8 MHz       | 8.3   | 66                | mA   |                                       |

|                   |           |      |                  |        | 4 MHz       | 5.9   | 63                | mA   | ]                                     |

# Table 12-3 Typical and Maximum Current Consumption in Normal Operation (PLL), Code with Data Accessing Running from Flash Memory (Flash 0 Wait-Cycle Mode and Read Access 0 Wait)

1:  $T_A = +25 \text{ °C}$ ,  $V_{CC} = 3.3 \text{ V}$

2:  $T_J$  = +125 °C,  $V_{CC}$  = 5.5 V

3: When all ports are input and are fixed at 0

4: Frequency is a value of HCLK when PCLK0 = PCLK1 = PCLK2 = HCLK

5: When operating flash 0 wait-cycle mode and read access 0 wait (FRWTR.RWT = 00, FBFCR.SD = 000)

6: With data access to a MainFlash memory.

7: When using the crystal oscillator of 4 MHz (including the current consumption of the oscillation circuit)

### 12.3.2 Pin Characteristics

|                                         | -                |                                           | JSBV <sub>CC</sub> 0 = USBV                                                                                                |                         | Value |                          |            |                    |

|-----------------------------------------|------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|--------------------------|------------|--------------------|

| Parameter                               | Symbol           | Pin Name                                  | Conditions                                                                                                                 | Min                     | Тур   | Max                      | Unit       | Remarks            |

|                                         |                  | CMOS hysteresis input pin,                |                                                                                                                            | V <sub>CC</sub> ×0.8    | -     | V <sub>CC</sub> + 0.3    | V          |                    |

|                                         |                  | MD0, MD1                                  | -                                                                                                                          | ETHV <sub>CC</sub> ×0.8 | -     | ETHV <sub>CC</sub> + 0.3 | V          |                    |

| H level input<br>voltage<br>(hysteresis | V <sub>IHS</sub> | MADATAxx                                  | $\label{eq:VCC} \begin{array}{l} V_{CC} > \textbf{3.0 V,} \\ V_{CC} \leq \textbf{3.6 V,} \end{array}$                      | 2.4                     | -     | V <sub>CC</sub> + 0.3    | V          | At External<br>Bus |

| input)                                  |                  | 5V tolerant input pin                     | -                                                                                                                          | V <sub>CC</sub> ×0.8    | -     | V <sub>SS</sub> + 5.5    | V          |                    |

|                                         |                  | Input pin doubled as I <sup>2</sup> C Fm+ | -                                                                                                                          | V <sub>CC</sub> ×0.7    | -     | V <sub>ss</sub> + 5.5    | V          |                    |

|                                         |                  | TTL Schmitt input pin                     | -                                                                                                                          | 2.0                     | -     | ETHV <sub>CC</sub> +0.3  | V          |                    |

|                                         |                  | CMOS hysteresis input pin,                |                                                                                                                            | V <sub>SS</sub> - 0.3   | -     | V <sub>CC</sub> ×0.2     | V          |                    |

| L level input                           |                  | MD0, MD1                                  | -                                                                                                                          | V <sub>ss</sub> - 0.3   | -     | ETHV <sub>CC</sub> ×0.2  | V          |                    |

| voltage<br>(hysteresis                  | VILS             | 5V tolerant input pin                     | -                                                                                                                          | V <sub>SS</sub> - 0.3   | -     | V <sub>CC</sub> ×0.2     | V          |                    |

| input)                                  |                  | Input pin doubled as I <sup>2</sup> C Fm+ | -                                                                                                                          | Vss                     | -     | V <sub>CC</sub> ×0.3     | V          |                    |

|                                         |                  | TTL Schmitt input pin                     | -                                                                                                                          | V <sub>SS</sub> - 0.3   | -     | 0.8                      | V          |                    |

|                                         |                  |                                           | $\label{eq:Vcc} \begin{array}{l} V_{\rm CC} \geq 4.5 \ \text{V}, \\ I_{\rm OH} = - \ 4 \ \text{mA} \end{array}$            | V <sub>CC</sub> - 0.5   |       | V <sub>cc</sub>          | V          |                    |

|                                         |                  |                                           | $V_{\rm CC}$ < 4.5 V,<br>$I_{\rm OH}$ = - 2 mA                                                                             | VCC - 0.5               | -     | VCC                      | v          |                    |

|                                         |                  | 4 mA type                                 | $\begin{array}{l} \text{ETHV}_{\text{CC}} \geq 4.5 \text{ V}, \\ \text{I}_{\text{OH}} = \text{-} 4 \text{ mA} \end{array}$ | V <sub>CC</sub> - 0.5   | _     | ETHVcc                   | V          |                    |

|                                         |                  |                                           | $\begin{array}{l} \text{ETHV}_{\rm CC} < 4.5 \text{ V}, \\ I_{\rm OH} = \text{-} 2 \text{ mA} \end{array}$                 |                         |       |                          |            |                    |

|                                         |                  | 8 mA type                                 | $\label{eq:VCC} \begin{array}{l} V_{\rm CC} \geq 4.5 \ \text{V}, \\ I_{\rm OH} = \text{-} \ 8 \ \text{mA} \end{array}$     | V <sub>CC</sub> - 0.5   | -     | Vcc                      | V          |                    |

|                                         |                  |                                           | V <sub>CC</sub> < 4.5 V,<br>I <sub>OH</sub> = - 4 mA                                                                       | V(( - 0.0               | _     | Vit                      | v          |                    |

| H level output                          | V <sub>OH</sub>  |                                           | $\begin{array}{l} \text{ETHV}_{\text{CC}} \geq 4.5 \text{ V}, \\ \text{I}_{\text{OH}} = \text{- 8 mA} \end{array}$         | ETHVcc - 0.5            | -     | ETHVcc                   | V          |                    |

| voltage                                 | V OH             |                                           | ETHV <sub>CC</sub> < 4.5 V,<br>І <sub>ОН</sub> = - 4 mA                                                                    |                         |       |                          |            |                    |

|                                         |                  | 12 mA type                                | $\label{eq:VCC} \begin{array}{l} V_{\rm CC} \geq 4.5 \ \text{V}, \\ I_{\rm OH} = \text{-} \ 12 \ \text{mA} \end{array}$    | V <sub>CC</sub> - 0.5   | -     | Vcc                      | V          |                    |

|                                         |                  |                                           | V <sub>CC</sub> < 4.5 V,<br>I <sub>OH</sub> = - 8 mA                                                                       | Vec - 0.5               | -     | Vtt                      | v          |                    |

|                                         |                  | The pin                                   | $\begin{array}{l} USBV_{CC} \geq 4.5 \text{ V}, \\ I_{OH} = \text{-} 20.5 \text{ mA} \end{array}$                          | USBVcc - 0.4            |       | USBVcc                   | V          | *1                 |

|                                         |                  | doubled as USB I/O                        | $\begin{array}{l} USBV_{\rm CC} < 4.5 \text{ V}, \\ I_{\rm OH} = - \ 13.0 \text{ mA} \end{array}$                          | 000 VCC - 0.4           | -     | USBVCC                   | v          |                    |

|                                         |                  | The pip doubled as <sup>12</sup> C Free   | $\label{eq:Vcc} \begin{array}{l} V_{\rm CC} \geq 4.5 \ \text{V}, \\ I_{\rm OH} = - \ 4 \ \text{mA} \end{array}$            |                         |       | V                        | \ <i>\</i> |                    |

|                                         |                  | The pin doubled as I <sup>2</sup> C Fm+   | V <sub>CC</sub> < 4.5V,<br>I <sub>OH</sub> = - 3 mA                                                                        | V <sub>CC</sub> - 0.5   | -     | Vcc                      | V          | At GPIO            |

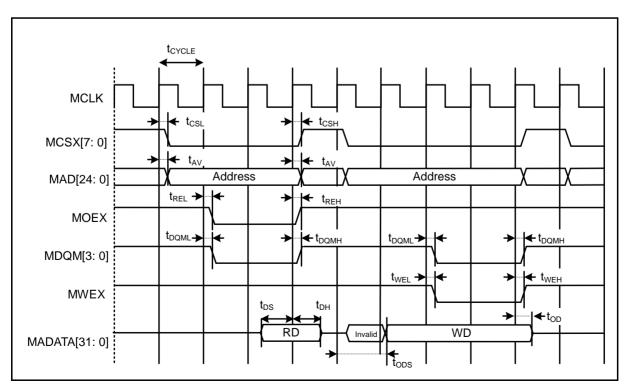

## Separate Bus Access Synchronous SRAM Mode

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Devenueter                   | Cumula al         | Din Nama               | Conditions | Va     | lue     | 11   | Domorko |

|------------------------------|-------------------|------------------------|------------|--------|---------|------|---------|

| Parameter                    | Symbol            | Pin Name               | Conditions | Min    | Max     | Unit | Remarks |

| Address delay time           | t <sub>AV</sub>   | MCLK,<br>MAD[24: 0]    | -          | 1      | 9       | ns   |         |

|                              | tcs∟              | MCLK,                  | -          | 1      | 9       | ns   |         |

| MCSX delay time              | t <sub>сsн</sub>  | MCSX[7: 0]             | -          | 1      | 9       | ns   |         |

| MOEV dolou time              | t <sub>REL</sub>  | MCLK,                  | -          | 1      | 9       | ns   |         |

| MOEX delay time              | t <sub>REH</sub>  | MOEX                   | -          | 1      | 9       | ns   |         |

| Data set up<br>→MCLK ↑ time  | t <sub>DS</sub>   | MCLK,<br>MADATA[31: 0] | -          | 19     | -       | ns   |         |

| MCLK ↑ →<br>Data hold time   | t <sub>DH</sub>   | MCLK,<br>MADATA[31: 0] | -          | 0      | -       | ns   |         |

|                              | twel              | MCLK,                  | -          | 1      | 9       | ns   |         |

| MWEX delay time              | t <sub>WEH</sub>  | MWEX                   | -          | 1      | 9       | ns   |         |

| MDQM[1: 0]                   | <b>t</b> DQML     | MCLK,                  | -          | 1      | 9       | ns   |         |

| delay time                   | t <sub>DQMH</sub> | MDQM[3: 0]             | -          | 1      | 9       | ns   |         |

| MCLK ↑ →<br>Data output time | t <sub>ODS</sub>  | MCLK,<br>MADATA[31: 0] | -          | MCLK+1 | MCLK+18 | ns   |         |

| MCLK ↑ →<br>Data hold time   | top               | MCLK,<br>MADATA[31: 0] | -          | 1      | 18      | ns   |         |

Note:

- When the external load capacitance  $C_L = 30 \, pF$

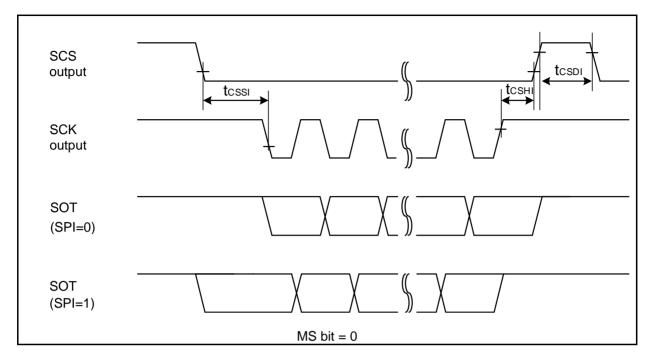

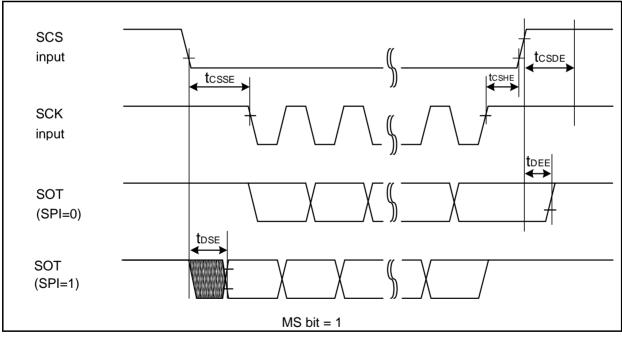

## When Using Synchronous Serial Chip Select (SCINV = 0, CSLVL = 0)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Devementer           | Cumhal            | Conditions              | Vcc <                          | 4.5 V                          | V <sub>cc</sub> ≥              | Unit                           |      |  |

|----------------------|-------------------|-------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|------|--|

| Parameter            | Symbol            | Conditions              | Min                            | Мах                            | Min                            | Мах                            | onit |  |

| SCS↑→SCK↓ setup time | tcssi             |                         | (*1)-50                        | (*1)+0                         | (*1)-50                        | (*1)+0                         | ns   |  |

| SCK↑→SCS↓ hold time  | tcsнi             | Internal shift<br>clock | (*2)+0                         | (*2)+50                        | (*2)+0                         | (*2)+50                        | ns   |  |

| SCS deselect time    | tcsDI             | operation               | (*3)-50<br>+5t <sub>CYCP</sub> | (*3)+50<br>+5t <sub>CYCP</sub> | (*3)-50<br>+5t <sub>СҮСР</sub> | (*3)+50<br>+5t <sub>CYCP</sub> | ns   |  |

| SCS↑→SCK↓ setup time | t <sub>CSSE</sub> |                         | 3t <sub>CYCP</sub> +30         | -                              | 3t <sub>CYCP</sub> +30         | -                              | ns   |  |

| SCK↑→SCS↓ hold time  | tcshe             |                         | 0                              | -                              | 0                              | -                              | ns   |  |

| SCS deselect time    | tcsde             | External shift<br>clock | 3tcycp+30                      | -                              | 3tcycp+30                      | -                              | ns   |  |

| SCS∱→SOT delay time  | tDSE              | operation               | -                              | 40                             | -                              | 40                             | ns   |  |

| SCS↓→SOT delay time  | <b>t</b> DEE      |                         | 0                              | -                              | 0                              | -                              | ns   |  |

(\*1): CSSU bit valuexserial chip select timing operating clock cycle [ns]

(\*2): CSHD bit valuexserial chip select timing operating clock cycle [ns]

(\*3): CSDS bit valuexserial chip select timing operating clock cycle [ns]

#### Notes:

- tcycp indicates the APB bus clock cycle time. For more information about the APB bus number to which the multi-function serial is connected, see 1. S6E2G Series Block Diagram in this data sheet.

- For more information about CSSU, CSHD, CSDS, and the serial chip select timing operating clock, see FM4 Family Peripheral Manual Main Part (002-04856).

- When the external load capacitance  $C_L = 30 \text{ pF}$ .

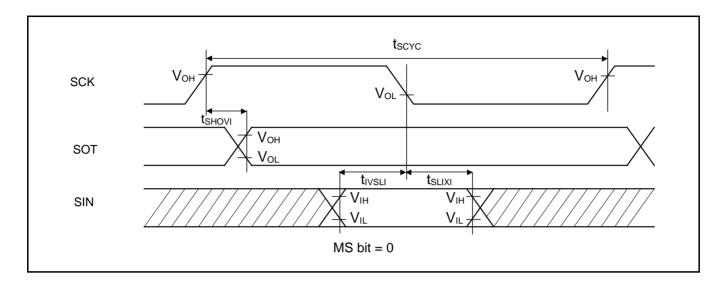

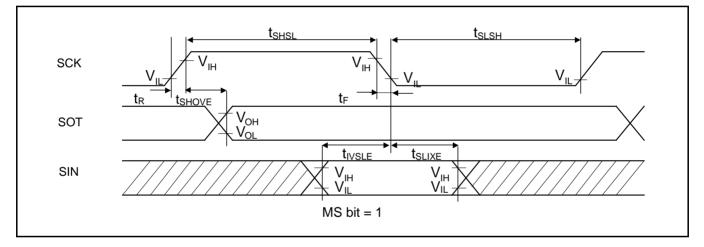

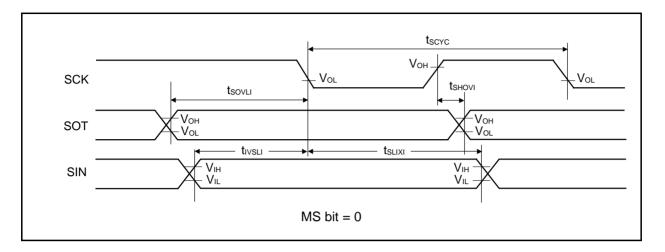

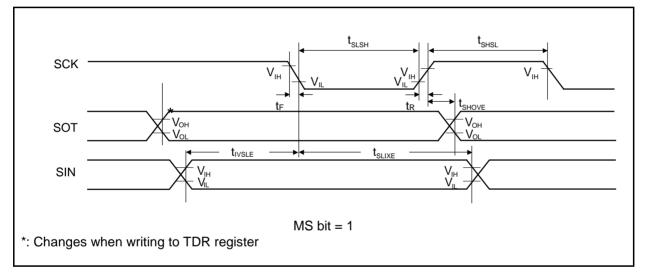

## High-Speed Synchronous Serial (SPI = 1, SCINV = 1)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Demonster                  | 0. mili al         | Pin           | O an all the set               | <b>V</b> cc <           | 4.5 V | V <sub>CC</sub> ≥       | 4.5 V | 11   |

|----------------------------|--------------------|---------------|--------------------------------|-------------------------|-------|-------------------------|-------|------|

| Parameter                  | Symbol             | Name          | Conditions                     | Min                     | Max   | Min                     | Max   | Unit |

| Serial clock cycle time    | tscyc              | SCKx          |                                | 4tcycp                  | -     | 4t <sub>CYCP</sub>      | -     | ns   |

| SCK↓→SOT delay time        | tslovi             | SCKx,<br>SOTx |                                | - 10                    | + 10  | - 10                    | + 10  | ns   |

| SIN→SCK↑ setup time        | tı∨sнı             | SCKx,         | Internal shift                 | 14                      |       | 12.5                    |       | ns   |

|                            | UVSHI              | SINx          | clock operation                | 12.5*                   | -     | 12.5                    | -     | 115  |

| SCK↑→SIN hold time         | t <sub>SHIXI</sub> | SCKx,<br>SINx |                                | 5                       | -     | 5                       | -     | ns   |

| SOT→SCK↑ delay time        | tsovнı             | SCKx,<br>SOTx |                                | 2t <sub>CYCP</sub> - 10 | -     | 2t <sub>CYCP</sub> - 10 | -     | ns   |

| Serial clock L pulse width | t <sub>SLSH</sub>  | SCKx          |                                | 2t <sub>CYCP</sub> - 5  | -     | 2t <sub>CYCP</sub> - 5  | -     | ns   |

| Serial clock H pulse width | t <sub>SHSL</sub>  | SCKx          |                                | t <sub>CYCP</sub> + 10  | -     | t <sub>CYCP</sub> + 10  | -     | ns   |

| SCK↓→SOT delay time        | <b>t</b> SLOVE     | SCKx,<br>SOTx |                                | -                       | 15    | -                       | 15    | ns   |

| SIN→SCK↑ setup time        | tivshe             | SCKx,<br>SINx | External shift clock operation | 5                       | -     | 5                       | -     | ns   |

| SCK↑→SIN hold time         | t <sub>SHIXE</sub> | SCKx,<br>SINx |                                | 5                       | -     | 5                       | -     | ns   |

| SCK fall time              | t⊧                 | SCKx          | ]                              | -                       | 5     | -                       | 5     | ns   |

| SCK rise time              | t <sub>R</sub>     | SCKx          |                                | -                       | 5     | -                       | 5     | ns   |

#### Notes:

The above characteristics apply to CLK synchronous mode.

- tcycp indicates the APB bus clock cycle time. For more information about the APB bus number to which the multi-function serial is connected, see 1. S6E2G Series Block Diagram in this data sheet.

- These characteristics only guarantee the following pins:

No chip select: SIN4\_0, SOT4\_0, SCK4\_0

Chip select: SIN6\_0, SOT6\_0, SCK6\_0, SCS60\_0, SCS61\_0, SCS62\_0, SCS63\_0

- When the external load capacitance  $C_L = 30 \text{ pF}$ . (for \*, when  $C_L = 10 \text{ pF}$ )

## When Using High-Speed Synchronous Serial Chip Select (SCINV = 1, CSLVL = 0)

$(V_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = 0V)$

| Denemator            | Complete          | Conditions              | Vcc <                          | 4.5 V                          | V <sub>cc</sub> ≥              | Unit                           |      |

|----------------------|-------------------|-------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|------|

| Parameter            | Symbol            | Conditions              | Min                            | Мах                            | Min                            | Мах                            | Unit |

| SCS↓→SCK↓ setup time | tcssi             |                         | (*1)-20                        | (*1)+0                         | (*1)-20                        | (*1)+0                         | ns   |

| SCK↑→SCS↓ hold time  | tсsні             | Internal shift<br>clock | (*2)+0                         | (*2)+20                        | (*2)+0                         | (*2)+20                        | ns   |

| SCS deselect time    | tcsdi             | operation               | (*3)-20<br>+5t <sub>CYCP</sub> | (*3)+20<br>+5t <sub>CYCP</sub> | (*3)-20<br>+5t <sub>СҮСР</sub> | (*3)+20<br>+5t <sub>СҮСР</sub> | ns   |

| SCS↑→SCK↑ setup time | t <sub>CSSE</sub> |                         | 3t <sub>CYCP</sub> +15         | -                              | 3t <sub>CYCP</sub> +15         | -                              | ns   |

| SCK↓→SCS↓ hold time  | tcshe             |                         | 0                              | -                              | 0                              | -                              | ns   |

| SCS deselect time    | tcsde             | External shift<br>clock | 3tcycp+15                      | -                              | 3tcycp+15                      | -                              | ns   |

| SCS∱→SOT delay time  | tDSE              | operation               | -                              | 40                             | -                              | 40                             | ns   |

| SCS↓→SOT delay time  | tdee              |                         | 0                              | -                              | 0                              | -                              | ns   |

(\*1): CSSU bit valuexserial chip select timing operating clock cycle [ns]

(\*2): CSHD bit valuexserial chip select timing operating clock cycle [ns]

(\*3): CSDS bit valuexserial chip select timing operating clock cycle [ns]

#### Notes:

- tcycp indicates the APB bus clock cycle time. For more information about the APB bus number to which the multi-function serial is connected, see 1. S6E2G Series Block Diagram in this data sheet.

- For more information about CSSU, CSHD, CSDS, and the serial chip select timing operating clock, see FM4 Family Peripheral Manual Main Part (002-04856).

- When the external load capacitance  $C_L = 30 \text{ pF}$ .

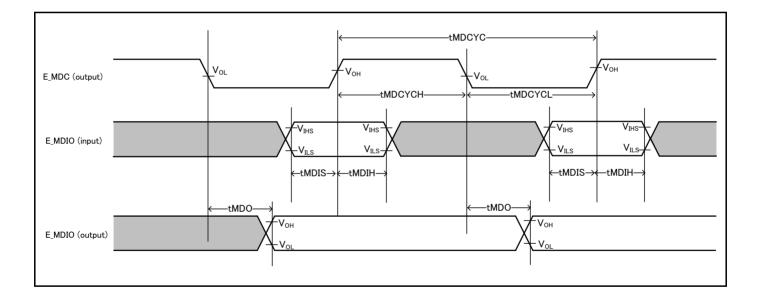

### **Management Interface**

| Deservation                                                        | 0. militad          | Dia Nama | Osmalitisms    | Va  | Unit    |    |

|--------------------------------------------------------------------|---------------------|----------|----------------|-----|---------|----|

| Parameter                                                          | Symbol              | Pin Name | Conditions     | Min | Min Max |    |

| Management clock<br>cycle time*                                    | tмdсүс              | E_MDC    | -              | 400 | -       | ns |

| Management clock<br>High pulse width duty cycle                    | tмdсүсн             | E_MDC    | tмdсүсн/tмdсүс | 35  | 65      | %  |

| Management clock<br>Low pulse width duty cycle                     | t <sub>MDCYCL</sub> | E_MDC    | tмdсүсL/tмdсүс | 35  | 65      | %  |

| MDC ↓ → MDIO<br>Delay time                                         | t <sub>MDO</sub>    | E_MDIO   | -              | -   | 60      | ns |

| $\begin{array}{l} MDIO \to MDC \uparrow \\ Setup time \end{array}$ | t <sub>MDIS</sub>   | E_MDIO   | -              | 20  | -       | ns |

| MDC ↑ → MDIO<br>Hold time                                          | tмdiн               | E_MDIO   | -              | 0   | -       | ns |

(ETHV<sub>CC</sub> = 3.0V to 3.6V, 4.5V to 5.5V, V<sub>SS</sub> = 0V, C<sub>L</sub> = 25 pF)

\*: The clock time should be set to a value greater than the minimum value by setting the Ethernet-MAC setting register.

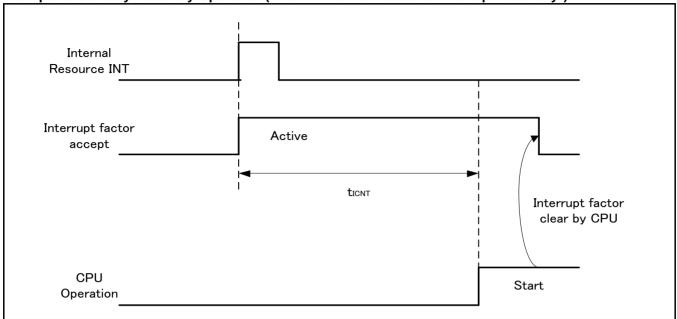

#### Example of Standby Recovery Operation (when in Internal Resource Interrupt Recovery\*)

\*: Depending on the standby mode, interrupt from the internal resource is not included in the recovery cause.

#### Notes:

- The return factor is different in each low-power consumption mode. See Chapter 6: Low Power Consumption mode and Operations of Standby modes in FM4 Family Peripheral Manual Main Part (002-04856).

- The recovery process is unique for each operating mode. See Chapter 6: Low Power Consumption mode in FM4 Family Peripheral Manual Main Part (002-04856).

# **13. Ordering Information**

| Part Number       | Flash  | RAM    | CAN          | Ethernet | SD Card      | Crypto       | Package                                 |

|-------------------|--------|--------|--------------|----------|--------------|--------------|-----------------------------------------|

| S6E2GM6H0AGV2000A | 512 KB | 128 KB | $\checkmark$ | ~        | ✓            |              |                                         |

| S6E2GM8H0AGV2000A | 1 MB   | 192 KB | ✓            | ~        | ✓            |              | Plastic LQFP (0.5 mm pitch),            |

| S6E2GM6HHAGV2000A | 512 KB | 128 KB | $\checkmark$ | ~        | ✓            | $\checkmark$ | 144 pin<br>(LQS144)                     |

| S6E2GM8HHAGV2000A | 1 MB   | 192 KB | $\checkmark$ | ~        | ~            | ✓            |                                         |

| S6E2GM6J0AGV2000A | 512 KB | 128 KB | ✓            | ~        | ✓            |              |                                         |

| S6E2GM8J0AGV2000A | 1 MB   | 192 KB | ✓            | ~        | ✓            |              | Plastic LQFP (0.5 mm pitch),<br>176 pin |

| S6E2GM6JHAGV2000A | 512 KB | 128 KB | $\checkmark$ | ~        | ~            | $\checkmark$ | (LQP176)                                |

| S6E2GM8JHAGV2000A | 1 MB   | 192 KB | $\checkmark$ | ✓        | ✓            | ✓            |                                         |

| S6E2GK6H0AGV2000A | 512 KB | 128 KB |              | ~        | ~            |              |                                         |

| S6E2GK8H0AGV2000A | 1 MB   | 192 KB |              | ~        | $\checkmark$ |              | Plastic LQFP (0.5 mm pitch),<br>144 pin |

| S6E2GK6HHAGV2000A | 512 KB | 128 KB |              | ~        | $\checkmark$ | ~            | (LQS144)                                |

| S6E2GK8HHAGV2000A | 1 MB   | 192 KB |              | ~        | ✓            | ~            |                                         |

| S6E2GK6J0AGV2000A | 512 KB | 128 KB |              | ~        | ✓            |              |                                         |

| S6E2GK8J0AGV2000A | 1 MB   | 192 KB |              | ~        | ~            |              | Plastic LQFP (0.5 mm pitch),            |

| S6E2GK6JHAGV2000A | 512 KB | 128 KB |              | ~        | ~            | ✓            | 176 pin<br>(LQP176)                     |

| S6E2GK8JHAGV2000A | 1 MB   | 192 KB |              | ~        | ~            | √            |                                         |

| S6E2GH6H0AGV2000A | 512 KB | 128 KB | $\checkmark$ |          | ~            |              | Plastic LQFP (0.5 mm pitch),            |

| S6E2GH8H0AGV2000A | 1 MB   | 192 KB | $\checkmark$ |          | ~            |              | 144 pin<br>(LQS144)                     |

| S6E2GH6J0AGV2000A | 512 KB | 128 KB | $\checkmark$ |          | ~            |              | Plastic LQFP (0.5 mm pitch),            |

| S6E2GH8J0AGV2000A | 1 MB   | 192 KB | $\checkmark$ |          | ~            |              | 176 pin<br>(LQP176)                     |

| S6E2G36H0AGV2000A | 512 KB | 128 KB |              |          |              |              | Plastic LQFP (0.5 mm pitch),            |

| S6E2G38H0AGV2000A | 1 MB   | 192 KB |              |          |              |              | 144 pin<br>(LQS144)                     |

| S6E2G36J0AGV2000A | 512 KB | 128 KB |              |          |              |              | Plastic LQFP (0.5 mm pitch),            |

| S6E2G38J0AGV2000A | 1 MB   | 192 KB |              |          |              |              | 176 pin<br>(LQP176)                     |

| S6E2G26H0AGV2000A | 512 KB | 128 KB |              | ~        |              |              |                                         |

| S6E2G28H0AGV2000A | 1 MB   | 192 KB |              | ~        |              |              | Plastic LQFP (0.5 mm pitch),            |

| S6E2G26HHAGV2000A | 512 KB | 128 KB |              | ~        |              | ~            | 144 pin<br>(LQS144)                     |

| S6E2G28HHAGV2000A | 1 MB   | 192 KB |              | ~        |              | ~            |                                         |

| S6E2G26J0AGV2000A | 512 KB | 128 KB |              | ~        |              |              |                                         |

| S6E2G28J0AGV2000A | 1 MB   | 192 KB |              | ~        |              |              | Plastic LQFP (0.5 mm pitch),            |

| S6E2G26JHAGV2000A | 512 KB | 128 KB |              | ~        |              | ~            | 176 pin<br>(LQP176)                     |

| S6E2G28JHAGV2000A | 1 MB   | 192 KB |              | ~        |              | ~            |                                         |