### NXP USA Inc. - MC9S08AC128CFUER Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | S08                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                       |

| Number of I/O              | 54                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-QFP                                                                   |

| Supplier Device Package    | 64-QFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac128cfuer |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Chapter 1<br>Device Overview                           |

|--------------------------------------------------------|

| Chapter 2                                              |

| Pins and Connections                                   |

| 2.1 Device Pin Assignment                              |

| Chapter 3                                              |

| Electrical Characteristics and Timing Specifications11 |

| 3.1 Introduction                                       |

| 3.2 Parameter Classification                           |

| 3.3 Absolute Maximum Ratings11                         |

| 3.4 Thermal Characteristics                            |

| 3.5 ESD Protection and Latch-Up Immunity               |

| 3.6 DC Characteristics                                 |

| 3.7 Supply Current Characteristics                     |

| 3.8 ADC Characteristics                                |

| 3.9       | Internal Clock Generation Module Characteristics 24 |

|-----------|-----------------------------------------------------|

|           | 3.9.1 ICG Frequency Specifications 25               |

| 3.10      | AC Characteristics                                  |

|           | 3.10.1 Control Timing 27                            |

|           | 3.10.2 Timer/PWM (TPM) Module Timing 28             |

| 3.11      | SPI Characteristics                                 |

| 3.12      | FLASH Specifications                                |

|           | EMC Performance                                     |

|           | 3.13.1 Radiated Emissions 34                        |

| Chapter 4 | 4                                                   |

| Orde      | ring Information and Mechanical Drawings            |

| 4.1       | Ordering Information                                |

| 4.2       | Orderable Part Numbering System                     |

| 4.3       | Mechanical Drawings                                 |

| Chapter 5 |                                                     |

| Revis     | sion History                                        |

### **Related Documentation**

### MC9S08AC128 Series Reference Manual (MC9S08AC128RM)

contains extensive product information including modes of operartion, memory, resets and interrupts, register definitions, port pins, CPU, and all peripheral module information.

For the latest version of the documentation, check our website at: http://www.freescale.com

**Chapter 2 Pins and Connections**

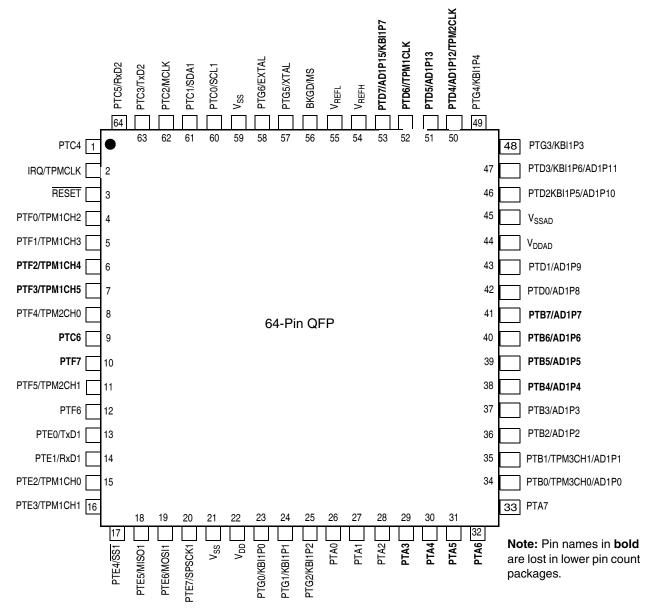

Figure 2-2 shows the 64-pin package assignments for the MC9S08AC128 Series devices.

Figure 2-2. MC9S08AC128 Series in 64-Pin QFP Package

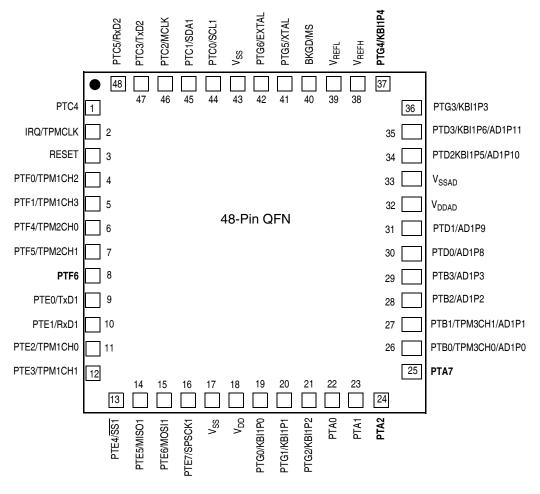

Figure 2-1 shows the 48-pin package assignments for the MC9S08AC128 Series devices.

**Note:** Pin names in **bold** are lost in lower pin count packages.

|    | Pin N | umber | r  | Lowest <        | Priority | > Highest |

|----|-------|-------|----|-----------------|----------|-----------|

| 80 | 64    | 48    | 44 | Port Pin        | Alt 1    | Alt 2     |

| 13 | —     | _     | _  | PTJ0            |          |           |

| 14 | —     | _     | _  | PTJ1            |          |           |

| 15 | _     | _     | _  | PTJ2            |          |           |

| 16 | —     | —     | _  | PTJ3            |          |           |

| 17 | 13    | 9     | 8  | PTE0            | TxD1     |           |

| 18 | 14    | 10    | 9  | PTE1            | RxD1     |           |

| 19 | 15    | 11    | 10 | PTE2            | TPM1CH0  |           |

| 20 | 16    | 12    | 11 | PTE3            | TPM1CH1  |           |

| 21 | 17    | 13    | 12 | PTE4            | SS1      |           |

| 22 | 18    | 14    | 13 | PTE5            | MISO1    |           |

| 23 | 19    | 15    | 14 | PTE6            | MOSI1    |           |

| 24 | 20    | 16    | 15 | PTE7            | SPSCK1   |           |

| 25 | 21    | 17    | 16 | V <sub>SS</sub> |          |           |

| 26 | 22    | 18    | 17 | V <sub>DD</sub> |          |           |

| 27 | —     |       |    | PTJ4            |          |           |

| 28 | —     |       |    | PTJ5            |          |           |

| 29 | —     |       |    | PTJ6            |          |           |

| 30 | —     | _     | _  | PTJ7            |          |           |

| 31 | 23    | 19    | 18 | PTG0            | KBI1P0   |           |

| 32 | 24    | 20    | 19 | PTG1            | KBI1P1   |           |

| 33 | 25    | 21    | 20 | PTG2            | KBI1P2   |           |

| 34 | 26    | 22    | 21 | PTA0            |          |           |

| 35 | 27    | 23    | 22 | PTA1            |          |           |

| 36 | 28    | 24    |    | PTA2            |          |           |

| 37 | 29    | —     |    | PTA3            |          |           |

| 38 | 30    | _     |    | PTA4            |          |           |

| 39 | 31    | _     |    | PTA5            |          |           |

| 40 | 32    | —     | _  | PTA6            |          |           |

| 41 | 33    | 25    | _  | PTA7            |          |           |

| 42 | _     | _     | _  | PTH0            | TPM2CH2  |           |

| 43 | _     | _     | —  | PTH1            | TPM2CH3  |           |

| 44 | —     | _     |    | PTH2            | TPM2CH4  |           |

| 45 | —     | _     |    | PTH3            | TPM2CH5  |           |

| 46 | 34    | 26    | 23 | PTB0            | TPM3CH0  | AD1P0     |

| 47 | 35    | 27    | 24 | PTB1            | TPM3CH1  | AD1P1     |

| 48 | 36    | 28    | 25 | PTB2            | AD1P2    |           |

| 49 | 37    | 29    | 26 | PTB3            | AD1P3    |           |

| 50 | 38    | _     | _  | PTB4            | AD1P4    |           |

| 51 | 39    | —     | —  | PTB5            | AD1P5    |           |

| 52 | 40    | —     | —  | PTB6            | AD1P6    |           |

| 53 | 41    | —     | —  | PTB7            | AD1P7    |           |

Table 2-4. Pin Availability by Package Pin-Count (continued)

# Chapter 3 Electrical Characteristics and Timing Specifications

# 3.1 Introduction

This section contains electrical and timing specifications.

## 3.2 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

### Table 3-1. Parameter Classifications

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 3.3 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 3-2 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ).

| Num | С | Deveneter                                                                                                                                                                                                                                                                                   | Symbol             | Min                                                                                              | <b>T</b> . m1    | Мах                      | Linit |

|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------|------------------|--------------------------|-------|

| Num | U | Parameter                                                                                                                                                                                                                                                                                   | Symbol             | Min                                                                                              | Typ <sup>1</sup> | -                        | Unit  |

| 1   | - | Operating Voltage                                                                                                                                                                                                                                                                           | V <sub>DD</sub>    | 2.7                                                                                              | —                | 5.5                      | V     |

| 2   | Ρ | Output high voltage — Low Drive (PTxDSn = 0)<br>$5 \text{ V}, \text{ I}_{\text{Load}} = -2 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = -0.6 \text{ mA}$<br>$5 \text{ V}, \text{ I}_{\text{Load}} = -0.4 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = -0.24 \text{ mA}$ |                    | V <sub>DD</sub> - 1.5<br>V <sub>DD</sub> - 1.5<br>V <sub>DD</sub> - 0.8<br>V <sub>DD</sub> - 0.8 |                  | <br>                     |       |

|     | Ρ | Output high voltage — High Drive (PTxDSn = 1)<br>$5 \text{ V}, \text{ I}_{\text{Load}} = -10 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = -3 \text{ mA}$<br>$5 \text{ V}, \text{ I}_{\text{Load}} = -2 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = -0.4 \text{ mA}$    | V <sub>OH</sub>    | V <sub>DD</sub> - 1.5<br>V <sub>DD</sub> - 1.5<br>V <sub>DD</sub> - 0.8<br>V <sub>DD</sub> - 0.8 |                  |                          | V     |

| 3   | Ρ | Output low voltage — Low Drive (PTxDSn = 0)<br>$5 \text{ V}, \text{ I}_{\text{Load}} = 2 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = 0.6 \text{ mA}$<br>$5 \text{ V}, \text{ I}_{\text{Load}} = 0.4 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = 0.24 \text{ mA}$      | Mari               |                                                                                                  |                  | 1.5<br>1.5<br>0.8<br>0.8 | V     |

|     | Ρ | Output low voltage — High Drive (PTxDSn = 1)<br>5 V, I <sub>Load</sub> = 10 mA<br>3 V, I <sub>Load</sub> = 3 mA<br>5 V, I <sub>Load</sub> = 2 mA<br>3 V, I <sub>Load</sub> = 0.4 mA                                                                                                         | V <sub>OL</sub>    |                                                                                                  |                  | 1.5<br>1.5<br>0.8<br>0.8 | v     |

| 4   | Ρ | Output high current — Max total I <sub>OH</sub> for all ports<br>5V<br>3V                                                                                                                                                                                                                   | I <sub>ОНТ</sub>   |                                                                                                  |                  | 100<br>60                | mA    |

| 5   | Ρ | Output low current — Max total I <sub>OL</sub> for all ports<br>5V<br>3V                                                                                                                                                                                                                    | I <sub>OLT</sub>   | _                                                                                                |                  | 100<br>60                | mA    |

| 6   | Ρ | Input high $2.7v \le V_{DD} 4.5v$                                                                                                                                                                                                                                                           | V <sub>IH</sub>    | $0.70 \mathrm{xV}_{\mathrm{DD}}$                                                                 | _                | —                        |       |

|     |   | voltage; all $4.5v \le V_{DD} \le 5.5v$                                                                                                                                                                                                                                                     | V <sub>IH</sub>    | 0.65xV <sub>DD</sub>                                                                             |                  | —                        | V     |

| 7   | Ρ | Input low voltage; all digital inputs                                                                                                                                                                                                                                                       | V <sub>IL</sub>    |                                                                                                  | _                | $0.35 \times V_{DD}$     |       |

| 8   | Ρ | Input hysteresis; all digital inputs                                                                                                                                                                                                                                                        | V <sub>hys</sub>   | $0.06 \times V_{DD}$                                                                             |                  |                          | mV    |

| 9   | Ρ | Input leakage current; input only pins <sup>2</sup>                                                                                                                                                                                                                                         | ll <sub>In</sub> l |                                                                                                  | 0.1              | 1                        | μA    |

| 10  | Ρ | High Impedance (off-state) leakage current <sup>2</sup>                                                                                                                                                                                                                                     | I <sub>OZ</sub>    | _                                                                                                | 0.1              | 1                        | μA    |

| 11  | Ρ | Internal pullup resistors <sup>3</sup>                                                                                                                                                                                                                                                      | R <sub>PU</sub>    | 20                                                                                               | 45               | 65                       | kΩ    |

| 12  | Ρ | Internal pulldown resistors <sup>4</sup>                                                                                                                                                                                                                                                    | R <sub>PD</sub>    | 20                                                                                               | 45               | 65                       | kΩ    |

| 13  | С | Input Capacitance; all non-supply pins                                                                                                                                                                                                                                                      | C <sub>In</sub>    | _                                                                                                | —                | 8                        | pF    |

| 14  | D | RAM retention voltage                                                                                                                                                                                                                                                                       | V <sub>RAM</sub>   | _                                                                                                | 0.6              | 1.0                      | V     |

| 15  | Ρ | POR rearm voltage                                                                                                                                                                                                                                                                           | V <sub>POR</sub>   | 0.9                                                                                              | 1.4              | 2.0                      | V     |

| 16  | D | POR rearm time                                                                                                                                                                                                                                                                              | t <sub>POR</sub>   | 10                                                                                               |                  | —                        | μS    |

| 17  | Ρ | Low-voltage detection threshold — high range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                                                                                                                           | V <sub>LVDH</sub>  | 4.2<br>4.3                                                                                       | 4.3<br>4.4       | 4.4<br>4.5               | V     |

| 18  | Ρ | Low-voltage detection threshold — low range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                                                                                                                            | V <sub>LVDL</sub>  | 2.48<br>2.54                                                                                     | 2.56<br>2.62     | 2.64<br>2.7              | v     |

#### Table 3-6. DC Characteristics

### MC9S08AC128 MCU Series Data Sheet, Rev. 4

**Chapter 3 Electrical Characteristics and Timing Specifications**

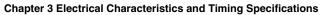

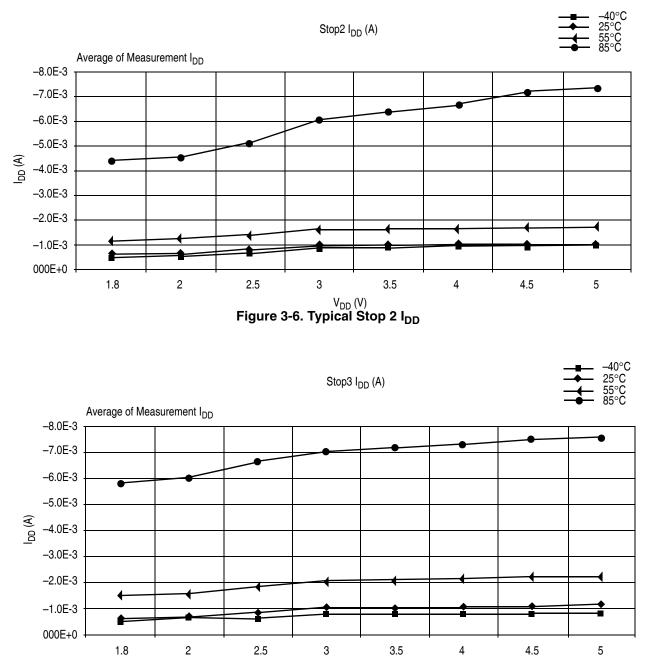

# 3.7 Supply Current Characteristics

Table 3-7. Supply Current Characteristics

| Num | с | Parameter                                                          | Symbol                | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max              | Unit     | Temp<br>(°C)                |

|-----|---|--------------------------------------------------------------------|-----------------------|------------------------|------------------|------------------|----------|-----------------------------|

|     | _ | Run supply current <sup>2</sup> measured at                        |                       | 5                      | 1.1              | 1.4 <sup>3</sup> |          |                             |

| 1   | С | (CPU clock = 2 MHz, $f_{Bus} = 1$ MHz)                             | RI <sub>DD</sub>      | 3                      | 1.0              | 1.2              | mA       | –40 to 125°C                |

|     | с | Run supply current <sup>4</sup> measured at                        |                       | 5                      | 6.7              | 8.0 <sup>5</sup> |          |                             |

| 2   | C | (CPU clock = 16 MHz, f <sub>Bus</sub> = 8 MHz)                     | RI <sub>DD</sub>      | 3                      | 6                | 7.5              | mA       | –40 to 125°C                |

|     |   | Stop2 mode supply current                                          |                       | 5                      | 1.0              | 25<br>160        | μA       | –40 to 85°C<br>–40 to 125°C |

| 3   | С |                                                                    |                       |                        | 1.0              |                  |          |                             |

|     |   |                                                                    | S2I <sub>DD</sub>     | 3                      | 0.8              | 23<br>150        | μA       | −40 to 85°C −40 to 125°C    |

|     |   |                                                                    |                       | 5                      |                  | 27               | μA       | –40 to 85°C                 |

| 4   | с | Stop3 mode supply current                                          |                       |                        | 1.2              | 180 <sup>3</sup> | port     | –40 to 125°C                |

|     | - |                                                                    | S3I <sub>DD</sub>     | 3                      |                  | 25               | μA       | -40 to 85°C                 |

|     |   |                                                                    |                       |                        | 1.0              | 170              | •        | –40 to 125°C                |

|     |   |                                                                    |                       | 5                      | 300              | 500<br>500       | nA       | –40 to 85°C<br>–40 to 125°C |

| 5   | С | RTI adder to stop2 or stop3 <sup>6</sup>                           | S23I                  |                        |                  |                  |          |                             |

|     |   |                                                                    | S23I <sub>ddrti</sub> | 3                      | 300              | 500<br>500       | nA       | −40 to 85°C −40 to 125°C    |

|     |   |                                                                    |                       | 5                      | 110              | 180              | μA       | -40 to 85°C                 |

| 6   | С | LVD adder to stop3 (LVDE = LVDSE = 1)                              | S3I                   |                        |                  | 180              |          | –40 to 125°C                |

|     |   |                                                                    | S3I <sub>DDLVD</sub>  | 3                      | 90               | 160<br>160       | μA       | −40 to 85°C −40 to 125°C    |

|     |   |                                                                    |                       |                        |                  |                  |          |                             |

| 7   | С | Adder to stop3 for oscillator enabled <sup>7</sup><br>(OSCSTEN =1) | S3I <sub>DDOSC</sub>  | 5,3                    | 5                | 8<br>8           | μΑ<br>μΑ | –40 to 85°C<br>–40 to 125°C |

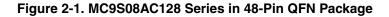

<sup>1</sup> Typical values are based on characterization data at 25°C unless otherwise stated. See Figure 3-5 through Figure 3-7 for typical curves across voltage/temperature.

<sup>2</sup> All modules except ADC active, ICG configured for FBE, and does not include any dc loads on port pins

<sup>3</sup> Every unit tested to this parameter. All other values in the Max column are guaranteed by characterization.

<sup>4</sup> All modules except ADC active, ICG configured for FBE, and does not include any dc loads on port pins

<sup>5</sup> Every unit tested to this parameter. All other values in the Max column are guaranteed by characterization.

<sup>6</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode. Wait mode typical is 560  $\mu$ A at 3 V with f<sub>Bus</sub> = 1 MHz.

<sup>7</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768kHz crystal, low power mode (HGO = 0), clock monitor disabled (LOCD = 1).

**Chapter 3 Electrical Characteristics and Timing Specifications**

Note: External clock is square wave supplied by function generator. For FEE mode, external reference frequency is 4 MHz Figure 3-5. Typical Run I<sub>DD</sub> for FBE and FEE Modes, I<sub>DD</sub> vs. V<sub>DD</sub>

V<sub>DD</sub> (V) Figure 3-7. Typical Stop3 I<sub>DD</sub>

MC9S08AC128 Series Data Sheet, Rev. 4

# 3.8 ADC Characteristics

| Table 3-8. 5 Volt 10-bit ADC | <b>Operating Conditions</b> |

|------------------------------|-----------------------------|

|------------------------------|-----------------------------|

| Characteristic                              | Conditions                                                                  | Symb                | Min               | Typ <sup>1</sup>  | Max               | Unit    |

|---------------------------------------------|-----------------------------------------------------------------------------|---------------------|-------------------|-------------------|-------------------|---------|

| Supply voltage                              | Absolute                                                                    | V <sub>DDAD</sub>   | 2.7               | _                 | 5.5               | V       |

| Supply voltage                              | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDAD</sub> ) <sup>2</sup> | $\Delta V_{DDAD}$   | -100              | 0                 | +100              | mV      |

| Ground voltage                              | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSAD</sub> ) <sup>2</sup> | ΔV <sub>SSAD</sub>  | -100              | 0                 | +100              | mV      |

| Ref voltage high                            |                                                                             | V <sub>REFH</sub>   | 2.7               | V <sub>DDAD</sub> | V <sub>DDAD</sub> | V       |

| Ref voltage low                             |                                                                             | V <sub>REFL</sub>   | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V       |

| Supply current                              | Stop, reset, module off                                                     | I <sub>DDAD</sub>   | _                 | 0.011             | 1                 | μA      |

| Input voltage                               |                                                                             | V <sub>ADIN</sub>   | V <sub>REFL</sub> | _                 | V <sub>REFH</sub> | V       |

| Input capacitance                           |                                                                             | C <sub>ADIN</sub>   | _                 | 4.5               | 5.5               | pF      |

| Input resistance                            |                                                                             | R <sub>ADIN</sub>   | _                 | 3                 | 5                 | kΩ      |

| Analog source resistance<br>External to MCU | 10-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz         | R <sub>AS</sub>     |                   |                   | 5<br>10           | kΩ      |

|                                             | 8-bit mode (all valid f <sub>ADCK</sub> )                                   |                     |                   | _                 | 10                |         |

|                                             | High speed (ADLPC = 0)                                                      | 4                   | 0.4               |                   | 8.0               | N 41 1- |

| ADC conversion clock frequency              | Low power (ADLPC = 1)                                                       | f <sub>ADCK</sub>   | 0.4               | _                 | 4.0               | MHz     |

| Temp Sensor                                 | -40°C to 25°C                                                               | m                   |                   | 3.266             | —                 | mV/∘    |

| Slope                                       | 25°C to 125°C                                                               |                     | _                 | 3.638             | —                 | С       |

| Temp Sensor<br>Voltage                      | 25°C                                                                        | V <sub>TEMP25</sub> | _                 | 1.396             | _                 | V       |

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 5.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> dc potential difference.

| Characteristic                                        | Conditions                | С        | Symb               | Min        | Typ <sup>1</sup> | Max  | Unit             |

|-------------------------------------------------------|---------------------------|----------|--------------------|------------|------------------|------|------------------|

| Supply current<br>ADLPC = 1<br>ADLSMP = 1<br>ADCO = 1 |                           | Т        | I <sub>DDAD</sub>  |            | 133              |      | μΑ               |

| Supply current<br>ADLPC = 1<br>ADLSMP = 0<br>ADCO = 1 |                           | Т        | I <sub>DDAD</sub>  | _          | 218              | _    | μΑ               |

| Supply current<br>ADLPC = 0<br>ADLSMP = 1<br>ADCO = 1 |                           | Т        | I <sub>DDAD</sub>  | _          | 327              | _    | μΑ               |

| Supply current                                        |                           | Т        | I <sub>DDAD</sub>  | —          | 582              | _    | μA               |

| ADLPC = 0<br>ADLSMP = 0<br>ADCO = 1                   | $V_{DDAD} \le 5.5 V$      | Р        |                    | _          | _                | 1    | mA               |

| ADC asynchronous clock source                         | High speed (ADLPC = 0)    | Р        | f <sub>ADACK</sub> | 2          | 3.3              | 5    | MHz              |

| $t_{ADACK} = 1/f_{ADACK}$                             | Low power (ADLPC = 1)     |          |                    | 1.25       | 2                | 3.3  |                  |

| Conversion time                                       | Short sample (ADLSMP = 0) | Р        | t <sub>ADC</sub>   | —          | 20               | _    | ADCK<br>cycles   |

| (Including sample time)                               | Long sample (ADLSMP = 1)  |          |                    | _          | 40               | _    |                  |

| Sample time                                           | Short sample (ADLSMP = 0) | Р        | t <sub>ADS</sub>   | _          | 3.5              | _    | ADCK             |

|                                                       | Long sample (ADLSMP = 1)  |          |                    |            | 23.5             | _    | cycles           |

| Total unadjusted error                                | 10-bit mode               | Р        | E <sub>TUE</sub>   |            | ±1               | ±2.5 | LSB <sup>2</sup> |

| Includes quantization                                 | 8-bit mode                |          |                    | _          | ±0.5             | ±1.0 |                  |

|                                                       | 10-bit mode               | Р        | DNL                | —          | ±0.5             | ±1.0 | LSB <sup>2</sup> |

| Differential non-linearity                            | 8-bit mode                |          |                    | _          | ±0.3             | ±0.5 |                  |

|                                                       | Monotoni                  | city and | d no-missing       | g-codes gu | aranteed         |      |                  |

| Integral non-linearity                                | 10-bit mode               | С        | INL                | —          | ±0.5             | ±1.0 | LSB <sup>2</sup> |

| Integral non-intearity                                | 8-bit mode                |          |                    | _          | ±0.3             | ±0.5 |                  |

| Zero-scale error                                      | 10-bit mode               | Р        | E <sub>ZS</sub>    | —          | ±0.5             | ±1.5 | LSB <sup>2</sup> |

| $V_{ADIN} = V_{SSA}$                                  | 8-bit mode                |          |                    | _          | ±0.5             | ±0.5 |                  |

| Full-scale error                                      | 10-bit mode               | Р        | E <sub>FS</sub>    | _          | ±0.5             | ±1.5 | LSB <sup>2</sup> |

| $V_{ADIN} = V_{DDA}$                                  | 8-bit mode                |          |                    | _          | ±0.5             | ±0.5 |                  |

| Quantization error                                    | 10-bit mode               | D        | EQ                 | _          | —                | ±0.5 | LSB <sup>2</sup> |

|                                                       | 8-bit mode                |          |                    |            |                  | ±0.5 |                  |

Table 3-9. 5 Volt 10-bit ADC Characteristics ( $V_{REFH} = V_{DDAD}$ ,  $V_{REFL} = V_{SSAD}$ )

### 3.9.1 ICG Frequency Specifications

### Table 3-11. ICG Frequency Specifications

### $(V_{DDA} = V_{DDA} \text{ (min) to } V_{DDA} \text{ (max)}, \text{ Temperature Range} = -40 \text{ to } 125^{\circ}\text{C} \text{ Ambient})$

| Num | С | Characteristic                                                                                                                                                         | Symbol                                   | Min                                               | Typ <sup>1</sup> | Max                                                           | Unit                     |

|-----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------|------------------|---------------------------------------------------------------|--------------------------|

|     |   | Oscillator crystal or resonator (REFS = 1)<br>(Fundamental mode crystal or ceramic resonator)<br>Low range<br>High range                                               | flo                                      | 32                                                | _                | 100                                                           | kHz                      |

| 1   |   | High Gain, FBE (HGO = 1,CLKS = 10)<br>High Gain, FEE (HGO = 1,CLKS = 11)<br>Low Power, FBE (HGO = 0, CLKS = 10)<br>Low Power, FEE (HGO = 0, CLKS = 11)                 | fhi_byp<br>fhi_eng<br>flp_byp<br>flp_eng | 1<br>2<br>1<br>2                                  | _                | 16<br>10<br>8<br>8                                            | MHz<br>MHz<br>MHz<br>MHz |

| 2   |   | Input clock frequency (CLKS = 11, REFS = 0)<br>Low range<br>High range                                                                                                 | f <sub>lo</sub><br>f <sub>hi_eng</sub>   | 32<br>2                                           |                  | 100<br>10                                                     | kHz<br>MHz               |

| 3   |   | Input clock frequency (CLKS = 10, REFS = 0)                                                                                                                            | f <sub>Extal</sub>                       | 0                                                 | _                | 40                                                            | MHz                      |

| 4   |   | Internal reference frequency (untrimmed)                                                                                                                               | f <sub>ICGIRCLK</sub>                    | 182.25                                            | 243              | 303.75                                                        | kHz                      |

| 5   |   | Duty cycle of input clock (REFS = 0)                                                                                                                                   | t <sub>dc</sub>                          | 40                                                | _                | 60                                                            | %                        |

| 6   |   | Output clock ICGOUT frequency<br>CLKS = 10, REFS = 0<br>All other cases                                                                                                | ficgout                                  | f <sub>Extal</sub> (min)<br>f <sub>lo</sub> (min) |                  | f <sub>Extal</sub> (max)<br>f <sub>ICGDCLKmax</sub> (<br>max) | MHz                      |

| 7   |   | Minimum DCO clock (ICGDCLK) frequency                                                                                                                                  | f <sub>ICGDCLKmin</sub>                  | 3                                                 |                  |                                                               | MHz                      |

| 8   |   | Maximum DCO clock (ICGDCLK) frequency                                                                                                                                  | f <sub>ICGDCLKmax</sub>                  |                                                   | _                | 40                                                            | MHz                      |

| 9   |   | Self-clock mode (ICGOUT) frequency <sup>2</sup>                                                                                                                        | f <sub>Self</sub>                        | f <sub>ICGDCLKmin</sub>                           |                  | f <sub>ICGDCLKmax</sub>                                       | MHz                      |

| 10  |   | Self-clock mode reset (ICGOUT) frequency                                                                                                                               | f <sub>Self_reset</sub>                  | 5.5                                               | 8                | 10.5                                                          | MHz                      |

| 11  |   | Loss of reference frequency <sup>3</sup><br>Low range<br>High range                                                                                                    | f <sub>LOR</sub>                         | 5<br>50                                           |                  | 25<br>500                                                     | kHz                      |

| 12  |   | Loss of DCO frequency <sup>4</sup>                                                                                                                                     | f <sub>LOD</sub>                         | 0.5                                               |                  | 1.5                                                           | MHz                      |

| 13  |   | Crystal start-up time <sup>5, 6</sup><br>Low range<br>High range                                                                                                       | <sup>t</sup> CSTL<br><sup>t</sup> CSTH   | _                                                 | 430<br>4         |                                                               | ms                       |

| 14  |   | FLL lock time <sup>, 7</sup><br>Low range<br>High range                                                                                                                | t <sub>Lockl</sub><br>t <sub>Lockh</sub> | _                                                 |                  | 2<br>2                                                        | ms                       |

| 15  |   | FLL frequency unlock range                                                                                                                                             | n <sub>Unlock</sub>                      | -4*N                                              |                  | 4*N                                                           | counts                   |

| 16  |   | FLL frequency lock range                                                                                                                                               | n <sub>Lock</sub>                        | -2*N                                              |                  | 2*N                                                           | counts                   |

| 17  |   | ICGOUT period jitter, <sup>, 8</sup> measured at f <sub>ICGOUT</sub> Max<br>Long term jitter (averaged over 2 ms interval)                                             | C <sub>Jitter</sub>                      | _                                                 |                  | 0.2                                                           | % f <sub>ICG</sub>       |

| 18  |   | Internal oscillator deviation from trimmed<br>frequency <sup>9</sup><br>$V_{DD} = 2.7 - 5.5 V$ , (constant temperature)<br>$V_{DD} = 5.0 V \pm 10\%$ , -40° C to 125°C | ACC <sub>int</sub>                       |                                                   | ±0.5<br>±0.5     | ±2<br>±2                                                      | %                        |

<sup>1</sup> Typical values are based on characterization data at  $V_{DD} = 5.0V$ , 25°C unless otherwise stated.

<sup>2</sup> Self-clocked mode frequency is the frequency that the DCO generates when the FLL is open-loop.

**Chapter 3 Electrical Characteristics and Timing Specifications**

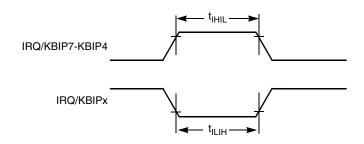

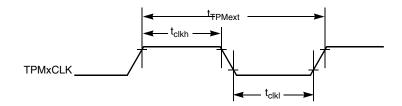

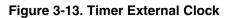

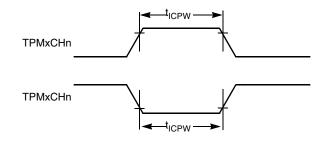

### 3.10.2 Timer/PWM (TPM) Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| Function                  | Symbol              | Min | Мах                 | Unit             |

|---------------------------|---------------------|-----|---------------------|------------------|

| External clock frequency  | f <sub>TPMext</sub> | dc  | f <sub>Bus</sub> /4 | MHz              |

| External clock period     | t <sub>TPMext</sub> | 4   | —                   | t <sub>cyc</sub> |

| External clock high time  | t <sub>clkh</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

| External clock low time   | t <sub>ciki</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

| Input capture pulse width | t <sub>ICPW</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

Table 3-13. TPM Input Timing

**Chapter 3 Electrical Characteristics and Timing Specifications**

Figure 3-14. Timer Input Capture Pulse

## 3.12 FLASH Specifications

This section provides details about program/erase times and program-erase endurance for the Flash memory.

Program and erase operations do not require any special power sources other than the normal V<sub>DD</sub> supply.

| Num | С | Characteristic                                                                                                    | Symbol                  | Min    | Typ <sup>1</sup> | Max               | Unit              |

|-----|---|-------------------------------------------------------------------------------------------------------------------|-------------------------|--------|------------------|-------------------|-------------------|

| 1   | Р | Supply voltage for program/erase                                                                                  | V <sub>prog/erase</sub> | 2.7    |                  | 5.5               | V                 |

| 2   | Р | Supply voltage for read operation                                                                                 | V <sub>Read</sub>       | 2.7    |                  | 5.5               | V                 |

| 3   | Р | Internal FCLK frequency <sup>2</sup>                                                                              | f <sub>FCLK</sub>       | 150    |                  | 200               | kHz               |

| 4   | Р | Internal FCLK period (1/FCLK)                                                                                     | t <sub>Fcyc</sub>       | 5      |                  | 6.67              | μs                |

| 5   | Р | Byte program time (random location) <sup>(2)</sup>                                                                | t <sub>prog</sub>       | 9      |                  |                   | t <sub>Fcyc</sub> |

| 6   | С | Byte program time (burst mode) <sup>(2)</sup>                                                                     | t <sub>Burst</sub>      | 4      |                  |                   | t <sub>Fcyc</sub> |

| 7   | Р | Page erase time <sup>3</sup>                                                                                      | t <sub>Page</sub>       | 4000   |                  |                   | t <sub>Fcyc</sub> |

| 8   | Р | Mass erase time <sup>(2)</sup>                                                                                    | t <sub>Mass</sub>       | 20,000 |                  | t <sub>Fcyc</sub> |                   |

| 9   | с | Program/erase endurance <sup>4</sup><br>T <sub>L</sub> to T <sub>H</sub> = $-40^{\circ}$ C to + 125°C<br>T = 25°C |                         | 10,000 | <br>100,000      |                   | cycles            |

| 10  | С | Data retention <sup>5</sup>                                                                                       | t <sub>D_ret</sub>      | 15     | 100              | _                 | years             |

<sup>1</sup> Typical values are based on characterization data at  $V_{DD} = 5.0 \text{ V}$ , 25°C unless otherwise stated.

<sup>2</sup> The frequency of this clock is controlled by a software setting.

<sup>3</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

<sup>4</sup> Typical endurance for Flash was evaluated for this product family on the 9S12Dx64. For additional information on how Freescale Semiconductor defines typical endurance, please refer to Engineering Bulletin EB619/D, *Typical Endurance for Nonvolatile Memory.*

<sup>5</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines typical data retention, please refer to Engineering Bulletin EB618/D, *Typical Data Retention for Nonvolatile Memory.*

**Chapter 3 Electrical Characteristics and Timing Specifications**

# 3.13 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

## 3.13.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East). For more detailed information concerning the evaluation results, conditions and setup, please refer to the EMC Evaluation Report for this device.

The maximum radiated RF emissions of the tested configuration in all orientations are less than or equal to the reported emissions levels.

| Parameter                         | Symbol              | Conditions                                                          | Frequency      | f <sub>OSC</sub> /f <sub>BUS</sub> | Level <sup>1</sup><br>(Max) | Unit |

|-----------------------------------|---------------------|---------------------------------------------------------------------|----------------|------------------------------------|-----------------------------|------|

|                                   | V <sub>RE_TEM</sub> | $V_{DD} = 5.0 V$<br>$T_A = +25^{\circ}C$<br>package type<br>80 LQFP | 0.15 – 50 MHz  | 32kHz crystal                      | 30                          | dBμV |

|                                   |                     |                                                                     | 50 – 150 MHz   | 20MHz Bus                          | 32                          |      |

| Radiated emissions,               |                     |                                                                     | 150 – 500 MHz  |                                    | 19                          |      |

| electric field and magnetic field |                     |                                                                     | 500 – 1000 MHz |                                    | 7                           |      |

|                                   |                     |                                                                     | IEC Level      |                                    | l <sup>2</sup>              | —    |

|                                   |                     |                                                                     | SAE Level      |                                    | l <sup>2</sup>              | —    |

Table 3-16. Radiated Emissions

<sup>1</sup> Data based on laboratory test results.

<sup>2</sup> IEC and SAE Level Maximums: I=36 dBuV.

# Chapter 4 Ordering Information and Mechanical Drawings

# 4.1 Ordering Information

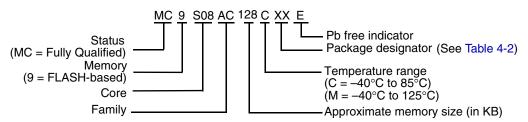

This section contains ordering numbers for MC9S08AC128 Series devices. See below for an example of the device numbering system.

| Device Number | Memory |     | Available Packages <sup>1</sup>  |  |

|---------------|--------|-----|----------------------------------|--|

| Device Number | FLASH  | RAM | Туре                             |  |

| MC9S08AC128   | 128K   | 8K  | 80 LQFP, 64 QFP, 48-QFN, 44-LQFP |  |

| MC9S08AC96    | 96K    | 6K  | 80 LQFP, 64 QFP, 48-QFN, 44-LQFP |  |

### Table 4-1. Device Numbering System

<sup>1</sup> See Table 4-2 for package information.

# 4.2 Orderable Part Numbering System

## 4.3 Mechanical Drawings

Table 4-2 provides the available package types and their document numbers. The latest package outline/mechanical drawings are available on the MC9S08AC128 Series Product Summary pages at http://www.freescale.com.

To view the latest drawing, either:

- Click on the appropriate link in Table 4-2, or

- Open a browser to the Freescale<sup>®</sup> website (http://www.freescale.com), and enter the appropriate document number (from Table 4-2) in the "Enter Keyword" search box at the top of the page.

| Pin Count | Туре | Designator | Document No. |

|-----------|------|------------|--------------|

| 80        | LQFP | LK         | 98ASS23237W  |

| 64        | QFP  | FU         | 98ASB42844B  |

| 48        | QFN  | FT         | 98ARH99048A  |

| 44        | LQFP | FG         | 98ASS23225W  |

### Table 4-2. Package Information

Chapter 4 Ordering Information and Mechanical Drawings

# Chapter 5 Revision History

To provide the most up-to-date information, the version of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                  |  |  |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                  | 9/2008           | Initial release of a separate data sheet and reference manual. Removed PTH7, clarified SPI as one full and one master-only, added missing RoHS logo, updated back cover addresses, and incorporated general release edits and updates. Added some finalized electrical characteristics. |  |  |

| 2                  | 6/2009           | Added the parameter "Bandgap Voltage Reference" in Table 3-6<br>Updated Section 3.13, "EMC Performance" and corrected Table 3-16.<br>Updated disclaimer page.                                                                                                                           |  |  |

| 3                  | 9/2010           | Added 48-pin QFN package information.                                                                                                                                                                                                                                                   |  |  |

| 4                  | 8/2011           | Updated the t <sub>RTI</sub> in the Table 3-12.<br>Updated the RI <sub>DD</sub> in the Table 3-7.                                                                                                                                                                                       |  |  |