Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

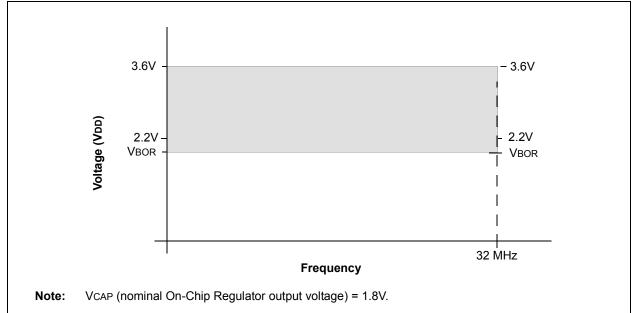

| Speed                      | 32MHz                                                                           |

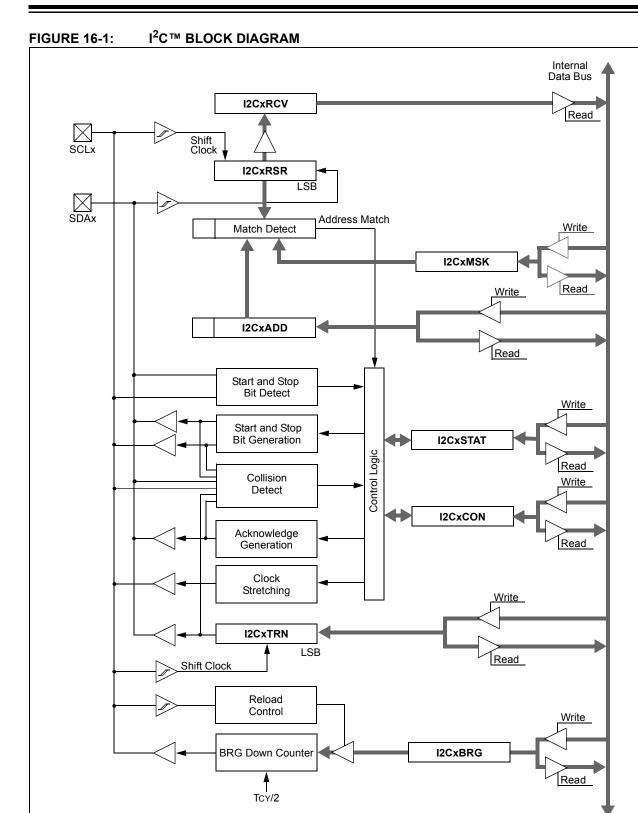

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128da106t-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **High-Performance CPU**

- Modified Harvard Architecture

- Up to 16 MIPS Operation at 32 MHz

- 8 MHz Internal Oscillator

- 17-Bit x 17-Bit Single-Cycle Hardware Multiplier

- 32-Bit by 16-Bit Hardware Divider

- 16 x 16-Bit Working Register Array

- C Compiler Optimized Instruction Set Architecture with Flexible Addressing modes

- Linear Program Memory Addressing, up to 12 Mbytes

- Data Memory Addressing, up to 16 Mbytes:

- 2K SFR space

- 30K linear data memory

- 66K extended data memory

- Remaining (from 16 Mbytes) memory (external) can be accessed using extended data Memory (EDS) and EPMP (EDS is divided into 32-Kbyte pages)

- Two Address Generation Units for Separate Read and Write Addressing of Data Memory

### **Power Management:**

- On-Chip Voltage Regulator of 1.8V

- Switch between Clock Sources in Real Time

- Idle, Sleep and Doze modes with Fast Wake-up and Two-Speed Start-up

- + Run Mode: 800  $\mu\text{A}/\text{MIPS},$  3.3V Typical

- + Sleep mode Current Down to 20  $\mu\text{A},$  3.3V Typical

- Standby Current with 32 kHz Oscillator: 22  $\mu\text{A},$  3.3V Typical

### Analog Features:

- 10-Bit, up to 24-Channel Analog-to-Digital (A/D) Converter at 500 ksps:

- Operation is possible in Sleep mode

- Band gap reference input feature

- Three Analog Comparators with Programmable Input/Output Configuration

- Charge Time Measurement Unit (CTMU):

- Supports capacitive touch sensing for touch screens and capacitive switches

- Minimum time measurement setting at 100 ps

- Available LVD Interrupt VLVD Level

### **Special Microcontroller Features:**

- Operating Voltage Range of 2.2V to 3.6V

- 5.5V Tolerant Input (digital pins only)

- Configurable Open-Drain Outputs on Digital I/O

Ports

- High-Current Sink/Source (18 mA/18 mA) on all I/O Ports

- Selectable Power Management modes:

Sleep, Idle and Doze modes with fast wake-up

- Fail-Safe Clock Monitor (FSCM) Operation:

- Detects clock failure and switches to on-chip, FRC oscillator

- On-Chip LDO Regulator

- Power-on Reset (POR) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Flexible Watchdog Timer (WDT) with On-Chip Low-Power RC Oscillator for Reliable Operation

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and In-Circuit Debug (ICD) via 2 Pins

- JTAG Boundary Scan Support

- Flash Program Memory:

- 10,000 erase/write cycle endurance (minimum)

- 20-year data retention minimum

- Selectable write protection boundary

- Self-reprogrammable under software control

- Write protection option for Configuration Words

| TABLE     | 4-9: | OUT                                   | ГРИТ С | OMPA     | RE REG  | ISTER I | MAP     |        |              |                |             |        |          |          |          |          |          |               |

|-----------|------|---------------------------------------|--------|----------|---------|---------|---------|--------|--------------|----------------|-------------|--------|----------|----------|----------|----------|----------|---------------|

| File Name | Addr | Bit 15                                | Bit 14 | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8        | Bit 7          | Bit 6       | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| OC1CON1   | 0190 | —                                     | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1       | ENFLT0         | OCFLT2      | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2   | 0192 | FLTMD                                 | FLTOUT | FLTTRIEN | OCINV   |         | DCB1    | DCB0   | OC32         | OCTRIG         | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS     | 0194 |                                       |        |          |         |         |         |        | Output Comp  | are 1 Seconda  | ny Register |        |          |          |          |          |          | 0000          |

| OC1R      | 0196 |                                       |        |          |         |         |         |        | Output       | Compare 1 Re   | gister      |        |          |          |          |          |          | 0000          |

| OC1TMR    | 0198 |                                       |        |          |         |         |         |        | Output Compa | are 1 Timer Va | ue Register |        |          |          |          |          |          | xxxx          |

| OC2CON1   | 019A | _                                     | —      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1       | ENFLT0         | OCFLT2      | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2   | 019C | FLTMD                                 | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32         | OCTRIG         | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS     | 019E |                                       |        |          |         |         |         |        | Output Comp  | are 2 Seconda  | ny Register |        |          |          |          |          |          | 0000          |

| OC2R      | 01A0 |                                       |        |          |         |         |         |        | Output       | Compare 2 Re   | gister      |        |          |          |          |          |          | 0000          |

| OC2TMR    | 01A2 |                                       |        |          |         |         |         |        | Output Compa | are 2 Timer Va | ue Register |        |          |          |          |          |          | xxxx          |

| OC3CON1   | 01A4 | _                                     | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1       | ENFLT0         | OCFLT2      | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2   | 01A6 | FLTMD                                 | FLTOUT | FLTTRIEN | OCINV   | _       | DCB1    | DCB0   | OC32         | OCTRIG         | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS     | 01A8 |                                       |        |          |         |         |         |        | Output Comp  | are 3 Seconda  | ny Register |        |          |          |          |          |          | 0000          |

| OC3R      | 01AA |                                       |        |          |         |         |         |        | Output       | Compare 3 Re   | gister      |        |          |          |          |          |          | 0000          |

| OC3TMR    | 01AC | Output Compare 3 Timer Value Register |        |          |         |         | xxxx    |        |              |                |             |        |          |          |          |          |          |               |

| OC4CON1   | 01AE | —                                     | —      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1       | ENFLT0         | OCFLT2      | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2   | 01B0 | FLTMD                                 | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32         | OCTRIG         | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS     | 01B2 |                                       |        |          |         |         |         |        | Output Comp  | are 4 Seconda  | ny Register |        |          |          |          |          |          | 0000          |

| OC4R      | 01B4 |                                       |        |          |         |         |         |        | Output       | Compare 4 Re   | gister      |        |          |          |          |          |          | 0000          |

| OC4TMR    | 01B6 |                                       |        |          |         |         |         |        | Output Compa | are 4 Timer Va | ue Register |        |          |          |          |          |          | xxxx          |

| OC5CON1   | 01B8 | _                                     | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1       | ENFLT0         | OCFLT1      | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC5CON2   | 01BA | FLTMD                                 | FLTOUT | FLTTRIEN | OCINV   | —       | DCB1    | DCB0   | OC32         | OCTRIG         | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC5RS     | 01BC |                                       |        |          |         |         |         |        | Output Comp  | are 5 Seconda  | ny Register |        |          |          |          |          |          | 0000          |

| OC5R      | 01BE |                                       |        |          |         |         |         |        | Output       | Compare 5 Re   | gister      |        |          |          |          |          |          | 0000          |

| OC5TMR    | 01C0 |                                       |        |          |         |         |         |        | Output Compa | are 5 Timer Va | ue Register |        |          |          |          |          |          | xxxx          |

| OC6CON1   | 01C2 | _                                     | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1       | ENFLT0         | OCFLT2      | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC6CON2   | 01C4 | FLTMD                                 | FLTOUT | FLTTRIEN | OCINV   | _       | DCB1    | DCB0   | OC32         | OCTRIG         | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC6RS     | 01C6 |                                       |        |          |         |         |         |        | Output Comp  | are 6 Seconda  | ny Register |        |          |          |          |          |          | 0000          |

| OC6R      | 01C8 |                                       |        |          |         |         |         |        | Output       | Compare 6 Re   | gister      |        |          |          |          |          |          | 0000          |

| OC6TMR    | 01CA |                                       |        |          |         |         |         |        | Output Compa | are 6 Timer Va | ue Register |        |          |          |          |          |          | xxxx          |

| OC7CON1   | 01CC | —                                     | _      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1       | ENFLT0         | OCFLT2      | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC7CON2   | 01CE | FLTMD                                 | FLTOUT | FLTTRIEN | OCINV   | _       | DCB1    | DCB0   | OC32         | OCTRIG         | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC7RS     | 01D0 |                                       |        |          |         |         |         |        | Output Comp  | are 7 Seconda  | ry Register |        |          |          |          |          |          | 0000          |

| OC7R      | 01D2 |                                       |        |          |         |         |         |        | Output       | Compare 7 Re   | gister      |        |          |          |          |          |          | 0000          |

| OC7TMR    | 01D4 |                                       |        |          |         |         |         |        | Output Compa | are 7 Timer Va | ue Register |        |          |          |          |          |          | xxxx          |

DS39969B-page 55

## TABLE 4-30: PERIPHERAL PIN SELECT REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|--------|--------|--------|--------|--------|--------|---------------|

| RPINR0       | 0680 | _      | _      | INT1R5  | INT1R4  | INT1R3  | INT1R2  | INT1R1  | INT1R0  | _     | —     | —      | —      | _      | _      | —      | _      | 3F00          |

| RPINR1       | 0682 | _      | _      | INT3R5  | INT3R4  | INT3R3  | INT3R2  | INT3R1  | INT3R0  | _     |       | INT2R5 | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 | 3F3F          |

| RPINR2       | 0684 | _      |        | _       |         |         |         |         | _       | _     |       | INT4R5 | INT4R4 | INT4R3 | INT4R2 | INT4R1 | INT4R0 | 003F          |

| RPINR3       | 0686 | —      | _      | T3CKR5  | T3CKR4  | T3CKR3  | T3CKR2  | T3CKR1  | T3CKR0  | —     | —     | T2CKR5 | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 | 3F3F          |

| RPINR4       | 0688 | _      | _      | T5CKR5  | T5CKR4  | T5CKR3  | T5CKR2  | T5CKR1  | T5CKR0  | _     | _     | T4CKR5 | T4CKR4 | T4CKR3 | T4CKR2 | T4CKR1 | T4CKR0 | 3F3F          |

| RPINR7       | 068E | _      | _      | IC2R5   | IC2R4   | IC2R3   | IC2R2   | IC2R1   | IC2R0   | _     | _     | IC1R5  | IC1R4  | IC1R3  | IC1R2  | IC1R1  | IC1R0  | 3F3F          |

| RPINR8       | 0690 | _      | _      | IC4R5   | IC4R4   | IC4R3   | IC4R2   | IC4R1   | IC4R0   | _     | _     | IC3R5  | IC3R4  | IC3R3  | IC3R2  | IC3R1  | IC3R0  | 3F3F          |

| RPINR9       | 0692 | _      | _      | IC6R5   | IC6R4   | IC6R3   | IC6R2   | IC6R1   | IC6R0   | _     | _     | IC5R5  | IC5R4  | IC5R3  | IC5R2  | IC5R1  | IC5R0  | 3F3F          |

| RPINR10      | 0694 | —      | _      | IC8R5   | IC8R4   | IC8R3   | IC8R2   | IC8R1   | IC8R0   | —     | _     | IC7R5  | IC7R4  | IC7R3  | IC7R2  | IC7R1  | IC7R0  | 3F3F          |

| RPINR11      | 0696 | —      | _      | OCFBR5  | OCFBR4  | OCFBR3  | OCFBR2  | OCFBR1  | OCFBR0  | —     | —     | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 | 3F3F          |

| RPINR15      | 069E | _      |        | IC9R5   | IC9R4   | IC9R3   | IC9R2   | IC9R1   | IC9R0   |       | _     | _      | _      | _      | —      | —      | —      | 3F00          |

| RPINR17      | 06A2 | _      |        | U3RXR5  | U3RXR4  | U3RXR3  | U3RXR2  | U3RXR1  | U3RXR0  |       | _     | —      | —      | —      | —      | —      | —      | 3F00          |

| RPINR18      | 06A4 | _      | _      | U1CTSR5 | U1CTSR4 | U1CTSR3 | U1CTSR2 | U1CTSR1 | U1CTSR0 | _     | _     | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 | 3F3F          |

| RPINR19      | 06A6 | _      |        | U2CTSR5 | U2CTSR4 | U2CTSR3 | U2CTSR2 | U2CTSR1 | U2CTSR0 |       | _     | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 | 3F3F          |

| RPINR20      | 06A8 | _      |        | SCK1R5  | SCK1R4  | SCK1R3  | SCK1R2  | SCK1R1  | SCK1R0  |       | _     | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 | 3F3F          |

| RPINR21      | 06AA | _      | _      | U3CTSR5 | U3CTSR4 | U3CTSR3 | U3CTSR2 | U3CTSR1 | U3CTSR0 | _     | _     | SS1R5  | SS1R4  | SS1R3  | SS1R2  | SS1R1  | SS1R0  | 3F3F          |

| RPINR22      | 06AC | —      | —      | SCK2R5  | SCK2R4  | SCK2R3  | SCK2R2  | SCK2R1  | SCK2R0  | —     | _     | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 | 3F3F          |

| RPINR23      | 06AE | _      | _      | —       | _       | _       | —       | —       | —       |       |       | SS2R5  | SS2R4  | SS2R3  | SS2R2  | SS2R1  | SS2R0  | 003F          |

| RPINR27      | 06B6 | —      | _      | U4CTSR5 | U4CTSR4 | U4CTSR3 | U4CTSR2 | U4CTSR1 | U4CTSR0 |       | —     | U4RXR5 | U4RXR4 | U4RXR3 | U4RXR2 | U4RXR1 | U4RXR0 | 3F3F          |

| RPINR28      | 06B8 | _      | _      | SCK3R5  | SCK3R4  | SCK3R3  | SCK3R2  | SCK3R1  | SCK3R0  |       |       | SDI3R5 | SDI3R4 | SDI3R3 | SDI3R2 | SDI3R1 | SDI3R0 | 3F3F          |

| RPINR29      | 06BA | _      | _      | _       | _       | _       | _       | _       | _       | _     | _     | SS3R5  | SS3R4  | SS3R3  | SS3R2  | SS3R1  | SS3R0  | 003F          |

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note

1:

Bits are unimplemented in 64-pin devices; read as '0'.

### TABLE 4-31: GRAPHICS REGISTER MAP

| File Name | Addr | Bit 15                                          | Bit 14   | Bit 13          | Bit 12                                      | Bit 11            | Bit 10                                                           | Bit 9        | Bit 8            | Bit 7           | Bit 6         | Bit 5          | Bit 4            | Bit 3           | Bit 2           | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|-------------------------------------------------|----------|-----------------|---------------------------------------------|-------------------|------------------------------------------------------------------|--------------|------------------|-----------------|---------------|----------------|------------------|-----------------|-----------------|----------|----------|---------------|

| G1CMDL    | 0700 |                                                 |          |                 |                                             |                   |                                                                  | Graph        | ics Command F    | Register<15:0>  | ,             |                |                  |                 |                 |          |          | 0000          |

| G1CMDH    | 0702 |                                                 |          |                 |                                             |                   |                                                                  | Graphi       | cs Command F     | Register<31:16  | >             |                |                  |                 |                 |          |          | 0000          |

| G1CON1    | 0704 | G1EN                                            | _        | G1SIDL          | GCMDWMK4                                    | GCMDWMK3          | GCMDWMK2                                                         | GCMDWMK1     | GCMDWMK0         | PUBPP2          | PUBPP1        | PUBPP0         | GCMDCNT4         | GCMDCNT3        | GCMDCNT2        | GCMDCNT1 | GCMDCNT0 | 0000          |

| G1STAT    | 0706 | PUBUSY                                          | _        |                 | _                                           | _                 | -                                                                | _            | _                | IPUBUSY         | RCCBUSY       | CHRBUSY        | VMRGN            | HMRGN           | CMDLV           | CMDFUL   | CMDMPT   | 0000          |

| G1IE      | 0708 | PUIE                                            |          |                 | _                                           | _                 |                                                                  | _            | _                | IPUIE           | RCCIE         | CHRIE          | VMRGNIE          | HMRGNIE         | CMDLVIE         | CMDFULIE | CMDMPTIE | 0000          |

| G1IR      | 070A | PUIF                                            | -        |                 | —                                           | —                 |                                                                  | —            | —                | IPUIF           | RCCIF         | CHRIF          | VMRGNIF          | HMRGNIF         | CMDLVIF         | CMDFULIF | CMDMPTIF | 0000          |

| G1W1ADRL  | 070C |                                                 |          |                 |                                             |                   |                                                                  | GPU Work A   | Area 1 Start Ado | dress Register∙ | <15:0>        |                |                  |                 |                 |          |          | 0000          |

| G1W1ADRH  | 070E | —                                               | —        | -               | -                                           | - <u> </u>        |                                                                  |              |                  |                 |               |                | 0000             |                 |                 |          |          |               |

| G1W2ADRL  | 0710 | GPU Work Area 2 Start Address Register<15:0> 00 |          |                 |                                             |                   |                                                                  |              |                  | 0000            |               |                |                  |                 |                 |          |          |               |

| G1W2ADRH  | 0712 | —                                               | _        | —               | —                                           | —                 | _                                                                | _            | —                |                 |               | GPU Wo         | rk Area 2 Star   | Address Regi    | ster<23:16>     |          |          | 0000          |

| G1PUW     | 0714 | —                                               | _        | —               | —                                           | —                 |                                                                  |              |                  |                 | GPU Wor       | k Area Width   | Register         |                 |                 |          |          | 0000          |

| G1PUH     | 0716 | _                                               | —        | _               | _                                           | _                 |                                                                  |              |                  |                 | GPU Wor       | k Area Heigh   | t Register       |                 |                 |          |          | 0000          |

| G1DPADRL  | 0718 |                                                 |          |                 | Display Buffer Start Address Register<15:0> |                   |                                                                  |              |                  |                 |               | 0000           |                  |                 |                 |          |          |               |

| G1DPADRH  | 071A | _                                               | —        | _               | —                                           | _                 | —         —         Display Buffer Start Address Register<23:16> |              |                  |                 |               |                | 0000             |                 |                 |          |          |               |

| G1DPW     | 071C | —                                               | _        | _               | —                                           | —                 |                                                                  |              |                  |                 | Display F     | Frame Width    | Register         |                 |                 |          |          | 0000          |

| G1DPH     | 071E | —                                               | _        | _               | —                                           | —                 |                                                                  |              |                  |                 | Display F     | rame Height    | Register         |                 |                 |          |          | 0000          |

| G1DPWT    | 0720 | —                                               | _        | _               | —                                           | —                 |                                                                  |              |                  |                 | Display       | Total Width F  | Register         |                 |                 |          |          | 0000          |

| G1DPHT    | 0722 | —                                               | —        | —               | —                                           | —                 |                                                                  |              |                  |                 | Display       | Total Height F | Register         |                 |                 |          |          | 0000          |

| G1CON2    | 0724 | DPGWDTH1                                        | DPGWDTH0 | DPSTGER1        | DPSTGER0                                    | _                 | _                                                                | DPTEST1      | DPTEST0          | DPBPP2          | DPBPP1        | DPBPP0         | —                | —               | DPMODE2         | DPMODE1  | DPMODE0  | 0000          |

| G1CON3    | 0726 | —                                               | —        | —               | —                                           | —                 | —                                                                | DPPINOE      | DPPOWER          | DPCLKPOL        | DPENPOL       | DPVSPOL        | DPHSPOL          | DPPWROE         | DPENOE          | DPVSOE   | DPHSOE   | 0000          |

| G1ACTDA   | 0728 |                                                 |          | Number of       | Lines Before th                             | ne First Active L | ine Register                                                     |              |                  |                 |               | Number of      | Pixels Before t  | he First Active | Plxel Register  |          |          | 0000          |

| G1HSYNC   | 072A |                                                 |          | HSYN            | IC Pulse-Width                              | Configuration F   | Register                                                         |              |                  |                 |               | HSYN           | IC Start Delay   | Configuration   | Register        |          |          | 0000          |

| G1VSYNC   | 072C |                                                 |          | VSYN            | IC Pulse-Width                              | Configuration F   | Register                                                         |              |                  |                 |               | VSYN           | IC Start Delay   | Configuration   | Register        |          |          | 0000          |

| G1DBLCON  | 072E |                                                 |          | ical Blanking S | Start to First Dis                          | played Line Co    | nfiguration Reg                                                  |              | 1                |                 | Horizo        | ntal Blanking  | Start to First D | Displayed Line  | Configuration F | Regsiter |          | 0000          |

| G1CLUT    | 0730 | CLUTEN                                          | CLUTBUSY | —               | _                                           | _                 | —                                                                | CLUTTRD      | CLUTRWEN         |                 |               | Color Lo       | ook-Up Table N   | Memory Addres   | ss Register     |          |          | 0000          |

| G1CLUTWR  | 0732 |                                                 |          |                 |                                             |                   |                                                                  |              | p Table Memor    |                 | •             |                |                  |                 |                 |          |          | 0000          |

| G1CLUTRD  | 0734 |                                                 |          |                 |                                             |                   |                                                                  | Color Look-u | p Table Memor    | y Read Data R   | Register      |                |                  |                 |                 |          |          | 0000          |

| G1MRGN    | 0736 |                                                 |          | V               | ertical Blanking                            | Advance Regis     | ster                                                             |              |                  |                 |               | Но             | rizontal Blanki  | ng Advance Re   | egister         |          |          | 0000          |

| G1CHRX    | 0738 | -                                               | —        | —               | -                                           | _                 |                                                                  |              |                  | Curre           | ent Character | X-Coordinate   | Position Reg     | ister           |                 |          |          | 0000          |

| G1CHRY    | 073A | _                                               | _        | _               | _                                           | _                 |                                                                  |              |                  | Curre           | ent Character | Y-Coordinate   | Position Regi    | ster            |                 |          |          | 0000          |

| G1IPU     | 073C | _                                               | _        | _               | _                                           | _                 | _                                                                | _            | _                | _               | _             | HUFFERR        | BLCKERR          | LENERR          | WRAPERR         | IPUDONE  | BFINAL   | 0000          |

| G1DBEN    | 073E | GDBEN15                                         | GDBEN14  | GDBEN13         | GDBEN12                                     | GDBEN11           | GDBEN10                                                          | GDBEN9       | GDBEN8           | GDBEN7          | GDBEN6        | GDBEN5         | GDBEN4           | GDBEN3          | GDBEN2          | GDBEN1   | GDBEN0   | 0000          |

Legend:

DS39969B-page 69

: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY BLOCK ('C' LANGUAGE CODE)

| <pre>// C example using MPLAB C30     unsigned long progAddr = 0xXXXXXX;     unsigned int offset;</pre> | // Address of row to write                             |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| //Set up pointer to the first memory location t                                                         | o be written                                           |

| TBLPAG = progAddr>>16;                                                                                  | // Initialize PM Page Boundary SFR                     |

| offset = progAddr & 0xFFFF;                                                                             | <pre>// Initialize lower word of address</pre>         |

| <pre>builtin_tblwtl(offset, 0x0000);</pre>                                                              | // Set base address of erase block                     |

|                                                                                                         | // with dummy latch write                              |

| NVMCON = $0 \times 4042$ ;                                                                              | // Initialize NVMCON                                   |

| asm("DISI #5");                                                                                         | <pre>// Block all interrupts with priority &lt;7</pre> |

|                                                                                                         | // for next 5 instructions                             |

| builtin_write_NVM();                                                                                    | // check function to perform unlock                    |

|                                                                                                         | // sequence and set WR                                 |

#### EXAMPLE 5-3: LOADING THE WRITE BUFFERS

| ; Set up NVMCON for row programming operation | 22                                          |

|-----------------------------------------------|---------------------------------------------|

| MOV #0x4001, W0                               | ;                                           |

| MOV W0, NVMCON                                | ,<br>; Initialize NVMCON                    |

| ; Set up a pointer to the first program memo  |                                             |

| ; program memory selected, and writes enable  |                                             |

| MOV #0x0000, W0                               | ;                                           |

| MOV W0, TBLPAG                                | ,<br>; Initialize PM Page Boundary SFR      |

| MOV #0x6000, W0                               | ; An example program memory address         |

| ; Perform the TBLWT instructions to write th  |                                             |

| ; Oth program word                            |                                             |

| MOV #LOW_WORD_0, W2                           | i                                           |

| MOV #HIGH_BYTE_0, W3                          | ;                                           |

| TBLWTL W2, [W0]                               | ,<br>; Write PM low word into program latch |

| TBLWTH W3, [W0++]                             | ; Write PM high byte into program latch     |

| ; lst_program_word                            | , write in high byte into program faton     |

| MOV #LOW_WORD_1, W2                           | i                                           |

| MOV #HIGH BYTE 1, W3                          | ;                                           |

| TBLWTL W2, [W0]                               | ; Write PM low word into program latch      |

| TBLWTH W3, [W0++]                             | ; Write PM high byte into program latch     |

| ; 2nd program word                            |                                             |

| MOV #LOW_WORD_2, W2                           | i                                           |

| MOV #HIGH_BYTE_2, W3                          | i                                           |

| TBLWTL W2, [W0]                               | ; Write PM low word into program latch      |

| TBLWTH W3, [W0++]                             | ; Write PM high byte into program latch     |

| •                                             |                                             |

| •                                             |                                             |

| •                                             |                                             |

| ; 63rd_program_word                           |                                             |

| MOV #LOW_WORD_63, W2                          | ;                                           |

| MOV #HIGH_BYTE_63, W3                         | ;                                           |

| TBLWTL W2, [W0]                               | ; Write PM low word into program latch      |

| TBLWTH W3, [W0]                               | ; Write PM high byte into program latch     |

|                                               |                                             |

#### EXAMPLE 5-4: INITIATING A PROGRAMMING SEQUENCE

| DISI  | #5          | ; Block all interrupts with priority <7 |

|-------|-------------|-----------------------------------------|

|       |             | ; for next 5 instructions               |

| MOV.B | #0x55, W0   |                                         |

| MOV   | W0, NVMKEY  | ; Write the 0x55 key                    |

| MOV.B | #0xAA, W1   | ;                                       |

| MOV   | W1, NVMKEY  | ; Write the OxAA key                    |

| BSET  | NVMCON, #WR | ; Start the programming sequence        |

| NOP   |             | ; Required delays                       |

| NOP   |             |                                         |

| BTSC  | NVMCON, #15 | ; and wait for it to be                 |

| BRA   | \$-2        | ; completed                             |

## REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

| bit 5 | Unimplemented: Read as '0'                                                                                                   |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | INT1IF: External Interrupt 1 Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |

| bit 3 | CNIF: Input Change Notification Interrupt Flag Status bit                                                                    |

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>                          |

| bit 2 | CMIF: Comparator Interrupt Flag Status bit                                                                                   |

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>                          |

| bit 1 | MI2C1IF: Master I2C1 Event Interrupt Flag Status bit                                                                         |

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>                          |

| bit 0 | SI2C1IF: Slave I2C1 Event Interrupt Flag Status bit                                                                          |

|       | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul>                          |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | R/W-0, HS            | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS |

|--------|-----|----------------------|-----------|-----------|-----------|-----------|-----------|

| —      |     | PMPIF <sup>(1)</sup> | OC8IF     | OC7IF     | OC6IF     | OC5IF     | IC6IF     |

| bit 15 |     |                      |           |           |           |           | bit 8     |

| R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS |

|-----------|-----------|-----------|-----|-----|-----|-----------|-----------|

| IC5IF     | IC4IF     | IC3IF     | —   | —   | —   | SPI2IF    | SPF2IF    |

| bit 7     |           |           |     |     |     |           | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------|

| bit 13    | PMPIF: Parallel Master Port Interrupt Flag Status bit <sup>(1)</sup>                                |

|           | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 12    | OC8IF: Output Compare Channel 8 Interrupt Flag Status bit                                           |

|           | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 11    | OC7IF: Output Compare Channel 7 Interrupt Flag Status bit                                           |

|           | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 10    | OC6IF: Output Compare Channel 6 Interrupt Flag Status bit                                           |

|           | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 9     | OC5IF: Output Compare Channel 5 Interrupt Flag Status bit                                           |

|           | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| Note 1:   | Not available in PIC24FJXXXDAX06 devices.                                                           |

### REGISTER 7-31: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1    | R/W-0    | R/W-0    |

|--------|-----|-----|-----|-----|----------|----------|----------|

| —      | —   | —   | —   | —   | MI2C2IP2 | MI2C2IP1 | MI2C2IP0 |

| bit 15 |     |     |     |     |          |          | bit 8    |

| U-0   | R/W-1    | R/W-0    | R/W-0    | U-0 | U-0 | U-0 | U-0   |

|-------|----------|----------|----------|-----|-----|-----|-------|

| —     | SI2C2IP2 | SI2C2IP1 | SI2C2IP0 | —   | —   | —   | —     |

| bit 7 |          |          |          |     |     |     | bit 0 |

| Legend:      |                                                            |                           |                       |                    |  |  |  |  |

|--------------|------------------------------------------------------------|---------------------------|-----------------------|--------------------|--|--|--|--|

| R = Readab   | ole bit                                                    | W = Writable bit          | U = Unimplemented bit | , read as '0'      |  |  |  |  |

| -n = Value a | at POR                                                     | '1' = Bit is set          | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |

|              |                                                            |                           |                       |                    |  |  |  |  |

| bit 15-11    | Unimpleme                                                  | ented: Read as '0'        |                       |                    |  |  |  |  |

| bit 10-8     | MI2C2IP<2                                                  | :0>: Master I2C2 Event In | terrupt Priority bits |                    |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                           |                       |                    |  |  |  |  |

|              | •                                                          |                           |                       |                    |  |  |  |  |

|              |                                                            |                           |                       |                    |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                         |                           |                       |                    |  |  |  |  |

|              |                                                            | rupt source is disabled   |                       |                    |  |  |  |  |

| bit 7        |                                                            | ented: Read as '0'        |                       |                    |  |  |  |  |

| bit 6-4      | SI2C2IP<2:                                                 | 0>: Slave I2C2 Event Inte | errupt Priority bits  |                    |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                           |                       |                    |  |  |  |  |

|              | •                                                          |                           |                       |                    |  |  |  |  |

|              | •                                                          |                           |                       |                    |  |  |  |  |

|              | •<br>001 = Intor                                           | rupt is priority 1        |                       |                    |  |  |  |  |

|              |                                                            | rupt source is disabled   |                       |                    |  |  |  |  |

| bit 3-0      |                                                            | ented: Read as '0'        |                       |                    |  |  |  |  |

| 511 0-0      | Sumpleme                                                   |                           |                       |                    |  |  |  |  |

### 10.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 10.4.1 AVAILABLE PINS

The PPS feature is used with a range of up to 44 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

PIC24FJ256DA210 family devices support a larger number of remappable input only pins than remappable input/output pins. In this device family, there are up to 32 remappable input/output pins, depending on the pin count of the particular device selected; these are numbered, RP0 through RP31. Remappable input only pins are numbered above this range, from RPI32 to RPI43 (or the upper limit for that particular device).

See Table 1-1 for a summary of pinout options in each package offering.

### 10.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals.

PPS is not available for  $l^2C^{TM}$ , change notification inputs, RTCC alarm outputs, EPMP signals, graphics controller signals or peripherals with analog inputs.

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 10.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g., OC, UART transmit) will take priority over general purpose digital functions on a pin, such as EPMP and port I/O. Specialized digital outputs, such as USB functionality, will take priority over PPS outputs on the same pin. The pin diagrams list peripheral outputs in the order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pin selectable peripheral inputs will never take ownership of a pin. The pin's output buffer will be controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in digital mode then the PPS input will operate correctly. If an analog function is enabled on the pin the PPS input will be disabled.

### 10.4.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

### 10.4.3.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral; that is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-8 through Register 10-28). Each register contains two sets of 6-bit fields, with each set associated with one of the pin-selectable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn/RPIn pin with that value to that peripheral. For any given device, the valid range of values for any of the bit fields corresponds to the maximum number of Peripheral Pin Selections supported by the device.

### REGISTER 10-18: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| U-0                                | U-0 | R/W-1 | R/W-1             | R/W-1           | R/W-1           | R/W-1 | R/W-1 |

|------------------------------------|-----|-------|-------------------|-----------------|-----------------|-------|-------|

|                                    | —   | IC9R5 | IC9R4             | IC9R3           | IC9R2           | IC9R1 | IC9R0 |

| bit 15                             |     |       |                   |                 |                 |       | bit 8 |

|                                    |     |       |                   |                 |                 |       |       |

| U-0                                | U-0 | U-0   | U-0               | U-0             | U-0             | U-0   | U-0   |

|                                    | —   | —     |                   | —               | —               | —     | _     |

| bit 7                              |     |       |                   |                 |                 |       | bit C |

|                                    |     |       |                   |                 |                 |       |       |

| Legend:                            |     |       |                   |                 |                 |       |       |

| R = Readable bit W = Writable bit  |     | bit   | U = Unimplem      | ented bit, read | read as '0'     |       |       |

| -n = Value at POR '1' = Bit is set |     |       | '0' = Bit is clea | ired            | x = Bit is unkr | iown  |       |

bit 13-8 IC9R<5:0>: Assign Input Capture 9 (IC9) to Corresponding RPn or RPIn Pin bits

bit 7-0 Unimplemented: Read as '0'

### REGISTER 10-19: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17

| U-0                                | U-0 | R/W-1  | R/W-1                                   | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|------------------------------------|-----|--------|-----------------------------------------|--------|--------|--------|--------|

| —                                  | —   | U3RXR5 | U3RXR4                                  | U3RXR3 | U3RXR2 | U3RXR1 | U3RXR0 |

| bit 15                             |     |        |                                         | •      |        |        | bit 8  |

|                                    |     |        |                                         |        |        |        |        |

| U-0                                | U-0 | U-0    | U-0                                     | U-0    | U-0    | U-0    | U-0    |

| _                                  | —   | —      | —                                       | —      | —      | —      | —      |

| bit 7                              |     |        |                                         |        |        |        | bit 0  |

|                                    |     |        |                                         |        |        |        |        |

| Legend:                            |     |        |                                         |        |        |        |        |

| R = Readable bit W = Writable bit  |     | bit    | U = Unimplemented bit, read as '0'      |        |        |        |        |

| -n = Value at POR '1' = Bit is set |     |        | '0' = Bit is cleared x = Bit is unknown |        |        | nown   |        |

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 U3RXR<5:0>: Assign UART3 Receive (U3RX) to Corresponding RPn or RPIn Pin bits

bit 7-0 Unimplemented: Read as '0'

NOTES:

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 4 **RXINV:** Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode (4 BRG clock cycles per bit)

- 0 = Standard-Speed mode (16 BRG clock cycles per bit)

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Bit Selection bit

- 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

### REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters</li> </ul> |

| bit 5   | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Address Detect mode is enabled</li> <li>If 9-bit mode is not selected, this does not take effect.</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                                                     |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Receiver is Idle</li> <li>0 = Receiver is active</li> </ul>                                                                                                                                                                                                                                                                                                                                   |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                              |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed (clearing a previously set OERR bit (1 → 0 transition); will reset the receiver buffer and the RSR to the empty state</li> </ul>                                                                                                                                                                                 |

| bit 0   | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                                              |

| Note 1: | Value of bit only affects the transmit properties of the module when the $IrDA^{\textcircled{R}}$ encoder is enabled (IREN = 1).                                                                                                                                                                                                                                                                           |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

### 18.7.1 USB OTG MODULE CONTROL REGISTERS

### REGISTER 18-3: U10TGSTAT: USB OTG STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| R-0, HSC | U-0 | R-0, HSC | U-0 | R-0, HSC | R-0, HSC | U-0 | R-0, HSC |

|----------|-----|----------|-----|----------|----------|-----|----------|

| ID       | —   | LSTATE   | —   | SESVD    | SESEND   | —   | VBUSVD   |

| bit 7    |     |          |     |          |          |     | bit 0    |

| Legend:           | U = Unimplemented b | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|---------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit    | HSC = Hardware Setta               | ble/Clearable bit  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | ID: ID Pin State Indicator bit                                                                                                                                                            |

|          | <ul> <li>1 = No plug is attached, or a type B cable has been plugged into the USB receptacle</li> <li>0 = A type A plug has been plugged into the USB receptacle</li> </ul>               |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 5    | LSTATE: Line State Stable Indicator bit                                                                                                                                                   |

|          | <ul> <li>1 = The USB line state (as defined by SE0 and JSTATE) has been stable for the previous 1 ms</li> <li>0 = The USB line state has not been stable for the previous 1 ms</li> </ul> |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 3    | SESVD: Session Valid Indicator bit                                                                                                                                                        |

|          | 1 = The VBUS voltage is above VA_SESS_VLD (as defined in the USB OTG Specification) on the A or<br>B-device                                                                               |

|          | 0 = The VBUS voltage is below VA_SESS_VLD on the A or B-device                                                                                                                            |

| bit 2    | SESEND: B Session End Indicator bit                                                                                                                                                       |

|          | 1 = The VBUS voltage is below VB_SESS_END (as defined in the USB OTG Specification) on the<br>B-device                                                                                    |

|          | 0 = The VBUS voltage is above VB_SESS_END on the B-device                                                                                                                                 |

| bit 1    | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 0    | VBUSVD: A VBUS Valid Indicator bit                                                                                                                                                        |

|          | 1 = The VBUS voltage is above VA_VBUS_VLD (as defined in the USB OTG Specification) on the<br>A-device                                                                                    |

|          | 0 = The VBUS voltage is below VA_VBUS_VLD on the A-device                                                                                                                                 |

| R/W-0           | R/W-0                                                                                                 | R/W-0                                                                        | R/W-0           | U-0            | R/W-0            | R/W-0            | R/W-0 |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------|----------------|------------------|------------------|-------|--|--|--|--|

| CSDIS           | CSP                                                                                                   | CSPTEN                                                                       | BEP             | _              | WRSP             | RDSP             | SM    |  |  |  |  |

| oit 15          |                                                                                                       |                                                                              |                 |                |                  |                  | bi    |  |  |  |  |

|                 |                                                                                                       |                                                                              |                 |                |                  |                  |       |  |  |  |  |

| R/W-0           | R/W-0                                                                                                 | R/W-0                                                                        | U-0             | U-0            | U-0              | U-0              | U-0   |  |  |  |  |

| ACKP            | PTSZ1                                                                                                 | PTSZ0                                                                        | —               | —              |                  | _                | —     |  |  |  |  |

| bit 7           |                                                                                                       |                                                                              |                 |                |                  |                  | bi    |  |  |  |  |

| Legend:         |                                                                                                       |                                                                              |                 |                |                  |                  |       |  |  |  |  |

| R = Readable    | bit                                                                                                   | W = Writable b                                                               | oit             | U = Unimp      | lemented bit, re | ad as '0'        |       |  |  |  |  |

| -n = Value at F | POR                                                                                                   | '1' = Bit is set                                                             |                 | '0' = Bit is   |                  | x = Bit is unkno | own   |  |  |  |  |

|                 |                                                                                                       |                                                                              |                 |                |                  |                  |       |  |  |  |  |

| bit 15          | CSDIS: Chi                                                                                            | p Select x Disab                                                             | le bit          |                |                  |                  |       |  |  |  |  |

|                 | 1 = Disable                                                                                           | the Chip Select                                                              | x functionality | 1              |                  |                  |       |  |  |  |  |

|                 |                                                                                                       | the Chip Select                                                              | ,               |                |                  |                  |       |  |  |  |  |

| bit 14          | •                                                                                                     | Select x Polarity                                                            | bit             |                |                  |                  |       |  |  |  |  |

|                 |                                                                                                       | nigh <u>(PMCS</u> x)<br>ow (PMCSx)                                           |                 |                |                  |                  |       |  |  |  |  |

| bit 13          |                                                                                                       | . ,                                                                          | hla hit         |                |                  |                  |       |  |  |  |  |

|                 |                                                                                                       | CSPTEN: PMCSx Port Enable bit<br>1 = PMCSx port is enabled                   |                 |                |                  |                  |       |  |  |  |  |

|                 |                                                                                                       | port is disabled                                                             |                 |                |                  |                  |       |  |  |  |  |

| oit 12          |                                                                                                       | Select x Nibble/E                                                            |                 | plarity bit    |                  |                  |       |  |  |  |  |

|                 | 1 = Nibble/I                                                                                          | 1 = Nibble/Byte enable active-high (PMBE0, PMBE1)                            |                 |                |                  |                  |       |  |  |  |  |

|                 | 0 = Nibble/                                                                                           | Byte enable acti                                                             | ve-low (PMBE    | 0, PMBE1)      |                  |                  |       |  |  |  |  |

| bit 11          | Unimpleme                                                                                             | ented: Read as '                                                             | 0'              |                |                  |                  |       |  |  |  |  |

| bit 10          | WRSP: Chip Select x Write Strobe Polarity bit                                                         |                                                                              |                 |                |                  |                  |       |  |  |  |  |

|                 |                                                                                                       | odes and Maste                                                               |                 | <u>SM = 0:</u> |                  |                  |       |  |  |  |  |