Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

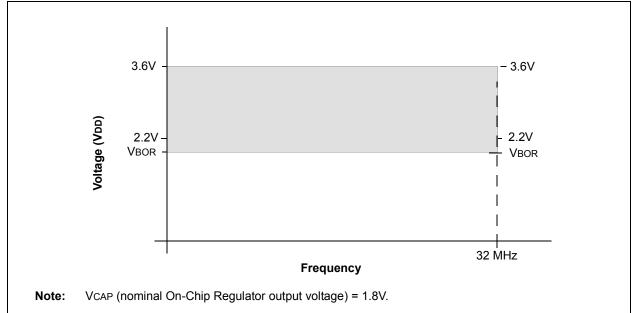

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128da106t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HSC |

|--------|-----|-----|-----|-----|-----|-----|------------|

| —      | —   | —   | —   | —   | —   | —   | DC         |

| bit 15 |     |     |     |     |     |     | bit 8      |

| R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup> | R-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC |

|---------------------------|---------------------------|---------------------------|----------|------------|------------|------------|------------|

| IPL2 <sup>(2)</sup>       | IPL1 <sup>(2)</sup>       | IPL0 <sup>(2)</sup>       | RA       | N          | OV         | Z          | С          |

| bit 7                     |                           |                           |          |            |            |            | bit 0      |

| Legend:           | HSC = Hardware Settable | /Clearable bit            |                    |  |  |

|-------------------|-------------------------|---------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ad as '0'          |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |  |  |

| bit 15-9 | Unimplemented: Read as '0'                                                                                                                                                                                   |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8    | DC: ALU Half Carry/Borrow bit                                                                                                                                                                                |

|          | <ul> <li>1 = A carry out from the 4<sup>th</sup> low-order bit (for byte-sized data) or 8<sup>th</sup> low-order bit (for word-sized data) of the result occurred</li> </ul>                                 |

|          | 0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred                                                                                                        |

| bit 7-5  | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                          |

|          | 111 = CPU interrupt priority level is 7 (15); user interrupts are disabled                                                                                                                                   |

|          | 110 = CPU interrupt priority level is 6 (14)                                                                                                                                                                 |

|          | 101 = CPU interrupt priority level is 5 (13)<br>100 = CPU interrupt priority level is 4 (12)                                                                                                                 |

|          | 011 = CPU interrupt priority level is 3 (11)                                                                                                                                                                 |

|          | 010 = CPU interrupt priority level is 2 (10)                                                                                                                                                                 |

|          | 001 = CPU interrupt priority level is 1 (9)                                                                                                                                                                  |

|          | 000 = CPU interrupt priority level is 0 (8)                                                                                                                                                                  |

| bit 4    | RA: REPEAT Loop Active bit                                                                                                                                                                                   |

|          | 1 = REPEAT loop in progress                                                                                                                                                                                  |

|          | 0 = REPEAT loop not in progress                                                                                                                                                                              |

| bit 3    | N: ALU Negative bit                                                                                                                                                                                          |

|          | 1 = Result was negative                                                                                                                                                                                      |

| h:+ 0    | 0 = Result was not negative (zero or positive)                                                                                                                                                               |

| bit 2    | <b>OV:</b> ALU Overflow bit                                                                                                                                                                                  |

|          | <ul> <li>1 = Overflow occurred for signed (2's complement) arithmetic in this arithmetic operation</li> <li>0 = No overflow has occurred</li> </ul>                                                          |

| bit 1    | Z: ALU Zero bit                                                                                                                                                                                              |

|          | <ul> <li>1 = An operation, which affects the Z bit, has set it at some time in the past</li> <li>0 = The most recent operation, which affects the Z bit, has cleared it (i.e., a non-zero result)</li> </ul> |

| bit 0    | <b>C:</b> ALU Carry/Borrow bit                                                                                                                                                                               |

| DILU     | 1 = A carry out from the Most Significant bit of the result occurred                                                                                                                                         |

|          | 0 = No carry out from the Most Significant bit of the result occurred                                                                                                                                        |

| No.4     |                                                                                                                                                                                                              |

| Note 1:  |                                                                                                                                                                                                              |

| 2:       | The IPL Status bits are concatenated with the IPL3 (CORCON< $3$ ) bit to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.                              |

|          | E = 1 and $E = 1$ .                                                                                                                                                                                          |

### 4.2 Data Memory Space

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 45. "Data Memory with Extended Data Space" (DS39733). The information in this data sheet supersedes the information in the FRM.

The PIC24F core has a 16-bit wide data memory space, addressable as a single linear range.

The data space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The data space memory map is shown in Figure 4-3.

The 16-bit wide data addresses in the data memory space point to bytes within the Data Space (DS). This gives a DS address range of 64 Kbytes or 32K words. The lower 32 Kbytes (0x0000 to 0x7FFF) of DS is compatible with the PIC24F microcontrollers without EDS.

The upper 32 Kbytes of data memory address space (0x8000 - 0xFFFF) are used as an EDS window.

The EDS window is used to access all memory region implemented in EDS, as shown in Figure 4-4.

The EDS includes any additional internal data memory not accessible by the lower 32-Kbyte data address space and any external memory through EPMP. For more details on accessing internal extended data memory, refer to the "*PIC24F Family Reference Manual*", Section 45. "Data Memory with Extended Data Space (EDS)" (DS39733). For more details on accessing external memory using EPMP, refer to the "*PIC24F Family Reference Manual*", Section 42. "Enhanced Parallel Master Port (EPMP)" (DS39730). In PIC24F microcontrollers with EDS, the program memory can also be read from EDS. This is called Program Space Visibility (PSV). Table 4-2 lists the total memory accessible by each of the devices in this family.

The EDS is organized as pages, with a single page called an EDS page that equals the EDS window (32 Kbytes). A particular EDS page is selected through the Data Space Read register (DSRPAG) or Data Space Write register (DSWPAG). For PSV, only the DSRPAG register is used. The combination of the DSRPAG register value and the 16-bit wide data address forms a 24-bit Effective Address (EA). For more information on EDS, refer to **Section 4.3.3 "Reading Data from Program Memory Using EDS"**.

| Devices         | Internal RAM                          | External RAM Access<br>Using EPMP | Program Memory Access<br>Using EDS |

|-----------------|---------------------------------------|-----------------------------------|------------------------------------|

| PIC24FJXXXDA210 | 96 Kbytes (30K + 66K <sup>(1)</sup> ) | Yes (up to 16 MB)                 | Yes                                |

| PIC24FJXXXDA206 | 96 Kbytes (30K + 66K <sup>(1)</sup> ) | No                                | Yes                                |

| PIC24FJXXXDA110 | 24 Kbytes                             | Yes (up to 16 MB)                 | Yes                                |

| PIC24FJXXXDA106 | 24 Kbytes                             | No                                | Yes                                |

#### TABLE 4-2:TOTAL MEMORY ACCESSIBLE BY THE DEVICE

Note 1: The internal RAM above 30 Kbytes can be accessed through EDS window.

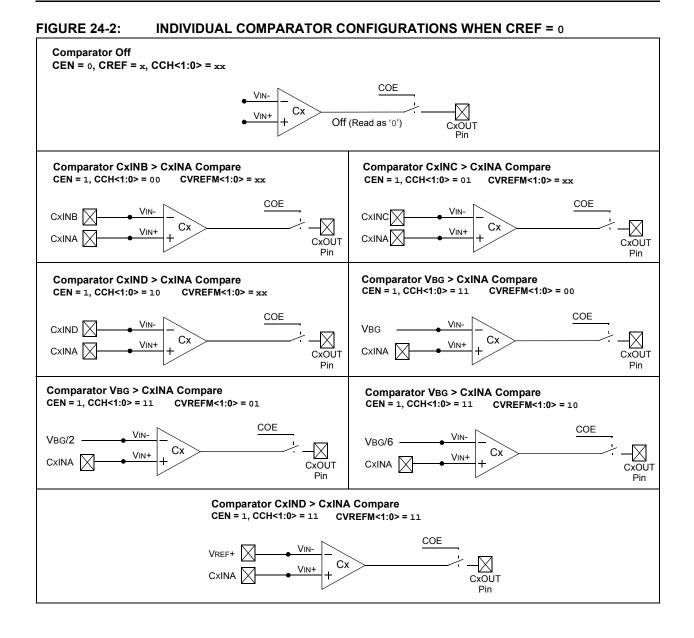

### TABLE 4-28: COMPARATORS REGISTER MAP

|   | File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|---|--------------|------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| C | MSTAT        | 0630 | CMIDL  | _      | _      | _      |        | C3EVT  | C2EVT   | C1EVT   | _      | _      | _     | _     | _     | C3OUT | C2OUT | C10UT | 0000          |

| C | VRCON        | 0632 | _      | _      | _      | _      | _      | CVREFP | CVREFM1 | CVREFM0 | CVREN  | CVROE  | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| C | M1CON        | 0634 | CON    | COE    | CPOL   | _      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 |       | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| C | M2CON        | 0636 | CON    | COE    | CPOL   | _      |        | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| C | M3CON        | 0638 | CON    | COE    | CPOL   | —      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | -     | _     | CCH1  | CCH0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-29: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8        | Bit 7         | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|---------|---------|---------|---------|--------------|---------------|--------|---------|-------|---------|-------|-------|-------|---------------|

| CRCCON1      | 0640 | CRCEN  | _      | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0       | CRCFUL        | CRCMPT | CRCISEL | CRCGO | LENDIAN | _     | _     |       | 0040          |

| CRCCON2      | 0642 | _      | _      | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0      |               |        |         | PLEN4 | PLEN3   | PLEN2 | PLEN1 | PLEN0 | 0000          |

| CRCXORL      | 0644 | X15    | X14    | X13    | X12     | X11     | X10     | X9      | X8           | X7            | X6     | X5      | X4    | X3      | X2    | X1    | _     | 0000          |

| CRCXORH      | 0646 | X31    | X30    | X29    | X28     | X27     | X26     | X25     | X24          | X23           | X22    | X21     | X20   | X19     | X18   | X17   | X16   | 0000          |

| CRCDATL      | 0648 |        |        |        |         |         |         |         | CRC Data Inp | out Register  | Low    |         |       |         |       |       |       | 0000          |

| CRCDATH      | 064A |        |        |        |         |         |         | (       | CRC Data Inp | ut Register I | High   |         |       |         |       |       |       | 0000          |

| CRCWDATL     | 064C |        |        |        |         |         |         |         | CRC Result   | t Register Lo | w      |         |       |         |       |       |       | 0000          |

| CRCWDATH     | 064E |        |        |        |         |         |         |         | CRC Result   | Register Hig  | gh     |         |       |         |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0    | U-0 | R/W-0, HS |

|--------|-----|-----------|-----------|-----------|-----------|-----------|-----------|

| —      | —   | AD1IF     | U1TXIF    | U1RXIF    | SPI1IF    | SPF1IF    | T3IF      |

| bit 15 |     |           |           |           |           |           | bit 8     |

| R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS |

|-----------|-----------|-----------|-----|-----------|-----------|-----------|-----------|

| T2IF      | OC2IF     | IC2IF     | —   | T1IF      | OC1IF     | IC1IF     | INTOIF    |

| bit 7     |           |           |     |           |           |           | bit 0     |

| Legend:      |             | HS = Hardware Settable                                 | e bit                   |                    |

|--------------|-------------|--------------------------------------------------------|-------------------------|--------------------|

| R = Readab   | ole bit     | W = Writable bit                                       | U = Unimplemented bit,  | , read as '0'      |

| -n = Value a | at POR      | '1' = Bit is set                                       | '0' = Bit is cleared    | x = Bit is unknown |

|              |             |                                                        |                         |                    |

| bit 15-14    | -           | ented: Read as '0'                                     |                         |                    |

| bit 13       |             | Conversion Complete Inte                               | errupt Flag Status bit  |                    |

|              |             | pt request has occurred<br>pt request has not occurred | 4                       |                    |

| bit 12       | -           | ART1 Transmitter Interrupt                             |                         |                    |

|              |             | pt request has occurred                                | ridg oldido bit         |                    |

|              |             | pt request has not occurred                            | ł                       |                    |

| bit 11       | U1RXIF: U   | ART1 Receiver Interrupt Flag                           | ag Status bit           |                    |

|              |             | pt request has occurred                                |                         |                    |

|              | 0 = Interru | pt request has not occurred                            | 1                       |                    |

| bit 10       | SPI1IF: SP  | I1 Event Interrupt Flag Stat                           | tus bit                 |                    |

|              | •           | pt request has occurred                                | 4                       |                    |

| L:1 0        | -           | pt request has not occurred                            |                         |                    |

| bit 9        |             | PI1 Fault Interrupt Flag Stat                          | tus dit                 |                    |

|              |             | pt request has occurred<br>pt request has not occurred | ł                       |                    |

| bit 8        | -           | 3 Interrupt Flag Status bit                            | -                       |                    |

|              |             | ot request has occurred                                |                         |                    |

|              |             | ot request has not occurred                            |                         |                    |

| bit 7        | T2IF: Timer | 2 Interrupt Flag Status bit                            |                         |                    |

|              |             | pt request has occurred                                |                         |                    |

|              | 0 = Interru | pt request has not occurred                            | 1                       |                    |

| bit 6        |             | tput Compare Channel 2 In                              | terrupt Flag Status bit |                    |

|              |             | ot request has occurred<br>ot request has not occurred |                         |                    |

| bit 5        | -           | t Capture Channel 2 Interru                            |                         |                    |

| DIL J        | •           | pt request has occurred                                | ipi i lag Status bit    |                    |

|              |             | pt request has not occurred                            | ł                       |                    |

| bit 4        | -           | ented: Read as '0'                                     |                         |                    |

| bit 3        | T1IF: Timer | 1 Interrupt Flag Status bit                            |                         |                    |

|              |             | pt request has occurred                                |                         |                    |

|              | 0 = Interru | pt request has not occurred                            | ł                       |                    |

| bit 2        | OC1IF: Out  | tput Compare Channel 1 In                              | terrupt Flag Status bit |                    |

|              | •           | pt request has occurred                                |                         |                    |

|              | 0 = Interru | pt request has not occurred                            | 1                       |                    |

|                   | R/W-1                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                      | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |

|-------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------|------------------|-----------------|---------|--|--|--|

| —                 | U3TXIP2                            | U3TXIP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U3TXIP0                                                                                    |                  | U3RXIP2          | U3RXIP1         | U3RXIP0 |  |  |  |

| bit 15            |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                            | ·                |                  |                 | bit     |  |  |  |

| U-0               | R/W-1                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                      | U-0              | U-0              | U-0             | U-0     |  |  |  |

| _                 | U3ERIP2                            | U3ERIP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U3ERIP0                                                                                    |                  | _                | _               |         |  |  |  |

| bit 7             |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                            |                  |                  |                 | bit     |  |  |  |

| Legend:           |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                            |                  |                  |                 |         |  |  |  |

| R = Readab        | ole bit                            | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit                                                                                        | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |

| -n = Value a      | at POR                             | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                            | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |

|                   | •<br>•<br>•<br>• 001 = Interru     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | abled                                                                                      |                  |                  |                 |         |  |  |  |

|                   | 000 = Interrupt source is disabled |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                            |                  |                  |                 |         |  |  |  |

|                   | IInimplomon                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                            |                  |                  |                 |         |  |  |  |

| bit 11            | -                                  | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                            | Deigerite ( hite |                  |                 |         |  |  |  |

|                   | U3RXIP<2:0> 111 = Interru          | IUART3 Reception<br>Definition of the second | iver Interrupt I<br>nighest priority                                                       | •                |                  |                 |         |  |  |  |

| bit 10-8<br>bit 7 | U3RXIP<2:0> 111 = Interru          | : UART3 Rece<br>pt is priority 7 (I<br>pt is priority 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | iver Interrupt I<br>nighest priority<br>abled                                              | •                |                  |                 |         |  |  |  |

| bit 10-8          | U3RXIP<2:0> 111 = Interru          | <ul> <li>UART3 Recept is priority 7 (1)</li> <li>pt is priority 1</li> <li>pt source is dis</li> <li>ted: Read as '0</li> <li>UART3 Error</li> <li>pt is priority 7 (1)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | iver Interrupt I<br>nighest priority<br>abled<br>o'<br>Interrupt Prior<br>nighest priority | rity bits        |                  |                 |         |  |  |  |

### REGISTER 7-37: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| Input Name              | Function Name | Register | Function Mapping<br>Bits |

|-------------------------|---------------|----------|--------------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<5:0>               |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<5:0>               |

| External Interrupt 3    | INT3          | RPINR1   | INT3R<5:0>               |

| External Interrupt 4    | INT4          | RPINR2   | INT4R<5:0>               |

| Input Capture 1         | IC1           | RPINR7   | IC1R<5:0>                |

| Input Capture 2         | IC2           | RPINR7   | IC2R<5:0>                |

| Input Capture 3         | IC3           | RPINR8   | IC3R<5:0>                |

| Input Capture 4         | IC4           | RPINR8   | IC4R<5:0>                |

| Input Capture 5         | IC5           | RPINR9   | IC5R<5:0>                |

| Input Capture 6         | IC6           | RPINR9   | IC6R<5:0>                |

| Input Capture 7         | IC7           | RPINR10  | IC7R<5:0>                |

| Input Capture 8         | IC8           | RPINR10  | IC8R<5:0>                |

| Input Capture 9         | IC9           | RPINR15  | IC9R<5:0>                |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<5:0>               |

| Output Compare Fault B  | OCFB          | RPINR11  | OCFBR<5:0>               |

| SPI1 Clock Input        | SCK1IN        | RPINR20  | SCK1R<5:0>               |

| SPI1 Data Input         | SDI1          | RPINR20  | SDI1R<5:0>               |

| SPI1 Slave Select Input | SS1IN         | RPINR21  | SS1R<5:0>                |

| SPI2 Clock Input        | SCK2IN        | RPINR22  | SCK2R<5:0>               |

| SPI2 Data Input         | SDI2          | RPINR22  | SDI2R<5:0>               |

| SPI2 Slave Select Input | SS2IN         | RPINR23  | SS2R<5:0>                |

| SPI3 Clock Input        | SCK3IN        | RPINR28  | SCK3R<5:0>               |

| SPI3 Data Input         | SDI3          | RPINR28  | SDI3R<5:0>               |

| SPI3 Slave Select Input | SS3IN         | RPINR29  | SS3R<5:0>                |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<5:0>               |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<5:0>               |

| Timer4 External Clock   | T4CK          | RPINR4   | T4CKR<5:0>               |

| Timer5 External Clock   | T5CK          | RPINR4   | T5CKR<5:0>               |

| UART1 Clear To Send     | U1CTS         | RPINR18  | U1CTSR<5:0>              |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<5:0>               |

| UART2 Clear To Send     | U2CTS         | RPINR19  | U2CTSR<5:0>              |

| UART2 Receive           | U2RX          | RPINR19  | U2RXR<5:0>               |

| UART3 Clear To Send     | U3CTS         | RPINR21  | U3CTSR<5:0>              |

| UART3 Receive           | U3RX          | RPINR17  | U3RXR<5:0>               |

| UART4 Clear To Send     | U4CTS         | RPINR27  | U4CTSR<5:0>              |

| UART4 Receive           | U4RX          | RPINR27  | U4RXR<5:0>               |

### TABLE 10-3: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)<sup>(1)</sup>

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger (ST) input buffers.

| R/W-0        | U-0                                                             | R/W-0                             | U-0               | U-0               | U-0              | U-0               | U-0          |  |  |  |  |

|--------------|-----------------------------------------------------------------|-----------------------------------|-------------------|-------------------|------------------|-------------------|--------------|--|--|--|--|

| TON          |                                                                 | TSIDL                             |                   |                   |                  | —                 |              |  |  |  |  |

| bit 15       |                                                                 |                                   |                   |                   |                  |                   | bit          |  |  |  |  |

| U-0          | R/W-0                                                           | R/W-0                             | R/W-0             | U-0               | R/W-0            | R/W-0             | U-0          |  |  |  |  |

|              | TGATE                                                           | TCKPS1                            | TCKPS0            | 0-0               | TSYNC            | TCS               |              |  |  |  |  |

| bit 7        | TOAL                                                            | 1010101                           |                   |                   | 101110           | 100               | bit          |  |  |  |  |

| Legend:      |                                                                 |                                   |                   |                   |                  |                   |              |  |  |  |  |

| R = Readab   | le hit                                                          | W = Writable                      | hit               | II – I Inimplen   | nented bit, read | 1 as 'O'          |              |  |  |  |  |

| -n = Value a |                                                                 | '1' = Bit is set                  | JIL               | '0' = Bit is clea |                  | x = Bit is unkno  |              |  |  |  |  |

|              | IFUR                                                            | I - DILIS SEL                     |                   |                   | areu             |                   | JWII         |  |  |  |  |

| bit 15       | TON: Timer1                                                     | On bit                            |                   |                   |                  |                   |              |  |  |  |  |

|              | 1 = Starts 16                                                   |                                   |                   |                   |                  |                   |              |  |  |  |  |

|              | 0 = Stops 16                                                    |                                   |                   |                   |                  |                   |              |  |  |  |  |

| bit 14       | -                                                               | nted: Read as '                   |                   |                   |                  |                   |              |  |  |  |  |

| bit 13       |                                                                 | in Idle Mode bit                  |                   |                   |                  |                   |              |  |  |  |  |

|              |                                                                 | nue module ope<br>e module operat |                   |                   | e mode           |                   |              |  |  |  |  |

| bit 12-7     |                                                                 | nted: Read as '                   |                   | -                 |                  |                   |              |  |  |  |  |

| bit 6        | -                                                               | er1 Gated Time                    |                   | Enable bit        |                  |                   |              |  |  |  |  |

|              |                                                                 | When TCS = 1:                     |                   |                   |                  |                   |              |  |  |  |  |

|              | This bit is igr                                                 |                                   |                   |                   |                  |                   |              |  |  |  |  |

|              | <u>When TCS =</u><br>1 = Gated ti                               | : <u>0:</u><br>me accumulatio     | n enabled         |                   |                  |                   |              |  |  |  |  |

|              |                                                                 | me accumulatio                    |                   |                   |                  |                   |              |  |  |  |  |

| bit 5-4      | TCKPS<1:0                                                       | >: Timer1 Input                   | Clock Prescale    | Select bits       |                  |                   |              |  |  |  |  |

|              | 11 <b>= 1:256</b>                                               |                                   |                   |                   |                  |                   |              |  |  |  |  |

|              | 10 = 1:64<br>01 = 1:8                                           |                                   |                   |                   |                  |                   |              |  |  |  |  |

|              | 01 = 1.8<br>00 = 1.1                                            |                                   |                   |                   |                  |                   |              |  |  |  |  |

| bit 3        | Unimplemer                                                      | nted: Read as '                   | )'                |                   |                  |                   |              |  |  |  |  |

| bit 2        | TSYNC: Tim                                                      | er1 External Clo                  | ock Input Syncl   | nronization Sel   | ect bit          |                   |              |  |  |  |  |

|              | When TCS =                                                      |                                   |                   |                   |                  |                   |              |  |  |  |  |

|              |                                                                 | nize external clo                 |                   |                   |                  |                   |              |  |  |  |  |

|              | 0 = D0 hot s<br>When TCS =                                      | synchronize exte                  | mai ciock inpu    | l.                |                  |                   |              |  |  |  |  |

|              | This bit is igr                                                 |                                   |                   |                   |                  |                   |              |  |  |  |  |

| bit 1        | TCS: Timer1                                                     | Clock Source S                    | Select bit        |                   |                  |                   |              |  |  |  |  |

|              |                                                                 | clock from T1C<br>clock (Fosc/2)  | K pin (on the r   | ising edge)       |                  |                   |              |  |  |  |  |

| bit 0        | Unimplemer                                                      | nted: Read as 'o                  | )'                |                   |                  |                   |              |  |  |  |  |

|              | Changing the values of the transformer the set and is not rest. |                                   | hile the timer is | s running (TON    | l = 1) causes tl | ne timer prescale | e counter to |  |  |  |  |

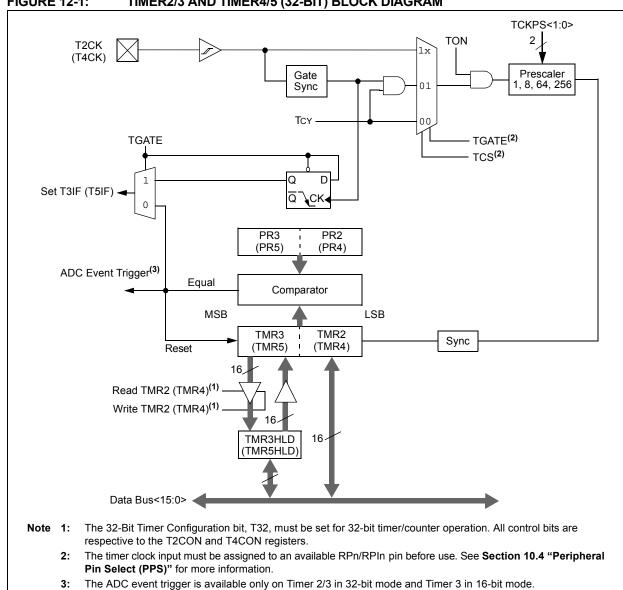

### FIGURE 12-1: TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM

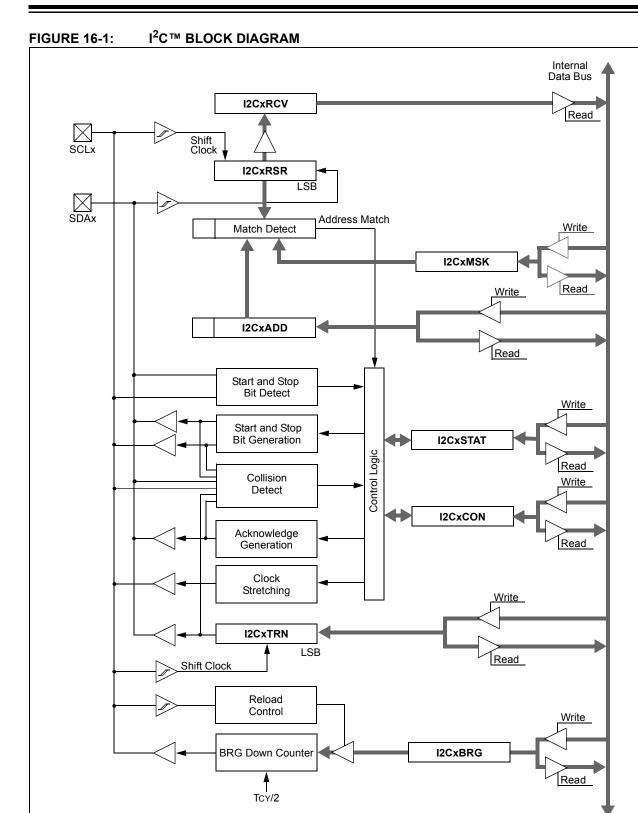

### 16.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 24. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS39702). The information in this data sheet supersedes the information in the FRM.

The Inter-Integrated Circuit<sup>TM</sup> (I<sup>2</sup>C<sup>TM</sup>) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, A/D Converters, etc.

The I<sup>2</sup>C module supports these features:

- Independent master and slave logic

- · 7-bit and 10-bit device addresses

- General call address, as defined in the I<sup>2</sup>C protocol

- Clock stretching to provide delays for the processor to respond to a slave data request

- Both 100 kHz and 400 kHz bus specifications

- · Configurable address masking

- Multi-Master modes to prevent loss of messages in arbitration

- Bus Repeater mode, allowing the acceptance of all messages as a slave regardless of the address

- Automatic SCL

- A block diagram of the module is shown in Figure 16-1.

### 16.1 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDAx and SCLx.

- 2. Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDAx and SCLx.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDAx and SCLx.

### REGISTER 18-6: U1STAT: USB STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| R-0, HSC            | U-0 | U-0   |

|----------|----------|----------|----------|----------|---------------------|-----|-------|

| ENDPT3   | ENDPT2   | ENDPT1   | ENDPT0   | DIR      | PPBI <sup>(1)</sup> | —   | —     |

| bit 7    |          |          |          |          |                     |     | bit 0 |

| Legend:           | U = Unimplemented bit, read as '0' |                                       |                    |  |  |

|-------------------|------------------------------------|---------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/Clearable bit |                    |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                  | x = Bit is unknown |  |  |

| bit 15-8<br>bit 7-4 | Unimplemented: Read as '0'<br>ENDPT<3:0>: Number of the Last Endpoint Activity bits<br>(Represents the number of the BDT updated by the last USB transfer.)<br>1111 = Endpoint 15<br>1110 = Endpoint 14 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                                                                                                                                                                                                         |

|                     | •                                                                                                                                                                                                       |

|                     | 0001 = Endpoint 1                                                                                                                                                                                       |

|                     | 0000 = Endpoint 0                                                                                                                                                                                       |

| bit 3               | DIR: Last BD Direction Indicator bit                                                                                                                                                                    |

|                     | 1 = The last transaction was a transmit transfer (TX)<br>a = The last transaction was a receive transfer (PX)                                                                                           |

|                     | 0 = The last transaction was a receive transfer (RX)                                                                                                                                                    |

| bit 2               | PPBI: Ping-Pong BD Pointer Indicator bit <sup>(1)</sup>                                                                                                                                                 |

|                     | 1 = The last transaction was to the odd BD bank                                                                                                                                                         |

|                     | 0 = The last transaction was to the even BD bank                                                                                                                                                        |