Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                |

| Number of I/O              | 84                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 96K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                    |

| Data Converters            | A/D 24x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128da210-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Number |                    |                 |                | Input |        |                             |  |  |  |

|------------|--------------------|-----------------|----------------|-------|--------|-----------------------------|--|--|--|

| Function   | 64-Pin<br>TQFP/QFN | 100-Pin<br>TQFP | 121-Pin<br>BGA | I/O   | Buffer | Description                 |  |  |  |

| CN0        | 48                 | 74              | B11            | Ι     | ST     |                             |  |  |  |

| CN1        | 47                 | 73              | C10            | Ι     | ST     |                             |  |  |  |

| CN2        | 16                 | 25              | K2             | Ι     | ST     |                             |  |  |  |

| CN3        | 15                 | 24              | K1             | Ι     | ST     |                             |  |  |  |

| CN4        | 14                 | 23              | J2             | Ι     | ST     |                             |  |  |  |

| CN5        | 13                 | 22              | J1             | Ι     | ST     |                             |  |  |  |

| CN6        | 12                 | 21              | H2             | -     | ST     |                             |  |  |  |

| CN7        | 11                 | 20              | H1             | Ι     | ST     |                             |  |  |  |

| CN8        | 4                  | 10              | E3             | Ι     | ST     |                             |  |  |  |

| CN9        | 5                  | 11              | F4             | Ι     | ST     |                             |  |  |  |

| CN10       | 6                  | 12              | F2             | Ι     | ST     |                             |  |  |  |

| CN11       | 8                  | 14              | F3             | -     | ST     |                             |  |  |  |

| CN12       | 30                 | 44              | L8             | Ι     | ST     |                             |  |  |  |

| CN13       | 52                 | 81              | C8             | Ι     | ST     |                             |  |  |  |

| CN14       | 53                 | 82              | B8             | -     | ST     |                             |  |  |  |

| CN15       | 54                 | 83              | D7             | Ι     | ST     |                             |  |  |  |

| CN16       | 55                 | 84              | C7             | Ι     | ST     |                             |  |  |  |

| CN17       | 31                 | 49              | L10            | Ι     | ST     |                             |  |  |  |

| CN18       | 32                 | 50              | L11            | Ι     | ST     |                             |  |  |  |

| CN19       | —                  | 80              | D8             | Ι     | ST     | Interrupt on Change Innute  |  |  |  |

| CN20       |                    | 47              | L9             | Ι     | ST     | Interrupt-on-Change Inputs. |  |  |  |

| CN21       | —                  | 48              | K9             | Ι     | ST     |                             |  |  |  |

| CN22       | 40                 | 64              | F11            | Ι     | ST     |                             |  |  |  |

| CN23       | 39                 | 63              | F9             | Ι     | ST     |                             |  |  |  |

| CN24       | 17                 | 26              | L1             | Ι     | ST     |                             |  |  |  |

| CN25       | 18                 | 27              | J3             | Ι     | ST     |                             |  |  |  |

| CN26       | 21                 | 32              | K4             | Ι     | ST     |                             |  |  |  |

| CN27       | 22                 | 33              | L4             | Ι     | ST     |                             |  |  |  |

| CN28       | 23                 | 34              | L5             | Ι     | ST     |                             |  |  |  |

| CN29       | 24                 | 35              | J5             | -     | ST     |                             |  |  |  |

| CN30       | 27                 | 41              | J7             | Ι     | ST     |                             |  |  |  |

| CN31       | 28                 | 42              | L7             | Ι     | ST     |                             |  |  |  |

| CN32       | 29                 | 43              | K7             | Ι     | ST     |                             |  |  |  |

| CN33       | _                  | 17              | G3             | Ι     | ST     |                             |  |  |  |

| CN34       | —                  | 38              | J6             | Ι     | ST     |                             |  |  |  |

| CN35       | —                  | 58              | H11            | Ι     | ST     |                             |  |  |  |

| CN36       | —                  | 59              | G10            | Ι     | ST     |                             |  |  |  |

| CN37       | —                  | 60              | G11            | Ι     | ST     |                             |  |  |  |

| CN38       |                    | 61              | G9             | Ι     | ST     |                             |  |  |  |

| CN39       |                    | 91              | C5             | Ι     | ST     |                             |  |  |  |

## TABLE 1-3: PIC24FJ256DA210 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

**Note 1:** The alternate EPMP pins are selected when the ALTPMP (CW3<12>) bit is programmed to '0'.

**2:** The PMSC2 signal will replace the PMA15 signal on the 15-pin PMA when CSF<1:0> = 01 or 10.

**3:** The PMCS1 signal will replace the PMA14 signal on the 14-pin PMA when CSF<1:0 > = 10.

4: The alternate VREF pins selected when the ALTVREF (CW1<5>) bit is programmed to '0'.

# 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 44. "CPU with Extended Data Space (EDS)" (DS39732). The information in this data sheet supersedes the information in the FRM.

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16<sup>th</sup> working register (W15) operates as a Software Stack Pointer for interrupts and calls.

The lower 32 Kbytes of the data space can be accessed linearly. The upper 32 Kbytes of the data space are referred to as extended data space to which the extended data RAM, EPMP memory space or program memory can be mapped.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs. The core supports Inherent (no operand), Relative, Literal, Memory Direct Addressing modes along with three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit x 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit x 16-bit or 8-bit x 8-bit, integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit, integer signed and unsigned division. All divide operations require 19 cycles to complete but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to 8 sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is shown in Figure 3-1.

## 3.1 Programmer's Model

The programmer's model for the PIC24F is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. A description of each register is provided in Table 3-1. All registers associated with the programmer's model are memory mapped.

#### TABLE 4-5: ICN REGISTER MAP

| File<br>Name | Addr | Bit 15                 | Bit 14                 | Bit 13                 | Bit 12                 | Bit 11                 | Bit 10                 | Bit 9                  | Bit 8                  | Bit 7                  | Bit 6                  | Bit 5                  | Bit 4                  | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0                  | All<br>Resets |

|--------------|------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------|

| CNPD1        | 0056 | CN15PDE                | CN14PDE                | CN13PDE                | CN12PDE                | CN11PDE                | CN10PDE                | CN9PDE                 | CN8PDE                 | CN7PDE                 | CN6PDE                 | CN5PDE                 | CN4PDE                 | CN3PDE                 | CN2PDE                 | CN1PDE                 | CN0PDE                 | 0000          |

| CNPD2        | 0058 | CN31PDE                | CN30PDE                | CN29PDE                | CN28PDE                | CN27PDE                | CN26PDE                | CN25PDE                | CN24PDE                | CN23PDE                | CN22PDE                | CN21PDE <sup>(1)</sup> | CN20PDE <sup>(1)</sup> | CN19PDE <sup>(1)</sup> | CN18PDE                | CN17PDE                | CN16PDE                | 0000          |

| CNPD3        | 005A | CN47PDE <sup>(1)</sup> | CN46PDE <sup>(1)</sup> | CN45PDE <sup>(1)</sup> | CN44PDE <sup>(1)</sup> | CN43PDE <sup>(1)</sup> | CN42PDE <sup>(1)</sup> | CN41PDE <sup>(1)</sup> | CN40PDE <sup>(1)</sup> | CN39PDE <sup>(1)</sup> | CN38PDE <sup>(1)</sup> | CN37PDE <sup>(1)</sup> | CN36PDE <sup>(1)</sup> | CN35PDE <sup>(1)</sup> | CN34PDE <sup>(1)</sup> | CN33PDE <sup>(1)</sup> | CN32PDE                | 0000          |

| CNPD4        | 005C | CN63PDE                | CN62PDE                | CN61PDE                | CN60PDE                | CN59PDE                | CN58PDE                | CN57PDE <sup>(1)</sup> | CN56PDE                | CN55PDE                | CN54PDE                | CN53PDE                | CN52PDE                | CN51PDE                | CN50PDE                | CN49PDE                | CN48PDE <sup>(1)</sup> | 0000          |

| CNPD5        | 005E | CN79PDE <sup>(1)</sup> | CN78PDE <sup>(1)</sup> | CN77PDE <sup>(1)</sup> | CN76PDE <sup>(1)</sup> | CN75PDE <sup>(1)</sup> | CN74PDE <sup>(1)</sup> | CN73PDE <sup>(1)</sup> | _                      | CN71PDE                | CN70PDE(1)             | CN69PDE                | CN68PDE                | CN67PDE <sup>(1)</sup> | CN66PDE <sup>(1)</sup> | CN65PDE                | CN64PDE                | 0000          |

| CNPD6        | 0060 | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | CN84PDE                | CN83PDE                | CN82PDE <sup>(1)</sup> | CN81PDE <sup>(1)</sup> | CN80PDE <sup>(1)</sup> | 0000          |

| CNEN1        | 0062 | CN15IE                 | CN14IE                 | CN13IE                 | CN12IE                 | CN11IE                 | CN10IE                 | CN9IE                  | CN8IE                  | CN7IE                  | CN6IE                  | CN5IE                  | CN4IE                  | <b>CN3IE</b>           | CN2IE                  | CN1IE                  | CN0IE                  | 0000          |

| CNEN2        | 0064 | CN31IE                 | CN30IE                 | CN29IE                 | CN28IE                 | CN27IE                 | CN26IE                 | CN25IE                 | CN24IE                 | CN23IE                 | CN22IE                 | CN21IE <sup>(1)</sup>  | CN20IE <sup>(1)</sup>  | CN19IE <sup>(1)</sup>  | CN18IE                 | CN17IE                 | CN16IE                 | 0000          |

| CNEN3        | 0066 | CN47IE <sup>(1)</sup>  | CN46IE <sup>(1)</sup>  | CN45IE <sup>(1)</sup>  | CN44IE <sup>(1)</sup>  | CN43IE <sup>(1)</sup>  | CN42IE <sup>(1)</sup>  | CN41IE <sup>(1)</sup>  | CN40IE <sup>(1)</sup>  | CN39IE <sup>(1)</sup>  | CN38IE <sup>(1)</sup>  | CN37IE <sup>(1)</sup>  | CN36IE <sup>(1)</sup>  | CN35IE <sup>(1)</sup>  | CN34IE <sup>(1)</sup>  | CN33IE <sup>(1)</sup>  | CN32IE                 | 0000          |

| CNEN4        | 0068 | CN63IE                 | CN62IE                 | CN61IE                 | CN60IE                 | CN59IE                 | CN58IE                 | CN57IE <sup>(1)</sup>  | CN56IE                 | CN55IE                 | CN54IE                 | CN53IE                 | CN52IE                 | CN51IE                 | CN50IE                 | CN49IE                 | CN48IE <sup>(1)</sup>  | 0000          |

| CNEN5        | 006A | CN79IE <sup>(1)</sup>  | CN78IE <sup>(1)</sup>  | CN77IE <sup>(1)</sup>  | CN76IE <sup>(1)</sup>  | CN75IE <sup>(1)</sup>  | CN74IE <sup>(1)</sup>  | CN73IE <sup>(1)</sup>  | _                      | CN71IE                 | CN70IE <sup>(1)</sup>  | CN69IE                 | CN68IE                 | CN67IE <sup>(1)</sup>  | CN66IE <sup>(1)</sup>  | CN65IE                 | CN64IE                 | 0000          |

| CNEN6        | 006C | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | —                      | CN84IE                 | CN83IE                 | CN82IE <sup>(1)</sup>  | CN81IE <sup>(1)</sup>  | CN80IE <sup>(1)</sup>  | 0000          |

| CNPU1        | 006E | CN15PUE                | CN14PUE                | CN13PUE                | CN12PUE                | CN11PUE                | CN10PUE                | CN9PUE                 | CN8PUE                 | CN7PUE                 | CN6PUE                 | CN5PUE                 | CN4PUE                 | <b>CN3PUE</b>          | CN2PUE                 | CN1PUE                 | CN0PUE                 | 0000          |

| CNPU2        | 0070 | CN31PUE                | CN30PUE                | CN29PUE                | CN28PUE                | CN27PUE                | CN26PUE                | CN25PUE                | CN24PUE                | CN23PUE                | CN22PUE                | CN21PUE <sup>(1)</sup> | CN20PUE <sup>(1)</sup> | CN19PUE <sup>(1)</sup> | CN18PUE                | CN17PUE                | CN16PUE                | 0000          |

| CNPU3        | 0072 | CN47PUE <sup>(1)</sup> | CN46PUE <sup>(1)</sup> | CN45PUE <sup>(1)</sup> | CN44PUE <sup>(1)</sup> | CN43PUE <sup>(1)</sup> | CN42PUE <sup>(1)</sup> | CN41PUE <sup>(1)</sup> | CN40PUE <sup>(1)</sup> | CN39PUE <sup>(1)</sup> | CN38PUE <sup>(1)</sup> | CN37PUE <sup>(1)</sup> | CN36PUE <sup>(1)</sup> | CN35PUE <sup>(1)</sup> | CN34PUE <sup>(1)</sup> | CN33PUE <sup>(1)</sup> | CN32PUE                | 0000          |

| CNPU4        | 0074 | CN63PUE                | CN62PUE                | CN61PUE                | CN60PUE                | CN59PUE                | CN58PUE                | CN57PUE <sup>(1)</sup> | CN56PUE                | CN55PUE                | CN54PUE                | CN53PUE                | CN52PUE                | CN51PUE                | CN50PUE                | CN49PUE                | CN48PUE <sup>(1)</sup> | 0000          |

| CNPU5        | 0076 | CN79PUE <sup>(1)</sup> | CN78PUE <sup>(1)</sup> | CN77PUE <sup>(1)</sup> | CN76PUE <sup>(1)</sup> | CN75PUE <sup>(1)</sup> | CN74PUE <sup>(1)</sup> | CN73PUE <sup>(1)</sup> | _                      | CN71PUE                | CN70PUE <sup>(1)</sup> | CN69PUE                | CN68PUE                | CN67PUE <sup>(1)</sup> | CN66PUE <sup>(1)</sup> | CN65PUE                | CN64PUE                | 0000          |

| CNPU6        | 0078 | _                      | _                      | _                      | _                      | _                      | _                      | _                      |                        |                        | —                      |                        | CN84PUE                | CN83PUE                | CN82PUE <sup>(1)</sup> | CN81PUE <sup>(1)</sup> | CN80PUE <sup>(1)</sup> | 0000          |

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note

1:

Unimplemented in 64-pin devices; read as '0'.

## TABLE 4-9: OUTPUT COMPARE REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15    | Bit 14                                                          | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8        | Bit 7          | Bit 6       | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|-----------|-----------------------------------------------------------------|----------|---------|---------|---------|--------|--------------|----------------|-------------|--------|----------|----------|----------|----------|----------|---------------|

| OC8CON1   | 01D6 | _         | _                                                               | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1       | ENFLT0         | OCFLT2      | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC8CON2   | 01D8 | FLTMD     | FLTOUT                                                          | FLTTRIEN | OCINV   | _       | DCB1    | DCB0   | OC32         | OCTRIG         | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC8RS     | 01DA |           |                                                                 |          |         |         |         |        | Output Compa | are 8 Seconda  | ry Register |        |          |          |          |          |          | 0000          |

| OC8R      | 01DC |           |                                                                 |          |         |         |         |        | Output 0     | Compare 8 Re   | gister      |        |          |          |          |          |          | 0000          |

| OC8TMR    | 01DE |           |                                                                 |          |         |         |         |        | Output Compa | re 8 Timer Val | ue Register |        |          |          |          |          |          | xxxx          |

| OC9CON1   | 01E0 |           | _                                                               | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | ENFLT2 | ENFLT1       | ENFLT0         | OCFLT2      | OCFLT1 | OCFLT0   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC9CON2   | 01E2 | FLTMD     | FLTOUT                                                          | FLTTRIEN | OCINV   | _       | DCB1    | DCB0   | OC32         | OCTRIG         | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC9RS     | 01E4 |           |                                                                 |          |         |         |         |        | Output Compa | are 9 Seconda  | ry Register |        |          |          |          |          |          | 0000          |

| OC9R      | 01E6 |           |                                                                 |          |         |         |         |        | Output 0     | Compare 9 Re   | gister      |        |          |          |          |          |          | 0000          |

| OC9TMR    | 01E8 |           | Output Compare 9 Timer Value Register                           |          |         |         |         |        |              |                | xxxx        |        |          |          |          |          |          |               |

| Legend:   | _=   | unimpleme | nplemented, read as '0'. Reset values are shown in hexadecimal. |          |         |         |         |        |              |                |             |        |          |          |          |          |          |               |

# TABLE 4-10: I<sup>2</sup>C™ REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5        | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|--------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200 | _       | —      | _       | _      | _      | —      | -      | _     |       |       |              | I2C1 Receiv  | e Register   |       |       |       | 0000          |

| I2C1TRN      | 0202 | _       | —      |         | _      | _      | _      | —      | _     |       |       |              | I2C1 Transm  | nit Register |       |       |       | 00FF          |

| I2C1BRG      | 0204 | _       | —      | _       | _      |        | _      | _      |       |       |       | I2C1 Baud I  | Rate Generat | or Register  |       |       |       | 0000          |

| I2C1CON      | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT        | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208 | ACKSTAT | TRSTAT | —       |        |        | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/Ā          | Р            | s            | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A | _       | —      | _       | _      |        | _      |        |       |       |       | I2C1 Addre   | ss Register  |              |       |       |       | 0000          |

| I2C1MSK      | 020C | _       | _      | _       | _      |        | _      |        |       |       | 12    | C1 Address   | Mask Registe | er           |       |       |       | 0000          |

| I2C2RCV      | 0210 | —       | —      | —       | —      |        | _      | —      |       |       |       |              | I2C2 Receiv  | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212 | _       | _      | _       | _      |        | _      | _      |       |       |       |              | I2C2 Transm  | nit Register |       |       |       | 00FF          |

| I2C2BRG      | 0214 | —       | —      | —       | —      | —      | —      | —      |       |       |       | I2C2 Baud I  | Rate Generat | or Register  |       |       |       | 0000          |

| I2C2CON      | 0216 | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT        | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218 | ACKSTAT | TRSTAT | _       | —      | —      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A          | Р            | S            | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A | _       | —      | _       | _      |        | _      |        |       |       |       | I2C2 Addre   | ss Register  |              |       |       |       | 0000          |

| I2C2MSK      | 021C | _       | —      | _       | _      |        | _      |        |       |       | 12    | C2 Address   | Mask Registe | r            |       |       |       | 0000          |

| I2C3RCV      | 0270 | _       | —      | _       | _      |        | _      | _      |       |       |       |              | I2C3 Receiv  | e Register   |       |       |       | 0000          |

| I2C3TRN      | 0272 | _       | —      | _       | _      |        | —      | _      |       |       |       |              | I2C3 Transm  | nit Register |       |       |       | 00FF          |

| I2C3BRG      | 0274 | _       | _      | _       | _      |        | _      | _      |       |       |       | I2C3 Baud I  | Rate Generat | or Register  |       |       |       | 0000          |

| I2C3CON      | 0276 | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT        | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C3STAT     | 0278 | ACKSTAT | TRSTAT | —       | _      |        | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A          | Р            | s            | R/W   | RBF   | TBF   | 0000          |

| I2C3ADD      | 027A | _       | —      | _       | _      |        | _      |        |       |       |       | I2C3 Addre   | ss Register  |              |       |       |       | 0000          |

| I2C3MSK      | 027C | _       | _      | _       | _      | _      | _      |        |       |       | 120   | C3 Address I | Mask Registe | er           |       |       |       | 0000          |

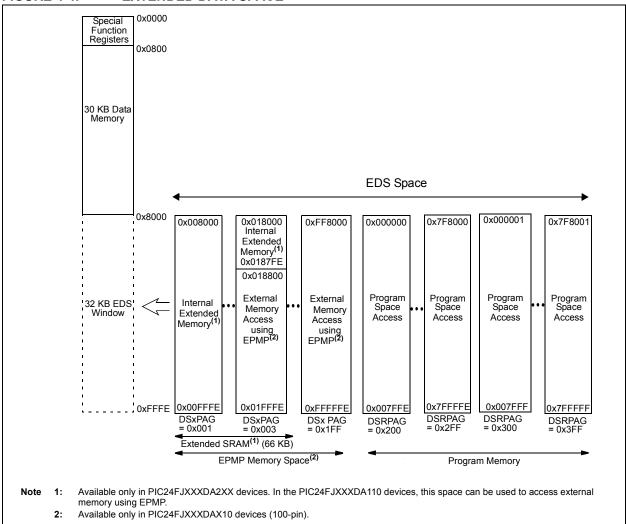

### 4.2.5 EXTENDED DATA SPACE (EDS)

The enhancement of the data space in PIC24FJ256DA210 family devices has been accomplished by a new technique, called the Extended Data Space (EDS).

The EDS includes any additional internal extended data memory not accessible by the lower 32 Kbytes data address space, any external memory through EPMP and the Program Space Visibility (PSV).

The extended data space is always accessed through the EDS window, the upper half of data space. The entire extended data space is organized into EDS pages, each having 32 Kbytes of data. Mapping of the EDS page into the EDS window is done using the Data Space Read register (DSRPAG<9:0>) for read operations and Data Space Write register (DSWPAG<8:0>) for write operations. Figure 4-4 displays the entire EDS space.

Note: Accessing Page 0 in the EDS window will generate an address error trap as Page 0 is the base data memory (data locations, 0x0800 to 0x7FFF, in the lower data space).

|                   | Vector | IVT     | AIVT    | Inte     | errupt Bit Locat | ions         |

|-------------------|--------|---------|---------|----------|------------------|--------------|

| Interrupt Source  | Number | Address | Address | Flag     | Enable           | Priority     |

| Timer1            | 3      | 00001Ah | 00011Ah | IFS0<3>  | IEC0<3>          | IPC0<14:12>  |

| Timer2            | 7      | 000022h | 000122h | IFS0<7>  | IEC0<7>          | IPC1<14:12>  |

| Timer3            | 8      | 000024h | 000124h | IFS0<8>  | IEC0<8>          | IPC2<2:0>    |

| Timer4            | 27     | 00004Ah | 00014Ah | IFS1<11> | IEC1<11>         | IPC6<14:12>  |

| Timer5            | 28     | 00004Ch | 00014Ch | IFS1<12> | IEC1<12>         | IPC7<2:0>    |

| UART1 Error       | 65     | 000096h | 000196h | IFS4<1>  | IEC4<1>          | IPC16<6:4>   |

| UART1 Receiver    | 11     | 00002Ah | 00012Ah | IFS0<11> | IEC0<11>         | IPC2<14:12>  |

| UART1 Transmitter | 12     | 00002Ch | 00012Ch | IFS0<12> | IEC0<12>         | IPC3<2:0>    |

| UART2 Error       | 66     | 000098h | 000198h | IFS4<2>  | IEC4<2>          | IPC16<10:8>  |

| UART2 Receiver    | 30     | 000050h | 000150h | IFS1<14> | IEC1<14>         | IPC7<10:8>   |

| UART2 Transmitter | 31     | 000052h | 000152h | IFS1<15> | IEC1<15>         | IPC7<14:12>  |

| UART3 Error       | 81     | 0000B6h | 0001B6h | IFS5<1>  | IEC5<1>          | IPC20<6:4>   |

| UART3 Receiver    | 82     | 0000B8h | 0001B8h | IFS5<2>  | IEC5<2>          | IPC20<10:8>  |

| UART3 Transmitter | 83     | 0000BAh | 0001BAh | IFS5<3>  | IEC5<3>          | IPC20<14:12> |

| UART4 Error       | 87     | 0000C2h | 0001C2h | IFS5<7>  | IEC5<7>          | IPC21<14:12> |

| UART4 Receiver    | 88     | 0000C4h | 0001C4h | IFS5<8>  | IEC5<8>          | IPC22<2:0>   |

| UART4 Transmitter | 89     | 0000C6h | 0001C6h | IFS5<9>  | IEC5<9>          | IPC22<6:4>   |

| USB Interrupt     | 86     | 0000C0h | 0001C0h | IFS5<6>  | IEC5<6>          | IPC21<10:8>  |

### TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS (CONTINUED)

Note 1: Not available in 64-pin devices (PIC24FJXXXDAX06).

## 7.3 Interrupt Control and Status Registers

The PIC24FJ256DA210 family of devices implements a total of 40 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS6

- IEC0 through IEC6

- IPC0 through IPC25 (except IPC14, IPC17 and IPC24)

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table (AIVT).

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or an external signal and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals. The IPCx registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the order of their vector numbers, as shown in Table 7-2. For example, the INT0 (External Interrupt 0) is shown as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU interrupt priority level. The user can change the current CPU priority level by writing to the IPL bits.

| GCLKDIV<6:0> | Frequency Divisor                 | Display Module Clock Frequency<br>96 MHz Input (48 MHz Input) |

|--------------|-----------------------------------|---------------------------------------------------------------|

| 000000       | 1                                 | 96 MHz (48 MHz)                                               |

| 000001       | 1.25 (start incrementing by 0.25) | 76.80 MHz (38.4 MHz)                                          |

| 0000010      | 1.5                               | 64 MHz (32 MHz)                                               |

|              |                                   |                                                               |

| 0111111      | 16.75                             | 5.73 MHz (2.86 MHz)                                           |

| 1000000      | 17                                | 5.65 MHz (2.82 MHz)                                           |

| 1000001      | 17.5 (start incrementing by 0.5)  | 5.49 MHz (2.74 MHz)                                           |

| 1000010      | 18                                | 5.33 MHz (2.66 MHz)                                           |

|              |                                   |                                                               |

| 1011111      | 32.5                              | 2.95 MHz (1.47 MHz)                                           |

| 1100000      | 33                                | 2.91 MHz (1.45 MHz)                                           |

| 1100001      | 34 (start incrementing by 1)      | 2.82 MHz (1.41 MHz)                                           |

| 1100010      | 35                                | 2.74 MHz (1.37 MHz)                                           |

|              |                                   |                                                               |

| 1111110      | 63                                | 1.52 MHz (762 kHz)                                            |

| 1111111      | 64                                | 1.50 MHz (750 kHz)                                            |

### TABLE 8-4: DISPLAY MODULE CLOCK FREQUENCY DIVISION

## 8.6 Reference Clock Output

In addition to the CLKO output (Fosc/2) available in certain oscillator modes, the device clock in the PIC24FJ256DA210 family devices can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 8-5). Setting the ROEN bit (REFOCON<15>) makes the clock signal available on the REFO pin. The RODIV bits (REFOCON<11:8>) enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<13:12>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSCI and OSCO, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on REFO when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for one of the primary modes (EC, HS or XT); otherwise, if the POSCEN bit is not also set, the oscillator on OSCI and OSCO will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

#### 10.4.6 PERIPHERAL PIN SELECT REGISTERS

The PIC24FJ256DA210 family of devices implements a total of 37 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (21)

- Output Remappable Peripheral Registers (16)

#### Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.4.4.1 "Control Register Lock" for a specific command sequence.

#### REGISTER 10-8: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0                                | U-0   | R/W-1          | R/W-1  | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|------------------------------------|-------|----------------|--------|-------------------|------------------|-----------------|--------|

| —                                  | —     | INT1R5         | INT1R4 | INT1R3            | INT1R2           | INT1R1          | INT1R0 |

| bit 15                             |       |                |        |                   |                  |                 | bit 8  |

|                                    |       |                |        |                   |                  |                 |        |

| U-0                                | U-0   | U-0            | U-0    | U-0               | U-0              | U-0             | U-0    |

| _                                  | -     | —              | —      | —                 | —                | —               | —      |

| bit 7                              |       |                |        |                   |                  |                 | bit 0  |

|                                    |       |                |        |                   |                  |                 |        |

| Legend:                            |       |                |        |                   |                  |                 |        |

| R = Readable                       | e bit | W = Writable b | oit    | U = Unimplem      | nented bit, read | l as '0'        |        |

| -n = Value at POR '1' = Bit is set |       |                |        | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |

| bit 15-14 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 13-8  | INT1R<5:0>: Assign External Interrupt 1 (INT1) to Corresponding RPn or RPIn Pin bits |

| bit 7-0   | Unimplemented: Read as '0'                                                           |

### REGISTER 10-9: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0             | U-0   | R/W-1            | R/W-1  | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|-----------------|-------|------------------|--------|-------------------|------------------|-----------------|--------|

| _               | _     | INT3R5           | INT3R4 | INT3R3            | INT3R2           | INT3R1          | INT3R0 |

| bit 15          |       |                  |        |                   |                  | ·               | bit    |

|                 |       |                  |        |                   |                  |                 |        |

| U-0             | U-0   | R/W-1            | R/W-1  | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

| _               | _     | INT2R5           | INT2R4 | INT2R3            | INT2R2           | INT2R1          | INT2R0 |

| bit 7           |       | ·                |        |                   |                  |                 | bit    |

|                 |       |                  |        |                   |                  |                 |        |

| Legend:         |       |                  |        |                   |                  |                 |        |

| R = Readable    | e bit | W = Writable     | bit    | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value at I | POR   | '1' = Bit is set |        | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

| bit 15-14 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 13-8  | INT3R<5:0>: Assign External Interrupt 3 (INT3) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                           |

| bit 5-0   | INT2R<5:0>: Assign External Interrupt 2 (INT2) to Corresponding RPn or RPIn Pin bits |

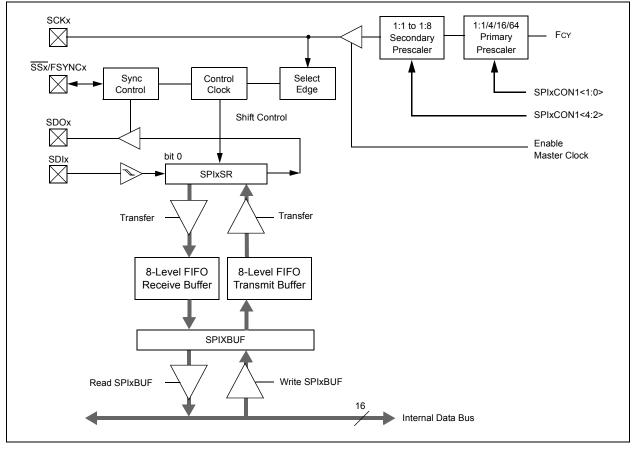

To set up the SPI module for the Enhanced Buffer Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- 6. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPI module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Select Enhanced Buffer mode by setting the SPIBEN bit (SPIxCON2<0>).

- 8. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

#### FIGURE 15-2: SPIX MODULE BLOCK DIAGRAM (ENHANCED MODE)

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 4 **RXINV:** Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode (4 BRG clock cycles per bit)

- 0 = Standard-Speed mode (16 BRG clock cycles per bit)

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Bit Selection bit

- 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

#### 18.6.2 HOST NEGOTIATION PROTOCOL (HNP)

In USB OTG applications, a Dual Role Device (DRD) is a device that is capable of being either a host or a peripheral. Any OTG DRD must support Host Negotiation Protocol (HNP).

HNP allows an OTG B-device to temporarily become the USB host. The A-device must first enable the B-device to follow HNP. Refer to the "On-The-Go Supplement to the USB 2.0 Specification" for more information regarding HNP. HNP may only be initiated at full speed.

After being enabled for HNP by the A-device, the B-device requests being the host any time that the USB link is in suspend state, by simply indicating a disconnect. This can be done in software by clearing DPPULUP and DMPULUP. When the A-device detects the disconnect condition (via the URSTIF (U1IR<0>) interrupt), the A-device may allow the B-device to take over as host. The A-device does this by signaling connect as a full-speed function. Software may accomplish this by setting DPPULUP.

If the A-device responds instead with resume signaling, the A-device remains as host. When the B-device detects the connect condition (via ATTACHIF (U1IR<6>), the B-device becomes host. The B-device drives Reset signaling prior to using the bus.

When the B-device has finished in its role as host, it stops all bus activity and turns on its D+ pull-up resistor by setting DPPULUP. When the A-device detects a suspend condition (Idle for 3 ms), the A-device turns off its D+ pull-up. The A-device may also power-down the VBUS supply to end the session. When the A-device detects the connect condition (via ATTACHIF), the A-device resumes host operation and drives Reset signaling.

#### 18.6.3 **EXTERNAL VBUS COMPARATORS**

The external VBUS comparator option is enabled by setting the UVCMPDIS bit (U1CNFG2<1>). This disables the internal VBUS comparators, removing the need to attach VBUS to the microcontroller's VBUS pin.

The external comparator interface uses either the VCMPST1 and VCMPST2 pins, or the VBUSVLD, SESSVLD and SESSEND pins, based upon the setting of the UVCMPSEL bit (U1CNFG2<5>). These pins are digital inputs and should be set in the following patterns (see Table 18-3), based on the current level of the VBUS voltage.

#### **EXTERNAL VBUS COMPARATOR STATES** TABLE 18-3:

| lf U\ | CMPSEL = 0 |

|-------|------------|

|       |            |

| VCMPST1 | VCMPST2 | Bus Condition                    |  |  |  |  |

|---------|---------|----------------------------------|--|--|--|--|

| 0       | 0       | VBUS < VB_SESS_END               |  |  |  |  |

| 1       | 0       | VB_SESS_END < VBUS < VA_SESS_VLD |  |  |  |  |

| 0       | 1       | VA_SESS_VLD < VBUS < VA_VBUS_VLD |  |  |  |  |

| 1       | 1       | VBUS > VBUS_VLD                  |  |  |  |  |

|         |         |                                  |  |  |  |  |

### IF UVCMPSEL = 1

| VBUSVLD | SESSVLD | SESSEND | Bus Condition                    |  |  |  |  |  |  |

|---------|---------|---------|----------------------------------|--|--|--|--|--|--|

| 0       | 0       | 1       | VBUS < VB_SESS_END               |  |  |  |  |  |  |

| 0       | 0       | 0       | VB_SESS_END < VBUS < VA_SESS_VLD |  |  |  |  |  |  |

| 0       | 1       | 0       | VA_SESS_VLD < VBUS < VA_VBUS_VLD |  |  |  |  |  |  |

| 1       | 1       | 0       | VBUS > VBUS_VLD                  |  |  |  |  |  |  |

| R/W-0         | U-0                                             | R/W-0                                              | R/W-0                                                                        | R/W-0                                    | U-0             | R/W-0            | R/W-0       |

|---------------|-------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|-----------------|------------------|-------------|

| PMPEN         |                                                 | PSIDL                                              | ADRMUX1                                                                      | ADRMUX0                                  | —               | MODE1            | MODE0       |

| bit 15        |                                                 |                                                    |                                                                              |                                          |                 |                  | bit 8       |

| R/W-0         | R/W-0                                           | R/W-0                                              | R/W-0                                                                        | U-0                                      | R/W-0           | R/W-0            | R/W-0       |

| CSF1          | CSF0                                            | ALP                                                | ALMODE                                                                       |                                          | BUSKEEP         | IRQM1            | IRQM0       |

| bit 7         | 0010                                            | ,                                                  | , LINODE                                                                     |                                          | DUCINELI        | in equilit       | bit (       |

| Legend:       |                                                 |                                                    |                                                                              |                                          |                 |                  |             |

| R = Readabl   | e bit                                           | W = Writable                                       | e bit                                                                        | U = Unimplem                             | ented bit, read | l as '0'         |             |

| -n = Value at | POR                                             | '1' = Bit is se                                    | t                                                                            | '0' = Bit is clea                        | ared            | x = Bit is unkr  | nown        |

| bit 15        | <b>PMPEN:</b> Par<br>1 = EPMP is<br>0 = EPMP is |                                                    | ort Enable bit                                                               |                                          |                 |                  |             |

| bit 14        | Unimpleme                                       | nted: Read as                                      | · '0'                                                                        |                                          |                 |                  |             |

| bit 13        | PSIDL: Stop                                     | in Idle Mode I                                     | bit                                                                          |                                          |                 |                  |             |

|               |                                                 |                                                    | peration when de                                                             |                                          | mode            |                  |             |

|               |                                                 |                                                    | ation in Idle mod                                                            |                                          |                 |                  |             |

| bit 12-11     |                                                 |                                                    | Data Multiplexing                                                            |                                          |                 |                  |             |

|               | 10 = Lower<br>01 = Lower                        | address bits a<br>address bits a                   | re multiplexed w<br>re multiplexed w<br>re multiplexed w<br>pear on separate | ith data bits usir<br>ith data bits usir | ng 2 address p  | hases            |             |

| bit 10        | Unimpleme                                       | nted: Read as                                      | · '0'                                                                        |                                          |                 |                  |             |

| bit 9-8       | MODE<1:0>                                       | : Parallel Port                                    | Mode Select bits                                                             | 6                                        |                 |                  |             |

|               | 01 = Buffere<br>00 = Legacy                     | ced PSP; pins<br>ed PSP; pins u<br>/ Parallel Slav | used are PMRD<br>ised are PMRD,<br>e Port; PMRD, P                           | PMWR, PMCS                               | and PMD<7:0     | >                |             |

| bit 7-6       | CSF<1:0>: (                                     | Chip Select Fu                                     | nction bits                                                                  |                                          |                 |                  |             |

|               | 01 = PMA<                                       | 15> used for C<br>15> used for C                   | Chip Select 2, PN<br>Chip Select 2, PN<br>p Select 2, PMC                    | ICS1 used for C                          | hip Select 1    |                  |             |

| bit 5         | ALP: Addres                                     | s Latch Polari                                     | ty bit                                                                       |                                          |                 |                  |             |

|               |                                                 |                                                    | MALH and PMA                                                                 |                                          |                 |                  |             |

| bit 4         | ALMODE: A                                       | ddress Latch                                       | Strobe Mode bit                                                              |                                          |                 |                  |             |

|               | cause a                                         |                                                    | ss strobes (each<br>ess in the latch tl<br>ss strobes                        | -                                        | • •             | t if the current | access woul |

| bit 3         | Unimpleme                                       | nted: Read as                                      | · '0'                                                                        |                                          |                 |                  |             |

| bit 2         | BUSKEEP:                                        | Bus Keeper bi                                      | t                                                                            |                                          |                 |                  |             |

|               |                                                 |                                                    | t value when not<br>pedance state wi                                         |                                          |                 |                  |             |

| oit 1-0       | IRQM<1:0>:                                      | Interrupt Req                                      | uest Mode bits                                                               |                                          |                 |                  |             |

|               |                                                 | read or write                                      | when Read Buffer                                                             |                                          |                 |                  |             |

| U-0                   | U-0                                                                                                                              | U-0                                                                                                                                                                               | U-0                | U-0              | U-0            | R/W-0          | R/W-0     |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|----------------|----------------|-----------|--|--|--|--|

| —                     | —                                                                                                                                | —                                                                                                                                                                                 | —                  | —                | _              | DPPINOE        | DPPOWER   |  |  |  |  |

| oit 15                |                                                                                                                                  |                                                                                                                                                                                   |                    |                  |                |                | bit       |  |  |  |  |

| R/W-0                 | R/W-0                                                                                                                            | R/W-0                                                                                                                                                                             | R/W-0              | R/W-0            | R/W-0          | R/W-0          | R/W-0     |  |  |  |  |

| DPCLKPOL              | DPENPOL                                                                                                                          | DPVSPOL                                                                                                                                                                           | DPHSPOL            | DPPWROE          | DPENOE         | DPVSOE         | DPHSOE    |  |  |  |  |

| bit 7                 |                                                                                                                                  | DIVOIOL                                                                                                                                                                           | DITIOL             |                  | DI LINOL       | DIVSOL         | bit       |  |  |  |  |

|                       |                                                                                                                                  |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

| Legend:               |                                                                                                                                  |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

| R = Readable          | bit                                                                                                                              | W = Writable bit                                                                                                                                                                  |                    | U = Unimple      | mented bit, re | ead as '0'     |           |  |  |  |  |

| -n = Value at I       | POR                                                                                                                              | '1' = Bit is set                                                                                                                                                                  |                    | '0' = Bit is cle | eared          | x = Bit is unl | known     |  |  |  |  |

| bit 15-10             | Unimplemen                                                                                                                       | ted: Read as '0'                                                                                                                                                                  |                    |                  |                |                |           |  |  |  |  |

| bit 9                 | -                                                                                                                                | isplay Pin Output P                                                                                                                                                               | ad Enable bit      |                  |                |                |           |  |  |  |  |

|                       | DPPINOE is                                                                                                                       | the master outp                                                                                                                                                                   | ut enable and      |                  |                | GDBEN<15:0     | >, DPENOE |  |  |  |  |

|                       |                                                                                                                                  | DPVSOE and DPH                                                                                                                                                                    | SOE to enable      | the associated   | d pads         |                |           |  |  |  |  |

|                       |                                                                                                                                  | lisplay output pads<br>display output signa                                                                                                                                       | als as set by G[   | DBEN<15:0>       |                |                |           |  |  |  |  |

|                       | Pins used by                                                                                                                     | <ul> <li>Disable display output signals as set by GDBEN&lt;15:0&gt;</li> <li>Pins used by the signals are assigned to the next enabled module that uses the same pins.</li> </ul> |                    |                  |                |                |           |  |  |  |  |

|                       | For data sign                                                                                                                    | als, GDBEN<15:0><br>set                                                                                                                                                           | can be used to     | o disable or en  | able specific  | data signals   | while     |  |  |  |  |

| bit 8                 |                                                                                                                                  | Display Power-up F                                                                                                                                                                | Power-Down Se      | equencer Cont    | trol bit       |                |           |  |  |  |  |

|                       | Refer to the "PIC24F Family Reference Manual", Section 43. "Graphics Controller Module (GFX)"                                    |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

|                       | for details.<br>1 = Set Display Power Sequencer Control port (GPWR) to '1'                                                       |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

|                       |                                                                                                                                  | er Control Sequence                                                                                                                                                               |                    |                  |                |                |           |  |  |  |  |

| bit 7                 | DPCLKPOL:                                                                                                                        | Display Glass Cloo                                                                                                                                                                | ck (GCLK) Pola     | rity bit         |                |                |           |  |  |  |  |

|                       |                                                                                                                                  | atches data on the                                                                                                                                                                |                    |                  |                |                |           |  |  |  |  |

| <b>h</b> : <b>h</b> O |                                                                                                                                  | atches data on the                                                                                                                                                                |                    |                  |                |                |           |  |  |  |  |

| bit 6                 |                                                                                                                                  | Display Enable Sign                                                                                                                                                               |                    | -                |                |                |           |  |  |  |  |

|                       | For TFT mode (DPMODE (G1CON2<2:0>) = 001):<br>1 = Active-high (GEN)                                                              |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

|                       | $0 = \text{Active-low}(\overline{\text{GEN}})$                                                                                   |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

|                       | For STN mode (DPMODE (G1CON2<2:0>) = 010 or 011):<br>1 = GEN connects to the shift clock input of the display (Shift Clock mode) |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

|                       |                                                                                                                                  | inects to the MOD i                                                                                                                                                               |                    |                  |                | ,              |           |  |  |  |  |

| bit 5                 | DPVSPOL: Display Vertical Synchronization (VSYNC) Polarity bit                                                                   |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

|                       | 1 = Active-hi                                                                                                                    |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

| hit 1                 | 0 = Active-lo                                                                                                                    | ( )                                                                                                                                                                               | which reprize tion |                  | arity bit      |                |           |  |  |  |  |

| bit 4                 | <b>DPHSPOL:</b> Display Horizontal Synchronization (HSYNC) Polarity bit<br>1 = Active-high (HSYNC)                               |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

|                       | 0 = Active-loc                                                                                                                   |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

| bit 3                 | DPPWROE:                                                                                                                         | Display Power-up/F                                                                                                                                                                | Power-Down Se      | equencer Cont    | rol port (GPV  | VR) enable b   | it        |  |  |  |  |

|                       |                                                                                                                                  | ort is enabled (pin<br>ort is disabled (pin                                                                                                                                       |                    |                  | ·              | 3<8>))         |           |  |  |  |  |

| bit 2                 | -                                                                                                                                | splay Enable Port E                                                                                                                                                               |                    | s an orunnary h  |                |                |           |  |  |  |  |

|                       |                                                                                                                                  |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

|                       | 1 = GEN por                                                                                                                      |                                                                                                                                                                                   |                    |                  |                |                |           |  |  |  |  |

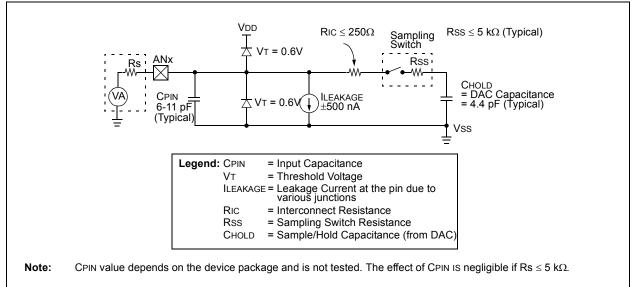

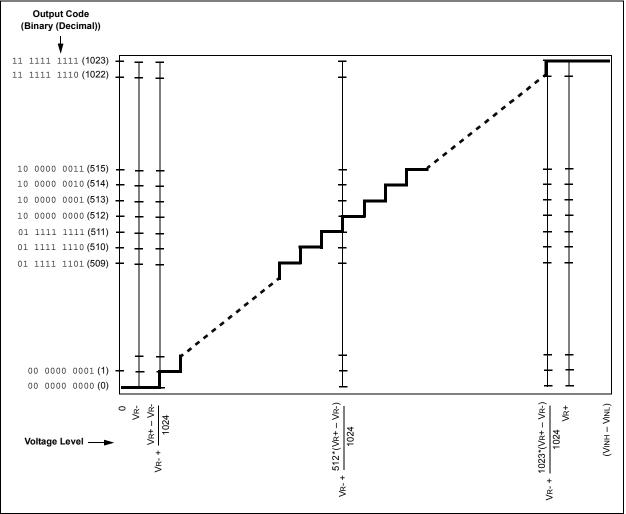

# 23.0 10-BIT HIGH-SPEED A/D CONVERTER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 17. "10-Bit A/D Converter" (DS39705). The information in this data sheet supersedes the information in the FRM.

The 10-bit A/D Converter has the following key features:

- · Successive Approximation (SAR) conversion

- · Conversion speeds of up to 500 ksps

- 24 analog input pins (PIC24FJXXXDAX10 devices) and 16 analog input pins (PIC24FJXXXDAX06 devices)

- External voltage reference input pins

- Internal band gap reference inputs

- · Automatic Channel Scan mode

- · Selectable conversion trigger source

- 32-word conversion result buffer

- · Selectable Buffer Fill modes

- · Four result alignment options

- · Operation during CPU Sleep and Idle modes

On all PIC24FJ256DA210 family devices, the 10-bit A/D Converter has 24 analog input pins, designated AN0 through AN23. In addition, there are two analog input pins for external voltage reference connections (VREF+ and VREF-). These voltage reference inputs may be shared with other analog input pins.

A block diagram of the A/D Converter is shown in Figure 23-1.

To perform an A/D conversion:

- 1. Configure the A/D module:

- Configure the port pins as analog inputs and/or select band gap reference inputs (ANCFG registers).

- b) Select the voltage reference source to match the expected range on analog inputs (AD1CON2<15:13>).