Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

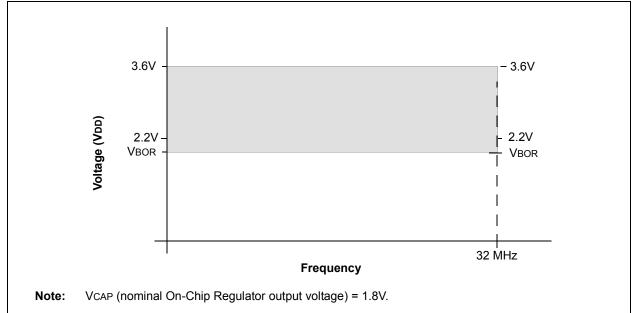

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 84                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 96K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| Data Converters            | A/D 24x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128da210t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 2: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 100-PIN DEVICES

| Pin | Function                              | Pin | Function            |

|-----|---------------------------------------|-----|---------------------|

| 81  | RP25/PMWR/CN13/RD4                    | 91  | AN23/GEN/CN39/RA6   |

| 82  | RP20/PMRD/CN14/RD5                    | 92  | AN22/PMA17/CN40/RA7 |

| 83  | C3INB/PMD14/CN15/RD6                  | 93  | PMD0/CN58/RE0       |

| 84  | C3INA/SESSEND/PMD15/CN16/RD7          | 94  | PMD1/CN59/RE1       |

| 85  | VCAP                                  | 95  | PMA16/CN81/RG14     |

| 86  | ENVREG                                | 96  | Vsync/CN79/RG12     |

| 87  | VBUSST/VCMPST1/VBUSVLD/PMD11/CN68/RF0 | 97  | HSYNC/CN80/RG13     |

| 88  | VCMPST2/SESSVLD/PMD10/CN69/RF1        | 98  | PMD2/CN60/RE2       |

| 89  | PMD9/CN78/RG1                         | 99  | PMD3/CN61/RE3       |

| 90  | PMD8/CN77/RG0                         | 100 | PMD4/CN62/RE4       |

Legend:

end: RPn and RPIn represent remappable pins for Peripheral Pin Select (PPS) functions.

Note 1: Alternate pin assignments for VREF+ and VREF- when the ALTVREF Configuration bit is programmed.

2: Alternate pin assignments for EPMP when the ALTPMP Configuration bit is programmed.

3: Pin assignment for PMCSx when CSF<1:0> is not equal to '00'.

## 1.2 Graphics Controller

With the PIC24FJ256DA210 family of devices, Microchip introduces the Graphics Controller module, which acts as an interface between the CPU (mainly through SFRs) and a display. On-board RAM is provided for display buffer, scratch areas, images and fonts. In some cases, the RAM requirements for the display used exceeds the on-board RAM; external memory connected through EPMP can be used.

This module provides acceleration for drawing points, vertical and horizontal lines, rectangles, copying rectangles between different locations on screen, drawing text and decompressing compressed data.

## 1.3 USB On-The-Go

The USB On-The-Go (USB OTG) module provides on-chip functionality as a target device compatible with the USB 2.0 standard, as well as limited stand-alone functionality as a USB embedded host. By implementing USB Host Negotiation Protocol (HNP), the module can also dynamically switch between device and host operation, allowing for a much wider range of versatile USB enabled applications on a microcontroller platform.

In addition to USB host functionality, PIC24FJ256DA210 family devices provide a true single chip USB solution, including an on-chip transceiver and voltage regulator, and a voltage boost generator for sourcing bus power during host operations.

## 1.4 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

- Communications: The PIC24FJ256DA210 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are three independent I<sup>2</sup>C<sup>™</sup> modules that support both Master and Slave modes of operation. Devices also have, through the PPS feature, four independent UARTs with built-in IrDA<sup>®</sup> encoders/decoders and three SPI modules.

- Analog Features: All members of the PIC24FJ256DA210 family include a 10-bit A/D Converter (ADC) module and a triple comparator module. The ADC module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speeds. The comparator module includes three analog comparators that are configurable for a wide range of operations.

- **CTMU Interface:** In addition to their other analog features, members of the PIC24FJ256DA210 family include the CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- Enhanced Parallel Master/Parallel Slave Port: There are general purpose I/O ports, which can be configured for parallel data communications. In this mode, the device can be master or slave on the communication bus. 4-bit, 8-bit and 16-bit data transfers, with up to 23 external address lines are supported in Master modes.

- Real-Time Clock and Calendar: (RTCC) This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

## 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including microcontrollers to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 Master Clear (MCLR) Pin

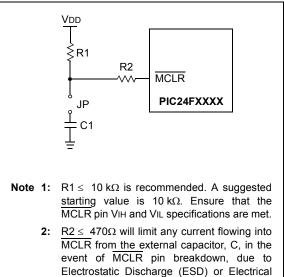

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

Overstress (EOS). Ensure that the MCLR pin

VIH and VIL specifications are met.

#### REGISTER 7-13: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 6 | <ul> <li>IC7IE: Input Capture Channel 7 Interrupt Enable bit</li> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5 | Unimplemented: Read as '0'                                                                                                                                      |

| bit 4 | INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup>                                                                                                          |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

| bit 3 | CNIE: Input Change Notification Interrupt Enable bit                                                                                                            |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

| bit 2 | CMIE: Comparator Interrupt Enable bit                                                                                                                           |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

| bit 1 | MI2C1IE: Master I2C1 Event Interrupt Enable bit                                                                                                                 |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

| bit 0 | SI2C1IE: Slave I2C1 Event Interrupt Enable bit                                                                                                                  |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

**Note 1:** If an external interrupt is enabled, the interrupt input must also be configured to an available RPx or RPIx pin. See **Section 10.4 "Peripheral Pin Select (PPS)**" for more information.

#### REGISTER 7-19: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

|                  | R/W-1                                                                                                                                        | R/W-0                                                                                                                                                                                                | R/W-0                                                                                                    | U-0                                      | R/W-1            | R/W-0           | R/W-0   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|-----------------|---------|

|                  | T1IP2                                                                                                                                        | T1IP1                                                                                                                                                                                                | T1IP0                                                                                                    |                                          | OC1IP2           | OC1IP1          | OC1IP0  |

| pit 15           |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 | bit     |

|                  |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          | <b>-</b>         | 5444.6          |         |

| U-0              | R/W-1                                                                                                                                        | R/W-0                                                                                                                                                                                                | R/W-0                                                                                                    | U-0                                      | R/W-1            | R/W-0           | R/W-0   |

|                  | IC1IP2                                                                                                                                       | IC1IP1                                                                                                                                                                                               | IC1IP0                                                                                                   |                                          | INT0IP2          | INT0IP1         | INT0IP0 |

| oit 7            |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 | bit     |

| Legend:          |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 |         |

| R = Readab       | ole bit                                                                                                                                      | W = Writable t                                                                                                                                                                                       | bit                                                                                                      | U = Unimple                              | mented bit, read | d as '0'        |         |

| -n = Value a     | It POR                                                                                                                                       | '1' = Bit is set                                                                                                                                                                                     |                                                                                                          | '0' = Bit is cle                         | eared            | x = Bit is unkr | nown    |

|                  |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 |         |

| bit 15           | Unimpleme                                                                                                                                    | ented: Read as '0                                                                                                                                                                                    | ,                                                                                                        |                                          |                  |                 |         |

| bit 14-12        | -                                                                                                                                            | Timer1 Interrupt                                                                                                                                                                                     |                                                                                                          |                                          |                  |                 |         |

|                  |                                                                                                                                              | rupt is priority 7 (h                                                                                                                                                                                | ,                                                                                                        | / interrupt)                             |                  |                 |         |

|                  | •                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                          | • •                                      |                  |                 |         |

|                  | •                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 |         |

|                  | 001 = Inter                                                                                                                                  | rupt is priority 1                                                                                                                                                                                   |                                                                                                          |                                          |                  |                 |         |

|                  | 000 = Inter                                                                                                                                  | rupt source is disa                                                                                                                                                                                  | abled                                                                                                    |                                          |                  |                 |         |

| bit 11           | Unimpleme                                                                                                                                    | ented: Read as '0                                                                                                                                                                                    | '                                                                                                        |                                          |                  |                 |         |

| oit 10-8         | OC1IP<2:0                                                                                                                                    | >: Output Compa                                                                                                                                                                                      | re Channel 1                                                                                             | Interrupt Priori                         | ty bits          |                 |         |

|                  | 111 — linterr                                                                                                                                | upt is priority 7 (h                                                                                                                                                                                 | iahest priority                                                                                          | (interrunt)                              |                  |                 |         |

|                  | $\perp \perp \perp = interi$                                                                                                                 | upt is priority 7 (i                                                                                                                                                                                 | ingricor priority                                                                                        | interrupt)                               |                  |                 |         |

|                  | 111 = Interr<br>•                                                                                                                            |                                                                                                                                                                                                      | ingricor priority                                                                                        | interrupt)                               |                  |                 |         |

|                  | •<br>•<br>•                                                                                                                                  |                                                                                                                                                                                                      | ignoot priority                                                                                          | menupty                                  |                  |                 |         |

|                  |                                                                                                                                              | rupt is priority 1                                                                                                                                                                                   |                                                                                                          | interrupt)                               |                  |                 |         |

|                  | 001 = Inter                                                                                                                                  |                                                                                                                                                                                                      |                                                                                                          | interrupt)                               |                  |                 |         |

| bit 7            | •<br>•<br>001 = Inter<br>000 = Inter                                                                                                         | rupt is priority 1                                                                                                                                                                                   | abled                                                                                                    | interrupt)                               |                  |                 |         |

|                  | •<br>•<br>001 = Inter<br>000 = Inter<br>Unimpleme                                                                                            | rupt is priority 1<br>rupt source is disa                                                                                                                                                            | abled                                                                                                    |                                          | ts               |                 |         |

| bit 7<br>bit 6-4 | •<br>•<br>001 = Inter<br>000 = Inter<br>Unimpleme<br>IC1IP<2:0>                                                                              | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0                                                                                                                                       | abled<br>, <sup>,</sup><br>hannel 1 Inter                                                                | rupt Priority bi                         | ts               |                 |         |

|                  | •<br>•<br>001 = Inter<br>000 = Inter<br>Unimpleme<br>IC1IP<2:0>                                                                              | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C                                                                                                                  | abled<br>, <sup>,</sup><br>hannel 1 Inter                                                                | rupt Priority bi                         | ts               |                 |         |

|                  | •<br>•<br>001 = Inter<br>000 = Inter<br>Unimpleme<br>IC1IP<2:0>                                                                              | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C                                                                                                                  | abled<br>, <sup>,</sup><br>hannel 1 Inter                                                                | rupt Priority bi                         | ts               |                 |         |

|                  | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                           | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1                                                                   | abled<br>,'<br>hannel 1 Inter<br>highest priority                                                        | rupt Priority bi                         | ts               |                 |         |

| bit 6-4          | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                           | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa                                            | abled<br>,,<br>hannel 1 Inter<br>nighest priority<br>abled                                               | rupt Priority bi                         | ts               |                 |         |

| bit 6-4<br>bit 3 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (f<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0                       | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled                                               | rupt Priority bi<br>/ interrupt)         | ts               |                 |         |

| bit 6-4<br>bit 3 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>>: External Intern | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled<br>,'<br>upt 0 Priority b                     | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

| bit 6-4<br>bit 3 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (f<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0                       | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled<br>,'<br>upt 0 Priority b                     | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

|                  | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>>: External Intern | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled<br>,'<br>upt 0 Priority b                     | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

| bit 6-4<br>bit 3 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>>: External Intern | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled<br>,'<br>upt 0 Priority b                     | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

| bit 6-4<br>bit 3 | 001 = Inten<br>000 = Inten<br>Unimpleme<br>IC1IP<2:0><br>111 = Inten<br>001 = Inten<br>Unimpleme<br>INT0IP<2:0<br>111 = Inten<br>001 = Inten | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>>: External Intern | abled<br>,,<br>hannel 1 Inter<br>highest priority<br>abled<br>,,<br>upt 0 Priority b<br>highest priority | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

## 10.1.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

### 10.1.2 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, each port pin can also be individually configured for either a digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

#### 10.1.3 CONFIGURING D+ AND D- PINS (RG2 AND RG3)

The input buffers of the RG2 and RG3 pins are by default, tri-stated. To use these pins as input pins, the UTRDIS bit (U1CNFG2<0>) should be set which enables the input buffers on these pins.

## 10.2 Configuring Analog Port Pins (ANSEL)

The ANSx and TRISx registers control the operation of the pins with analog function. Each port pin with analog function is associated with one of the ANS bits (see Register 10-1 through Register 10-7), which decides if the pin function should be analog or digital. Refer to Table 10-1 for detailed behavior of the pin for different ANSx and TRISx bit settings.

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

#### 10.2.1 ANALOG INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Pins that are used as digital only inputs are able to handle DC voltages of up to 5.5V, a level typical for digital logic circuits. In contrast, pins that also have analog input functions of any kind can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should always be avoided. Table 10-2 summarizes the input capabilities. Refer to **Section 30.1 "DC Characteristics"** for more details.

| Pin Function   | ANSx Setting | TRISx Setting | Comments                                                                                                                                   |

|----------------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Analog Input   | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Analog Output  | 1            | 1             | It is recommended to keep ANSx = 1.                                                                                                        |

| Digital Input  | 0            | 1             | Firmware must wait at least one instruction cycle<br>after configuring a pin as a digital input before a valid<br>input value can be read. |

| Digital Output | 0            | 0             | Make sure to disable the analog output function on the pin if any is present.                                                              |

TABLE 10-1: CONFIGURING ANALOG/DIGITAL FUNCTION OF AN I/O PIN

## TABLE 10-2: INPUT VOLTAGE LEVELS FOR PORT OR PIN TOLERATED DESCRIPTION INPUT

| Port or Pin                            | Tolerated Input | Description                              |  |  |

|----------------------------------------|-----------------|------------------------------------------|--|--|

| PORTA <sup>(1)</sup> <10:9, 7:6>       |                 |                                          |  |  |

| PORTB<15:0>                            |                 |                                          |  |  |

| PORTC <sup>(1)</sup> <15:12, 4>        |                 |                                          |  |  |

| PORTD<7:6>                             | VDD             | Only VDD input levels are tolerated.     |  |  |

| PORTE <sup>(1)</sup> <9>               |                 |                                          |  |  |

| PORTF<0>                               |                 |                                          |  |  |

| PORTG<9:6, 3:2>                        |                 |                                          |  |  |

| PORTA <sup>(1)</sup> <15:14, 5:0>      |                 |                                          |  |  |

| PORTC <sup>(1)</sup> <3:1>             |                 |                                          |  |  |

| PORTD <sup>(1)</sup> <15:8, 5:0>       |                 | Tolerates input levels above VDD, useful |  |  |

| PORTE <sup>(1)</sup> <8:0>             | 5.5V            | for most standard logic.                 |  |  |

| PORTF <sup>(1)</sup> <13:12, 8:7, 5:1> |                 |                                          |  |  |

| PORTG <sup>(1)</sup> <15:12, 1:0>      |                 |                                          |  |  |

**Note 1:** Not all of the pins of these PORTS are implemented in 64-pin devices (PIC24FJXXXDAX06); refer to the device pinout diagrams for the details.

#### 10.4.6 PERIPHERAL PIN SELECT REGISTERS

The PIC24FJ256DA210 family of devices implements a total of 37 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (21)

- Output Remappable Peripheral Registers (16)

#### Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.4.4.1 "Control Register Lock" for a specific command sequence.

#### REGISTER 10-8: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0           | U-0                                                                  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|---------------|----------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| —             | —                                                                    | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15        |                                                                      |        |        |        |        |        | bit 8  |

|               |                                                                      |        |        |        |        |        |        |

| U-0           | U-0                                                                  | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    |

| _             | -                                                                    | —      | —      | —      | —      | —      | —      |

| bit 7         |                                                                      |        |        |        |        |        | bit 0  |

|               |                                                                      |        |        |        |        |        |        |

| Legend:       |                                                                      |        |        |        |        |        |        |

| R = Readable  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |        |        |        |        |        |        |

| -n = Value at | t POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown       |        | iown   |        |        |        |        |

| bit 15-14 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 13-8  | INT1R<5:0>: Assign External Interrupt 1 (INT1) to Corresponding RPn or RPIn Pin bits |

| bit 7-0   | Unimplemented: Read as '0'                                                           |

### REGISTER 10-9: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                               | U-0 | R/W-1            | R/W-1                              | R/W-1                | R/W-1  | R/W-1              | R/W-1  |

|-----------------------------------|-----|------------------|------------------------------------|----------------------|--------|--------------------|--------|

| _                                 | _   | INT3R5           | INT3R4                             | INT3R3               | INT3R2 | INT3R1             | INT3R0 |

| bit 15                            |     |                  |                                    |                      |        | ·                  | bit    |

|                                   |     |                  |                                    |                      |        |                    |        |

| U-0                               | U-0 | R/W-1            | R/W-1                              | R/W-1                | R/W-1  | R/W-1              | R/W-1  |

| _                                 | _   | INT2R5           | INT2R4                             | INT2R3               | INT2R2 | INT2R1             | INT2R0 |

| bit 7                             |     | ·                |                                    |                      |        |                    | bit    |

|                                   |     |                  |                                    |                      |        |                    |        |

| Legend:                           |     |                  |                                    |                      |        |                    |        |

| R = Readable bit W = Writable bit |     | bit              | U = Unimplemented bit, read as '0' |                      |        |                    |        |

| -n = Value at I                   | POR | '1' = Bit is set |                                    | '0' = Bit is cleared |        | x = Bit is unknown |        |

| bit 15-14 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 13-8  | INT3R<5:0>: Assign External Interrupt 3 (INT3) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                           |

| bit 5-0   | INT2R<5:0>: Assign External Interrupt 2 (INT2) to Corresponding RPn or RPIn Pin bits |

#### REGISTER 10-16: RPINR10: PERIPHERAL PIN SELECT INPUT REGISTER 10

| -         -           bit 15         -           U-0         -           bit 7         - |       |       |       |       |       |       |

|------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| <br>bit 15                                                                               |       |       |       |       |       | bit 0 |

| <br>bit 15                                                                               | IC7R5 | IC7R4 | IC7R3 | IC7R2 | IC7R1 | IC7R0 |

| <u> </u>                                                                                 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|                                                                                          |       |       |       |       |       | DILO  |

|                                                                                          |       |       |       |       |       | bit 8 |

| •• ••                                                                                    | IC8R5 | IC8R4 | IC8R3 | IC8R2 | IC8R1 | IC8R0 |

| U-0 U-0                                                                                  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                    |

|-----------|-------------------------------------------------------------------------------|

| bit 13-8  | IC8R<5:0>: Assign Input Capture 8 (IC8) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                    |

| bit 5-0   | IC7R<5:0>: Assign Input Capture 7 (IC7) to Corresponding RPn or RPIn Pin bits |

### REGISTER 10-17: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | OCFBR5 | OCFBR4 | OCFBR3 | OCFBR2 | OCFBR1 | OCFBR0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 OCFBR<5:0>: Assign Output Compare Fault B (OCFB) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 OCFAR<5:0>: Assign Output Compare Fault A (OCFA) to Corresponding RPn or RPIn Pin bits

## REGISTER 10-26: RPINR27: PERIPHERAL PIN SELECT INPUT REGISTER 27

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

|        | —   | U4CTSR5 | U4CTSR4 | U4CTSR3 | U4CTSR2 | U4CTSR1 | U4CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|        | —   | U4RXR5  | U4RXR4  | U4RXR3  | U4RXR2  | U4RXR1  | U4RXR0  |

| bit 7  |     |         |         |         |         |         | bit 0   |

| bit 7 |

|-------|

|-------|

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 13-8  | U4CTSR<5:0>: Assign UART4 Clear to Send (U4CTS) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                            |

| bit 5-0   | U4RXR<5:0>: Assign UART4 Receive (U4RX) to Corresponding RPn or RPIn Pin bits         |

## **REGISTER 10-27: RPINR28: PERIPHERAL PIN SELECT INPUT REGISTER 28**

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | SCK3R5 | SCK3R4 | SCK3R3 | SCK3R2 | SCK3R1 | SCK3R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | —   | SDI3R5 | SDI3R4 | SDI3R3 | SDI3R2 | SDI3R1 | SDI3R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 SCK3R<5:0>: Assign SPI3 Clock Input (SCK3IN) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SDI3R<5:0>: Assign SPI3 Data Input (SDI3) to Corresponding RPn or RPIn Pin bits

## 14.0 OUTPUT COMPARE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 35. "Output Compare with Dedicated Timer" (DS39723). The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ256DA210 family feature all of the 9 independent output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events, and can produce pulse-width modulated waveforms for driving power applications.

Key features of the output compare module include:

- Hardware configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 31 user-selectable trigger/sync sources available

- Two separate period registers (a main register, OCxR, and a secondary register, OCxRS) for greater flexibility in generating pulses of varying widths

- Configurable for single pulse or continuous pulse generation on an output event, or continuous PWM waveform generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

## 14.1 General Operating Modes

#### 14.1.1 SYNCHRONOUS AND TRIGGER MODES

When the output compare module operates in a free-running mode, the internal 16-bit counter, OCxTMR, runs counts up continuously, wrapping around from 0xFFFF to 0x0000 on each overflow, with its period synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the period registers occurs.

In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the module's internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the counter to run.

Free-running mode is selected by default or any time that the SYNCSEL bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSEL bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSEL bits determine the sync/trigger source.

## 14.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-bit timer and duty cycle registers. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (OCx) provides the Least Significant 16 bits of the 32-bit register pairs and the even module (OCy) provides the Most Significant 16 bits. Wrap-arounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bit (OCxCON2<8>) for both modules. For more details on cascading, refer to the "*PIC24F Family Reference Manual*", **Section 35.** "**Output Compare with Dedicated Timer**".

## 17.1 UART Baud Rate Generator (BRG)

The UART module includes a dedicated, 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 17-1 shows the formula for computation of the baud rate with BRGH = 0.

## EQUATION 17-1: UART BAUD RATE WITH BRGH = $0^{(1,2)}$

Baud Rate =

$$\frac{FCY}{16 \cdot (UxBRG + 1)}$$

UxBRG =  $\frac{FCY}{16 \cdot Baud Rate} - 1$

**Note 1:** FCY denotes the instruction cycle clock frequency (FOSC/2).

**2:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 17-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 17-2 shows the formula for computation of the baud rate with BRGH = 1.

## EQUATION 17-2: UART BAUD RATE WITH BRGH = $1^{(1,2)}$

Baud Rate =

$$\frac{FCY}{4 \cdot (UxBRG + 1)}$$

UxBRG =  $\frac{FCY}{4 \cdot Baud Rate} - 1$

- **Note 1:** FCY denotes the instruction cycle clock frequency.

- **2:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FCY/4 (for UxBRG = 0) and the minimum baud rate possible is FCY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

## EXAMPLE 17-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

| Desired Baud Rate    | = FCY/(16 (BRGx + 1))                                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------------------------|

| Solving for BRGx Va  | lue:                                                                                                                 |

| BRGx<br>BRGx         | = ((FCY/Desired Baud Rate)/16) - 1<br>= ((4000000/9600)/16) - 1                                                      |

| BRGx                 | = 25                                                                                                                 |

| Calculated Baud Rate | = 4000000/(16(25+1)) = 9615                                                                                          |

| Error                | <ul> <li>= (Calculated Baud Rate – Desired Baud Rate)<br/>Desired Baud Rate</li> <li>= (9615 – 9600)/9600</li> </ul> |

| Note: Based or       | FCY = FOSC/2; Doze mode and PLL are disabled.                                                                        |

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 4 **RXINV:** Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode (4 BRG clock cycles per bit)

- 0 = Standard-Speed mode (16 BRG clock cycles per bit)

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Bit Selection bit

- 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

## 18.7 USB OTG Module Registers

There are a total of 37 memory mapped registers associated with the USB OTG module. They can be divided into four general categories:

- USB OTG Module Control (12)

- USB Interrupt (7)

- USB Endpoint Management (16)

- USB VBUS Power Control (2)

This total does not include the (up to) 128 BD registers in the BDT. Their prototypes, described in Register 18-1 and Register 18-2, are shown separately in **Section 18.2 "USB Buffer Descriptors and the BDT"**. With the exception of U1PWMCON and U1PWMRRS, all USB OTG registers are implemented in the Least Significant Byte of the register. Bits in the upper byte are unimplemented and have no function. Note that some registers are instantiated only in Host mode, while other registers have different bit instantiations and functions in Device and Host modes.

The registers described in the following sections are those that have bits with specific control and configuration features. The following registers are used for data or address values only:

- U1BDTP1: Specifies the 256-word page in data RAM used for the BDT; 8-bit value with bit 0 fixed as '0' for boundary alignment.

- U1FRML and U1FRMH: Contains the 11-bit byte counter for the current data frame.

- U1PWMRRS: Contains the 8-bit value for PWM duty cycle bits<15:8> and PWM period bits<7:0> for the VBUS boost assist PWM module.

### 18.7.4 USB VBUS POWER CONTROL REGISTER

### REGISTER 18-22: U1PWMCON: USB VBUS PWM GENERATOR CONTROL REGISTER

| R/W-0        | U-0                          | U-0                                          | U-0              | U-0                                | U-0               | R/W-0              | R/W-0 |  |  |  |  |

|--------------|------------------------------|----------------------------------------------|------------------|------------------------------------|-------------------|--------------------|-------|--|--|--|--|

| PWMEN        |                              | —                                            | —                | —                                  | —                 | PWMPOL             | CNTEN |  |  |  |  |

| bit 15       |                              |                                              |                  | -                                  |                   |                    | bit 8 |  |  |  |  |

|              |                              |                                              |                  |                                    |                   |                    |       |  |  |  |  |

| U-0          | U-0                          | U-0                                          | U-0              | U-0                                | U-0               | U-0                | U-0   |  |  |  |  |

|              | —                            | —                                            | _                | —                                  | —                 | —                  | —     |  |  |  |  |

| bit 7        |                              |                                              |                  |                                    |                   |                    | bit 0 |  |  |  |  |

|              |                              |                                              |                  |                                    |                   |                    |       |  |  |  |  |

| Legend:      |                              |                                              |                  |                                    |                   |                    |       |  |  |  |  |

| R = Readab   | ole bit                      | W = Writable                                 | bit              | U = Unimplemented bit, read as '0' |                   |                    |       |  |  |  |  |

| -n = Value a | it POR                       | '1' = Bit is set                             |                  | '0' = Bit is clea                  | ared              | x = Bit is unknown |       |  |  |  |  |

|              |                              |                                              |                  |                                    |                   |                    |       |  |  |  |  |

| bit 15       | PWMEN: PW                    | M Enable bit                                 |                  |                                    |                   |                    |       |  |  |  |  |

|              | 1 = PWM generator is enabled |                                              |                  |                                    |                   |                    |       |  |  |  |  |

|              | 0 = PWM ger                  | nerator is disab                             | led; output is h | eld in the Rese                    | et state specifie | d by PWMPOL        |       |  |  |  |  |

| bit 14-10    | Unimplemen                   | ted: Read as '                               | )'               |                                    |                   |                    |       |  |  |  |  |

| bit 9        | PWMPOL: P\                   | NM Polarity bit                              |                  |                                    |                   |                    |       |  |  |  |  |

|              | 1 = PWM out                  | 1 = PWM output is active-low and resets high |                  |                                    |                   |                    |       |  |  |  |  |

|              | 0 = PWM out                  | 0 = PWM output is active-high and resets low |                  |                                    |                   |                    |       |  |  |  |  |

| bit 8        | CNTEN: PWN                   | CNTEN: PWM Counter Enable bit                |                  |                                    |                   |                    |       |  |  |  |  |

|              | 1 = Counter i                | s enabled                                    |                  |                                    |                   |                    |       |  |  |  |  |

|              | 0 = Counter i                | s disabled                                   |                  |                                    |                   |                    |       |  |  |  |  |

| bit 7-0      | Unimplemen                   | ted: Read as '                               | )'               |                                    |                   |                    |       |  |  |  |  |

|              |                              |                                              |                  |                                    |                   |                    |       |  |  |  |  |

####

| R/W-0           | R/W-0                                                                 | R/W-0                                                                              | R/W-0                              | R/W-0                              | R/W-0                         | R/W-0, HSC                          | R/W-0, HSC   |

|-----------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------|------------------------------------|-------------------------------|-------------------------------------|--------------|

| ALRMEN          | CHIME                                                                 | AMASK3                                                                             | AMASK2                             | AMASK1                             | AMASK0                        | ALRMPTR1                            | ALRMPTRO     |

| bit 15          |                                                                       |                                                                                    |                                    |                                    |                               |                                     | bit          |

| R/W-0, HSC      | R/W-0, HSC                                                            | R/W-0, HSC                                                                         | R/W-0, HSC                         | R/W-0, HSC                         | R/W-0, HSC                    | R/W-0, HSC                          | R/W-0, HSC   |

| ARPT7           | ARPT6                                                                 | ARPT5                                                                              | ARPT4                              | ARPT3                              | ARPT2                         | ARPT1                               | ARPT0        |

| bit 7           |                                                                       |                                                                                    |                                    |                                    |                               |                                     | bit          |

| Legend:         |                                                                       | HSC = Hardw                                                                        | are Settable/C                     | learable bit                       |                               |                                     |              |

| R = Readable    | bit                                                                   | W = Writable                                                                       | bit                                | U = Unimplem                       | nented bit, read              | l as '0'                            |              |

| -n = Value at I | POR                                                                   | '1' = Bit is set                                                                   |                                    | '0' = Bit is clea                  |                               | x = Bit is unkr                     | iown         |

| bit 15          | ALRMEN: Ala                                                           | arm Enable bit                                                                     |                                    |                                    |                               |                                     |              |

|                 |                                                                       | •                                                                                  | ed automatica                      | lly after an ala                   | rm event whe                  | never ARPT<7                        | :0> = 00h an |

|                 | CHIME =<br>0 = Alarm is o                                             | ,                                                                                  |                                    |                                    |                               |                                     |              |

| oit 14          | CHIME: Chim                                                           |                                                                                    |                                    |                                    |                               |                                     |              |

|                 |                                                                       | •                                                                                  |                                    | allowed to roll<br>p once they rea |                               | to FFh                              |              |

| oit 13-10       |                                                                       |                                                                                    | Configuration b                    |                                    |                               |                                     |              |

|                 |                                                                       | a month<br>a week<br>a day<br>hour<br>10 minutes<br>minute<br>10 seconds<br>second |                                    | ed for February                    | r 29 <sup>th</sup> , once eve | ery 4 years)                        |              |

| oit 9-8         | -                                                                     |                                                                                    | ue Reaister Wir                    | ndow Pointer bi                    | its                           |                                     |              |

|                 | Points to the co                                                      | orresponding A<br>R<1:0> value d<br><u>i:8&gt;:</u><br>mented<br>NTH<br>D          | arm Value regis                    | sters when read                    | ing the ALRMV                 | ALH and ALRM'<br>.H until it reache |              |

|                 | ALRMVAL<7:<br>11 = Unimple<br>10 = ALRMD/<br>01 = ALRMH<br>00 = ALRMS | mented<br>AY<br>R                                                                  |                                    |                                    |                               |                                     |              |

| bit 7-0         |                                                                       | -                                                                                  | Counter Value I<br>eat 255 more ti |                                    |                               |                                     |              |

|                 | <br>00000000 =                                                        | Alarm will not                                                                     | repeat                             |                                    | s prevented fro               | m rolling over fr                   | om 00h to FF |

The counter decrements on any alarm event. The counter is prevented from rolling over from 00h to FFh unless CHIME = 1.

#### REGISTER 23-7: AD1CSSH: A/D INPUT SCAN SELECT REGISTER (HIGH)

| R/W-0<br>SSL21 <sup>(1)</sup>                                                                                                                                                     | <br>R/W-0<br>CSSL20 <sup>(1)</sup>                          | CSSL27<br>R/W-0<br>CSSL19 <sup>(1)</sup><br>U = Unimplem                                                                                     | CSSL26<br>R/W-0<br>CSSL18 <sup>(1)</sup>                                                                                                                                                                    | CSSL25<br>R/W-0<br>CSSL17 <sup>(1)</sup>                                                                                                                                                  | CSSL24<br>bit 8<br>R/W-0<br>CSSL16 <sup>(1)</sup><br>bit 0                                                                                                                                                                 |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|