Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                |

| Number of I/O              | 52                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 8                                                                        |

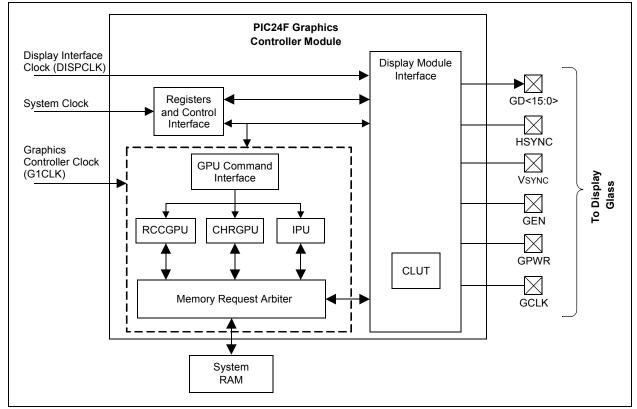

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

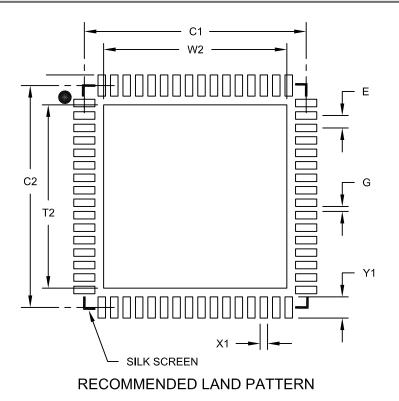

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256da106-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                    | Pin Number            |                                           |     | Immunt          | Description                                                 |  |  |  |  |

|----------|--------------------|-----------------------|-------------------------------------------|-----|-----------------|-------------------------------------------------------------|--|--|--|--|

| Function | 64-Pin<br>TQFP/QFN | 100-Pin<br>TQFP       | 121-Pin<br>BGA                            | I/O | Input<br>Buffer |                                                             |  |  |  |  |

| TCK      | 27                 | 38                    | J6                                        | Ι   | ST              | JTAG Test Clock Input.                                      |  |  |  |  |

| TDI      | 28                 | 60                    | G11                                       | I   | ST              | JTAG Test Data Input.                                       |  |  |  |  |

| TDO      | 24                 | 61                    | G9                                        | 0   | _               | JTAG Test Data Output.                                      |  |  |  |  |

| TMS      | 23                 | 17                    | G3                                        | Ι   | ST              | JTAG Test Mode Select Input.                                |  |  |  |  |

| USBID    | 33                 | 51                    | K10                                       | Ι   | ST              | USB OTG ID (OTG mode only).                                 |  |  |  |  |

| USBOEN   | 12                 | 21                    | H2                                        | 0   |                 | USB Output Enable Control (for external transceiver).       |  |  |  |  |

| VBUS     | 34                 | 54                    | H8                                        | Ι   | ANA             | USB Voltage, Host mode (5V).                                |  |  |  |  |

| VBUSCHG  | 49                 | 76                    | A11                                       | 0   |                 | External USB VBUS Charge Output.                            |  |  |  |  |

| VBUSON   | 11                 | 20                    | H1                                        | 0   |                 | USB OTG External Charge Pump Control.                       |  |  |  |  |

| VBUSST   | 58                 | 87                    | B6                                        | I   | ANA             | USB OTG Internal Charge Pump Feedback Control.              |  |  |  |  |

| VBUSVLD  | 58                 | 87                    | B6                                        | I   | ST              | USB VBUS Boost Generator, Comparator Input 1.               |  |  |  |  |

| VCAP     | 56                 | 85                    | B7                                        | Р   |                 | External Filter Capacitor Connection (regulator enabled).   |  |  |  |  |

| VCMPST1  | 58                 | 87                    | B6                                        | Ι   | ST              | USB VBUS Boost Generator, Comparator Input 1.               |  |  |  |  |

| VCMPST2  | 59                 | 88                    | A6                                        | Ι   | ST              | USB VBUS Boost Generator, Comparator Input 2.               |  |  |  |  |

| VCPCON   | 49                 | 76                    | A11                                       | 0   |                 | USB OTG VBUS PWM/Charge Output.                             |  |  |  |  |

| Vdd      | 10, 26, 38         | 2, 16, 37,<br>46, 62  | C2, C9, F8,<br>G5, H6, K8,<br>H4, E5      | Р   | —               | Positive Supply for Peripheral Digital Logic and I/O Pins.  |  |  |  |  |

| VMIO     | 14                 | 23                    | J2                                        | Ι   | ST              | USB Differential Minus Input/Output (external transceiver). |  |  |  |  |

| VPIO     | 13                 | 22                    | J1                                        | Ι   | ST              | USB Differential Plus Input/Output (external transceiver).  |  |  |  |  |

| VREF-    | 15                 | 28, 24 <sup>(4)</sup> | L2, K1 <sup>(4)</sup>                     | I   | ANA             | A/D and Comparator Reference Voltage (low) Input.           |  |  |  |  |

| VREF+    | 16                 | 29, 25 <sup>(4)</sup> | K3, K2 <sup>(4)</sup>                     | Ι   | ANA             | A/D and Comparator Reference Voltage (high) Input.          |  |  |  |  |

| Vss      | 9, 25, 41          | 15, 36, 45,<br>65, 75 | B10, F5,<br>F10, G6,<br>G7, H3, D4,<br>D5 | Ρ   | —               | Ground Reference for Logic and I/O Pins.                    |  |  |  |  |

| VSYNC    | 1                  | 96                    | C3                                        | 0   |                 | Graphics Display Vertical Sync Pulse.                       |  |  |  |  |

| VUSB     | 35                 | 55                    | H9                                        | Р   | —               | USB Voltage (3.3V).                                         |  |  |  |  |

ANA = Analog level input/output  $I^2C^{TM} = I^2C/SMBus input buffer$

**Note 1:** The alternate EPMP pins are selected when the  $\overline{\text{ALTPMP}}$  (CW3<12>) bit is programmed to '0'.

2: The PMSC2 signal will replace the PMA15 signal on the 15-pin PMA when CSF<1:0> = 01 or 10.

3: The PMCS1 signal will replace the PMA14 signal on the 14-pin PMA when CSF<1:0> = 10.

4: The alternate VREF pins selected when the ALTVREF (CW1<5>) bit is programmed to '0'.

#### TABLE 4-26: ENHANCED PARALLEL MASTER/SLAVE PORT REGISTER MAP<sup>(1)</sup>

| File<br>Name | Addr | Bit 15                                    | Bit 14                                     | Bit 13  | Bit 12      | Bit 11         | Bit 10  | Bit 9   | Bit 8   | Bit 7                         | Bit 6   | Bit 5   | Bit 4       | Bit 3       | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|------|-------------------------------------------|--------------------------------------------|---------|-------------|----------------|---------|---------|---------|-------------------------------|---------|---------|-------------|-------------|---------|---------|---------|---------------|

| PMCON1       | 0600 | PMPEN                                     | PMPEN – PSIDL ADRMUX1 ADRMUX0 – MODE1 MODE |         |             |                |         |         |         | CSF1                          | CSF0    | ALP     | ALMODE      | —           | BUSKEEP | IRQM1   | IRQM0   | 0000          |

| PMCON2       | 0602 | BUSY                                      | _                                          | ERROR   | TIMEOUT     | AMREQ          | CURMST  | MSTSEL1 | MSTSEL0 | RADDR23                       | RADDR22 | RADDR21 | RADDR20     | RADDR19     | RADDR18 | RADDR17 | RADDR16 | 0000          |

| PMCON3       | 0604 | PTWREN                                    | PTRDEN                                     | PTBE1EN | PTBE0EN     | _              | AWAITM1 | AWAITM0 | AWAITE  | _                             | PTEN22  | PTEN21  | PTEN20      | PTEN19      | PTEN18  | PTEN17  | PTEN16  | 0000          |

| PMCON4       | 0606 | PTEN15                                    | PTEN14                                     | PTEN13  | PTEN12      | PTEN11         | PTEN10  | PTEN9   | PTEN8   | PTEN7                         | PTEN6   | PTEN5   | PTEN4       | PTEN3       | PTEN2   | PTEN1   | PTEN0   | 0000          |

| PMCS1CF      | 0608 | CSDIS                                     | CSP                                        | CSPTEN  | BEP         | _              | WRSP    | RDSP    | SM      | ACKP                          | PTSZ1   | PTSZ0   | _           |             | —       | _       | _       | 0000          |

| PMCS1BS      | 060A | BASE23                                    | BASE22                                     | BASE21  | BASE20      | BASE19         | BASE18  | BASE17  | BASE16  | BASE15                        | _       | _       | _           | BASE11      | _       | _       | _       | 0200          |

| PMCS1MD      | 060C | ACKM1 ACKM0 AMWAIT2 AMWAIT1 AMWAIT0 — — — |                                            |         |             |                |         |         | _       | DWAITB1                       | DWAITB0 | DWAITM3 | DWAITM2     | DWAITM1     | DWAITM0 | DWAITE1 | DWAITE0 | 0000          |

| PMCS2CF      | 060E | CSDIS                                     | CSP                                        | CSPTEN  | BEP         | _              | WRSP    | RDSP    | SM      | ACKP                          | PTSZ1   | PTSZ0   | _           |             | —       | _       | _       | 0000          |

| PMCS2BS      | 0610 | BASE23                                    | BASE22                                     | BASE21  | BASE20      | BASE19         | BASE18  | BASE17  | BASE16  | BASE15                        | _       | _       | _           | BASE11      | _       | _       | _       | 0600          |

| PMCS2MD      | 0612 | ACKM1                                     | ACKM0                                      | AMWAIT2 | AMWAIT1     | AMWAIT0        | _       | _       | _       | DWAITB1                       | DWAITB0 | DWAITM3 | DWAITM2     | DWAITM1     | DWAITM0 | DWAITE1 | DWAITE0 | 0000          |

| PMDOUT1      | 0614 |                                           |                                            | EF      | MP Data Out | Register 1<15: | 8>      |         |         | EPMP Data Out Register 1<7:0> |         |         |             |             |         |         |         | xxxx          |

| PMDOUT2      | 0616 |                                           |                                            | EF      | MP Data Out | Register 2<15: | 8>      |         |         |                               |         | EP      | MP Data Out | Register 2< | 7:0>    |         |         | xxxx          |

| PMDIN1       | 0618 |                                           | EPMP Data In Register 1<15:8>              |         |             |                |         |         |         | EPMP Data In Register 1<7:0>  |         |         |             |             |         |         |         | xxxx          |

| PMDIN2       | 061A | EPMP Data In Register 2<15:8>             |                                            |         |             |                |         |         |         | EPMP Data In Register 2<7:0>  |         |         |             |             |         |         |         | xxxx          |

| PMSTAT       | 061C | IBF                                       | IBOV                                       | _       | —           | IB3F           | IB2F    | IB1F    | IB0F    | OBE                           | OBUF    | —       | _           | OB3E        | OB2E    | OB1E    | OB0E    | 008F          |

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note

1:

Unimplemented in 64-pin devices, read as '0'.

#### TABLE 4-27: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                                             | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9    | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|----------------------------------------------------|---------|---------|---------|--------|----------|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL      | 0620 |        | Alarm Value Register Window Based on ALRMPTR<1:0>  |         |         |         |        |          |          |       |       |       | xxxx  |       |       |       |       |               |

| ALCFGRPT     | 0622 | ALRMEN | CHIME                                              | AMASK3  | AMASK2  | AMASK1  | AMASK0 | ALRMPTR1 | ALRMPTR0 | ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| RTCVAL       | 0624 |        | RTCC Value Register Window Based on RTCPTR<1:0> xx |         |         |         |        |          |          |       |       | xxxx  |       |       |       |       |       |               |

| RCFGCAL      | 0626 | RTCEN  |                                                    | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPTR1  | RTCPTR0  | CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | (Note 1)      |

Legend:

- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note

1:

The status of the RCFGCAL register on POR is '0000' and on other Resets is unchanged.

### TABLE 4-30: PERIPHERAL PIN SELECT REGISTER MAP (CONTINUED)

| File<br>Name          | Addr | Bit 15 | Bit 14 | Bit 13                | Bit 12                | Bit 11                | Bit 10                | Bit 9                 | Bit 8                 | Bit 7 | Bit 6 | Bit 5                 | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | All<br>Resets |

|-----------------------|------|--------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------|

| RPOR0                 | 06C0 | _      |        | RP1R5                 | RP1R4                 | RP1R3                 | RP1R2                 | RP1R1                 | RP1R0                 | —     | —     | RP0R5                 | RP0R4                 | RP0R3                 | RP0R2                 | RP0R1                 | RP0R0                 | 0000          |

| RPOR1                 | 06C2 | -      | _      | RP3R5                 | RP3R4                 | RP3R3                 | RP3R2                 | RP3R1                 | RP3R0                 | _     | _     | RP2R5                 | RP2R4                 | RP2R3                 | RP2R2                 | RP2R1                 | RP2R0                 | 0000          |

| RPOR2                 | 06C4 | -      | _      | RP5R5 <sup>(1)</sup>  | RP5R4 <sup>(1)</sup>  | RP5R3 <sup>(1)</sup>  | RP5R2 <sup>(1)</sup>  | RP5R1 <sup>(1)</sup>  | RP5R0 <sup>(1)</sup>  | _     | _     | RP4R5                 | RP4R4                 | RP4R3                 | RP4R2                 | RP4R1                 | RP4R0                 | 0000          |

| RPOR3                 | 06C6 | _      | _      | RP7R5                 | RP7R4                 | RP7R3                 | RP7R2                 | RP7R1                 | RP7R0                 | _     | _     | RP6R5                 | RP6R4                 | RP6R3                 | RP6R2                 | RP6R1                 | RP6R0                 | 0000          |

| RPOR4                 | 06C8 | -      | _      | RP9R5                 | RP9R4                 | RP9R3                 | RP9R2                 | RP9R1                 | RP9R0                 | _     | _     | RP8R5                 | RP8R4                 | RP8R3                 | RP8R2                 | RP8R1                 | RP8R0                 | 0000          |

| RPOR5                 | 06CA | -      | _      | RP11R5                | RP11R4                | RP11R3                | RP11R2                | RP11R1                | RP11R0                | _     | _     | RP10R5                | RP10R4                | RP10R3                | RP10R2                | RP10R1                | RP10R0                | 0000          |

| RPOR6                 | 06CC | _      | _      | RP13R5                | RP13R4                | RP13R3                | RP13R2                | RP13R1                | RP13R0                | _     | _     | RP12R5                | RP12R4                | RP12R3                | RP12R2                | RP12R1                | RP12R0                | 0000          |

| RPOR7                 | 06CE |        | _      | RP15R5 <sup>(1)</sup> | RP15R4 <sup>(1)</sup> | RP15R3 <sup>(1)</sup> | RP15R2 <sup>(1)</sup> | RP15R1 <sup>(1)</sup> | RP15R0 <sup>(1)</sup> | _     | _     | RP14R5                | RP14R4                | RP14R3                | RP14R2                | RP14R1                | RP14R0                | 0000          |

| RPOR8                 | 06D0 | -      | _      | RP17R5                | RP17R4                | RP17R3                | RP17R2                | RP17R1                | RP17R0                | _     | _     | RP16R5                | RP16R4                | RP16R3                | RP16R2                | RP16R1                | RP16R0                | 0000          |

| RPOR9                 | 06D2 | _      | _      | RP19R5                | RP19R4                | RP19R3                | RP19R2                | RP19R1                | RP19R0                | _     | _     | RP18R5                | RP18R4                | RP18R3                | RP18R2                | RP18R1                | RP18R0                | 0000          |

| RPOR10                | 06D4 |        | _      | RP21R5                | RP21R4                | RP21R3                | RP21R2                | RP21R1                | RP21R0                | _     | _     | RP20R5                | RP20R4                | RP20R3                | RP20R2                | RP20R1                | RP20R0                | 0000          |

| RPOR11                | 06D6 | -      | _      | RP23R5                | RP23R4                | RP23R3                | RP23R2                | RP23R1                | RP23R0                | _     | _     | RP22R5                | RP22R4                | RP22R3                | RP22R2                | RP22R1                | RP22R0                | 0000          |

| RPOR12                | 06D8 | _      | _      | RP25R5                | RP25R4                | RP25R3                | RP25R2                | RP25R1                | RP25R0                | _     | _     | RP24R5                | RP24R4                | RP24R3                | RP24R2                | RP24R1                | RP24R0                | 0000          |

| RPOR13                | 06DA | -      | _      | RP27R5                | RP27R4                | RP27R3                | RP27R2                | RP27R1                | RP27R0                | _     | _     | RP26R5                | RP26R4                | RP26R3                | RP26R2                | RP26R1                | RP26R0                | 0000          |

| RPOR14                | 06DC | _      | _      | RP29R5                | RP29R4                | RP29R3                | RP29R2                | RP29R1                | RP29R0                | _     | _     | RP28R5                | RP28R4                | RP28R3                | RP28R2                | RP28R1                | RP28R0                | 0000          |

| RPOR15 <sup>(1)</sup> | 06DE | _      | _      | RP31R5 <sup>(1)</sup> | RP31R4 <sup>(1)</sup> | RP31R3 <sup>(1)</sup> | RP31R2 <sup>(1)</sup> | RP31R1 <sup>(1)</sup> | RP31R0 <sup>(1)</sup> | _     | _     | RP30R5 <sup>(1)</sup> | RP30R4 <sup>(1)</sup> | RP30R3 <sup>(1)</sup> | RP30R2 <sup>(1)</sup> | RP30R1 <sup>(1)</sup> | RP30R0 <sup>(1)</sup> | 0000          |

Legend:

-- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note

1:

Bits are unimplemented in 64-pin devices; read as '0'.

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are described in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

Note: Only table read operations will execute in the configuration memory space, where Device IDs are located. Table write operations are not allowed.

|                | \$20-\$                                         | grann Spacce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78:098%<br>[]2 |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                | 23 34 0 00000h<br>020000h<br>030000h<br>800000h | 23       16       8       0         00000000       00000000       00000000       00000000         000000000       00000000       00000000       00000000         Phantom' Byte       (Phantom' Byte       00000000       00000000         00000000       00000000       00000000       00000000         Phantom' Byte       00000000       00000000       00000000         00000000       00000000       00000000       00000000         000000000       000000000       00000000       00000000         000000000       00000000       00000000       00000000         000000000       00000000       000000000       00000000         000000000       00000000       00000000       00000000         000000000       00000000       00000000       00000000         00000000000       000000000       000000000       000000000         00000000000000       00000000000       0000000000000       000000000000000000000000000000000000 |

#### FIGURE 4-9: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| <b>REGISTER 5-1:</b> NVMCON: FLASH MEMORY CONTROL REGISTER |

|------------------------------------------------------------|

|------------------------------------------------------------|

| R/S-0, HC(   | 1) R/W-0 <sup>(1)</sup>  | R-0, HSC <sup>(1)</sup>                                                              | U-0                           | U-0                               | U-0                                 | U-0                     | U-0                   |

|--------------|--------------------------|--------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|-------------------------------------|-------------------------|-----------------------|

| WR           | WREN                     | WRERR                                                                                | _                             | _                                 | _                                   | _                       | _                     |

| bit 15       |                          |                                                                                      |                               |                                   |                                     |                         | bit                   |

| U-0          | R/W-0 <sup>(1)</sup>     | U-0                                                                                  | U-0                           | R/W-0 <sup>(1)</sup>              | R/W-0 <sup>(1)</sup>                | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>  |

|              | ERASE                    |                                                                                      |                               | NVMOP3 <sup>(2)</sup>             | NVMOP2 <sup>(2)</sup>               | NVMOP1 <sup>(2)</sup>   | NVMOP0 <sup>(2)</sup> |

| bit 7        |                          |                                                                                      |                               |                                   | 1                                   | 1                       | bit                   |

| Legend:      |                          | S = Settable bi                                                                      | t                             | HSC = Hardw                       | are Settable/C                      | learable bit            |                       |

| R = Readat   | ole bit                  | W = Writable b                                                                       | it                            | U = Unimplen                      | nented bit, read                    | l as '0'                |                       |

| -n = Value a | at POR                   | '1' = Bit is set                                                                     |                               | '0' = Bit is clea                 | ared                                | x = Bit is unkr         | nown                  |

| HC = Hardv   | ware Clearable b         | vit                                                                                  |                               |                                   |                                     |                         |                       |

| bit 15       | cleared<br>0 = Program   | a Flash memory<br>by hardware onc<br>or erase operati<br>e Enable bit <sup>(1)</sup> | e the operatio                | on is complete                    | n; the operatio                     | n is self-timed         | and the bit i         |

| bit 14       | 1 = Enable I             | e Enable bit <sup>ver</sup><br>Flash program/er<br>lash program/era                  |                               |                                   |                                     |                         |                       |

| bit 13       |                          | ite Sequence Err                                                                     | -                             |                                   |                                     |                         |                       |

|              | automat                  | oper program o<br>ically on any set<br>gram or erase op                              | attempt of the                | e WR bit)                         | t or terminatic                     | n has occurre           | ed (bit is se         |

| bit 12-7     | Unimpleme                | nted: Read as '0                                                                     | 2                             |                                   |                                     |                         |                       |

| bit 6        | ERASE: Era               | se/Program Enal                                                                      | ble bit <sup>(1)</sup>        |                                   |                                     |                         |                       |

|              |                          | the erase operate<br>the program operate                                             |                               |                                   |                                     |                         | nd                    |

| bit 5-4      | Unimpleme                | nted: Read as '0                                                                     | ,                             |                                   |                                     |                         |                       |

| bit 3-0      |                          | >: NVM Operation                                                                     |                               |                                   |                                     |                         |                       |

|              | 0011 = Mer<br>0010 = Mer | nory bulk erase o<br>nory word progra<br>nory page erase<br>nory row prograr         | am operation<br>operation (Ef | (ERASE = 0) or<br>RASE = 1) or no | r no operation (<br>o operation (EF | ERASE = 1)<br>RASE = 0) |                       |

|              |                          | nly be reset on P                                                                    |                               |                                   |                                     |                         |                       |

|              |                          | ations of NVMOP                                                                      |                               | •                                 |                                     |                         |                       |

| 3.           | Available in ICSI        | P™ mode only re                                                                      | eter to the dev               | /ice programmi                    | ng specification                    | ו                       |                       |

3: Available in ICSP<sup>™</sup> mode only; refer to the device programming specification.

RCON: RESET CONTROL REGISTER<sup>(1)</sup>

#### R/W-0. HS R/W-0. HS U-0 U-0 U-0 U-0 R/W-0. HS R/W-0 TRAPR IOPUWR VREGS<sup>(3)</sup> CM bit 15 bit 8 R/W-0, HS R/W-0, HS R/W-0, HS R/W-0, HS R/W-0, HS R/W-0. HS R/W-1, HS R/W-1, HS SWDTEN<sup>(2)</sup> EXTR SWR WDTO SLEEP IDLE BOR POR bit 7 bit 0 Legend: HS = Hardware Settable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 15 TRAPR: Trap Reset Flag bit 1 = A Trap Conflict Reset has occurred 0 = A Trap Conflict Reset has not occurred bit 14 IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit 1 = An illegal opcode detection, an illegal address mode or uninitialized W register is used as an Address Pointer and caused a Reset 0 = An illegal opcode or uninitialized W Reset has not occurred bit 13-10 Unimplemented: Read as '0' bit 9 CM: Configuration Word Mismatch Reset Flag bit 1 = A Configuration Word Mismatch Reset has occurred 0 = A Configuration Word Mismatch Reset has not occurred bit 8 VREGS: Voltage Regulator Standby Enable bit<sup>(3)</sup> 1 = Program memory and regulator remain active during Sleep/Idle 0 = Program memory power is removed and regulator goes to standby during Seep/Idle bit 7 EXTR: External Reset (MCLR) Pin bit 1 = A Master Clear (pin) Reset has occurred 0 = A Master Clear (pin) Reset has not occurred bit 6 SWR: Software Reset (Instruction) Flag bit 1 = A RESET instruction has been executed 0 = A RESET instruction has not been executed SWDTEN: Software Enable/Disable of WDT bit<sup>(2)</sup> bit 5 1 = WDT is enabled 0 = WDT is disabled bit 4 WDTO: Watchdog Timer Time-out Flag bit 1 = WDT time-out has occurred 0 = WDT time-out has not occurred bit 3 SLEEP: Wake From Sleep Flag bit 1 = Device has been in Sleep mode 0 = Device has not been in Sleep mode Note 1: All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset. 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting. 3: Re-enabling the regulator after it enters Standby mode will add a delay, TVREG, when waking up from Sleep. Applications that do not use the voltage regulator should set this bit to prevent this delay from

**REGISTER 6-1:**

occurring.

#### REGISTER 7-12: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

| U-0         | U-0          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|-----------------|--------|

| —           |              | AD1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | U1TXIE           | U1RXIE           | SPI1IE          | SPF1IE          | T3IE   |

| oit 15      |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                  |                 |                 | bit 8  |

| DAMA        | DANO         | DAMO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11.0             | DAMA             | DAMA            | DAALO           |        |

| R/W-0       | R/W-0        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | U-0              | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

| T2IE        | OC2IE        | IC2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                | T1IE             | OC1IE           | IC1IE           | INT0IE |

| oit 7       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                  |                 |                 | bit    |

| Legend:     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                  |                 |                 |        |

| R = Readab  | le bit       | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit              | U = Unimpler     | nented bit, rea | d as '0'        |        |

| n = Value a | t POR        | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  | '0' = Bit is cle | ared            | x = Bit is unkn | own    |

|             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - 1              |                  |                 |                 |        |

| bit 15-14   | •            | nted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                  |                 |                 |        |

| bit 13      |              | Conversion Cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                | t Enable bit     |                 |                 |        |

|             |              | t request is enal<br>t request is not (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |                  |                 |                 |        |

| bit 12      | •            | RT1 Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  | ole bit          |                 |                 |        |

|             |              | t request is enal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                |                  |                 |                 |        |

|             |              | t request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                  |                 |                 |        |

| bit 11      | U1RXIE: UA   | RT1 Receiver II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nterrupt Enable  | bit              |                 |                 |        |

|             |              | t request is enal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                  |                 |                 |        |

|             | •            | t request is not o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                  |                 |                 |        |

| bit 10      |              | 1 Transfer Com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | nable bit        |                 |                 |        |

|             |              | t request is enal<br>t request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |                  |                 |                 |        |

| bit 9       | •            | 1 Fault Interrup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                  |                 |                 |        |

|             |              | t request is enal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                  |                 |                 |        |

|             |              | t request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                  |                 |                 |        |

| bit 8       | T3IE: Timer3 | B Interrupt Enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | le bit           |                  |                 |                 |        |

|             |              | t request is enal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                  |                 |                 |        |

|             |              | t request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                  |                 |                 |        |

| oit 7       |              | 2 Interrupt Enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                  |                 |                 |        |

|             |              | t request is enal<br>t request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |                  |                 |                 |        |

| oit 6       | -            | out Compare Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | ot Enable bit    |                 |                 |        |

|             | -            | t request is enal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | pt               |                 |                 |        |

|             |              | t request is not e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                  |                 |                 |        |

| bit 5       | IC2IE: Input | Capture Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | el 2 Interrupt E | nable bit        |                 |                 |        |

|             |              | t request is enal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                  |                 |                 |        |

|             | •            | t request is not o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                  |                 |                 |        |

| pit 4       | •            | nted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                  |                 |                 |        |

| bit 3       |              | I Interrupt Enab<br>t request is enal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |                  |                 |                 |        |

|             |              | t request is enaited to the terminal t |                  |                  |                 |                 |        |

| bit 2       | -            | out Compare Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | pt Enable bit    |                 |                 |        |

|             | -            | t request is enal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |                  |                 |                 |        |

|             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                  |                 |                 |        |

#### REGISTER 7-13: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 6 | <ul> <li>IC7IE: Input Capture Channel 7 Interrupt Enable bit</li> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5 | Unimplemented: Read as '0'                                                                                                                                      |

| bit 4 | INT1IE: External Interrupt 1 Enable bit <sup>(1)</sup>                                                                                                          |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

| bit 3 | CNIE: Input Change Notification Interrupt Enable bit                                                                                                            |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

| bit 2 | CMIE: Comparator Interrupt Enable bit                                                                                                                           |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

| bit 1 | MI2C1IE: Master I2C1 Event Interrupt Enable bit                                                                                                                 |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

| bit 0 | SI2C1IE: Slave I2C1 Event Interrupt Enable bit                                                                                                                  |

|       | 1 = Interrupt request is enabled                                                                                                                                |

|       | 0 = Interrupt request is not enabled                                                                                                                            |

**Note 1:** If an external interrupt is enabled, the interrupt input must also be configured to an available RPx or RPIx pin. See **Section 10.4 "Peripheral Pin Select (PPS)**" for more information.

#### REGISTER 7-33: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0           | U-0                | U-0                    | U-0              | U-0                                     | R/W-1            | R/W-0    | R/W-0  |  |  |  |

|---------------|--------------------|------------------------|------------------|-----------------------------------------|------------------|----------|--------|--|--|--|

| _             | —                  | —                      | —                | —                                       | RTCIP2           | RTCIP1   | RTCIP0 |  |  |  |

| bit 15        |                    |                        |                  |                                         |                  |          | bit 8  |  |  |  |

|               |                    |                        |                  |                                         |                  |          |        |  |  |  |

| U-0           | U-0                | U-0                    | U-0              | U-0                                     | U-0              | U-0      | U-0    |  |  |  |

| _             | —                  | —                      | —                | —                                       | —                | —        | —      |  |  |  |