Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                |

| Number of I/O              | 84                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                    |

| Data Converters            | A/D 24x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256da110-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.3.2 DIVIDER

The divide block supports signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE BIT AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic shift right source register by one or more bits. |

| SL          | Shift left source register by one or more bits.             |

| LSR         | Logical shift right source register by one or more bits.    |

### 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase blocks of eight rows (512 instructions) at a time and to program one row at a time. It is also possible to program single words.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 64 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused address should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is *not* recommended.

All of the table write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 JTAG Operation

The PIC24F family supports JTAG boundary scan. Boundary scan can improve the manufacturing process by verifying pin to PCB connectivity.

### 5.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.5 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.6 "Programming Operations"** for further details.

### 5.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### REGISTER 7-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | r-1 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-----|-----|-------|

| _     | —   | _   | —   | IPL3 <sup>(1)</sup> | r   | —   | —     |

| bit 7 |     |     |     |                     |     |     | bit 0 |

| Legend:           | r = Reserved bit | C = Clearable bit HSC = Hardware Settable/Cle |                    |

|-------------------|------------------|-----------------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea                    | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                          | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

- bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup>

- 1 = CPU interrupt priority level is greater than 7

- 0 = CPU interrupt priority level is 7 or less

- bit 2 Reserved: Read as '1'

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level; see Register 3-2 for bit description.

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit |

|-------|----------------------------------------------------------|

|       | <ol> <li>Interrupt request has occurred</li> </ol>       |

|       | 0 = Interrupt request has not occurred                   |

| bit 0 | INT0IF: External Interrupt 0 Flag Status bit             |

|       | 1 = Interrupt request has occurred                       |

|       |                                                          |

0 = Interrupt request has not occurred

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

|                    |                                                          |                                   |                     |                   |                   |                      | 1                    |  |  |  |  |

|--------------------|----------------------------------------------------------|-----------------------------------|---------------------|-------------------|-------------------|----------------------|----------------------|--|--|--|--|

| R/W-0, HS          | R/W-0, HS                                                | R/W-0, HS                         | R/W-0, HS           | R/W-0, HS         | R/W-0, HS         | R/W-0, HS            | U-0                  |  |  |  |  |

| U2TXIF             | U2RXIF                                                   | INT2IF                            | T5IF                | T4IF              | OC4IF             | OC3IF                | —                    |  |  |  |  |

| bit 15             |                                                          |                                   |                     |                   |                   |                      | bit 8                |  |  |  |  |

|                    |                                                          | U-0                               |                     |                   |                   |                      |                      |  |  |  |  |

| R/W-0, HS<br>IC8IF | R/W-0, HS<br>IC7IF                                       | 0-0                               | R/W-0, HS<br>INT1IF | R/W-0, HS<br>CNIF | R/W-0, HS<br>CMIF | R/W-0, HS<br>MI2C1IF | R/W-0, HS<br>SI2C1IF |  |  |  |  |

| bit 7              | IC/IF                                                    |                                   |                     | CINIF             | CIVIIF            | IVII2CTIF            | bit 0                |  |  |  |  |

|                    |                                                          |                                   |                     |                   |                   |                      | DILO                 |  |  |  |  |

| Legend:            |                                                          | HS = Hardwa                       | re Settable bit     |                   |                   |                      |                      |  |  |  |  |

| R = Readable       | bit                                                      | W = Writable                      | bit                 | U = Unimplem      | nented bit, read  | d as '0'             |                      |  |  |  |  |

| -n = Value at I    | POR                                                      | '1' = Bit is set                  |                     | '0' = Bit is clea | ared              | x = Bit is unkr      | iown                 |  |  |  |  |

|                    |                                                          |                                   |                     |                   |                   |                      |                      |  |  |  |  |

| bit 15             |                                                          | T2 Transmitter                    |                     | Status bit        |                   |                      |                      |  |  |  |  |

|                    | •                                                        | request has oc                    |                     |                   |                   |                      |                      |  |  |  |  |

| <b>L:1</b> 4 4     | -                                                        | request has no                    |                     | etus hit          |                   |                      |                      |  |  |  |  |

| bit 14             |                                                          | RT2 Receiver Ir<br>request has oc |                     | alus di           |                   |                      |                      |  |  |  |  |

|                    |                                                          | request has no                    |                     |                   |                   |                      |                      |  |  |  |  |

| bit 13             | INT2IF: Exter                                            | nal Interrupt 2                   | Flag Status bit     |                   |                   |                      |                      |  |  |  |  |

|                    |                                                          |                                   | equest has occurred |                   |                   |                      |                      |  |  |  |  |

|                    | 0 = Interrupt                                            | request has no                    | t occurred          |                   |                   |                      |                      |  |  |  |  |

| bit 12             |                                                          | Interrupt Flag S                  |                     |                   |                   |                      |                      |  |  |  |  |

|                    | •                                                        | request has oc<br>request has no  |                     |                   |                   |                      |                      |  |  |  |  |

| bit 11             | -                                                        | Interrupt Flag S                  |                     |                   |                   |                      |                      |  |  |  |  |

| bit II             |                                                          | request has oc                    |                     |                   |                   |                      |                      |  |  |  |  |

|                    |                                                          | request has no                    |                     |                   |                   |                      |                      |  |  |  |  |

| bit 10             | OC4IF: Output                                            | ut Compare Ch                     | annel 4 Interru     | pt Flag Status b  | bit               |                      |                      |  |  |  |  |

|                    |                                                          | request has oc                    |                     |                   |                   |                      |                      |  |  |  |  |

|                    | •                                                        | request has no                    |                     |                   |                   |                      |                      |  |  |  |  |

| bit 9              |                                                          | -                                 |                     | pt Flag Status b  | Dit               |                      |                      |  |  |  |  |

|                    |                                                          | request has oc<br>request has no  |                     |                   |                   |                      |                      |  |  |  |  |

| bit 8              | -                                                        | ted: Read as '                    |                     |                   |                   |                      |                      |  |  |  |  |

| bit 7              | IC8IF: Input Capture Channel 8 Interrupt Flag Status bit |                                   |                     |                   |                   |                      |                      |  |  |  |  |

|                    |                                                          | request has oc                    |                     | C                 |                   |                      |                      |  |  |  |  |

|                    | 0 = Interrupt                                            | request has no                    | t occurred          |                   |                   |                      |                      |  |  |  |  |

| bit 6              | -                                                        | Capture Channe                    | -                   | ag Status bit     |                   |                      |                      |  |  |  |  |

|                    | •                                                        | request has oc                    |                     |                   |                   |                      |                      |  |  |  |  |

|                    |                                                          | request has no                    | toccurred           |                   |                   |                      |                      |  |  |  |  |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)

| bit 8   | <ul> <li>IC6IF: Input Capture Channel 6 Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | <b>IC5IF:</b> Input Capture Channel 5 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                          |

| bit 6   | <ul> <li>IC4IF: Input Capture Channel 4 Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |

| bit 5   | <b>IC3IF:</b> Input Capture Channel 3 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                          |

| bit 4-2 | Unimplemented: Read as '0'                                                                                                                                               |

| bit 1   | <ul> <li>SPI2IF: SPI2 Event Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>             |

| bit 0   | <ul> <li>SPF2IF: SPI2 Fault Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>             |

Note 1: Not available in PIC24FJXXXDAX06 devices.

| U-0              | U-0                                                        | U-0                                  | U-0               | U-0              | U-0              | U-0                | U-0     |  |

|------------------|------------------------------------------------------------|--------------------------------------|-------------------|------------------|------------------|--------------------|---------|--|

| —                | —                                                          | _                                    | —                 | _                | —                | —                  |         |  |

| bit 15           |                                                            |                                      |                   |                  |                  |                    | bit 8   |  |

|                  |                                                            |                                      |                   |                  |                  |                    | _       |  |

| U-0              | R/W-1                                                      | R/W-0                                | R/W-0             | U-0              | R/W-1            | R/W-0              | R/W-0   |  |

|                  | AD1IP2                                                     | AD1IP1                               | AD1IP0            |                  | U1TXIP2          | U1TXIP1            | U1TXIP0 |  |

| bit 7            |                                                            |                                      |                   |                  |                  |                    | bit 0   |  |

|                  |                                                            |                                      |                   |                  |                  |                    |         |  |

| Legend:          |                                                            |                                      |                   |                  |                  |                    |         |  |

| R = Readable bit |                                                            | W = Writable                         | bit               |                  | mented bit, reac | d as '0'           |         |  |

| -n = Value a     | at POR                                                     | '1' = Bit is set                     | t                 | '0' = Bit is cle | ared             | x = Bit is unknown |         |  |

|                  |                                                            |                                      |                   |                  |                  |                    |         |  |

| bit 15-7         | Unimplemen                                                 | ted: Read as '                       | 0'                |                  |                  |                    |         |  |

| bit 6-4          | AD1IP<2:0>:                                                | A/D Conversion                       | on Complete In    | terrupt Priority | bits             |                    |         |  |

|                  | 111 = Interru                                              | pt is priority 7                     | (highest priority | interrupt)       |                  |                    |         |  |

|                  | •                                                          |                                      |                   |                  |                  |                    |         |  |

|                  | •                                                          |                                      |                   |                  |                  |                    |         |  |

|                  | 001 = Interru<br>000 = Interru                             | pt is priority 1<br>pt source is dis | sabled            |                  |                  |                    |         |  |

| bit 3            | Unimplemen                                                 | ted: Read as '                       | 0'                |                  |                  |                    |         |  |

| bit 2-0          | U1TXIP<2:0>                                                | : UART1 Tran                         | smitter Interrup  | t Priority bits  |                  |                    |         |  |

|                  | 111 = Interrupt is priority 7 (highest priority interrupt) |                                      |                   |                  |                  |                    |         |  |

|                  | •                                                          |                                      |                   |                  |                  |                    |         |  |

|                  | •                                                          |                                      |                   |                  |                  |                    |         |  |

|                  | 001 = Interru                                              |                                      |                   |                  |                  |                    |         |  |

|                  | 000 = Interru                                              | pt source is dis                     | sabled            |                  |                  |                    |         |  |

|                  |                                                            |                                      |                   |                  |                  |                    |         |  |

### REGISTER 7-22: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

### REGISTER 7-27: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | SPI2IP2 | SPI2IP1 | SPI2IP0 | —   | SPF2IP2 | SPF2IP1 | SPF2IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

| bit 15-7<br>bit 6-4 | Unimplemented: Read as '0'<br>SPI2IP<2:0>: SPI2 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                     | •<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                    |

| bit 3               | Unimplemented: Read as '0'                                                                                                                  |

| bit 2-0             | <pre>SPF2IP&lt;2:0&gt;: SPI2 Fault Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)</pre>                 |

### 8.3 Control Registers

The following five Special Function Registers control the operation of the oscillator:

- OSCCON

- CLKDIV

- OSCTUN

- CLKDIV2

- REFOCON

The OSCCON register (Register 8-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The CLKDIV register (Register 8-2) controls the features associated with Doze mode, as well as the postscaler for the FRC oscillator.

The OSCTUN register (Register 8-3) allows the user to fine tune the FRC oscillator over a range of approximately  $\pm 1.5\%$ .

The CLKDIV2 register (Register 8-4) controls the clock to the display glass, with the frequency ranging from 750 kHz to 96 MHz.

The REFOCON register (Register 8-5) controls the frequency of the reference clock out.

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-x, HSC <sup>(1)</sup> | R-x, HSC <sup>(1)</sup> | R-x, HSC <sup>(1)</sup> | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|-------------------------|-------------------------|-------------------------|-----|----------------------|----------------------|----------------------|

| _      | COSC2                   | COSC1                   | COSC0                   | _   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |                         |                         |                         |     |                      |                      | bit 8                |

| R/S-0   | R/W-0                 | R-0, HSC <sup>(3)</sup> | U-0 | R/C-0, HS | R/W-0  | R/W-0  | R/W-0 |

|---------|-----------------------|-------------------------|-----|-----------|--------|--------|-------|

| CLKLOCK | IOLOCK <sup>(2)</sup> | LOCK                    | _   | CF        | POSCEN | SOSCEN | OSWEN |

| bit 7   |                       |                         |     |           |        |        | bit 0 |

| Legend:                    | C = Clearable bit | S = Settable bit     | HSC = Hardware Settable/Clearable bit |  |  |

|----------------------------|-------------------|----------------------|---------------------------------------|--|--|

| R = Readable bit           | W = Writable bit  | U = Unimplemented bi | t, read as '0'                        |  |  |

| -n = Value at POR          | '1' = Bit is set  | '0' = Bit is cleared | x = Bit is unknown                    |  |  |

| HS = Hardware Settable bit |                   |                      |                                       |  |  |

### bit 15 Unimplemented: Read as '0'

### bit 14-12 COSC<2:0>: Current Oscillator Selection bits<sup>(1)</sup>

- 111 = Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = Fast RC/16 Oscillator

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = Fast RC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = Fast RC Oscillator (FRC)

- bit 11 Unimplemented: Read as '0'

- Note 1: Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1', once the IOLOCK bit is set, it cannot be cleared.

- 3: Also resets to '0' during any valid clock switch or whenever a non PLL Clock mode is selected.

### 10.3 Input Change Notification

The input change notification function of the I/O ports allows the PIC24FJ256DA210 family of devices to generate interrupt requests to the processor in response to a Change-Of-State (COS) on selected input pins. This feature is capable of detecting input Change-Of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 84 external inputs that may be selected (enabled) for generating an interrupt request on a Change-Of-State.

Registers, CNEN1 through CNEN6, contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin has a both a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source that is connected to the pin, while the pull-downs act as a current sink that is connected to the pin. These eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are separately enabled using the CNPU1 through CNPU6 registers (for pull-ups), and the CNPD1 through CNPD6 registers (for pull-downs). Each CN pin has individual control bits for its pull-up and pull-down. Setting a control bit enables the weak pull-up or pull-down for the corresponding pin.

When the internal pull-up is selected, the pin pulls up to VDD - 1.1V (typical). When the internal pull-down is selected, the pin pulls down to Vss.

Note: Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

Note: To use CN83 and CN84, which are on the D+ and D- pins, the UTRDIS bit (U1CNFG2<0>) should be set.

### EXAMPLE 10-1: PORT WRITE/READ IN ASSEMBLY

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | W0, TRISB  | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| BTSS | PORTB, #13 | ; Next Instruction                |

### EXAMPLE 10-2: PORT WRITE/READ IN 'C'

| TRISB = 0xFF00;                     | <pre>// Configure PORTB&lt;15:8&gt; as inputs and PORTB&lt;7:0&gt; as outputs</pre> |

|-------------------------------------|-------------------------------------------------------------------------------------|

| Nop();                              | // Delay 1 cycle                                                                    |

| <pre>If (PORTBbits.RB13) { };</pre> | // Next Instruction                                                                 |

### REGISTER 10-12: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | T5CKR5 | T5CKR4 | T5CKR3 | T5CKR2 | T5CKR1 | T5CKR0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | T4CKR5 | T4CKR4 | T4CKR3 | T4CKR2 | T4CKR1 | T4CKR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 13-8  | T5CKR<5:0>: Assign Timer5 External Clock (T5CK) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                            |

| bit 5-0   | T4CKR<5:0>: Assign Timer4 External Clock (T4CK) to Corresponding RPn or RPIn Pin bits |

### REGISTER 10-13: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | IC2R5 | IC2R4 | IC2R3 | IC2R2 | IC2R1 | IC2R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IC1R5 | IC1R4 | IC1R3 | IC1R2 | IC1R1 | IC1R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 IC2R<5:0>: Assign Input Capture 2 (IC2) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IC1R<5:0>: Assign Input Capture 1 (IC1) to Corresponding RPn or RPIn Pin bits

### REGISTER 10-22: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | SCK1R5 | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK1R<5:0>: Assign SPI1 Clock Input (SCK1IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI1R<5:0>: Assign SPI1 Data Input (SDI1) to Corresponding RPn or RPIn Pin bits    |

### REGISTER 10-23: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U3CTSR5 | U3CTSR4 | U3CTSR3 | U3CTSR2 | U3CTSR1 | U3CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS1R5 | SS1R4 | SS1R3 | SS1R2 | SS1R1 | SS1R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U3CTSR<5:0>: Assign UART3 Clear to Send (U3CTS) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SS1R<5:0>: Assign SPI1 Slave Select Input (SS1IN) to Corresponding RPn or RPIn Pin bits

### REGISTER 10-24: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | -   | SCK2R5 | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK2R<5:0>: Assign SPI2 Clock Input (SCK2IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI2R<5:0>: Assign SPI2 Data Input (SDI2) to Corresponding RPn or RPIn Pin bits    |

### REGISTER 10-25: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS2R5 | SS2R4 | SS2R3 | SS2R2 | SS2R1 | SS2R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 SS2R<5:0>: Assign SPI2 Slave Select Input (SS2IN) to Corresponding RPn or RPIn Pin bits

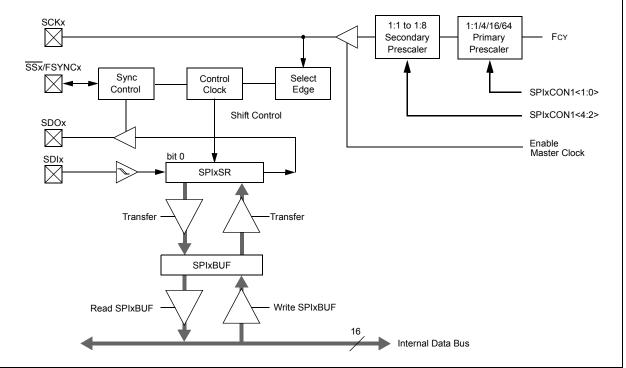

To set up the SPI module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPI module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFS register.

- b) Set the SPIxIE bit in the respective IEC register.

- c) Write the SPIxIP bits in the respective IPC register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with MSTEN (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit.

- If the CKE bit (SPIxCON1<8>) is set, then the SSEN bit (SPIxCON1<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

### 17.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 21. "UART" (DS39708). The information in this data sheet supersedes the information in the FRM.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-Bit data transmission through the UxTX and UxRX pins

- Even, Odd or No Parity options (for 8-bit data)

- One or two Stop bits

**FIGURE 17-1:**

Hardware Flow Control option with the UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 15 bps to 1 Mbps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect  $(9^{th} bit = 1)$

- · Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART is shown in Figure 17-1. The UART module consists of these key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

# Baud Rate Generator IrDA® Hardware Flow Control UxRTS/BCLKx UxCTS UxRTx Receiver UARTx Transmitter UXRX UxRX VarX V

UART SIMPLIFIED BLOCK DIAGRAM

### 18.1.2 HOST AND OTG MODES

### 18.1.2.1 D+ and D- Pull-Down Resistors

PIC24FJ256DA210 family devices have a built-in 15 kΩ pull-down resistor on the D+ and D- lines. These are used in tandem to signal to the bus that the microcontroller is operating in Host mode. They are engaged by setting the HOSTEN bit (U1CON<3>). If the OTGEN bit (U1OTGCON<2>) is set, then these pull-downs are enabled by setting the DPPULDWN and DMPULDWN bits (U1OTGCON<5:4>).

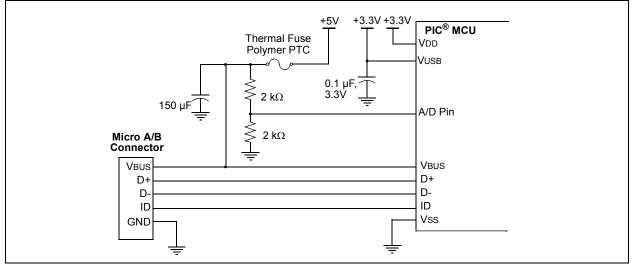

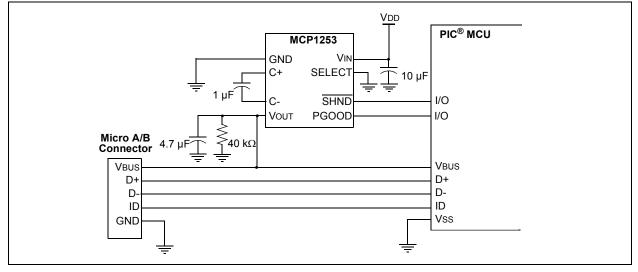

### 18.1.2.2 Power Configurations

In Host mode, as well as Host mode in On-The-Go operation, the USB 2.0 Specification requires that the host application should supply power on VBUS. Since

the microcontroller is running below VBUS, and is not able to source sufficient current, a separate power supply must be provided.

When the application is always operating in Host mode, a simple circuit can be used to supply VBUS and regulate current on the bus (Figure 18-6). For OTG operation, it is necessary to be able to turn VBUS on or off as needed, as the microcontroller switches between Device and Host modes. A typical example using an external charge pump is shown in Figure 18-7.

### FIGURE 18-6: HOST INTERFACE EXAMPLE

### FIGURE 18-7: OTG INTERFACE EXAMPLE

### 18.1.2.3 VBUS Voltage Generation with External Devices

When operating as a USB host, either as an A-device in an OTG configuration or as an embedded host, VBUS must be supplied to the attached device. PIC24FJ256DA210 family devices have an internal VBUS boost assist to help generate the required 5V VBUS from the available voltages on the board. This is comprised of a simple PWM output to control a Switch mode power supply, and built-in comparators to monitor output voltage and limit current.

To enable voltage generation:

- Verify that the USB module is powered (U1PWRC<0> = 1) and that the VBUS discharge is disabled (U1OTGCON<0> = 0).

- 2. Set the PWM period (U1PWMRRS<7:0>) and duty cycle (U1PWMRRS<15:8>) as required.

- 3. Select the required polarity of the output signal based on the configuration of the external circuit with the PWMPOL bit (U1PWMCON<9>).

- 4. Select the desired target voltage using the VBUSCHG bit (U1OTGCON<1>).

- 5. Enable the PWM counter by setting the CNTEN bit to '1' (U1PWMCON<8>).

- 6. Enable the PWM module by setting the PWMEN bit (U1PWMCON<15>) to '1'.

- 7. Enable the VBUS generation circuit (U10TGCON<3> = 1).

- Note: This section describes the general process for VBUS voltage generation and control. Please refer to the "*PIC24F Family Reference Manual*" for additional examples.

### 18.1.3 USING AN EXTERNAL INTERFACE

Some applications may require the USB interface to be isolated from the rest of the system. PIC24FJ256DA210 family devices include a complete interface to communicate with and control an external USB transceiver, including the control of data line pull-ups and pull-downs. The VBUS voltage generation control circuit can also be configured for different VBUS generation topologies.

Refer to the "*PIC24F Family Reference Manual*", **Section 27. "USB On-The-Go (OTG)**" for information on using the external interface.

### 18.1.4 CALCULATING TRANSCEIVER POWER REQUIREMENTS

The USB transceiver consumes a variable amount of current depending on the characteristic impedance of the USB cable, the length of the cable, the VUSB supply voltage and the actual data patterns moving across the USB cable. Longer cables have larger capacitances and consume more total energy when switching output states. The total transceiver current consumption will be application-specific. Equation 18-1 can help estimate how much current actually may be required in full-speed applications.

Refer to the "*PIC24F Family Reference Manual*", **Section 27. "USB On-The-Go (OTG)**" for a complete discussion on transceiver power consumption.

### EQUATION 18-1: ESTIMATING USB TRANSCEIVER CURRENT CONSUMPTION

$\mathsf{IXCVR} = \frac{40 \text{ mA} \cdot \mathsf{VUSB} \cdot \mathsf{PZERO} \cdot \mathsf{PIN} \cdot \mathsf{LCABLE}}{3.3 \text{ V} \cdot 5 \text{ m}} + \mathsf{IPULLUP}$

Legend: VUSB – Voltage applied to the VUSB pin in volts (3.0V to 3.6V).

PZERO - Percentage (in decimal) of the IN traffic bits sent by the  $PIC^{\$}$  microcontroller that are a value of '0'.

PIN – Percentage (in decimal) of total bus bandwidth that is used for IN traffic.

LCABLE – Length (in meters) of the USB cable. The USB 2.0 Specification requires that full-speed applications use cables no longer than 5m.

IPULLUP – Current which the nominal, 1.5 k $\Omega$  pull-up resistor (when enabled) must supply to the USB cable.

### 18.6.2 HOST NEGOTIATION PROTOCOL (HNP)

In USB OTG applications, a Dual Role Device (DRD) is a device that is capable of being either a host or a peripheral. Any OTG DRD must support Host Negotiation Protocol (HNP).

HNP allows an OTG B-device to temporarily become the USB host. The A-device must first enable the B-device to follow HNP. Refer to the "On-The-Go Supplement to the USB 2.0 Specification" for more information regarding HNP. HNP may only be initiated at full speed.

After being enabled for HNP by the A-device, the B-device requests being the host any time that the USB link is in suspend state, by simply indicating a disconnect. This can be done in software by clearing DPPULUP and DMPULUP. When the A-device detects the disconnect condition (via the URSTIF (U1IR<0>) interrupt), the A-device may allow the B-device to take over as host. The A-device does this by signaling connect as a full-speed function. Software may accomplish this by setting DPPULUP.

If the A-device responds instead with resume signaling, the A-device remains as host. When the B-device detects the connect condition (via ATTACHIF (U1IR<6>), the B-device becomes host. The B-device drives Reset signaling prior to using the bus.

When the B-device has finished in its role as host, it stops all bus activity and turns on its D+ pull-up resistor by setting DPPULUP. When the A-device detects a suspend condition (Idle for 3 ms), the A-device turns off its D+ pull-up. The A-device may also power-down the VBUS supply to end the session. When the A-device detects the connect condition (via ATTACHIF), the A-device resumes host operation and drives Reset signaling.

### 18.6.3 **EXTERNAL VBUS COMPARATORS**

The external VBUS comparator option is enabled by setting the UVCMPDIS bit (U1CNFG2<1>). This disables the internal VBUS comparators, removing the need to attach VBUS to the microcontroller's VBUS pin.

The external comparator interface uses either the VCMPST1 and VCMPST2 pins, or the VBUSVLD, SESSVLD and SESSEND pins, based upon the setting of the UVCMPSEL bit (U1CNFG2<5>). These pins are digital inputs and should be set in the following patterns (see Table 18-3), based on the current level of the VBUS voltage.

### **EXTERNAL VBUS COMPARATOR STATES** TABLE 18-3:

| lf U\ | CMPSEL = 0 |

|-------|------------|

|       |            |

| VCMPST1 | VCMPST2 | Bus Condition                    |  |  |  |

|---------|---------|----------------------------------|--|--|--|

| 0       | 0       | VBUS < VB_SESS_END               |  |  |  |

| 1       | 0       | VB_SESS_END < VBUS < VA_SESS_VLD |  |  |  |

| 0       | 1       | VA_SESS_VLD < VBUS < VA_VBUS_VLD |  |  |  |

| 1       | 1       | VBUS > VBUS_VLD                  |  |  |  |

|         |         |                                  |  |  |  |

### IF UVCMPSEL = 1

| VBUSVLD | SESSVLD | SESSEND | Bus Condition                    |  |  |  |

|---------|---------|---------|----------------------------------|--|--|--|

| 0       | 0       | 1       | VBUS < VB_SESS_END               |  |  |  |

| 0       | 0       | 0       | VB_SESS_END < VBUS < VA_SESS_VLD |  |  |  |

| 0       | 1       | 0       | VA_SESS_VLD < VBUS < VA_VBUS_VLD |  |  |  |

| 1       | 1       | 0       | VBUS > VBUS_VLD                  |  |  |  |

### REGISTER 18-5: U1PWRC: USB POWER CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0, HS | U-0 | U-0 | R/W-0   | U-0 | U-0 | R/W-0, HC | R/W-0  |

|-----------|-----|-----|---------|-----|-----|-----------|--------|

| UACTPND   | —   | —   | USLPGRD | _   | -   | USUSPND   | USBPWR |

| bit 7     |     |     |         |     |     |           | bit 0  |

| Legend:           | HS = Hardware Settable bit | HC = Hardware Clearal  | ble bit            |

|-------------------|----------------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                             |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | UACTPND: USB Activity Pending bit                                                                                                                                      |

|          | <ul> <li>1 = Module should not be suspended at the moment (requires the USLPGRD bit to be set)</li> <li>0 = Module may be suspended or powered down</li> </ul>         |

| bit 6-5  | Unimplemented: Read as '0'                                                                                                                                             |

| bit 4    | USLPGRD: Sleep/Suspend Guard bit                                                                                                                                       |

|          | <ul> <li>1 = Indicate to the USB module that it is about to be suspended or powered down</li> <li>0 = No suspend</li> </ul>                                            |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                                                             |

| bit 1    | USUSPND: USB Suspend Mode Enable bit                                                                                                                                   |

|          | <ul> <li>1 = USB OTG module is in Suspend mode; USB clock is gated and the transceiver is placed in a low-power state</li> <li>0 = Normal USB OTG operation</li> </ul> |

| bit 0    | USBPWR: USB Operation Enable bit                                                                                                                                       |

|          | 1 = USB OTG module is enabled                                                                                                                                          |

|          | $0 = \text{USB OTG module is disabled}^{(1)}$                                                                                                                          |

| Note 1:  | Do not clear this bit unless the HOSTEN, USBEN and OTGEN bits (U1CON<3,0> and U1OTGCON<2>)                                                                             |

are all cleared.

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |

|----------------------|--------|-----------------|------------------------------|---------------|----------------|--------------------------|--|

| TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd        | 1             | 2              | None                     |  |

| TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |  |

| TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>       | 1             | 2              | None                     |  |

| ULNK                 | ULNK   |                 | Unlink Frame Pointer         | 1             | 1              | None                     |  |

| XOR                  | XOR    | f               | f = f .XOR. WREG             | 1             | 1              | N, Z                     |  |

|                      | XOR    | f,WREG          | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |  |

|                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |  |

|                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |  |

|                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |  |

| ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |  |

### TABLE 29-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| OSCTUN (FRC Oscillator Tune)             |            |

|------------------------------------------|------------|

| PADCFG1 (Pad Configuration Control)      |            |

| PMCON1 (EPMP Control 1)                  |            |

| PMCON2 (EPMP Control 2)                  | 276        |

|                                          |            |

| PMCON3 (EPMP Control 3)                  |            |

| PMCON4 (EPMP Control 4)                  |            |

| PMCSxBS (Chip Select x Base Address)     |            |

| PMCSxCF (Chip Select x Configuration)    |            |

| PMCSxMD (Chip Select x Mode)             |            |

|                                          |            |

| PMSTAT (EPMP Status, Slave Mode)         |            |

| RCFGCAL (RTCC Calibration and Configur   | ation) 287 |

| RCON (Reset Control)                     |            |

| REFOCON (Reference Oscillator Control).  |            |

|                                          |            |

| RPINRn (PPS Input)                       |            |

| RPORn (PPS Output)                       |            |

| SPIxCON1 (SPIx Control 1)                | 216        |

| SPIxCON2 (SPIx Control 2)                |            |

| SPIxSTAT (SPIx Status and Control)       |            |

|                                          |            |

| SR (ALU STATUS)                          |            |

| T1CON (Timer1 Control)                   |            |

| TxCON (Timer2 and Timer4 Control)        |            |

| TyCON (Timer3 and Timer5 Control)        |            |

| U1ADDR (USB Address)                     |            |

|                                          |            |

| U1CNFG1 (USB Configuration 1)            |            |

| U1CNFG2 (USB Configuration 2)            |            |

| U1CON (USB Control, Device Mode)         |            |

| U1CON (USB Control, Host Mode)           |            |

| U1EIE (USB Error Interrupt Enable)       |            |

| U1EIR (USB Error Interrupt Status)       |            |

|                                          |            |

| U1EPn (USB Endpoint n Control)           |            |

| U1IE (USB Interrupt Enable)              |            |

| U1IR (USB Interrupt Status, Device Mode) |            |

| U1IR (USB Interrupt Status, Host Mode)   |            |

| U1OTGCON (USB OTG Control)               |            |

| U10TGIE (USB OTG Interrupt Enable,       |            |

|                                          | 265        |

| Host Mode)                               |            |

| U1OTGIR (USB OTG Interrupt Status,       |            |

| Host Mode)                               |            |

| U1OTGSTAT (USB OTG Status)               |            |

| U1PWMCON USB (VBUS PWM Generator         |            |

| Control)                                 | 272        |

| U1PWRC (USB Power Control)               |            |

|                                          |            |

| U1SOF (USB OTG Start-Of-Token            |            |

| Threshold, Host Mode)                    |            |

| U1STAT (USB Status)                      |            |

| U1TOK (USB Token, Host Mode)             |            |

| UxMODE (UARTx Mode)                      |            |

|                                          |            |

| UxSTA (UARTx Status and Control)         |            |

| WKDYHR (RTCC Weekday and Hours Value     |            |

| YEAR (RTCC Year Value)                   |            |

| Resets                                   |            |

| BOR (Brown-out Reset)                    | 87         |

| Clock Source Selection                   |            |

| CM (Configuration Mismatch Reset)        |            |

| , , , , , , , , , , , , , , , , , , ,    |            |

| Delay Times                              |            |

| Device Times                             |            |

| IOPUWR (Illegal Opcode Reset)            |            |

| MCLR (Pin Reset)                         |            |

| POR (Power-on Reset)                     |            |

| RCON Flags Operation                     |            |

|                                          |            |

| SFR States                               |            |

| SWR (RESET Instruction)                  |            |

| TRAPR (Trap Conflict Reset)              |            |

| UWR (Uninitialized W Register Reset)     |            |

| WDT (Watchdog Timer Reset)               |            |

| Revision History    | 397 |

|---------------------|-----|

| Alarm Configuration | 294 |

| Calibration         | 294 |

| Key Features 2      | 285 |

| Register Mapping 2  | 286 |

| 9                   |     |

### S

| Selective Peripheral Power Control<br>Serial Peripheral Interface (SPI)<br>Serial Peripheral Interface. See SPI. |     |

|------------------------------------------------------------------------------------------------------------------|-----|

| SFR Space                                                                                                        | 49  |

| Sleep Mode                                                                                                       |     |

| Software Simulator (MPLAB SIM)                                                                                   | 361 |

| Software Stack                                                                                                   | 75  |

| Special Features                                                                                                 | 16  |

| SPI                                                                                                              | 211 |

### Т

| Timer1                   | 189 |

|--------------------------|-----|

| Timer2/3 and Timer4/5    | 191 |

| Timing Diagrams          |     |

| CLKO and I/O Timing      | 383 |

| External Clock           | 380 |

| Triple Comparator        | 335 |

| Triple Comparator Module | 335 |

|                          |     |

### U

| UART                                                 | 231 |

|------------------------------------------------------|-----|

| Baud Rate Generator (BRG)                            | 232 |

| IrDA Support                                         |     |

| Operation of UxCTS and UxRTS Pins                    | 233 |

| Receiving in 8-Bit or 9-Bit Data Mode                | 233 |

| Transmitting                                         |     |

| Break and Sync Sequence                              | 233 |

| in 8-Bit Data Mode                                   | 233 |

| Transmitting in 9-Bit Data Mode                      | 233 |

| Universal Asynchronous Receiver Transmitter. See UAR | Τ.  |

| Universal Serial Bus                                 |     |

| Buffer Descriptors                                   |     |

| Assignment in Different Buffering Modes              | 245 |

| Interrupts                                           |     |

| and USB Transactions                                 | 249 |

| Universal Serial Bus. See USB OTG.                   |     |

| USB On-The-Go (OTG)                                  | 16  |

| USB OTG                                              |     |

| Buffer Descriptors and BDT                           |     |

| Device Mode Operation                                |     |

| DMA Interface                                        | 245 |

| Hardware                                             |     |

| Calculating                                          |     |

| Transceiver Power Requirements                       |     |

| Hardware Configuration                               |     |

| Device Mode                                          |     |

| External Interface                                   |     |

| Host and OTG Modes                                   |     |

| VBUS Voltage Generation                              |     |

| Host Mode Operation                                  |     |

| Interrupts                                           |     |

| Operation                                            |     |

| Registers                                            |     |

| VBUS Voltage Generation                              | 243 |