Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                |

| Number of I/O              | 84                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                    |

| Data Converters            | A/D 24x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256da110-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

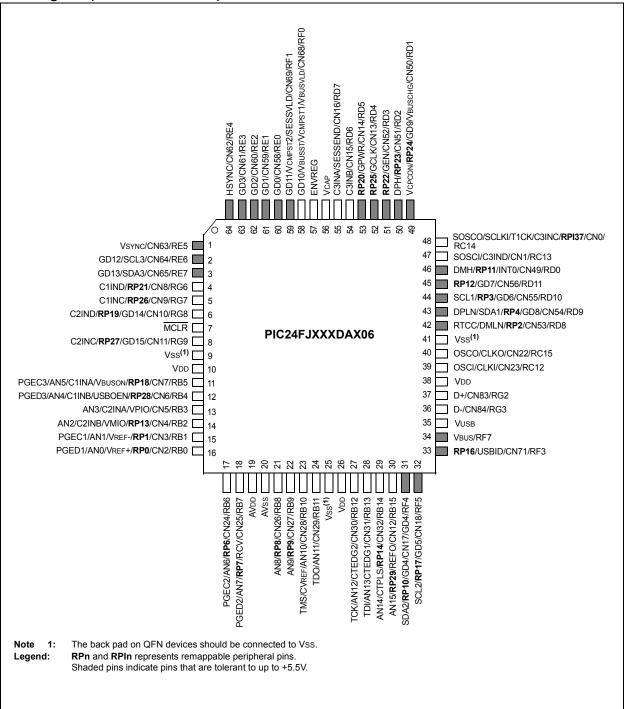

# Pin Diagram (64-Pin TQFP/QFN)

|          |                                | Pin Number                   |                |     | Incret          |                                                                       |

|----------|--------------------------------|------------------------------|----------------|-----|-----------------|-----------------------------------------------------------------------|

| Function | 64-Pin<br>TQFP/QFN             | 100-Pin<br>TQFP              | 121-Pin<br>BGA | I/O | Input<br>Buffer | Description                                                           |

| AN0      | 16                             | 25                           | K2             | I   | ANA             |                                                                       |

| AN1      | 15                             | 24                           | K1             | I   | ANA             |                                                                       |

| AN2      | 14                             | 23                           | J2             | I   | ANA             |                                                                       |

| AN3      | 13                             | 22                           | J1             | I   | ANA             |                                                                       |

| AN4      | 12                             | 21                           | H2             | I   | ANA             |                                                                       |

| AN5      | 11                             | 20                           | H1             | Ι   | ANA             |                                                                       |

| AN6      | 17                             | 26                           | L1             | I   | ANA             |                                                                       |

| AN7      | 18                             | 27                           | J3             | I   | ANA             |                                                                       |

| AN8      | 21                             | 32                           | K4             | I   | ANA             |                                                                       |

| AN9      | 22                             | 33                           | L4             | I   | ANA             |                                                                       |

| AN10     | 23                             | 34                           | L5             | I   | ANA             |                                                                       |

| AN11     | 24                             | 35                           | J5             | I   | ANA             |                                                                       |

| AN12     | 27                             | 41                           | J7             | I   | ANA             | A/D Analog Inputs.                                                    |

| AN13     | 28                             | 42                           | L7             | Ι   | ANA             |                                                                       |

| AN14     | 29                             | 43                           | K7             | I   | ANA             |                                                                       |

| AN15     | 30                             | 44                           | L8             | Ι   | ANA             |                                                                       |

| AN16     | —                              | 9                            | E1             | Ι   | ANA             |                                                                       |

| AN17     | —                              | 10                           | E3             | I   | ANA             |                                                                       |

| AN18     | —                              | 11                           | F4             | I   | ANA             |                                                                       |

| AN19     | —                              | 12                           | F2             | I   | ANA             |                                                                       |

| AN20     | —                              | 14                           | F3             | Ι   | ANA             |                                                                       |

| AN21     | —                              | 19                           | G2             | I   | ANA             |                                                                       |

| AN22     | —                              | 92                           | B5             | I   | ANA             |                                                                       |

| AN23     | —                              | 91                           | C5             | Ι   | ANA             |                                                                       |

| AVdd     | 19                             | 30                           | J4             | Р   | _               | Positive Supply for Analog modules.                                   |

| AVss     | 20                             | 31                           | L3             | Р   | _               | Ground Reference for Analog modules.                                  |

| C1INA    | 11                             | 20                           | H1             | Ι   | ANA             | Comparator 1 Input A.                                                 |

| C1INB    | 12                             | 21                           | H2             | I   | ANA             | Comparator 1 Input B.                                                 |

| C1INC    | 5                              | 11                           | F4             | I   | ANA             | Comparator 1 Input C.                                                 |

| C1IND    | 4                              | 10                           | E3             | I   | ANA             | Comparator 1 Input D.                                                 |

| C2INA    | 13                             | 22                           | J1             | I   | ANA             | Comparator 2 Input A.                                                 |

| C2INB    | 14                             | 23                           | J2             | Ι   | ANA             | Comparator 2 Input B.                                                 |

| C2INC    | 8                              | 14                           | F3             | I   | ANA             | Comparator 2 Input C.                                                 |

| C2IND    | 6                              | 12                           | F2             | I   | ANA             | Comparator 2 Input D.                                                 |

| C3INA    | 55                             | 84                           | C7             | I   | ANA             | Comparator 3 Input A.                                                 |

| C3INB    | 54                             | 83                           | D7             | I   | ANA             | Comparator 3 Input B.                                                 |

| C3INC    | 48                             | 74                           | B11            | I   | ANA             | Comparator 3 Input C.                                                 |

| C3IND    | 47                             | 73                           | C10            | I   | ANA             | Comparator 3 Input D.                                                 |

| CLKI     | 39                             | 63                           | F9             | I   | ST              | Main Clock Input Connection.                                          |

| CLKO     | 40                             | 64                           | F11            | 0   | —               | System Clock Output.                                                  |

|          | TTL = TTL inpu<br>ANA = Analog | ut buffer<br>level input/out | put            |     |                 | Schmitt Trigger input buffer<br>= I <sup>2</sup> C/SMBus input buffer |

| TABLE 1-3: | PIC24FJ256DA210 FAMILY PINOUT DESCRIPTIONS   |

|------------|----------------------------------------------|

| IADLL I-J. | FICZAI JZJODAZIU I AWILI FINOUI DLJCKIFIIONJ |

$I^2C^{TM} = I^2C/SMBus$  input buffer

Note 1: The alternate EPMP pins are selected when the ALTPMP (CW3<12>) bit is programmed to '0'.

2: The PMSC2 signal will replace the PMA15 signal on the 15-pin PMA when CSF<1:0> = 01 or 10.

3: The PMCS1 signal will replace the PMA14 signal on the 14-pin PMA when CSF<1:0> = 10.

4: The alternate VREF pins selected when the ALTVREF (CW1<5>) bit is programmed to '0'.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with  $PIC^{\textcircled{O}}$  MCUs and improve data space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all EA calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word, which contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The Most Significant Byte (MSB) is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend ( $\mathbb{ZE}$ ) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

# 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the near data space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the data space is addressable indirectly. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing with a 16-bit address field.

#### 4.2.4 SPECIAL FUNCTION REGISTER (SFR) SPACE

The first 2 Kbytes of the near data space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A diagram of the SFR space, showing where the SFRs are actually implemented, is shown in Table 4-3. Each implemented area indicates a 32-byte region where at least one address is implemented as an SFR. A complete list of implemented SFRs, including their addresses, is shown in Tables 4-4 throughTable 4-34.

|      |                   |           | SFR      | Space Add            | ess        |    |      |        |       |  |  |

|------|-------------------|-----------|----------|----------------------|------------|----|------|--------|-------|--|--|

|      | xx00              | xx20      | xx40     | xx60                 | хх         | 80 | xxA0 | xxC0   | xxE0  |  |  |

| 000h |                   | Core      |          |                      | Interrupts |    |      |        |       |  |  |

| 100h | Tim               | ners      | (        | Capture              |            |    | C    | ompare |       |  |  |

| 200h | I <sup>2</sup> C™ | UART      | SPI/UART | SPI/I <sup>2</sup> C | S          | PI | UART | I/     | 0     |  |  |

| 300h |                   | ADC/CTMU  |          | —                    | _          | _  | —    | _      |       |  |  |

| 400h | —                 | —         | _        | —                    |            |    | USB  |        | ANSEL |  |  |

| 500h | —                 | —         |          | —                    | _          | _  | _    | _      | —     |  |  |

| 600h | EPMP              | RTC/Comp  | CRC      | _                    |            |    | PPS  |        | _     |  |  |

| 700h | GFX C             | ontroller | System   | NVM/PMD              | _          | _  | _    | _      | _     |  |  |

|      |                   |           |          |                      |            |    |      |        |       |  |  |

TABLE 4-3:IMPLEMENTED REGIONS OF SFR DATA SPACE

Legend: — = No implemented SFRs in this block

| File<br>Name          | Addr | Bit 15 | Bit 14                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8        | Bit 7        | Bit 6     | Bit 5       | Bit 4       | Bit 3        | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|-----------------------|------|--------|-------------------------------------|--------|--------|--------|--------|---------|--------------|--------------|-----------|-------------|-------------|--------------|----------|-------|-------|---------------|

| WREG0                 | 0000 |        |                                     |        |        |        |        |         | Working R    | egister 0    |           |             |             |              |          |       | -     | 0000          |

| WREG1                 | 0002 |        |                                     |        |        |        |        |         | Working R    | egister 1    |           |             |             |              |          |       |       | 0000          |

| WREG2                 | 0004 |        |                                     |        |        |        |        |         | Working R    | egister 2    |           |             |             |              |          |       |       | 0000          |

| WREG3                 | 0006 |        |                                     |        |        |        |        |         | Working R    | egister 3    |           |             |             |              |          |       |       | 0000          |

| WREG4                 | 0008 |        |                                     |        |        |        |        |         | Working R    | egister 4    |           |             |             |              |          |       |       | 0000          |

| WREG5                 | 000A |        |                                     |        |        |        |        |         | Working R    | egister 5    |           |             |             |              |          |       |       | 0000          |

| WREG6                 | 000C |        |                                     |        |        |        |        |         | Working R    | egister 6    |           |             |             |              |          |       |       | 0000          |

| WREG7                 | 000E |        |                                     |        |        |        |        |         | Working R    | egister 7    |           |             |             |              |          |       |       | 0000          |

| WREG8                 | 0010 |        |                                     |        |        |        |        |         | Working R    | egister 8    |           |             |             |              |          |       |       | 0000          |

| WREG9                 | 0012 |        |                                     |        |        |        |        |         | Working R    | egister 9    |           |             |             |              |          |       |       | 0000          |

| WREG10                | 0014 |        |                                     |        |        |        |        |         | Working Re   | egister 10   |           |             |             |              |          |       |       | 0000          |

| WREG11                | 0016 |        |                                     |        |        |        |        |         | Working Re   | egister 11   |           |             |             |              |          |       |       | 0000          |

| WREG12                | 0018 |        |                                     |        |        |        |        |         | Working Re   | egister 12   |           |             |             |              |          |       |       | 0000          |

| WREG13                | 001A |        |                                     |        |        |        |        |         | Working Re   | egister 13   |           |             |             |              |          |       |       | 0000          |

| WREG14                | 001C |        |                                     |        |        |        |        |         | Working Re   | egister 14   |           |             |             |              |          |       |       | 0000          |

| WREG15                | 001E |        |                                     |        |        |        |        |         | Working Re   | egister 15   |           |             |             |              |          |       |       | 0800          |

| SPLIM                 | 0020 |        |                                     |        |        |        |        | Stack   | Pointer Limi | it Value Reg | gister    |             |             |              |          |       |       | xxxx          |

| PCL                   | 002E |        |                                     |        |        |        |        | Progran | n Counter L  | ow Word Re   | egister   |             |             |              |          |       |       | 0000          |

| PCH                   | 0030 | _      | _                                   | —      | —      | —      | _      | _       | —            |              |           | Program     | n Counter F | Register Hig | h Byte   |       |       | 0000          |

| DSRPAG                | 0032 | _      | _                                   | _      | —      | —      | _      |         |              | Exte         | nded Data | Space Rea   | d Page Add  | dress Regis  | ter      |       |       | 0001          |

| DSWPAG <sup>(1)</sup> | 0034 | _      | _                                   | _      | —      | —      | _      | _       |              |              | Extended  | d Data Spac | e Write Pag | e Address F  | Register |       |       | 0001          |

| RCOUNT                | 0036 |        |                                     |        |        |        |        | Repe    | eat Loop Co  | unter Regis  | ster      |             |             |              |          |       |       | xxxx          |

| SR                    | 0042 | —      | _                                   | —      | _      | _      | —      | _       | DC           | IPL2         | IPL1      | IPL0        | RA          | N            | OV       | Z     | С     | 0000          |

| CORCON                | 0044 | —      | _                                   | —      | —      | —      | —      | —       | —            | _            | —         | —           | —           | IPL3         | r        | —     | -     | 0004          |

| DISICNT               | 0052 | —      | Disable Interrupts Counter Register |        |        |        |        |         |              | xxxx         |           |             |             |              |          |       |       |               |

| TBLPAG                | 0054 | _      | _                                   | _      | _      | _      | _      | _       | _            |              |           | Table M     | emory Page  | e Address R  | egister  |       |       | 0000          |

# DS39969B-page 50

— = unimplemented, read as '0'; r = Reserved bit. Reset values are shown in hexadecimal. Reserved in PIC24FJXXXDA106 devices; do not use. Legend:

Note 1:

# TABLE 4-21: ADC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|---------|-------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ADC1BUF0     | 0300 |        |        |        |        |        |        |       | ADC Da  | ta Buffer 0 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF1     | 0302 |        |        |        |        |        |        |       | ADC Da  | ta Buffer 1 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF2     | 0304 |        |        |        |        |        |        |       | ADC Da  | ta Buffer 2 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF3     | 0306 |        |        |        |        |        |        |       | ADC Da  | ta Buffer 3 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF4     | 0308 |        |        |        |        |        |        |       | ADC Da  | ta Buffer 4 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF5     | 030A |        |        |        |        |        |        |       | ADC Da  | ta Buffer 5 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF6     | 030C |        |        |        |        |        |        |       | ADC Da  | ta Buffer 6 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF7     | 030E |        |        |        |        |        |        |       | ADC Da  | ta Buffer 7 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF8     | 0310 |        |        |        |        |        |        |       | ADC Da  | ta Buffer 8 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF9     | 0312 |        |        |        |        |        |        |       | ADC Da  | ta Buffer 9 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUFA     | 0314 |        |        |        |        |        |        |       | ADC Dat | a Buffer 10 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUFB     | 0316 |        |        |        |        |        |        |       | ADC Dat | a Buffer 11 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUFC     | 0318 |        |        |        |        |        |        |       | ADC Dat | a Buffer 12 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUFD     | 031A |        |        |        |        |        |        |       | ADC Dat | a Buffer 13 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUFE     | 031C |        |        |        |        |        |        |       | ADC Dat | a Buffer 14 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUFF     | 031E |        |        |        |        |        |        |       | ADC Dat | a Buffer 15 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF10    | 0340 |        |        |        |        |        |        |       | ADC Dat | a Buffer 16 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF11    | 0342 |        |        |        |        |        |        |       | ADC Dat | a Buffer 17 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF12    | 0344 |        |        |        |        |        |        |       | ADC Dat | a Buffer 18 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF13    | 0346 |        |        |        |        |        |        |       | ADC Dat | a Buffer 19 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF14    | 0348 |        |        |        |        |        |        |       | ADC Dat | a Buffer 20 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF15    | 034A |        |        |        |        |        |        |       | ADC Dat | a Buffer21  |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF16    | 034C |        |        |        |        |        |        |       | ADC Dat | a Buffer 22 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF17    | 034E |        |        |        |        |        |        |       | ADC Dat | a Buffer 23 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF18    | 0350 |        |        |        |        |        |        |       | ADC Dat | a Buffer 24 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF19    | 0352 |        |        |        |        |        |        |       | ADC Dat | a Buffer 25 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF1A    | 0354 |        |        |        |        |        |        |       | ADC Dat | a Buffer 26 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF1B    | 0356 |        |        |        |        |        |        |       | ADC Dat | a Buffer 27 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF1C    | 0358 |        |        |        |        |        |        |       | ADC Dat | a Buffer 28 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF1D    | 035A |        |        |        |        |        |        |       | ADC Dat | a Buffer 29 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF1E    | 035C |        |        |        |        |        |        |       | ADC Dat | a Buffer 30 |       |       |       |       |       |       |       | xxxx          |

| ADC1BUF1F    | 035E |        |        |        |        |        |        |       | ADC Dat | a Buffer 31 |       |       |       |       |       |       |       | xxxx          |

|              |      |        |        |        |        |        |        |       |         |             |       |       |       |       |       |       |       |               |

PIC24FJ256DA210 FAMILY

Legend:

-- = unimplemented, read as '0', r = reserved, maintain as '0'. Reset values are shown in hexadecimal.

Note

1:

Unimplemented in 64-pin devices, read as '0'

# TABLE 4-31: GRAPHICS REGISTER MAP

| File Name | Addr | Bit 15   | Bit 14   | Bit 13          | Bit 12             | Bit 11            | Bit 10          | Bit 9        | Bit 8             | Bit 7           | Bit 6         | Bit 5          | Bit 4            | Bit 3           | Bit 2           | Bit 1    | Bit 0    | All<br>Resets |

|-----------|------|----------|----------|-----------------|--------------------|-------------------|-----------------|--------------|-------------------|-----------------|---------------|----------------|------------------|-----------------|-----------------|----------|----------|---------------|

| G1CMDL    | 0700 |          |          |                 |                    |                   |                 | Graph        | ics Command F     | Register<15:0>  | ,             |                |                  |                 |                 |          |          | 0000          |

| G1CMDH    | 0702 |          |          |                 |                    |                   |                 | Graphi       | cs Command F      | Register<31:16  | >             |                |                  |                 |                 |          |          | 0000          |

| G1CON1    | 0704 | G1EN     | _        | G1SIDL          | GCMDWMK4           | GCMDWMK3          | GCMDWMK2        | GCMDWMK1     | GCMDWMK0          | PUBPP2          | PUBPP1        | PUBPP0         | GCMDCNT4         | GCMDCNT3        | GCMDCNT2        | GCMDCNT1 | GCMDCNT0 | 0000          |

| G1STAT    | 0706 | PUBUSY   | _        |                 | _                  | _                 | -               | _            | _                 | IPUBUSY         | RCCBUSY       | CHRBUSY        | VMRGN            | HMRGN           | CMDLV           | CMDFUL   | CMDMPT   | 0000          |

| G1IE      | 0708 | PUIE     |          |                 | _                  | _                 |                 | _            | _                 | IPUIE           | RCCIE         | CHRIE          | VMRGNIE          | HMRGNIE         | CMDLVIE         | CMDFULIE | CMDMPTIE | 0000          |

| G1IR      | 070A | PUIF     | -        |                 | —                  | —                 |                 | —            | —                 | IPUIF           | RCCIF         | CHRIF          | VMRGNIF          | HMRGNIF         | CMDLVIF         | CMDFULIF | CMDMPTIF | 0000          |

| G1W1ADRL  | 070C |          |          |                 |                    |                   |                 | GPU Work A   | Area 1 Start Ado  | dress Register∙ | <15:0>        |                |                  |                 |                 |          |          | 0000          |

| G1W1ADRH  | 070E | —        | —        | -               | -                  | —                 | —               | —            | —                 |                 |               | GPU Wo         | rk Area 1 Star   | Address Regi    | ster<23:16>     |          |          | 0000          |

| G1W2ADRL  | 0710 |          |          |                 |                    |                   |                 | GPU Work A   | Area 2 Start Ado  | dress Register  | <15:0>        |                |                  |                 |                 |          |          | 0000          |

| G1W2ADRH  | 0712 | —        | _        | —               | —                  | —                 | _               | _            | —                 |                 |               | GPU Wo         | rk Area 2 Star   | Address Regi    | ster<23:16>     |          |          | 0000          |

| G1PUW     | 0714 | —        | _        | —               | —                  | —                 |                 |              |                   |                 | GPU Wor       | k Area Width   | Register         |                 |                 |          |          | 0000          |

| G1PUH     | 0716 | _        | —        | _               | _                  | _                 |                 |              |                   |                 | GPU Wor       | k Area Heigh   | t Register       |                 |                 |          |          | 0000          |

| G1DPADRL  | 0718 |          |          |                 |                    |                   |                 | Display Bu   | uffer Start Addre | ess Register<1  | 5:0>          |                |                  |                 |                 |          |          | 0000          |

| G1DPADRH  | 071A | _        | —        | _               | —                  | _                 | _               | —            | —                 |                 |               | Display        | Buffer Start A   | ddress Registe  | er<23:16>       |          |          | 0000          |

| G1DPW     | 071C | —        | _        | _               | —                  | —                 |                 |              |                   |                 | Display F     | Frame Width    | Register         |                 |                 |          |          | 0000          |

| G1DPH     | 071E | —        | _        | _               | —                  | —                 |                 |              |                   |                 | Display F     | rame Height    | Register         |                 |                 |          |          | 0000          |

| G1DPWT    | 0720 | —        | _        | _               | —                  | —                 |                 |              |                   |                 | Display       | Total Width F  | Register         |                 |                 |          |          | 0000          |

| G1DPHT    | 0722 | —        | —        | —               | —                  | —                 |                 |              |                   |                 | Display       | Total Height F | Register         |                 |                 |          |          | 0000          |

| G1CON2    | 0724 | DPGWDTH1 | DPGWDTH0 | DPSTGER1        | DPSTGER0           | _                 | _               | DPTEST1      | DPTEST0           | DPBPP2          | DPBPP1        | DPBPP0         | —                | —               | DPMODE2         | DPMODE1  | DPMODE0  | 0000          |

| G1CON3    | 0726 | —        | —        | —               | —                  | —                 | —               | DPPINOE      | DPPOWER           | DPCLKPOL        | DPENPOL       | DPVSPOL        | DPHSPOL          | DPPWROE         | DPENOE          | DPVSOE   | DPHSOE   | 0000          |

| G1ACTDA   | 0728 |          |          | Number of       | Lines Before th    | ne First Active L | ine Register    |              |                   |                 |               | Number of      | Pixels Before t  | he First Active | Plxel Register  |          |          | 0000          |

| G1HSYNC   | 072A |          |          | HSYN            | IC Pulse-Width     | Configuration F   | Register        |              |                   |                 |               | HSYN           | IC Start Delay   | Configuration   | Register        |          |          | 0000          |

| G1VSYNC   | 072C |          |          | VSYN            | IC Pulse-Width     | Configuration F   | Register        |              |                   |                 |               | VSYN           | IC Start Delay   | Configuration   | Register        |          |          | 0000          |

| G1DBLCON  | 072E |          |          | ical Blanking S | Start to First Dis | played Line Co    | nfiguration Reg |              | 1                 |                 | Horizo        | ntal Blanking  | Start to First D | Displayed Line  | Configuration F | Regsiter |          | 0000          |

| G1CLUT    | 0730 | CLUTEN   | CLUTBUSY | —               | _                  | _                 | —               | CLUTTRD      | CLUTRWEN          |                 |               | Color Lo       | ook-Up Table N   | Memory Addres   | ss Register     |          |          | 0000          |

| G1CLUTWR  | 0732 |          |          |                 |                    |                   |                 |              | p Table Memor     |                 | •             |                |                  |                 |                 |          |          | 0000          |

| G1CLUTRD  | 0734 |          |          |                 |                    |                   |                 | Color Look-u | p Table Memor     | y Read Data R   | Register      |                |                  |                 |                 |          |          | 0000          |

| G1MRGN    | 0736 |          |          | V               | ertical Blanking   | Advance Regis     | ster            |              |                   |                 |               | Но             | rizontal Blanki  | ng Advance Re   | egister         |          |          | 0000          |

| G1CHRX    | 0738 | -        | —        | —               | -                  | _                 |                 |              |                   | Curre           | ent Character | X-Coordinate   | Position Reg     | ister           |                 |          |          | 0000          |

| G1CHRY    | 073A | _        | _        | _               | _                  | _                 |                 |              |                   | Curre           | ent Character | Y-Coordinate   | Position Regi    | ster            |                 |          |          | 0000          |

| G1IPU     | 073C | _        | _        | _               | _                  | _                 | _               | _            | _                 | _               | _             | HUFFERR        | BLCKERR          | LENERR          | WRAPERR         | IPUDONE  | BFINAL   | 0000          |

| G1DBEN    | 073E | GDBEN15  | GDBEN14  | GDBEN13         | GDBEN12            | GDBEN11           | GDBEN10         | GDBEN9       | GDBEN8            | GDBEN7          | GDBEN6        | GDBEN5         | GDBEN4           | GDBEN3          | GDBEN2          | GDBEN1   | GDBEN0   | 0000          |

Legend:

DS39969B-page 69

: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.6.2 PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

If a Flash location has been erased, it can be programmed using table write instructions to write an instruction word (24-bit) into the write latch. The TBLPAG register is loaded with the 8 Most Significant Bytes (MSB) of the Flash address. The TBLWTL and TBLWTH instructions write the desired data into the write latches and specify the lower 16 bits of the program memory address to write to. To configure the NVMCON register for a word write, set the NVMOP bits (NVMCON<3:0>) to '0011'. The write is performed by executing the unlock sequence and setting the WR bit (see Example 5-5). An equivalent procedure in 'C' compiler, using the MPLAB C30 compiler and built-in hardware functions is shown in Example 5-6.

#### EXAMPLE 5-5: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

| ; Setup a<br>MOV<br>MOV<br>MOV |                                                               | ;<br>;Initialize PM Page Boundary SFR<br>;Initialize a register with program memory address |

|--------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| MOV                            | #LOW_WORD_N, W2                                               | ;                                                                                           |

| MOV                            | #HIGH_BYTE_N, W3                                              | ;                                                                                           |

| TBLWTL                         | W2, [W0]                                                      | ; Write PM low word into program latch                                                      |

| TBLWTH                         | W3, [W0++]                                                    | ; Write PM high byte into program latch                                                     |

| ; Setup NV<br>MOV<br>MOV       | MCON for programming one word to<br>#0x4003, W0<br>W0, NVMCON | o data Program Memory<br>;<br>; Set NVMOP bits to 0011                                      |

| DISI                           | #5                                                            | ; Disable interrupts while the KEY sequence is written                                      |

| MOV.B                          | #0x55, W0                                                     | ; Write the key sequence                                                                    |

| MOV                            | W0, NVMKEY                                                    |                                                                                             |

| MOV.B                          | #0xAA, W0                                                     |                                                                                             |

| MOV                            | W0, NVMKEY                                                    |                                                                                             |

| BSET                           | NVMCON, #WR                                                   | ; Start the write cycle                                                                     |

| NOP                            |                                                               | ; Required delays                                                                           |

| NOP                            |                                                               |                                                                                             |

#### EXAMPLE 5-6: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY ('C' LANGUAGE CODE)

| // C example using MPLAB C30                  |                                      |

|-----------------------------------------------|--------------------------------------|

| unsigned int offset;                          |                                      |

| unsigned long progAddr = 0xXXXXXX;            | // Address of word to program        |

| unsigned int progDataL = 0xXXXX;              | // Data to program lower word        |

| unsigned char progDataH = 0xXX;               | // Data to program upper byte        |

|                                               |                                      |

| //Set up NVMCON for word programming          |                                      |

| NVMCON = 0x4003;                              | // Initialize NVMCON                 |

|                                               |                                      |

| //Set up pointer to the first memory locatio  | n to be written                      |

| TBLPAG = progAddr>>16;                        | // Initialize PM Page Boundary SFR   |

| offset = progAddr & 0xFFFF;                   | // Initialize lower word of address  |

|                                               |                                      |

| //Perform TBLWT instructions to write latche  | S                                    |

| <pre>builtin_tblwtl(offset, progDataL);</pre> | // Write to address low word         |

| <pre>builtin_tblwth(offset, progDataH);</pre> | // Write to upper byte               |

| asm("DISI #5");                               | // Block interrupts with priority <7 |

|                                               | // for next 5 instructions           |

| builtin_write_NVM();                          | // C30 function to perform unlock    |

|                                               | // sequence and set WR               |

|                                               | -                                    |

# REGISTER 7-17: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0          | U-0            | R/W-0                             | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|--------------|----------------|-----------------------------------|------------------|-------------------|-----------------|-----------------|--------|

| _            | _              | IC9IE                             | OC9IE            | SPI3IE            | SPF3IE          | U4TXIE          | U4RXIE |

| bit 15       |                |                                   |                  |                   |                 |                 | bit 8  |

| R/W-0        | R/W-0          | R/W-0                             | R/W-0            | R/W-0             | R/W-0           | R/W-0           | U-0    |

| U4ERIE       | USB1IE         | MI2C3IE                           | SI2C3IE          | U3TXIE            | U3RXIE          | U3ERIE          | _      |

| bit 7        |                |                                   |                  |                   |                 |                 | bit (  |

| Legend:      |                |                                   |                  |                   |                 |                 |        |

| R = Readab   | le bit         | W = Writable                      | bit              | U = Unimplen      | nented bit, rea | d as '0'        |        |

| -n = Value a | t POR          | '1' = Bit is set                  |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |

| bit 15-14    | Unimplemen     | ted: Read as '                    | )'               |                   |                 |                 |        |

| bit 13       | IC9IE: Input C | Capture Channe                    | el 9 Interrupt E | nable bit         |                 |                 |        |

|              |                | request enable<br>request not ena |                  |                   |                 |                 |        |

| bit 12       | •              | ut Compare Ch                     |                  | ipt Enable bit    |                 |                 |        |

|              | 1 = Interrupt  | request enable<br>request not ena | d                |                   |                 |                 |        |

| bit 11       | •              | Event Interrupt                   |                  |                   |                 |                 |        |

|              |                | request enable                    |                  |                   |                 |                 |        |

|              | •              | request not ena                   |                  |                   |                 |                 |        |

| bit 10       |                | 3 Fault Interrupt                 |                  |                   |                 |                 |        |

|              |                | request enable<br>request not ena |                  |                   |                 |                 |        |

| bit 9        | •              | RT4 Transmitter                   |                  | ble bit           |                 |                 |        |

|              | •              | request enable                    |                  |                   |                 |                 |        |

|              | -              | request not ena                   |                  |                   |                 |                 |        |

| bit 8        |                | RT4 Receiver Ir                   | •                | e bit             |                 |                 |        |

|              |                | request enable<br>request not ena |                  |                   |                 |                 |        |

| bit 7        |                | RT4 Error Interr                  |                  |                   |                 |                 |        |

|              |                | request enable                    | -                |                   |                 |                 |        |

|              | 0 = Interrupt  | request not ena                   | abled            |                   |                 |                 |        |

| bit 6        |                | B1 (USB OTG)                      | •                | le bit            |                 |                 |        |

|              |                | request enable                    |                  |                   |                 |                 |        |

| bit 5        | •              | request not ena<br>ster I2C3 Even |                  | hle hit           |                 |                 |        |

| bit 0        |                | request enable                    | -                |                   |                 |                 |        |

|              |                | request not ena                   |                  |                   |                 |                 |        |

| bit 4        | SI2C3IE: Slav  | ve I2C3 Event I                   | nterrupt Enabl   | e bit             |                 |                 |        |

|              | •              | request enable<br>request not ena |                  |                   |                 |                 |        |

| bit 3        | -              | RT3 Transmitter                   |                  | ble bit           |                 |                 |        |

|              | •              | request enable<br>request not ena |                  |                   |                 |                 |        |

| bit 2        | -              | RT3 Receiver Ir                   |                  | e bit             |                 |                 |        |

|              |                | request enable                    | -                |                   |                 |                 |        |

|              |                | request not ena                   |                  |                   |                 |                 |        |

# 8.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

## 8.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in CW2 must be programmed to '0'. (Refer to **Section 27.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSCx (OSCCON<10:8>) control bits do not control the clock selection when clock switching is disabled. However, the COSCx (OSCCON<14:12>) control bits will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN (OSCCON<0>) control bit has no effect when clock switching is disabled; It is held at '0' at all times.

#### 8.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- If desired, read the COSCx (OSCCON<14:12>) control bits to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSCx (OSCCON<10:8>) control bits for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bit values are transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or SOSC (if SOSCEN remains set).

- Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL modes are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

# 10.4.3.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Each register contains two 6-bit fields, with each field being associated with one RPn pin (see Register 10-29 through Register 10-44). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-4).

Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '000000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

| <b>TABLE 10-4</b> : | SELECTABLE OUTPUT SOURCES ( | (MAPS FUNCTION TO OUTPUT) |

|---------------------|-----------------------------|---------------------------|

|                     |                             |                           |

| Output Function Number <sup>(1)</sup> | Function             | Output Name              |

|---------------------------------------|----------------------|--------------------------|

| 0                                     | NULL <sup>(2)</sup>  | Null                     |

| 1                                     | C1OUT                | Comparator 1 Output      |

| 2                                     | C2OUT                | Comparator 2 Output      |

| 3                                     | U1TX                 | UART1 Transmit           |

| 4                                     | U1RTS <sup>(3)</sup> | UART1 Request To Send    |

| 5                                     | U2TX                 | UART2 Transmit           |

| 6                                     | U2RTS <sup>(3)</sup> | UART2 Request To Send    |

| 7                                     | SDO1                 | SPI1 Data Output         |

| 8                                     | SCK10UT              | SPI1 Clock Output        |

| 9                                     | SS1OUT               | SPI1 Slave Select Output |

| 10                                    | SDO2                 | SPI2 Data Output         |

| 11                                    | SCK2OUT              | SPI2 Clock Output        |

| 12                                    | SS2OUT               | SPI2 Slave Select Output |

| 18                                    | OC1                  | Output Compare 1         |

| 19                                    | OC2                  | Output Compare 2         |

| 20                                    | OC3                  | Output Compare 3         |

| 21                                    | OC4                  | Output Compare 4         |

| 22                                    | OC5                  | Output Compare 5         |

| 23                                    | OC6                  | Output Compare 6         |

| 24                                    | OC7                  | Output Compare 7         |

| 25                                    | OC8                  | Output Compare 8         |

| 28                                    | U3TX                 | UART3 Transmit           |

| 29                                    | U3RTS <sup>(3)</sup> | UART3 Request To Send    |

| 30                                    | U4TX                 | UART4 Transmit           |

| 31                                    | U4RTS <sup>(3)</sup> | UART4 Request To Send    |

| 32                                    | SDO3                 | SPI3 Data Output         |

| 33                                    | SCK3OUT              | SPI3 Clock Output        |

| 34                                    | SS3OUT               | SPI3 Slave Select Output |

| 35                                    | OC9                  | Output Compare 9         |

| 36                                    | C3OUT                | Comparator 3 Output      |

| 37-63                                 | (unused)             | NC                       |

**Note 1:** Setting the RPORx register with the listed value assigns that output function to the associated RPn pin.

2: The NULL function is assigned to all RPn outputs at device Reset and disables the RPn output function.

3: IrDA<sup>®</sup> BCLK functionality uses this output.

#### REGISTER 10-33: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | RP9R5 | RP9R4 | RP9R3 | RP9R2 | RP9R1 | RP9R0 |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | RP8R5 | RP8R4 | RP8R3 | RP8R2 | RP8R1 | RP8R0 |

| bit 7   |     |       |       |       |       | •     | bit 0 |

|         |     |       |       |       |       |       |       |

| Legend: |     |       |       |       |       |       |       |

| Legenu.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8**RP9R<5:0>:** RP9 Output Pin Mapping bits<br/>Peripheral output number n is assigned to pin, RP9 (see Table 10-4 for peripheral function numbers).bit 7-6**Unimplemented:** Read as '0'

- bit 5-0 **RP8R<5:0>:** RP8 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP8 (see Table 10-4 for peripheral function numbers).

## REGISTER 10-34: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP11R5 | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP11R<5:0>:** RP11 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP11 (see Table 10-4 for peripheral function numbers).

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP10R<5:0>:** RP10 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP10 (see Table 10-4 for peripheral function numbers).

# REGISTER 12-2: TyCON: TIMER3 AND TIMER5 CONTROL REGISTER<sup>(3)</sup>

| R/W-0 L<br>TON <sup>(1)</sup><br>bit 15 | J-0 R/W-0<br>— TSIDL <sup>(1)</sup>     | U-0                   | U-0                                     | U-0 | U-0                  | U-0   |  |

|-----------------------------------------|-----------------------------------------|-----------------------|-----------------------------------------|-----|----------------------|-------|--|

|                                         | - TSIDL <sup>(1)</sup>                  | _                     | _                                       | —   | _                    | —     |  |

| bit 15                                  |                                         |                       |                                         |     |                      |       |  |

| Γ                                       |                                         |                       |                                         |     |                      | bit 8 |  |

|                                         |                                         |                       |                                         |     |                      |       |  |

| U-0 R/                                  | W-0 R/W-0                               | R/W-0                 | U-0                                     | U-0 | R/W-0                | U-0   |  |

| — TG/                                   | TE <sup>(1)</sup> TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> | —                                       | —   | TCS <sup>(1,2)</sup> | —     |  |

| bit 7                                   |                                         |                       |                                         |     |                      | bit 0 |  |

|                                         |                                         |                       |                                         |     |                      |       |  |

| Legend:                                 |                                         |                       |                                         |     |                      |       |  |

| R = Readable bit                        | W = Writable                            | e bit                 | U = Unimplemented bit, read as '0'      |     |                      |       |  |

| -n = Value at POR '1' = Bit is set      |                                         |                       | '0' = Bit is cleared x = Bit is unknown |     |                      | iown  |  |

| bit 15   | <b>TON:</b> Timery On bit <sup>(1)</sup>                                                                                                |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Starts 16-bit Timery                                                                                                                |

|          | 0 = Stops 16-bit Timery                                                                                                                 |

| bit 14   | Unimplemented: Read as '0'                                                                                                              |

| bit 13   | TSIDL: Stop in Idle Mode bit <sup>(1)</sup>                                                                                             |

|          | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>   |

| bit 12-7 | Unimplemented: Read as '0'                                                                                                              |

| bit 6    | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(1)</sup>                                                                  |

|          | When TCS = 1:                                                                                                                           |

|          | This bit is ignored.                                                                                                                    |

|          | When TCS = 0:<br>1 = Gated time accumulation enabled                                                                                    |

|          | 0 = Gated time accumulation disabled                                                                                                    |

| bit 5-4  | TCKPS<1:0>: Timery Input Clock Prescale Select bits <sup>(1)</sup>                                                                      |

|          | 11 = 1:256                                                                                                                              |

|          | 10 = 1:64<br>01 = 1:8                                                                                                                   |

|          | 01 - 1.8<br>00 = 1.1                                                                                                                    |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                              |

| bit 1    | TCS: Timery Clock Source Select bit <sup>(1,2)</sup>                                                                                    |

|          | 1 = External clock from pin, TyCK (on the rising edge)                                                                                  |

|          | 0 = Internal clock (Fosc/2)                                                                                                             |

| bit 0    | Unimplemented: Read as '0'                                                                                                              |

| Note 1:  | When 32-bit operation is enabled (T2CON<3> or T4CON<3> = 1), these bits have no effect on Timery executions and through T2CON and T4CON |

operation; all timer functions are set through T2CON and T4CON.

2: If TCS = 1, RPINRx (TxCK) must be configured to an available RPn/RPIn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

**3:** Changing the value of TyCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

#### **REGISTER 14-1:** OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is only cleared by software

bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on OCx<sup>(2)</sup>

- 110 = Edge-Aligned PWM Mode on  $OCx^{(2)}$

- 101 = Double Compare Continuous Pulse mode: Initialize the OCx pin low, the toggle OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initialize the OCx pin low, toggle the OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: Compare events continuously toggle the OCx pin

- 010 = Single Compare Single-Shot mode: Initialize OCx pin high, compare event forces the OCx pin low

- 001 = Single Compare Single-Shot mode: Initialize OCx pin low, compare event forces the OCx pin high

- 000 = Output compare channel is disabled

- Note 1: The OCx output must also be configured to an available RPn pin. For more information, see Section 10.4 "Peripheral Pin Select (PPS)".

- 2: The Fault input enable and Fault status bits are valid when OCM<2:0> = 111 or 110.

- **3:** The Comparator 1 output controls the OC1-OC3 channels; Comparator 2 output controls the OC4-OC6 channels; Comparator 3 output controls the OC7-OC9 channels.

- 4: The OCFA/OCFB Fault input must also be configured to an available RPn/RPIn pin. For more information, see Section 10.4 "Peripheral Pin Select (PPS)".

#### 18.5.2 COMPLETE A CONTROL TRANSACTION TO A CONNECTED DEVICE

- 1. Follow the procedure described in Section 18.5.1 "Enable Host Mode and Discover a Connected Device" to discover a device.

- Set up the Endpoint Control register for bidirectional control transfers by writing 0Dh to U1EP0 (this sets the EPCONDIS, EPTXEN and EPHSHK bits).

- 3. Place a copy of the device framework setup command in a memory buffer. See *"Chapter 9 of the USB 2.0 Specification"* for information on the device framework command set.

- 4. Initialize the Buffer Descriptor (BD) for the current (even or odd) TX EP0 to transfer the eight bytes of command data for a device framework command (i.e., GET DEVICE DESCRIPTOR):

- a) Set the BD data buffer address (BD0ADR) to the starting address of the 8-byte memory buffer containing the command.

- b) Write 8008h to BD0STAT (this sets the UOWN bit and sets a byte count of 8).

- Set the USB device address of the target device in the address register (U1ADDR<6:0>). After a USB bus Reset, the device USB address will be zero. After enumeration, it will be set to another value between 1 and 127.

- 6. Write D0h to U1TOK; this is a SETUP token to Endpoint 0, the target device's default control pipe. This initiates a SETUP token on the bus, followed by a data packet. The device handshake is returned in the PID field of BD0STAT after the packets are complete. When the USB module updates BD0STAT, a transfer done interrupt is asserted (the TRNIF flag is set). This completes the setup phase of the setup transaction as referenced in *"Chapter 9 of the USB Specification"*.

- 7. To initiate the data phase of the setup transaction (i.e., get the data for the GET DEVICE DESCRIPTOR command), set up a buffer in memory to store the received data.

- 8. Initialize the current (even or odd) RX or TX (RX for IN, TX for OUT) EP0 BD to transfer the data.

- a) Write C040h to BD0STAT. This sets the UOWN, configures Data Toggle (DTS) to DATA1 and sets the byte count to the length of the data buffer (64 or 40h in this case).

- b) Set BD0ADR to the starting address of the data buffer.

- 9. Write the Token register with the appropriate IN or OUT token to Endpoint 0, the target device's default control pipe (e.g., write 90h to U1TOK for an IN token for a GET DEVICE DESCRIPTOR command). This initiates an IN token on the bus followed by a data packet from the device to the host. When the data packet completes, the BD0STAT is written and a transfer done interrupt is asserted (the TRNIF flag is set). For control transfers with a single packet data phase, this completes the data phase of the setup transaction as referenced in *"Chapter 9 of the USB Specification"*. If more data needs to be transferred, return to step 8.

- 10. To initiate the status phase of the setup transaction, set up a buffer in memory to receive or send the zero length status phase data packet.

- 11. Initialize the current (even or odd) TX EP0 BD to transfer the status data:

- a) Set the BDT buffer address field to the start address of the data buffer.

- b) Write 8000h to BD0STAT (set UOWN bit, configure DTS to DATA0 and set byte count to 0).

- 12. Write the Token register with the appropriate IN or OUT token to Endpoint 0, the target device's default control pipe (e.g., write 01h to U1TOK for an OUT token for a GET DEVICE DESCRIPTOR command). This initiates an OUT token on the bus followed by a zero length data packet from the host to the device. When the data packet completes, the BD is updated with the handshake from the device and a transfer done interrupt is asserted (the TRNIF flag is set). This completes the status phase of the setup transaction as described in *"Chapter 9 of the USB Specification"*.

- Note: Only one control transaction can be performed per frame.

## REGISTER 18-5: U1PWRC: USB POWER CONTROL REGISTER

| U-0    | U-0        | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |  |

|--------|------------|-----|-----|-----|-----|-----|-----|--|--|

| —      | —          | —   | —   | —   | —   | _   | —   |  |  |

| bit 15 | bit 15 bit |     |     |     |     |     |     |  |  |

| R/W-0, HS   | U-0 | U-0 | R/W-0   | U-0 | U-0 | R/W-0, HC | R/W-0  |  |

|-------------|-----|-----|---------|-----|-----|-----------|--------|--|

| UACTPND     | —   | —   | USLPGRD | _   | -   | USUSPND   | USBPWR |  |

| bit 7 bit 0 |     |     |         |     |     |           |        |  |

| Legend: HS = Hardware Settable bit |                  | HC = Hardware Clearable bit        |                    |  |

|------------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit                   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                  | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |