Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                |

| Number of I/O              | 52                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 96K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256da206-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 64/100-Pin, 16-Bit Flash Microcontrollers with Graphics Controller and USB On-The-Go (OTG)

#### **Graphics Controller Features:**

- Three Graphics Hardware Accelerators to Facilitate Rendering of Block Copying, Text and Unpacking of Compressed Data

- · Color Look-up Table (CLUT) with Maximum of 256 Entries

- 1/2/4/8/16 bits-per-pixel (bpp) Color Depth Set at

- Run Time

Display Resolution Programmable According to

Frame Buffer:

- Supports direct access to external memory on devices with EPMP

- Resolution supported is up to 480x272 @ 60 Hz, 16 bpp; 640x480 @ 30 Hz, 16 bpp or 640x480 @ 60 Hz, 8 bpp

- Supports Various Display Interfaces:

- 4/8/16-bit Monochrome STN

- 4/8/16-bit Color STN

- 9/12/18/24-bit Color TFT (18 and 24-bit displays are connected as 16-bit, 5-6-5 RGB color format)

#### **Universal Serial Bus Features:**

- USB v2.0 On-The-Go (OTG) Compliant

- Dual Role Capable Can act as either Host or Peripheral

- Low-Speed (1.5 Mbps) and Full-Speed (12 Mbps) USB Operation in Host mode

- Full-Speed USB Operation in Device mode

- High-Precision PLL for USB

- Supports up to 32 Endpoints (16 bidirectional):

- USB module can use the internal RAM location from 0x800 to 0xFFFF as USB endpoint buffers

- On-Chip USB Transceiver with Interface for Off-Chip Transceiver

- Supports Control, Interrupt, Isochronous and Bulk

Transfers

- On-Chip Pull-up and Pull-Down Resistors

#### **Peripheral Features:**

- Enhanced Parallel Master Port/Parallel Slave Port (EPMP/PSP), 100-pin devices only:

- Direct access from CPU with an Extended Data Space (EDS) interface

- 4, 8 and 16-bit wide data bus

- Up to 23 programmable address lines

- Up to 2 chip select lines

- Up to 2 Acknowledgement lines (one per chip select)

- Programmable address/data multiplexing

- Programmable address and data Wait states

- Programmable polarity on control signals

- · Peripheral Pin Select:

- Up to 44 available pins (100-pin devices)

- Three 3-Wire/4-Wire SPI modules (supports 4 Frame modes)

- Three I<sup>2</sup>C<sup>™</sup> modules Supporting Multi-Master/Slave modes and 7-Bit/10-Bit Addressing

- Four UART modules:

- Supports RS-485, RS-232, LIN/J2602 protocols and  $\text{IrDA}^{\textcircled{R}}$

- Five 16-Bit Timers/Counters with Programmable Prescaler

- Nine 16-Bit Capture Inputs, each with a Dedicated Time Base

- Nine 16-Bit Compare/PWM Outputs, each with a Dedicated Time Base

- Hardware Real-Time Clock and Calendar (RTCC)

- Enhanced Programmable Cyclic Redundancy Check (CRC) Generator

- Up to 5 External Interrupt Sources

|                 |         |                           |              | Re                 | emappa        | ble Per   | iphera                   | s   |      |                 |             |      |          |      | 9r                         |         |

|-----------------|---------|---------------------------|--------------|--------------------|---------------|-----------|--------------------------|-----|------|-----------------|-------------|------|----------|------|----------------------------|---------|

| PIC24FJ Device  | Pins    | Program Memory<br>(bytes) | SRAM (bytes) | Remappable<br>Pins | 16-Bit Timers | IC/OC PWM | UART w/IrDA <sup>®</sup> | IdS | I²C™ | 10-Bit A/D (ch) | Comparators | CTMU | EPMP/PSP | RTCC | <b>Graphics Controller</b> | USB OTG |

| PIC24FJ128DA106 | 64      | 128K                      | 24K          | 29                 | 5             | 9/9       | 4                        | 3   | 3    | 16              | 3           | Y    | Ν        | Y    | Y                          | Y       |

| PIC24FJ256DA106 | 64      | 256K                      | 24K          | 29                 | 5             | 9/9       | 4                        | 3   | 3    | 16              | 3           | Y    | Ν        | Y    | Y                          | Y       |

| PIC24FJ128DA110 | 100/121 | 128K                      | 24K          | 44                 | 5             | 9/9       | 4                        | 3   | 3    | 24              | 3           | Y    | Y        | Y    | Y                          | Y       |

| PIC24FJ256DA110 | 100/121 | 256K                      | 24K          | 44                 | 5             | 9/9       | 4                        | 3   | 3    | 24              | 3           | Y    | Y        | Y    | Y                          | Y       |

| PIC24FJ128DA206 | 64      | 128K                      | 96K          | 29                 | 5             | 9/9       | 4                        | 3   | 3    | 16              | 3           | Y    | Ν        | Y    | Y                          | Y       |

| PIC24FJ256DA206 | 64      | 256K                      | 96K          | 29                 | 5             | 9/9       | 4                        | 3   | 3    | 16              | 3           | Y    | Ν        | Y    | Y                          | Y       |

| PIC24FJ128DA210 | 100/121 | 128K                      | 96K          | 44                 | 5             | 9/9       | 4                        | 3   | 3    | 24              | 3           | Y    | Y        | Υ    | Y                          | Y       |

| PIC24FJ256DA210 | 100/121 | 256K                      | 96K          | 44                 | 5             | 9/9       | 4                        | 3   | 3    | 24              | 3           | Y    | Y        | Y    | Y                          | Y       |

#### **Table of Contents**

| 1.0   | Device Overview                                             |     |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Microcontrollers |     |

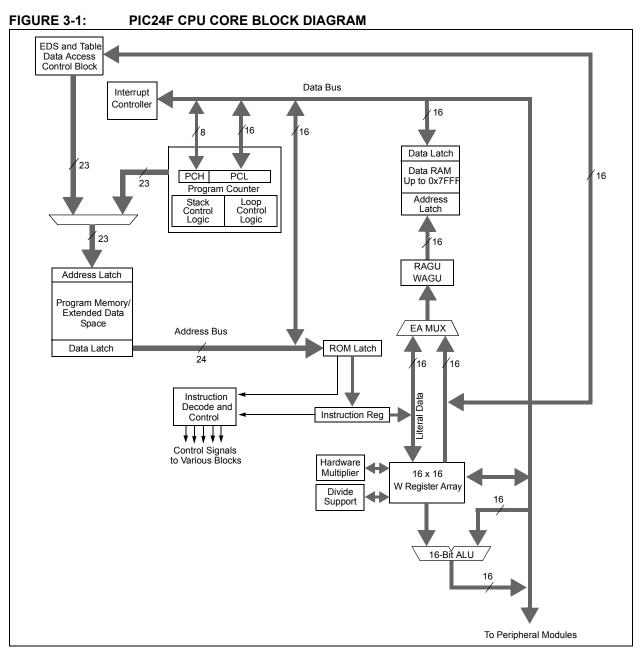

| 3.0   | CPU                                                         |     |

| 4.0   | Memory Organization                                         |     |

| 5.0   | Flash Program Memory                                        |     |

| 6.0   | Resets                                                      |     |

| 7.0   | Interrupt Controller                                        |     |

| 8.0   | Oscillator Configuration                                    | 141 |

| 9.0   | Power-Saving Features                                       | 155 |

| 10.0  | I/O Ports                                                   | 157 |

| 11.0  | Timer1                                                      | 189 |

| 12.0  |                                                             |     |

| 13.0  | Input Capture with Dedicated Timers                         | 197 |

| 14.0  | Output Compare with Dedicated Timers                        | 201 |

| 15.0  | Serial Peripheral Interface (SPI)                           |     |

| 16.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)               | 223 |

| 17.0  | Universal Asynchronous Receiver Transmitter (UART)          |     |

| 18.0  | Universal Serial Bus with On-The-Go Support (USB OTG)       |     |

| 19.0  | Enhanced Parallel Master Port (EPMP)                        |     |

| 20.0  | Real-Time Clock and Calendar (RTCC)                         |     |

| 21.0  | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator |     |

| 22.0  | Graphics Controller Module (GFX)                            |     |

| 23.0  | 10-Bit High-Speed A/D Converter                             |     |

| 24.0  | Triple Comparator Module                                    |     |

| 25.0  | Comparator Voltage Reference                                |     |

| 26.0  | Charge Time Measurement Unit (CTMU)                         |     |

| 27.0  | Special Features                                            |     |

| 28.0  | Development Support                                         |     |

|       | Instruction Set Summary                                     |     |

|       | Electrical Characteristics                                  |     |

|       | Packaging Information                                       |     |

| Appe  | endix A: Revision History                                   |     |

|       | Χ                                                           |     |

| The I | Microchip Web Site                                          | 405 |

|       | omer Change Notification Service                            |     |

|       | omer Support                                                |     |

|       | der Response                                                |     |

| Prod  | uct Identification System                                   | 407 |

#### 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including microcontrollers to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

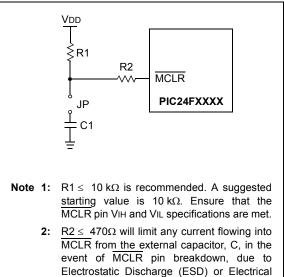

#### 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

Overstress (EOS). Ensure that the MCLR pin

VIH and VIL specifications are met.

| TABLE 3-1: | <b>CPU CORE REGISTERS</b> |

|------------|---------------------------|

|------------|---------------------------|

| Register(s) Name | Description                        |  |  |  |

|------------------|------------------------------------|--|--|--|

| W0 through W15   | Working Register Array             |  |  |  |

| PC               | 23-Bit Program Counter             |  |  |  |

| SR               | ALU STATUS Register                |  |  |  |

| SPLIM            | Stack Pointer Limit Value Register |  |  |  |

| TBLPAG           | Table Memory Page Address Register |  |  |  |

| RCOUNT           | Repeat Loop Counter Register       |  |  |  |

| CORCON           | CPU Control Register               |  |  |  |

| DISICNT          | Disable Interrupt Count Register   |  |  |  |

| DSRPAG           | Data Space Read Page Register      |  |  |  |

| DSWPAG           | Data Space Write Page Register     |  |  |  |

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | _   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R-1 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-----|-----|-------|

| —     | _   | —   | —   | IPL3 <sup>(1)</sup> | r   | —   | —     |

| bit 7 |     |     |     |                     |     |     | bit 0 |

| Legend:           | C = Clearable bit | r = Reserved bit       | HSC = Hardware Settable/Clearable bit |

|-------------------|-------------------|------------------------|---------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | , read as '0'                         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown                    |

bit 15-4 Unimplemented: Read as '0'

- bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup> 1 = CPU interrupt priority level is greater than 7 0 = CPU interrupt priority level is 7 or less

- bit 2 Reserved: Read as '1'

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level; see Register 3-1 for bit description.

#### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

#### REGISTER 7-21: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1                                                                                                                          | R/W-0                                    | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| —                | U1RXIP2                                                                                                                        | U1RXIP1                                  | U1RXIP0           | _                | SPI1IP2          | SPI1IP1         | SPI1IP0 |  |  |  |  |

| oit 15           |                                                                                                                                |                                          |                   |                  |                  |                 | bit     |  |  |  |  |

|                  |                                                                                                                                |                                          |                   |                  |                  |                 |         |  |  |  |  |

| U-0              | R/W-1                                                                                                                          | R/W-0                                    | R/W-0             | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|                  | SPF1IP2                                                                                                                        | SPF1IP1                                  | SPF1IP0           |                  | T3IP2            | T3IP1           | T3IP0   |  |  |  |  |

| bit 7            |                                                                                                                                |                                          |                   |                  |                  |                 | bit     |  |  |  |  |

| Legend:          |                                                                                                                                |                                          |                   |                  |                  |                 |         |  |  |  |  |

| R = Readab       | ole bit                                                                                                                        | W = Writable                             | bit               | U = Unimple      | mented bit, read | l as '0'        |         |  |  |  |  |

| -n = Value a     | at POR                                                                                                                         | '1' = Bit is set                         |                   | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |  |  |  |  |

|                  |                                                                                                                                |                                          |                   |                  |                  |                 |         |  |  |  |  |

| bit 15           | Unimplemen                                                                                                                     | ted: Read as '                           | )'                |                  |                  |                 |         |  |  |  |  |

| bit 14-12        | U1RXIP<2:0                                                                                                                     | >: UART1 Rece                            | iver Interrupt F  | Priority bits    |                  |                 |         |  |  |  |  |

|                  | <b>U1RXIP&lt;2:0&gt;:</b> UART1 Receiver Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                          |                   |                  |                  |                 |         |  |  |  |  |

|                  | •                                                                                                                              |                                          |                   |                  |                  |                 |         |  |  |  |  |

|                  |                                                                                                                                |                                          |                   |                  |                  |                 |         |  |  |  |  |

|                  | 001 = Interrupt is priority 1                                                                                                  |                                          |                   |                  |                  |                 |         |  |  |  |  |

|                  |                                                                                                                                | pt source is dis                         |                   |                  |                  |                 |         |  |  |  |  |

| bit 11           | Unimplemen                                                                                                                     | ited: Read as 'o                         | )'                |                  |                  |                 |         |  |  |  |  |

| bit 10-8         | <b>SPI1IP&lt;2:0&gt;:</b> SPI1 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)     |                                          |                   |                  |                  |                 |         |  |  |  |  |

|                  | 111 = Interru                                                                                                                  | pt is priority 7 (                       | highest priority  | interrupt)       |                  |                 |         |  |  |  |  |

|                  | •                                                                                                                              |                                          |                   |                  |                  |                 |         |  |  |  |  |

|                  | •                                                                                                                              |                                          |                   |                  |                  |                 |         |  |  |  |  |

|                  | 001 = Interru                                                                                                                  |                                          | ablad             |                  |                  |                 |         |  |  |  |  |

| bit 7            |                                                                                                                                | ipt source is dis<br>ited: Read as '(    |                   |                  |                  |                 |         |  |  |  |  |

|                  |                                                                                                                                |                                          |                   | hita             |                  |                 |         |  |  |  |  |

| bit 6-4          | <b>SPF1IP&lt;2:0&gt;:</b> SPI1 Fault Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)     |                                          |                   |                  |                  |                 |         |  |  |  |  |

|                  | •                                                                                                                              |                                          | ingricor priority | menuply          |                  |                 |         |  |  |  |  |

|                  | •                                                                                                                              |                                          |                   |                  |                  |                 |         |  |  |  |  |

|                  | •<br>001 = Interru                                                                                                             | pt is priority 1                         |                   |                  |                  |                 |         |  |  |  |  |

|                  |                                                                                                                                | ipt source is dis                        | abled             |                  |                  |                 |         |  |  |  |  |

|                  |                                                                                                                                | ited: Read as 'o                         |                   |                  |                  |                 |         |  |  |  |  |

| DIT 3            | -                                                                                                                              | imer3 Interrupt                          |                   |                  |                  |                 |         |  |  |  |  |

|                  |                                                                                                                                | •                                        | •                 | interrunt)       |                  |                 |         |  |  |  |  |

|                  | 111 = Interru                                                                                                                  | pt is priority 7 (                       | nignest priority  | interrupt)       |                  |                 |         |  |  |  |  |

|                  | 111 = Interru<br>•                                                                                                             | ipt is priority 7 (                      | nignest priority  | interrapt)       |                  |                 |         |  |  |  |  |

|                  | 111 = Interru<br>•                                                                                                             | ipt is priority 7 (                      | nignest priority  | interrupt/       |                  |                 |         |  |  |  |  |

| bit 3<br>bit 2-0 |                                                                                                                                | ıpt is priority 7 (<br>ıpt is priority 1 | nignest priority  | interrupt)       |                  |                 |         |  |  |  |  |

#### REGISTER 7-35: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0    | U-0  | U-0  | U-0  | U-0  | U-0 | U-0 | U-0   |

|--------|------|------|------|------|-----|-----|-------|

| —      | —    | —    | —    | —    | —   | —   | —     |

| bit 15 |      | •    |      |      |     |     | bit 8 |

|        |      |      |      |      |     |     |       |

| 11.0   | 11.0 | 11.0 | 11.0 | 11.0 |     |     |       |

| t | oit 7 |     |     |     |     |        |        | bit 0  |

|---|-------|-----|-----|-----|-----|--------|--------|--------|

|   | _     | _   | _   | _   | _   | LVDIP2 | LVDIP1 | LVDIP0 |

|   | U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1  | R/W-0  | R/W-0  |

#### Legend:

| Legenu.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

- bit 2-0 LVDIP<2:0>: Low-Voltage Detect Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)

- •

- •

- 001 = Interrupt is priority 1

- 000 = Interrupt source is disabled

#### REGISTER 7-36: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | _   | —   | —   | —     |

| bit 15 | •   |     |     |     |     |     | bit 8 |

| U-0       | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0 |

|-----------|---------|---------|---------|-----|-----|-----|-----|

| —         | CTMUIP2 | CTMUIP1 | CTMUIP0 | —   | —   | —   | —   |

| bit 7 bit |         |         |         |     |     |     |     |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

| bit 6-4 | CTMUIP<2:0>: CTMU Interrupt Priority bits                  |

|---------|------------------------------------------------------------|

|         | 111 = Interrupt is priority 7 (highest priority interrupt) |

|         | •                                                          |

|         | •                                                          |

|         | •                                                          |

|         | 001 = Interrupt is priority 1                              |

|         | 000 = Interrupt source is disabled                         |

| bit 3-0 | Unimplemented: Read as '0'                                 |

|         |                                                            |

#### 13.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs and the even module (ICy) provides the Most Significant 16 bits. Wrap-arounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bits (ICxCON2<8>) for both modules.

#### 13.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every 4<sup>th</sup> or 16<sup>th</sup>). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. Configure the ICx input for one of the available Peripheral Pin Select pins.

- 2. If Synchronous mode is to be used, disable the sync source before proceeding.

- 3. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 4. Set the SYNCSEL bits (ICxCON2<4:0>) to the desired sync/trigger source.

- 5. Set the ICTSEL bits (ICxCON1<12:10>) for the desired clock source.

- 6. Set the ICI bits (ICxCON1<6:5>) to the desired interrupt frequency

- 7. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSEL bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG, and clear the TRIGSTAT bit (ICxCON2<6>).

- 8. Set the ICM bits (ICxCON1<2:0>) to the desired operational mode.

- 9. Enable the selected sync/trigger source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8>) and (ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSEL and SYNCSEL bits for both modules to select the same sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSEL and SYNCSEL settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>). This forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICI bits (ICxCON1<6:5>) to set the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- Note: For Synchronous mode operation, enable the sync source as the last step. Both input capture modules are held in Reset until the sync source is enabled.

- Use the ICM bits of the odd module (ICxCON1<2:0>) to set the desired capture mode.

The module is ready to capture events when the time base and the sync/trigger source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the Isw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (performed automatically by hardware).

| R/W-0        | U-0 R/W-0 R/W-1, HC R/W-0 R/W-0 R/W-0 R/W                                                                                                 |                                     |                                                     |                   |                           |                   |                |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------|-------------------|---------------------------|-------------------|----------------|--|--|--|

| I2CEN        | - I2CSIDL SCLREL IPMIEN A10M DISSLW SMEN                                                                                                  |                                     |                                                     |                   |                           |                   |                |  |  |  |

| bit 15       |                                                                                                                                           |                                     |                                                     |                   |                           |                   | bit 8          |  |  |  |

| R/W-0        | R/W-0                                                                                                                                     | R/W-0                               | R/W-0, HC                                           | R/W-0, HC         | R/W-0, HC                 | R/W-0, HC         | R/W-0, HC      |  |  |  |

| GCEN         | STREN                                                                                                                                     | ACKDT                               | ACKEN                                               | RCEN              | PEN                       | RSEN              | SEN            |  |  |  |

| bit 7        |                                                                                                                                           |                                     |                                                     |                   |                           |                   | bit (          |  |  |  |

| Legend:      |                                                                                                                                           | HC = Hardwa                         | are Clearable bi                                    | t                 |                           |                   |                |  |  |  |

| R = Readab   | le bit                                                                                                                                    | W = Writable                        | bit                                                 | U = Unimplem      | nented bit, read          | 1 as '0'          |                |  |  |  |

| -n = Value a | t POR                                                                                                                                     | '1' = Bit is se                     | t                                                   | '0' = Bit is clea | ared                      | x = Bit is unkr   | own            |  |  |  |

| bit 15       | <b>12CEN:</b> 12Cx                                                                                                                        | Enable bit                          |                                                     |                   |                           |                   |                |  |  |  |

|              | 1 = Enables<br>0 = Disables                                                                                                               | the I2Cx modu                       | lle and configure<br>ule. All l <sup>2</sup> C™ pir | es the SDAx ar    | nd SCLx pins a            | s serial port pir | IS             |  |  |  |

| bit 14       |                                                                                                                                           | nted: Read as '                     | •                                                   |                   | a by port funct           | 10113             |                |  |  |  |

| bit 13       | -                                                                                                                                         | p in Idle Mode                      |                                                     |                   |                           |                   |                |  |  |  |

|              |                                                                                                                                           |                                     | peration when d<br>ation in Idle mo                 |                   | n Idle mode               |                   |                |  |  |  |

| bit 12       |                                                                                                                                           | •                                   |                                                     |                   | C slave)                  |                   |                |  |  |  |

|              | <b>SCLREL:</b> SCLx Release Control bit (when operating as I <sup>2</sup> C slave)<br>1 = Releases SCLx clock                             |                                     |                                                     |                   |                           |                   |                |  |  |  |

|              | 0 = Holds SCLx clock low (clock stretch)                                                                                                  |                                     |                                                     |                   |                           |                   |                |  |  |  |

|              | If STREN = 1:<br>Bit is R/W (i.e., software may write '0' to initiate stretch and write '1' to release clock). Hardware is clea           |                                     |                                                     |                   |                           |                   |                |  |  |  |

|              |                                                                                                                                           |                                     | nsmission. Hard                                     |                   |                           |                   |                |  |  |  |

|              | <u>If STREN = 0</u>                                                                                                                       |                                     |                                                     |                   |                           |                   |                |  |  |  |

|              | transmission                                                                                                                              |                                     | ay only write '1                                    | to release clo    | ock). Hardware            | e clear at begi   | nning of slave |  |  |  |

| bit 11       | IPMIEN: Inte                                                                                                                              | lligent Platform                    | Management I                                        | nterface (IPMI)   | Enable bit                |                   |                |  |  |  |

|              |                                                                                                                                           | •                                   | enabled; all addr                                   | resses are Ack    | nowledged                 |                   |                |  |  |  |

| bit 10       | 0 = IPMI mode is disabled<br>A10M: 10-Bit Slave Addressing bit                                                                            |                                     |                                                     |                   |                           |                   |                |  |  |  |

|              | 1 = I2CxADD is a 10-bit slave address                                                                                                     |                                     |                                                     |                   |                           |                   |                |  |  |  |

|              | 0 = I2CxADI                                                                                                                               | D is a 7-bit slav                   | e address                                           |                   |                           |                   |                |  |  |  |

| bit 9        | DISSLW: Disable Slew Rate Control bit                                                                                                     |                                     |                                                     |                   |                           |                   |                |  |  |  |

|              |                                                                                                                                           | e control disabl<br>e control enabl |                                                     |                   |                           |                   |                |  |  |  |

| bit 8        |                                                                                                                                           | us Input Levels                     |                                                     |                   |                           |                   |                |  |  |  |

|              |                                                                                                                                           | •                                   | olds compliant w                                    | vith SMBus spe    | cifications               |                   |                |  |  |  |

|              |                                                                                                                                           | the SMBus in                        |                                                     |                   |                           |                   |                |  |  |  |

| bit 7        |                                                                                                                                           |                                     | e bit (when operation                               | •                 | ,                         |                   |                |  |  |  |

|              | 1 = Enables<br>reception                                                                                                                  |                                     | a general call a                                    | address is rece   | ived in the I2C           | xRSR (module      | is enabled for |  |  |  |

|              |                                                                                                                                           |                                     | sabled                                              |                   |                           |                   |                |  |  |  |

|              | <ul> <li>General call address disabled</li> <li>STREN: SCL x Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)</li> </ul> |                                     |                                                     |                   |                           |                   |                |  |  |  |

| bit 6        | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.        |                                     |                                                     |                   |                           |                   |                |  |  |  |

| bit 6        | Used in conju                                                                                                                             | unction with the                    |                                                     |                   | s I <sup>2</sup> C slave) |                   |                |  |  |  |

#### 17.1 UART Baud Rate Generator (BRG)

The UART module includes a dedicated, 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 17-1 shows the formula for computation of the baud rate with BRGH = 0.

#### EQUATION 17-1: UART BAUD RATE WITH BRGH = $0^{(1,2)}$

Baud Rate =

$$\frac{FCY}{16 \cdot (UxBRG + 1)}$$

UxBRG =  $\frac{FCY}{16 \cdot Baud Rate} - 1$

**Note 1:** FCY denotes the instruction cycle clock frequency (FOSC/2).

**2:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 17-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 17-2 shows the formula for computation of the baud rate with BRGH = 1.

### EQUATION 17-2: UART BAUD RATE WITH BRGH = $1^{(1,2)}$

Baud Rate =

$$\frac{FCY}{4 \cdot (UxBRG + 1)}$$

UxBRG =  $\frac{FCY}{4 \cdot Baud Rate} - 1$

- **Note 1:** FCY denotes the instruction cycle clock frequency.

- **2:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FCY/4 (for UxBRG = 0) and the minimum baud rate possible is FCY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

#### EXAMPLE 17-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

| Desired Baud Rate    | = FCY/(16 (BRGx + 1))                                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------------------------|

| Solving for BRGx Va  | lue:                                                                                                                 |

| BRGx<br>BRGx         | = ((FCY/Desired Baud Rate)/16) - 1<br>= ((4000000/9600)/16) - 1                                                      |

| BRGx                 | = 25                                                                                                                 |

| Calculated Baud Rate | = 4000000/(16(25+1)) = 9615                                                                                          |

| Error                | <ul> <li>= (Calculated Baud Rate – Desired Baud Rate)<br/>Desired Baud Rate</li> <li>= (9615 – 9600)/9600</li> </ul> |

| Note: Based or       | FCY = FOSC/2; Doze mode and PLL are disabled.                                                                        |

#### 18.0 UNIVERSAL SERIAL BUS WITH ON-THE-GO SUPPORT (USB OTG)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, Section 27. "USB On-The-Go (OTG)" (DS39721). The information in this data sheet supersedes the information in the FRM.

PIC24FJ256DA210 family devices contain a full-speed and low-speed compatible, On-The-Go (OTG) USB Serial Interface Engine (SIE). The OTG capability allows the device to act either as a USB peripheral device or as a USB embedded host with limited host capabilities. The OTG capability allows the device to dynamically switch from device to host operation using OTG's Host Negotiation Protocol (HNP).

For more details on OTG operation, refer to the "On-The-Go Supplement to the USB 2.0 Specification", published by the USB-IF. For more details on USB operation, refer to the "Universal Serial Bus Specification", v2.0.

The USB OTG module offers these features:

- USB functionality in Device and Host modes, and OTG capabilities for application-controlled mode switching

- Software-selectable module speeds of full speed (12 Mbps) or low speed (1.5 Mbps, available in Host mode only)

- Support for all four USB transfer types: control, interrupt, bulk and isochronous

- 16 bidirectional endpoints for a total of 32 unique endpoints

- · DMA interface for data RAM access

- Queues up to sixteen unique endpoint transfers without servicing

- Integrated, on-chip USB transceiver with support for off-chip transceivers via a digital interface

- Integrated VBUS generation with on-chip comparators and boost generation, and support of external VBUS comparators and regulators through a digital interface

- Configurations for on-chip bus pull-up and pull-down resistors

A simplified block diagram of the USB OTG module is shown in Figure 18-1.

The USB OTG module can function as a USB peripheral device or as a USB host, and may dynamically switch between Device and Host modes under software control. In either mode, the same data paths and Buffer Descriptors (BDs) are used for the transmission and reception of data.

In discussing USB operation, this section will use a controller-centric nomenclature for describing the direction of the data transfer between the microcontroller and the USB. RX (Receive) will be used to describe transfers that move data from the USB to the microcontroller and TX (Transmit) will be used to describe transfers that move data from the microcontroller to the USB. Table 18-1 shows the relationship between data direction in this nomenclature and the USB tokens exchanged.

# TABLE 18-1:CONTROLLER-CENTRIC<br/>DATA DIRECTION FOR USB<br/>HOST OR TARGET

| USB Mode | Direction    |              |  |  |  |

|----------|--------------|--------------|--|--|--|

| OSD MODE | RX           | тх           |  |  |  |

| Device   | OUT or SETUP | IN           |  |  |  |

| Host     | IN           | OUT or SETUP |  |  |  |

This chapter presents the most basic operations needed to implement USB OTG functionality in an application. A complete and detailed discussion of the USB protocol and its OTG supplement are beyond the scope of this data sheet. It is assumed that the user already has a basic understanding of USB architecture and the latest version of the protocol.

Not all steps for proper USB operation (such as device enumeration) are presented here. It is recommended that application developers use an appropriate device driver to implement all of the necessary features. Microchip provides a number of application-specific resources, such as USB firmware and driver support. Refer to <u>www.microchip.com/usb</u> for the latest firmware and driver support.

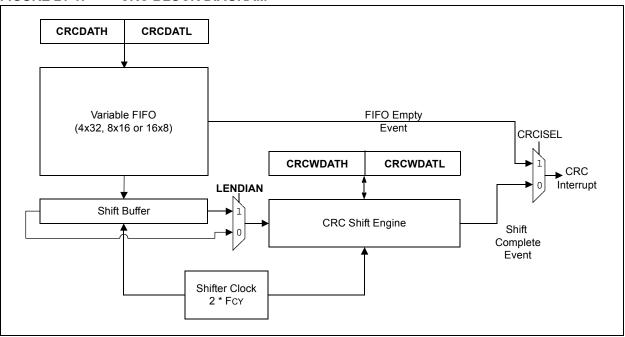

#### 21.0 32-BIT PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 41. "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS39729). The information in this data sheet supersedes the information in the FRM.

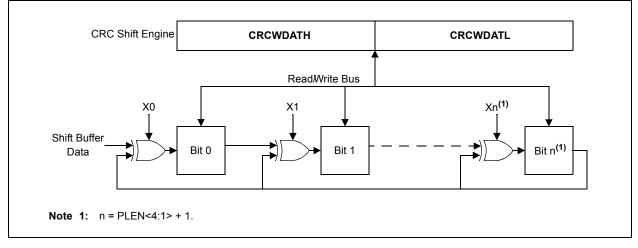

| FIGURE 21-1: | CRC BLOCK DIAGRAM |

|--------------|-------------------|

|              |                   |

The 32-bit programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

Figure 21-1 displays a simplified block diagram of the CRC generator. A simple version of the CRC shift engine is displayed in Figure 21-2.

#### REGISTER 22-23: G1VSYNC: VERTICAL SYNCHRONIZATION CONTROL REGISTER

| VSLEN7         VSLEN6         VSLEN5         VSLEN4         VSLEN3         VSLEN2         VSLEN1         VSLEN0           bit 15         bit 15 | R/W-0  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| bit 15 bi                                                                                                                                       | VSLEN7 | VSLEN6 | VSLEN5 | VSLEN4 | VSLEN3 | VSLEN2 | VSLEN1 | VSLEN0 |

|                                                                                                                                                 | bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| VSST7 | VSST6 | VSST5 | VSST4 | VSST3 | VSST2 | VSST1 | VSST0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-8

VSLEN<7:0>: VSYNC Pulse-Width Configuration bits (in lines) The DPVSOE bit (G1CON3<1>) must be set for the VSYNC signal to toggle; minimum value is 1.

bit 7-0

VSST<7:0>: VSYNC Start Delay Configuration bits (in lines) This is the number of lines from the start of vertical blanking to the start of VSYNC active.

#### REGISTER 22-24: G1DBLCON: DISPLAY BLANKING CONTROL REGISTER

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| VENST7 | VENST6 | VENST5 | VENST4 | VENST3 | VENST2 | VENST1 | VENST0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| HENST7 | HENST6 | HENST5 | HENST4 | HENST3 | HENST2 | HENST1 | HENST0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 **VENST<7:0>:** Vertical Blanking Start to First Displayed Line Configuration bits (in lines) This is the number of lines from the start of vertical blanking to the first displayed line of a frame.

bit 7-0 **HENST<7:0>:** Horizontal Blanking Start to First Displayed Pixel Configuration bits (in DISPCLKs) This is the number of GCLK cycles from the start of horizontal blanking to the first displayed pixel of each displayed line.

#### REGISTER 22-32: G1DBEN: DATA I/O PAD ENABLE REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| GDBEN15 | GDBEN14 | GDBEN13 | GDBEN12 | GDBEN11 | GDBEN10 | GDBEN9 | GDBEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| GDBEN7 | GDBEN6 | GDBEN5 | GDBEN4 | GDBEN3 | GDBEN2 | GDBEN1 | GDBEN0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 15-0 **GDBEN<15:0>:** Display Data Pads Output Enable bits

1 = Corresponding display data (GD<x>) pin is enabled

0 = Corresponding display data (GD<x>) pin is disabled

GDBEN<15:0> can be used to disable or enable specific data signals while the DPPINOE bit (G1CON3<9>) is set.

| DPPINOE | GDBENx<br>(where x = 0 to 15) |                                                              |

|---------|-------------------------------|--------------------------------------------------------------|

| 1       | 1                             | Display data signal (GD) associated with GDBENx is enabled.  |

| 1       | 0                             | Display data signal (GD) associated with GDBENx is disabled. |

| 0       | x                             | Display data signal (GD) associated with GDBENx is disabled. |

| REGISTER 27-1: | CW1: FLASH CONFIGURATION WORD 1 |

|----------------|---------------------------------|

|                |                                 |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| r-x      | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | r-1      | R/PO-1 | R/PO-1 |

|----------|--------|--------|--------|--------|----------|--------|--------|

| reserved | JTAGEN | GCP    | GWRP   | DEBUG  | reserved | ICS1   | ICS0   |

| bit 15   |        |        |        |        |          |        | bit 8  |

| R/PO-1 | R/PO-1 | R/PO-1                 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |

|--------|--------|------------------------|--------|--------|--------|--------|--------|

| FWDTEN | WINDIS | ALTVREF <sup>(1)</sup> | FWPSA  | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 |

| bit 7  |        |                        |        |        |        |        | bit 0  |

| Legend:           | r = Reserved bit |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | Reserved: The value is unknown; program as '0'                                                                                                                                                                                       |

| bit 14    | JTAGEN: JTAG Port Enable bit                                                                                                                                                                                                         |

|           | <ul><li>1 = JTAG port is enabled</li><li>0 = JTAG port is disabled</li></ul>                                                                                                                                                         |

| bit 13    | GCP: General Segment Program Memory Code Protection bit                                                                                                                                                                              |

|           | <ul> <li>1 = Code protection is disabled</li> <li>0 = Code protection is enabled for the entire program memory space</li> </ul>                                                                                                      |

| bit 12    | GWRP: General Segment Code Flash Write Protection bit                                                                                                                                                                                |

|           | <ul><li>1 = Writes to program memory are allowed</li><li>0 = Writes to program memory are not allowed</li></ul>                                                                                                                      |

| bit 11    | <b>DEBUG</b> : Background Debugger Enable bit                                                                                                                                                                                        |

|           | <ul><li>1 = Device resets into Operational mode</li><li>0 = Device resets into Debug mode</li></ul>                                                                                                                                  |

| bit 10    | Reserved: Always maintain as '1'                                                                                                                                                                                                     |

| bit 9-8   | ICS<1:0>: Emulator Pin Placement Select bits                                                                                                                                                                                         |

|           | <ul> <li>11 = Emulator functions are shared with PGEC1/PGED1</li> <li>10 = Emulator functions are shared with PGEC2/PGED2</li> <li>01 = Emulator functions are shared with PGEC3/PGED3</li> <li>00 = Reserved; do not use</li> </ul> |

| bit 7     | FWDTEN: Watchdog Timer Enable bit                                                                                                                                                                                                    |

|           | <ul><li>1 = Watchdog Timer is enabled</li><li>0 = Watchdog Timer is disabled</li></ul>                                                                                                                                               |

| bit 6     | WINDIS: Windowed Watchdog Timer Disable bit                                                                                                                                                                                          |

|           | <ul> <li>1 = Standard Watchdog Timer is enabled</li> <li>0 = Windowed Watchdog Timer is enabled; FWDTEN must be '1'</li> </ul>                                                                                                       |

| bit 5     | ALTVREF: Alternate VREF Pin Selection bit <sup>(1)</sup>                                                                                                                                                                             |

|           | 1 = VREF is on a default pin (VREF+ on RA10 and VREF- on RA9)                                                                                                                                                                        |

|           | 0 = VREF is on an alternate pin (VREF+ on RB0 and VREF- on RB1)                                                                                                                                                                      |

|           |                                                                                                                                                                                                                                      |

Note 1: Unimplemented in 64-pin devices, maintain at '1' (VREF+ on RB0 and VREF- on RB1).

U-0

\_\_\_\_

R FAMID0

R

bit 16

bit 8

| REGISTER 27-5: DEVID: DEVICE ID REGISTER |        |        |        |        |        |        |   |  |  |  |

|------------------------------------------|--------|--------|--------|--------|--------|--------|---|--|--|--|

| U-0                                      | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    |   |  |  |  |

| —                                        | —      | —      | —      | —      | —      | —      |   |  |  |  |

| bit 23                                   |        |        | •      |        | •      | •      |   |  |  |  |

|                                          |        |        |        |        |        |        |   |  |  |  |

| R                                        | R      | R      | R      | R      | R      | R      |   |  |  |  |

| FAMID7                                   | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 | FAMID1 | Γ |  |  |  |

| bit 15                                   |        |        |        |        |        |        |   |  |  |  |

|                                          |        |        |        |        |        |        |   |  |  |  |

| R                                        | R      | R      | R      | R      | R      | R      |   |  |  |  |

| DEV7                                     | DEV6   | DEV5   | DEV4   | DEV3   | DEV2   | DEV1   | Γ |  |  |  |

| DEV7  | DEV6 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

|-------|------|------|------|------|------|------|-------|

| bit 7 |      |      |      |      |      |      | bit 0 |

|       |      |      |      |      |      |      |       |

| Legend: | R = Readable bit | U = Unim | plemented bit |

|---------|------------------|----------|---------------|

|         |                  |          |               |

| bit 23-16 | Unimplemented: Read as '1' |

|-----------|----------------------------|

|-----------|----------------------------|

- bit 15-8 **FAMID<7:0>:** Device Family Identifier bits 01000001 = PIC24FJ256DA210 family

- bit 7-0 **DEV<7:0>:** Individual Device Identifier bits 00001000 = PIC24FJ128DA206 00001001 = PIC24FJ128DA106 00001010 = PIC24FJ128DA210 00001011 = PIC24FJ128DA110 00001100 = PIC24FJ256DA206 00001101 = PIC24FJ256DA106 00001110 = PIC24FJ256DA210 00001111 = PIC24FJ256DA110

#### 29.0 INSTRUCTION SET SUMMARY

| Note: | This chapter is a brief summary of the     |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | PIC24F instruction set architecture and is |  |  |  |  |  |

|       | not intended to be a comprehensive         |  |  |  |  |  |

|       | reference source.                          |  |  |  |  |  |

The PIC24F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from previous PIC MCU instruction sets. Most instructions are a single program memory word. Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction. The instruction set is highly orthogonal and is grouped into four basic categories:

- Word or byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

Table 29-1 shows the general symbols used in describing the instructions. The PIC24F instruction set summary in Table 29-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes, and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles.

Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

| DC CHARACTERISTICS                 |     |                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |       |            |                           |  |