Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 96K x 8                                                                         |

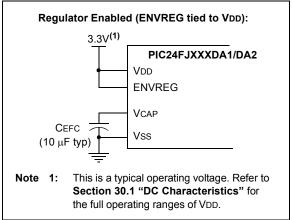

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256da206t-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

#### ISBN: 978-1-60932-235-9

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### 4.2 Data Memory Space

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 45. "Data Memory with Extended Data Space" (DS39733). The information in this data sheet supersedes the information in the FRM.

The PIC24F core has a 16-bit wide data memory space, addressable as a single linear range.

The data space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The data space memory map is shown in Figure 4-3.

The 16-bit wide data addresses in the data memory space point to bytes within the Data Space (DS). This gives a DS address range of 64 Kbytes or 32K words. The lower 32 Kbytes (0x0000 to 0x7FFF) of DS is compatible with the PIC24F microcontrollers without EDS.

The upper 32 Kbytes of data memory address space (0x8000 - 0xFFFF) are used as an EDS window.

The EDS window is used to access all memory region implemented in EDS, as shown in Figure 4-4.

The EDS includes any additional internal data memory not accessible by the lower 32-Kbyte data address space and any external memory through EPMP. For more details on accessing internal extended data memory, refer to the "*PIC24F Family Reference Manual*", Section 45. "Data Memory with Extended Data Space (EDS)" (DS39733). For more details on accessing external memory using EPMP, refer to the "*PIC24F Family Reference Manual*", Section 42. "Enhanced Parallel Master Port (EPMP)" (DS39730). In PIC24F microcontrollers with EDS, the program memory can also be read from EDS. This is called Program Space Visibility (PSV). Table 4-2 lists the total memory accessible by each of the devices in this family.

The EDS is organized as pages, with a single page called an EDS page that equals the EDS window (32 Kbytes). A particular EDS page is selected through the Data Space Read register (DSRPAG) or Data Space Write register (DSWPAG). For PSV, only the DSRPAG register is used. The combination of the DSRPAG register value and the 16-bit wide data address forms a 24-bit Effective Address (EA). For more information on EDS, refer to **Section 4.3.3 "Reading Data from Program Memory Using EDS"**.

| Devices         | Internal RAM                          | External RAM Access<br>Using EPMP | Program Memory Access<br>Using EDS |

|-----------------|---------------------------------------|-----------------------------------|------------------------------------|

| PIC24FJXXXDA210 | 96 Kbytes (30K + 66K <sup>(1)</sup> ) | Yes (up to 16 MB)                 | Yes                                |

| PIC24FJXXXDA206 | 96 Kbytes (30K + 66K <sup>(1)</sup> ) | No                                | Yes                                |

| PIC24FJXXXDA110 | 24 Kbytes                             | Yes (up to 16 MB)                 | Yes                                |

| PIC24FJXXXDA106 | 24 Kbytes                             | No                                | Yes                                |

#### TABLE 4-2:TOTAL MEMORY ACCESSIBLE BY THE DEVICE

Note 1: The internal RAM above 30 Kbytes can be accessed through EDS window.

#### TABLE 4-5: ICN REGISTER MAP

| File<br>Name | Addr | Bit 15                 | Bit 14                 | Bit 13                 | Bit 12                 | Bit 11                 | Bit 10                 | Bit 9                  | Bit 8                  | Bit 7                  | Bit 6                  | Bit 5                  | Bit 4                  | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0                  | All<br>Resets |

|--------------|------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------|

| CNPD1        | 0056 | CN15PDE                | CN14PDE                | CN13PDE                | CN12PDE                | CN11PDE                | CN10PDE                | CN9PDE                 | CN8PDE                 | CN7PDE                 | CN6PDE                 | CN5PDE                 | CN4PDE                 | CN3PDE                 | CN2PDE                 | CN1PDE                 | CN0PDE                 | 0000          |

| CNPD2        | 0058 | CN31PDE                | CN30PDE                | CN29PDE                | CN28PDE                | CN27PDE                | CN26PDE                | CN25PDE                | CN24PDE                | CN23PDE                | CN22PDE                | CN21PDE <sup>(1)</sup> | CN20PDE <sup>(1)</sup> | CN19PDE <sup>(1)</sup> | CN18PDE                | CN17PDE                | CN16PDE                | 0000          |

| CNPD3        | 005A | CN47PDE <sup>(1)</sup> | CN46PDE <sup>(1)</sup> | CN45PDE <sup>(1)</sup> | CN44PDE <sup>(1)</sup> | CN43PDE <sup>(1)</sup> | CN42PDE <sup>(1)</sup> | CN41PDE <sup>(1)</sup> | CN40PDE <sup>(1)</sup> | CN39PDE <sup>(1)</sup> | CN38PDE <sup>(1)</sup> | CN37PDE <sup>(1)</sup> | CN36PDE <sup>(1)</sup> | CN35PDE <sup>(1)</sup> | CN34PDE <sup>(1)</sup> | CN33PDE <sup>(1)</sup> | CN32PDE                | 0000          |

| CNPD4        | 005C | CN63PDE                | CN62PDE                | CN61PDE                | CN60PDE                | CN59PDE                | CN58PDE                | CN57PDE <sup>(1)</sup> | CN56PDE                | CN55PDE                | CN54PDE                | CN53PDE                | CN52PDE                | CN51PDE                | CN50PDE                | CN49PDE                | CN48PDE <sup>(1)</sup> | 0000          |

| CNPD5        | 005E | CN79PDE <sup>(1)</sup> | CN78PDE <sup>(1)</sup> | CN77PDE <sup>(1)</sup> | CN76PDE <sup>(1)</sup> | CN75PDE <sup>(1)</sup> | CN74PDE <sup>(1)</sup> | CN73PDE <sup>(1)</sup> | _                      | CN71PDE                | CN70PDE(1)             | CN69PDE                | CN68PDE                | CN67PDE <sup>(1)</sup> | CN66PDE <sup>(1)</sup> | CN65PDE                | CN64PDE                | 0000          |

| CNPD6        | 0060 | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | CN84PDE                | CN83PDE                | CN82PDE <sup>(1)</sup> | CN81PDE <sup>(1)</sup> | CN80PDE <sup>(1)</sup> | 0000          |

| CNEN1        | 0062 | CN15IE                 | CN14IE                 | CN13IE                 | CN12IE                 | CN11IE                 | CN10IE                 | CN9IE                  | CN8IE                  | CN7IE                  | CN6IE                  | CN5IE                  | CN4IE                  | <b>CN3IE</b>           | CN2IE                  | CN1IE                  | CN0IE                  | 0000          |

| CNEN2        | 0064 | CN31IE                 | CN30IE                 | CN29IE                 | CN28IE                 | CN27IE                 | CN26IE                 | CN25IE                 | CN24IE                 | CN23IE                 | CN22IE                 | CN21IE <sup>(1)</sup>  | CN20IE <sup>(1)</sup>  | CN19IE <sup>(1)</sup>  | CN18IE                 | CN17IE                 | CN16IE                 | 0000          |

| CNEN3        | 0066 | CN47IE <sup>(1)</sup>  | CN46IE <sup>(1)</sup>  | CN45IE <sup>(1)</sup>  | CN44IE <sup>(1)</sup>  | CN43IE <sup>(1)</sup>  | CN42IE <sup>(1)</sup>  | CN41IE <sup>(1)</sup>  | CN40IE <sup>(1)</sup>  | CN39IE <sup>(1)</sup>  | CN38IE <sup>(1)</sup>  | CN37IE <sup>(1)</sup>  | CN36IE <sup>(1)</sup>  | CN35IE <sup>(1)</sup>  | CN34IE <sup>(1)</sup>  | CN33IE <sup>(1)</sup>  | CN32IE                 | 0000          |

| CNEN4        | 0068 | CN63IE                 | CN62IE                 | CN61IE                 | CN60IE                 | CN59IE                 | CN58IE                 | CN57IE <sup>(1)</sup>  | CN56IE                 | CN55IE                 | CN54IE                 | CN53IE                 | CN52IE                 | CN51IE                 | CN50IE                 | CN49IE                 | CN48IE <sup>(1)</sup>  | 0000          |

| CNEN5        | 006A | CN79IE <sup>(1)</sup>  | CN78IE <sup>(1)</sup>  | CN77IE <sup>(1)</sup>  | CN76IE <sup>(1)</sup>  | CN75IE <sup>(1)</sup>  | CN74IE <sup>(1)</sup>  | CN73IE <sup>(1)</sup>  | _                      | CN71IE                 | CN70IE <sup>(1)</sup>  | CN69IE                 | CN68IE                 | CN67IE <sup>(1)</sup>  | CN66IE <sup>(1)</sup>  | CN65IE                 | CN64IE                 | 0000          |

| CNEN6        | 006C | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | _                      | —                      | CN84IE                 | CN83IE                 | CN82IE <sup>(1)</sup>  | CN81IE <sup>(1)</sup>  | CN80IE <sup>(1)</sup>  | 0000          |

| CNPU1        | 006E | CN15PUE                | CN14PUE                | CN13PUE                | CN12PUE                | CN11PUE                | CN10PUE                | CN9PUE                 | CN8PUE                 | CN7PUE                 | CN6PUE                 | CN5PUE                 | CN4PUE                 | <b>CN3PUE</b>          | CN2PUE                 | CN1PUE                 | CN0PUE                 | 0000          |

| CNPU2        | 0070 | CN31PUE                | CN30PUE                | CN29PUE                | CN28PUE                | CN27PUE                | CN26PUE                | CN25PUE                | CN24PUE                | CN23PUE                | CN22PUE                | CN21PUE <sup>(1)</sup> | CN20PUE <sup>(1)</sup> | CN19PUE <sup>(1)</sup> | CN18PUE                | CN17PUE                | CN16PUE                | 0000          |

| CNPU3        | 0072 | CN47PUE <sup>(1)</sup> | CN46PUE <sup>(1)</sup> | CN45PUE <sup>(1)</sup> | CN44PUE <sup>(1)</sup> | CN43PUE <sup>(1)</sup> | CN42PUE <sup>(1)</sup> | CN41PUE <sup>(1)</sup> | CN40PUE <sup>(1)</sup> | CN39PUE <sup>(1)</sup> | CN38PUE <sup>(1)</sup> | CN37PUE <sup>(1)</sup> | CN36PUE <sup>(1)</sup> | CN35PUE <sup>(1)</sup> | CN34PUE <sup>(1)</sup> | CN33PUE <sup>(1)</sup> | CN32PUE                | 0000          |

| CNPU4        | 0074 | CN63PUE                | CN62PUE                | CN61PUE                | CN60PUE                | CN59PUE                | CN58PUE                | CN57PUE <sup>(1)</sup> | CN56PUE                | CN55PUE                | CN54PUE                | CN53PUE                | CN52PUE                | CN51PUE                | CN50PUE                | CN49PUE                | CN48PUE <sup>(1)</sup> | 0000          |

| CNPU5        | 0076 | CN79PUE <sup>(1)</sup> | CN78PUE <sup>(1)</sup> | CN77PUE <sup>(1)</sup> | CN76PUE <sup>(1)</sup> | CN75PUE <sup>(1)</sup> | CN74PUE <sup>(1)</sup> | CN73PUE <sup>(1)</sup> | _                      | CN71PUE                | CN70PUE <sup>(1)</sup> | CN69PUE                | CN68PUE                | CN67PUE <sup>(1)</sup> | CN66PUE <sup>(1)</sup> | CN65PUE                | CN64PUE                | 0000          |

| CNPU6        | 0078 | _                      | _                      | _                      | _                      | _                      | _                      | _                      |                        |                        | —                      |                        | CN84PUE                | CN83PUE                | CN82PUE <sup>(1)</sup> | CN81PUE <sup>(1)</sup> | CN80PUE <sup>(1)</sup> | 0000          |

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note

1:

Unimplemented in 64-pin devices; read as '0'.

#### TABLE 4-6: **INTERRUPT CONTROLLER REGISTER MAP (CONTINUED)**

| File<br>Name | Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|--------|---------|---------|---------|--------|---------|---------|---------|-------|----------|----------|----------|---------|----------|----------|----------|---------------|

| IPC16        | 00C4 | —      | CRCIP2  | CRCIP1  | CRCIP0  | _      | U2ERIP2 | U2ERIP1 | U2ERIP0 |       | U1ERIP2  | U1ERIP1  | U1ERIP0  | -       | —        | _        | —        | 4440          |

| IPC18        | 00C8 | _      | _       | _       | _       | _      | _       | _       | _       | _     | _        | _        | _        | _       | LVDIP2   | LVDIP1   | LVDIP0   | 0004          |

| IPC19        | 00CA | _      | _       | _       | _       | _      | _       | _       | _       | _     | CTMUIP2  | CTMUIP1  | CTMUIP0  | _       | _        | -        | _        | 0040          |

| IPC20        | 00CC | _      | U3TXIP2 | U3TXIP1 | U3TXIP0 | _      | U3RXIP2 | U3RXIP1 | U3RXIP0 |       | U3ERIP2  | U3ERIP1  | U3ERIP0  | _       | —        | _        | _        | 4440          |

| IPC21        | 00CE | _      | U4ERIP2 | U4ERIP1 | U4ERIP0 | _      | USB1IP2 | USB1IP1 | USB1IP0 |       | MI2C3IP2 | MI2C3IP1 | MI2C3IP0 |         | SI2C3IP2 | SI2C3IP1 | SI2C3IP0 | 4444          |

| IPC22        | 00D0 | _      | SPI3IP2 | SPI3IP1 | SPI3IP0 | _      | SPF3IP2 | SPF3IP1 | SPF3IP0 | _     | U4TXIP2  | U4TXIP1  | U4TXIP0  | _       | U4RXIP2  | U4RXIP1  | U4RXIP0  | 4444          |

| IPC23        | 00D2 | _      | _       |         | _       | _      | _       | _       | _       |       | IC9IP2   | IC9IP1   | IC9IP0   | _       | OC9IP2   | OC9IP1   | OC9IP0   | 0044          |

| IPC25        | 00D6 | _      | _       |         | _       | _      | _       | _       | -       |       |          | -        | _        | _       | GFX1IP2  | GFX1IP1  | GFX1IP0  | 0004          |

| INTTREG      | 00E0 | CPUIRQ | _       | VHOLD   | _       | ILR3   | ILR2    | ILR1    | ILR0    |       | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

– = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Unimplemented in 64-pin devices, read as '0'.

The Reset value in 64-pin devices are '0004'. Legend:

Note 1:

2:

#### **TABLE 4-7:** TIMER REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                      | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8         | Bit 7         | Bit 6         | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|-----------------------------|--------|--------|--------|--------|--------------|---------------|---------------|---------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1         | 0100 |        |                             |        |        |        |        |              | Timer1        | Register      |               |        |        |       |       |       |       | 0000          |

| PR1          | 0102 |        |                             |        |        |        |        |              | Timer1 Peri   | od Register   |               |        |        |       |       |       |       | FFFF          |

| T1CON        | 0104 | TON    | _                           | TSIDL  | _      | _      | _      | _            | _             | —             | TGATE         | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| TMR2         | 0106 |        |                             |        |        |        |        |              | Timer2        | Register      |               |        |        |       |       |       |       | 0000          |

| TMR3HLD      | 0108 |        |                             |        |        |        | Time   | er3 Holding  | Register (for | 32-bit timer  | operations of | nly)   |        |       |       |       |       | 0000          |

| TMR3         | 010A |        |                             |        |        |        |        |              | Timer3        | Register      |               |        |        |       |       |       |       | 0000          |

| PR2          | 010C |        | Timer2 Period Register      |        |        |        |        |              |               |               | FFFF          |        |        |       |       |       |       |               |

| PR3          | 010E |        |                             |        |        |        |        |              | Timer3 Peri   | od Register   |               |        |        |       |       |       |       | FFFF          |

| T2CON        | 0110 | TON    | -                           | TSIDL  | -      |        | -      | —            | _             | —             | TGATE         | TCKPS1 | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T3CON        | 0112 | TON    | _                           | TSIDL  | _      | _      | _      | _            | _             | —             | TGATE         | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4         | 0114 |        |                             |        |        |        |        |              | Timer4        | Register      |               |        |        |       |       |       |       | 0000          |

| TMR5HLD      | 0116 |        |                             |        |        |        | Т      | imer5 Holdir | ng Register ( | for 32-bit op | erations only | ')     |        |       |       |       |       | 0000          |

| TMR5         | 0118 |        |                             |        |        |        |        |              | Timer5        | Register      |               |        |        |       |       |       |       | 0000          |

| PR4          | 011A |        | Timer4 Period Register FFF  |        |        |        |        |              |               |               | FFFF          |        |        |       |       |       |       |               |

| PR5          | 011C |        | Timer5 Period Register FFFF |        |        |        |        |              |               |               | FFFF          |        |        |       |       |       |       |               |

| T4CON        | 011E | TON    |                             | TSIDL  | _      | _      |        | _            | _             | —             | TGATE         | TCKPS1 | TCKPS0 | T45   | —     | TCS   | —     | 0000          |

| T5CON        | 0120 | TON    | _                           | TSIDL  | _      |        | _      |              | _             | —             | TGATE         | TCKPS1 | TCKPS0 | _     | _     | TCS   | —     | 0000          |

Legend:

- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>REGISTER 5-1:</b> NVMCON: FLASH MEMORY CONTROL REGISTER |

|------------------------------------------------------------|

|------------------------------------------------------------|

| R/S-0, HC(   | 1) R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                               | R-0, HSC <sup>(1)</sup>                                                      | U-0                           | U-0                               | U-0                                 | U-0                     | U-0                   |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------|-----------------------------------|-------------------------------------|-------------------------|-----------------------|--|

| WR           | WREN                                                                                                                                                                                                                                                                                                                                  | WRERR                                                                        | _                             | _                                 | _                                   | _                       | _                     |  |

| bit 15       |                                                                                                                                                                                                                                                                                                                                       |                                                                              |                               |                                   |                                     |                         | bit                   |  |

| U-0          | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                  | U-0                                                                          | U-0                           | R/W-0 <sup>(1)</sup>              | R/W-0 <sup>(1)</sup>                | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>  |  |

|              | ERASE                                                                                                                                                                                                                                                                                                                                 |                                                                              |                               | NVMOP3 <sup>(2)</sup>             | NVMOP2 <sup>(2)</sup>               | NVMOP1 <sup>(2)</sup>   | NVMOP0 <sup>(2)</sup> |  |

| bit 7        |                                                                                                                                                                                                                                                                                                                                       |                                                                              |                               |                                   | 1                                   | 1                       | bit                   |  |

| Legend:      |                                                                                                                                                                                                                                                                                                                                       | S = Settable bi                                                              | t                             | HSC = Hardw                       | are Settable/C                      | learable bit            |                       |  |

| R = Readat   | ole bit                                                                                                                                                                                                                                                                                                                               | W = Writable b                                                               | it                            | U = Unimplen                      | nented bit, read                    | l as '0'                |                       |  |

| -n = Value a | at POR                                                                                                                                                                                                                                                                                                                                | '1' = Bit is set                                                             |                               | '0' = Bit is clea                 | ared                                | x = Bit is unkr         | nown                  |  |

| HC = Hardv   | = Hardware Clearable bit                                                                                                                                                                                                                                                                                                              |                                                                              |                               |                                   |                                     |                         |                       |  |

| bit 15       | <ul> <li>WR: Write Control bit<sup>(1)</sup></li> <li>1 = Initiates a Flash memory program or erase operation; the operation is self-timed and the bit i cleared by hardware once the operation is complete</li> <li>0 = Program or erase operation is complete and inactive</li> <li>WREN: Write Enable bit<sup>(1)</sup></li> </ul> |                                                                              |                               |                                   |                                     |                         |                       |  |

| bit 14       | 1 = Enable I                                                                                                                                                                                                                                                                                                                          | e Enable bit <sup>ver</sup><br>Flash program/er<br>lash program/era          |                               |                                   |                                     |                         |                       |  |

| bit 13       |                                                                                                                                                                                                                                                                                                                                       | ite Sequence Err                                                             | -                             |                                   |                                     |                         |                       |  |

|              | automat                                                                                                                                                                                                                                                                                                                               | oper program o<br>ically on any set<br>gram or erase op                      | attempt of the                | e WR bit)                         | t or terminatic                     | n has occurre           | ed (bit is se         |  |

| bit 12-7     | Unimpleme                                                                                                                                                                                                                                                                                                                             | nted: Read as '0                                                             | 2                             |                                   |                                     |                         |                       |  |

| bit 6        | ERASE: Era                                                                                                                                                                                                                                                                                                                            | se/Program Enal                                                              | ble bit <sup>(1)</sup>        |                                   |                                     |                         |                       |  |

|              |                                                                                                                                                                                                                                                                                                                                       | the erase operate<br>the program operate                                     |                               |                                   |                                     |                         | nd                    |  |

| bit 5-4      | Unimpleme                                                                                                                                                                                                                                                                                                                             | nted: Read as '0                                                             | ,                             |                                   |                                     |                         |                       |  |

| bit 3-0      |                                                                                                                                                                                                                                                                                                                                       | >: NVM Operation                                                             |                               |                                   |                                     |                         |                       |  |

|              | 0011 = Mer<br>0010 = Mer                                                                                                                                                                                                                                                                                                              | nory bulk erase o<br>nory word progra<br>nory page erase<br>nory row prograr | am operation<br>operation (Ef | (ERASE = 0) or<br>RASE = 1) or no | r no operation (<br>o operation (EF | ERASE = 1)<br>RASE = 0) |                       |  |

|              |                                                                                                                                                                                                                                                                                                                                       | nly be reset on P                                                            |                               |                                   |                                     |                         |                       |  |

|              |                                                                                                                                                                                                                                                                                                                                       | ations of NVMOP                                                              |                               | •                                 |                                     |                         |                       |  |

| 3.           | Available in ICSI                                                                                                                                                                                                                                                                                                                     | P™ mode only re                                                              | eter to the dev               | /ice programmi                    | ng specification                    | ו                       |                       |  |

3: Available in ICSP<sup>™</sup> mode only; refer to the device programming specification.

#### 5.6.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time. To do this, it is necessary to erase the 8-row erase block containing the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-3).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- 6. Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-4.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY BLOCK (ASSEMBLY LANGUAGE CODE)

| ; Set up NVMCON for block erase oper | ation                                              |

|--------------------------------------|----------------------------------------------------|

| MOV #0x4042, W0 ;                    |                                                    |

| MOV W0, NVMCON                       | ; Initialize NVMCON                                |

| ; Init pointer to row to be ERASED   |                                                    |

| MOV #tblpage(PROG_ADDR), W0          | ;                                                  |

| MOV W0, TBLPAG                       | ; Initialize Program Memory (PM) Page Boundary SFR |

| MOV #tbloffset(PROG_ADDR), W0        | ; Initialize in-page EA<15:0> pointer              |

| TBLWTL W0, [W0]                      | ; Set base address of erase block                  |

| DISI #5                              | ; Block all interrupts with priority <7            |

|                                      | ; for next 5 instructions                          |

| MOV.B #0x55, W0                      |                                                    |

| MOV W0, NVMKEY                       | ; Write the 0x55 key                               |

| MOV.B #0xAA, W1 ;                    |                                                    |

| MOV W1, NVMKEY                       | ; Write the OxAA key                               |

| BSET NVMCON, #WR                     | ; Start the erase sequence                         |

| NOP                                  | ; Insert two NOPs after the erase                  |

| NOP                                  | ; command is asserted                              |

|                                      |                                                    |

| Interrupt Source                                    | Vector | IVT     | ΑΙΥΤ    | Inte     | errupt Bit Locat | ions         |

|-----------------------------------------------------|--------|---------|---------|----------|------------------|--------------|

| Interrupt Source                                    | Number | Address | Address | Flag     | Enable           | Priority     |

| ADC1 Conversion Done                                | 13     | 00002Eh | 00012Eh | IFS0<13> | IEC0<13>         | IPC3<6:4>    |

| Comparator Event                                    | 18     | 000038h | 000138h | IFS1<2>  | IEC1<2>          | IPC4<10:8>   |

| CRC Generator                                       | 67     | 00009Ah | 00019Ah | IFS4<3>  | IEC4<3>          | IPC16<14:12> |

| CTMU Event                                          | 77     | 0000AEh | 0001AEh | IFS4<13> | IEC4<13>         | IPC19<6:4>   |

| External Interrupt 0                                | 0      | 000014h | 000114h | IFS0<0>  | IEC0<0>          | IPC0<2:0>    |

| External Interrupt 1                                | 20     | 00003Ch | 00013Ch | IFS1<4>  | IEC1<4>          | IPC5<2:0>    |

| External Interrupt 2                                | 29     | 00004Eh | 00014Eh | IFS1<13> | IEC1<13>         | IPC7<6:4>    |

| External Interrupt 3                                | 53     | 00007Eh | 00017Eh | IFS3<5>  | IEC3<5>          | IPC13<6:4>   |

| External Interrupt 4                                | 54     | 000080h | 000180h | IFS3<6>  | IEC3<6>          | IPC13<10:8>  |

| Graphics Controller                                 | 100    | 0000DCh | 0001DCh | IFS6<4>  | IEC6<4>          | IPC25<2:0>   |

| I2C1 Master Event                                   | 17     | 000036h | 000136h | IFS1<1>  | IEC1<1>          | IPC4<6:4>    |

| I2C1 Slave Event                                    | 16     | 000034h | 000134h | IFS1<0>  | IEC1<0>          | IPC4<2:0>    |

| I2C2 Master Event                                   | 50     | 000078h | 000178h | IFS3<2>  | IEC3<2>          | IPC12<10:8>  |

| I2C2 Slave Event                                    | 49     | 000076h | 000176h | IFS3<1>  | IEC3<1>          | IPC12<6:4>   |

| I2C3 Master Event                                   | 85     | 0000BEh | 0001BEh | IFS5<5>  | IEC5<5>          | IPC21<6:4>   |

| I2C3 Slave Event                                    | 84     | 0000BCh | 0001BCh | IFS5<4>  | IEC5<4>          | IPC21<2:0>   |

| Input Capture 1                                     | 1      | 000016h | 000116h | IFS0<1>  | IEC0<1>          | IPC0<6:4>    |

| Input Capture 2                                     | 5      | 00001Eh | 00011Eh | IFS0<5>  | IEC0<5>          | IPC1<6:4>    |

| Input Capture 3                                     | 37     | 00005Eh | 00015Eh | IFS2<5>  | IEC2<5>          | IPC9<6:4>    |

| Input Capture 4                                     | 38     | 000060h | 000160h | IFS2<6>  | IEC2<6>          | IPC9<10:8>   |

| Input Capture 5                                     | 39     | 000062h | 000162h | IFS2<7>  | IEC2<7>          | IPC9<14:12>  |

| Input Capture 6                                     | 40     | 000064h | 000164h | IFS2<8>  | IEC2<8>          | IPC10<2:0>   |

| Input Capture 7                                     | 22     | 000040h | 000140h | IFS1<6>  | IEC1<6>          | IPC5<10:8>   |

| Input Capture 8                                     | 23     | 000042h | 000142h | IFS1<7>  | IEC1<7>          | IPC5<14:12>  |

| Input Capture 9                                     | 93     | 0000CEh | 0001CEh | IFS5<13> | IEC5<13>         | IPC23<6:4>   |

| Input Change Notification (ICN)                     | 19     | 00003Ah | 00013Ah | IFS1<3>  | IEC1<3>          | IPC4<14:12>  |

| Low-Voltage Detect (LVD)                            | 72     | 0000A4h | 0001A4h | IFS4<8>  | IEC4<8>          | IPC18<2:0>   |

| Output Compare 1                                    | 2      | 000018h | 000118h | IFS0<2>  | IEC0<2>          | IPC0<10:8>   |

| Output Compare 2                                    | 6      | 000020h | 000120h | IFS0<6>  | IEC0<6>          | IPC1<10:8>   |

| Output Compare 3                                    | 25     | 000046h | 000146h | IFS1<9>  | IEC1<9>          | IPC6<6:4>    |

| Output Compare 4                                    | 26     | 000048h | 000148h | IFS1<10> | IEC1<10>         | IPC6<10:8>   |

| Output Compare 5                                    | 41     | 000066h | 000166h | IFS2<9>  | IEC2<9>          | IPC10<6:4>   |

| Output Compare 6                                    | 42     | 000068h | 000168h | IFS2<10> | IEC2<10>         | IPC10<10:8>  |

| Output Compare 7                                    | 43     | 00006Ah | 00016Ah | IFS2<11> | IEC2<11>         | IPC10<14:12> |

| Output Compare 8                                    | 44     | 00006Ch | 00016Ch | IFS2<12> | IEC2<12>         | IPC11<2:0>   |

| Output Compare 9                                    | 92     | 0000CCh | 0001CCh | IFS5<12> | IEC5<12>         | IPC23<2:0>   |

| Enhanced Parallel Master Port (EPMP) <sup>(1)</sup> | 45     | 00006Eh | 00016Eh | IFS2<13> | IEC2<13>         | IPC11<6:4>   |

| Real-Time Clock and Calendar (RTCC)                 | 62     | 000090h | 000190h | IFS3<14> | IEC3<14>         | IPC15<10:8>  |

| SPI1 Error                                          | 9      | 000026h | 000126h | IFS0<9>  | IEC0<9>          | IPC2<6:4>    |

| SPI1 Event                                          | 10     | 000028h | 000128h | IFS0<10> | IEC0<10>         | IPC2<10:8>   |

| SPI2 Error                                          | 32     | 000054h | 000154h | IFS2<0>  | IEC2<0>          | IPC8<2:0>    |

| SPI2 Event                                          | 33     | 000056h | 000156h | IFS2<1>  | IEC2<1>          | IPC8<6:4>    |

| SPI3 Error                                          | 90     | 0000C8h | 0001C8h | IFS5<10> | IEC5<10>         | IPC22<10:8>  |

| SPI3 Event                                          | 91     | 0000CAh | 0001CAh | IFS5<11> | IEC5<11>         | IPC22<14:12> |

#### TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS

**Note 1:** Not available in 64-pin devices (PIC24FJXXXDAX06).

### REGISTER 7-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | r-1 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-----|-----|-------|

| _     | —   | _   | —   | IPL3 <sup>(1)</sup> | r   | —   | —     |

| bit 7 |     |     |     |                     |     |     | bit 0 |

| Legend:           | r = Reserved bit | C = Clearable bit          | HSC = Hardware Settable/Clearable bit |

|-------------------|------------------|----------------------------|---------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'                             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown                    |

bit 15-4 Unimplemented: Read as '0'

- bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup>

- 1 = CPU interrupt priority level is greater than 7

- 0 = CPU interrupt priority level is 7 or less

- bit 2 Reserved: Read as '1'

- bit 1-0 Unimplemented: Read as '0'

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level; see Register 3-2 for bit description.

### REGISTER 7-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5 (CONTINUED)

- bit 1 U3ERIF: UART3 Error Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

- bit 0 Unimplemented: Read as '0'

### REGISTER 7-11: IFS6: INTERRUPT FLAG STATUS REGISTER 6

| U-0     | U-0                        | U-0 | U-0       | U-0 | U-0 | U-0 | U-0   |

|---------|----------------------------|-----|-----------|-----|-----|-----|-------|

| _       | —                          | —   | —         | _   | —   | —   | —     |

| bit 15  |                            |     |           |     |     |     | bit 8 |

|         |                            |     |           |     |     |     |       |

| U-0     | U-0                        | U-0 | R/W-0, HS | U-0 | U-0 | U-0 | U-0   |

| _       | —                          | —   | GFX1IF    |     | —   | —   | —     |

| bit 7   |                            |     |           |     |     |     | bit 0 |

|         |                            |     |           |     |     |     |       |

| Legend: | HS = Hardware Settable bit |     |           |     |     |     |       |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-5 Unimplemented: Read as '0'

| bit 4 | GFX1IF: Graphics 1 Interrupt Flag Status bit       |

|-------|----------------------------------------------------|

|       | <ol> <li>Interrupt request has occurred</li> </ol> |

|       | 0 = Interrupt request has not occurred             |

bit 3-0 Unimplemented: Read as '0'

#### REGISTER 7-19: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

|                  | R/W-1                                                                                                                                        | R/W-0                                                                                                                                                                                                | R/W-0                                                                                                    | U-0                                      | R/W-1            | R/W-0           | R/W-0   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|-----------------|---------|

|                  | T1IP2                                                                                                                                        | T1IP1                                                                                                                                                                                                | T1IP0                                                                                                    |                                          | OC1IP2           | OC1IP1          | OC1IP0  |

| pit 15           |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 | bit     |

|                  |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          | <b>-</b>         | 5444.6          |         |

| U-0              | R/W-1                                                                                                                                        | R/W-0                                                                                                                                                                                                | R/W-0                                                                                                    | U-0                                      | R/W-1            | R/W-0           | R/W-0   |

|                  | IC1IP2                                                                                                                                       | IC1IP1                                                                                                                                                                                               | IC1IP0                                                                                                   |                                          | INT0IP2          | INT0IP1         | INT0IP0 |

| oit 7            |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 | bit     |

| Legend:          |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 |         |

| R = Readab       | ole bit                                                                                                                                      | W = Writable t                                                                                                                                                                                       | bit                                                                                                      | U = Unimple                              | mented bit, read | d as '0'        |         |

| -n = Value a     | It POR                                                                                                                                       | '1' = Bit is set                                                                                                                                                                                     |                                                                                                          | '0' = Bit is cle                         | eared            | x = Bit is unkr | nown    |

|                  |                                                                                                                                              |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 |         |

| bit 15           | Unimpleme                                                                                                                                    | ented: Read as '0                                                                                                                                                                                    | ) 7                                                                                                      |                                          |                  |                 |         |

| bit 14-12        | -                                                                                                                                            | Timer1 Interrupt                                                                                                                                                                                     |                                                                                                          |                                          |                  |                 |         |

|                  |                                                                                                                                              | rupt is priority 7 (h                                                                                                                                                                                | ,                                                                                                        | / interrupt)                             |                  |                 |         |

|                  | •                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                          | • •                                      |                  |                 |         |

|                  | •                                                                                                                                            |                                                                                                                                                                                                      |                                                                                                          |                                          |                  |                 |         |

|                  | 001 = Inter                                                                                                                                  | rupt is priority 1                                                                                                                                                                                   |                                                                                                          |                                          |                  |                 |         |

|                  | 000 = Inter                                                                                                                                  | rupt source is disa                                                                                                                                                                                  | abled                                                                                                    |                                          |                  |                 |         |

| bit 11           | Unimpleme                                                                                                                                    | ented: Read as '0                                                                                                                                                                                    | '                                                                                                        |                                          |                  |                 |         |

| oit 10-8         | OC1IP<2:0                                                                                                                                    | >: Output Compa                                                                                                                                                                                      | re Channel 1                                                                                             | Interrupt Priori                         | ty bits          |                 |         |

|                  | 111 — linterr                                                                                                                                | upt is priority 7 (h                                                                                                                                                                                 | iahest priority                                                                                          | (interrunt)                              |                  |                 |         |

|                  | $\perp \perp \perp = interi$                                                                                                                 | upt is priority 7 (i                                                                                                                                                                                 | ingricor priority                                                                                        | interrupt)                               |                  |                 |         |

|                  | 111 = Interr<br>•                                                                                                                            |                                                                                                                                                                                                      | ingricor priority                                                                                        | interrupt)                               |                  |                 |         |

|                  | •<br>•<br>•                                                                                                                                  |                                                                                                                                                                                                      | ignoot priority                                                                                          | menupty                                  |                  |                 |         |

|                  |                                                                                                                                              | rupt is priority 1                                                                                                                                                                                   |                                                                                                          | interrupt)                               |                  |                 |         |

|                  | 001 = Inter                                                                                                                                  |                                                                                                                                                                                                      |                                                                                                          | interrupt)                               |                  |                 |         |

| bit 7            | •<br>•<br>•<br>001 = Inter<br>000 = Inter                                                                                                    | rupt is priority 1                                                                                                                                                                                   | abled                                                                                                    | interrupt)                               |                  |                 |         |

|                  | •<br>•<br>001 = Inter<br>000 = Inter<br>Unimpleme                                                                                            | rupt is priority 1<br>rupt source is disa                                                                                                                                                            | abled                                                                                                    |                                          | ts               |                 |         |

| bit 7<br>bit 6-4 | •<br>•<br>001 = Inter<br>000 = Inter<br>Unimpleme<br>IC1IP<2:0>                                                                              | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0                                                                                                                                       | abled<br>, <sup>,</sup><br>hannel 1 Inter                                                                | rupt Priority bi                         | ts               |                 |         |

|                  | •<br>•<br>001 = Inter<br>000 = Inter<br>Unimpleme<br>IC1IP<2:0>                                                                              | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C                                                                                                                  | abled<br>, <sup>,</sup><br>hannel 1 Inter                                                                | rupt Priority bi                         | ts               |                 |         |

|                  | •<br>•<br>001 = Inter<br>000 = Inter<br>Unimpleme<br>IC1IP<2:0>                                                                              | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C                                                                                                                  | abled<br>, <sup>,</sup><br>hannel 1 Inter                                                                | rupt Priority bi                         | ts               |                 |         |

|                  | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                           | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1                                                                   | abled<br>,'<br>hannel 1 Inter<br>highest priority                                                        | rupt Priority bi                         | ts               |                 |         |

| bit 6-4          | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                           | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa                                            | abled<br>,,<br>hannel 1 Inter<br>nighest priority<br>abled                                               | rupt Priority bi                         | ts               |                 |         |

| bit 6-4<br>bit 3 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (f<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0                       | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled                                               | rupt Priority bi<br>/ interrupt)         | ts               |                 |         |

| bit 6-4<br>bit 3 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>>: External Intern | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled<br>,'<br>upt 0 Priority b                     | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

| bit 6-4<br>bit 3 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (f<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0                       | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled<br>,'<br>upt 0 Priority b                     | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

|                  | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>>: External Intern | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled<br>,'<br>upt 0 Priority b                     | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

| bit 6-4<br>bit 3 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                  | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>>: External Intern | abled<br>,'<br>hannel 1 Inter<br>highest priority<br>abled<br>,'<br>upt 0 Priority b                     | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

| bit 6-4<br>bit 3 | 001 = Inten<br>000 = Inten<br>Unimpleme<br>IC1IP<2:0><br>111 = Inten<br>001 = Inten<br>Unimpleme<br>INT0IP<2:0<br>111 = Inten<br>001 = Inten | rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>: Input Capture C<br>rupt is priority 7 (h<br>rupt is priority 1<br>rupt source is disa<br>ented: Read as '0<br>>: External Intern | abled<br>,,<br>hannel 1 Inter<br>highest priority<br>abled<br>,,<br>upt 0 Priority b<br>highest priority | rupt Priority bi<br>/ interrupt)<br>bits | ts               |                 |         |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | —   | RP29R5 | RP29R4 | RP29R3 | RP29R2 | RP29R1 | RP29R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8**RP29R<5:0>:** RP29 Output Pin Mapping bits<br/>Peripheral output number n is assigned to pin, RP29 (see Table 10-4 for peripheral function numbers).bit 7-6**Unimplemented:** Read as '0'