Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

|                           |                                                                                 |

| Product Status            | Active                                                                          |

| Core Processor            | PIC                                                                             |

| Core Size                 | 16-Bit                                                                          |

| Speed                     | 32MHz                                                                           |

| Connectivity              | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB OTG                                |

| Peripherals               | Brown-out Detect/Reset, GFX, LVD, POR, PWM, WDT                                 |

| Number of I/O             | 84                                                                              |

| Program Memory Size       | 256KB (85.5K x 24)                                                              |

| Program Memory Type       | FLASH                                                                           |

| EEPROM Size               | -                                                                               |

| AAM Size                  | 96K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                     |

| ata Converters            | A/D 24x10b                                                                      |

| Oscillator Type           | Internal                                                                        |

| perating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Nounting Type             | Surface Mount                                                                   |

| ackage / Case             | 121-TFBGA                                                                       |

| Supplier Device Package   | 121-TFBGA (10x10)                                                               |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256da210t-i-bg |

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R-1 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-----|-----|-------|

| _     | _   | _   | _   | IPL3 <sup>(1)</sup> | r   | _   | _     |

| bit 7 |     |     |     |                     |     |     | bit 0 |

| Legend:           | C = Clearable bit | r = Reserved bit           | HSC = Hardware Settable/Clearable bit |

|-------------------|-------------------|----------------------------|---------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, rea | d as '0'                              |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown                    |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit (1)

1 = CPU interrupt priority level is greater than 7

0 = CPU interrupt priority level is 7 or less

bit 2 Reserved: Read as '1'

bit 1-0 **Unimplemented:** Read as '0'

**Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level; see Register 3-1 for bit description.

### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as  $\overline{\text{Borrow}}$  and  $\overline{\text{Digit}}$  Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

**TABLE 4-11: UART REGISTER MAPS**

| File<br>Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7           | Bit 6       | Bit 5 | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|------|----------|--------|----------|--------|--------|--------|-----------|-------------|-----------------|-------------|-------|-------------|--------|--------|--------|-------|---------------|

| U1MODE       | 0220 | UARTEN   | -      | USIDL    | IREN   | RTSMD  | _      | UEN1      | UEN0        | WAKE            | LPBACK      | ABAUD | RXINV       | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF     | TRMT        | URXISEL1        | URXISEL0    | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224 | -        | _      | -        | _      | _      |        | _         |             |                 |             | UART1 | Transmit Re | gister |        |        |       | xxxx          |

| U1RXREG      | 0226 | 1        | 1      | _        | 1      | _      | _      | _         |             |                 |             | UART1 | Receive Re  | gister |        |        |       | 0000          |

| U1BRG        | 0228 |          |        |          |        |        |        | UART1 Bau | d Rate Gene | erator Prescale | er Register |       |             |        |        |        |       | 0000          |

| U2MODE       | 0230 | UARTEN   | -      | USIDL    | IREN   | RTSMD  | _      | UEN1      | UEN0        | WAKE            | LPBACK      | ABAUD | RXINV       | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA        | 0232 | UTXISEL1 | UTXINV | UTXISEL0 | 1      | UTXBRK | UTXEN  | UTXBF     | TRMT        | URXISEL1        | URXISEL0    | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U2TXREG      | 0234 | 1        | 1      | _        | 1      | _      | _      | _         |             |                 |             | UART2 | Transmit Re | gister |        |        |       | xxxx          |

| U2RXREG      | 0236 | ı        | -      | _        | ı      | _      | _      | _         |             |                 |             | UART2 | Receive Re  | gister |        |        |       | 0000          |

| U2BRG        | 0238 |          |        |          |        |        |        | UART2 Bau | d Rate Gene | erator Prescale | er Register |       |             |        |        |        |       | 0000          |

| U3MODE       | 0250 | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1      | UEN0        | WAKE            | LPBACK      | ABAUD | RXINV       | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U3STA        | 0252 | UTXISEL1 | UTXINV | UTXISEL0 | -      | UTXBRK | UTXEN  | UTXBF     | TRMT        | URXISEL1        | URXISEL0    | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U3TXREG      | 0254 | _        | _      | _        | -      | _      | _      | _         |             |                 |             | UART3 | Transmit Re | gister |        |        |       | xxxx          |

| U3RXREG      | 0256 | -        | _      | _        | _      | _      | _      | _         |             |                 |             | UART3 | Receive Re  | gister |        |        |       | 0000          |

| U3BRG        | 0258 |          |        |          |        |        |        | UART3 Bau | d Rate Gene | erator Prescale | er Register |       |             |        |        |        |       | 0000          |

| U4MODE       | 02B0 | UARTEN   | -      | USIDL    | IREN   | RTSMD  | _      | UEN1      | UEN0        | WAKE            | LPBACK      | ABAUD | RXINV       | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U4STA        | 02B2 | UTXISEL1 | UTXINV | UTXISEL0 | -      | UTXBRK | UTXEN  | UTXBF     | TRMT        | URXISEL1        | URXISEL0    | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U4TXREG      | 02B4 | 1        | -      | _        | -      | _      | _      | _         |             |                 |             | UART4 | Transmit Re | gister |        |        |       | xxxx          |

| U4RXREG      | 02B6 | 1        | _      | _        | -      | _      | _      | _         |             |                 |             | UART4 | Receive Re  | gister |        |        |       | 0000          |

| U4BRG        | 02B8 |          |        |          |        |        |        | UART4 Bau | d Rate Gene | erator Prescale | er Register |       |             |        |        |        |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-12: SPI REGISTER MAPS

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8         | Bit 7        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|---------|--------|--------|---------|---------|---------------|--------------|--------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT     | 0240 | SPIEN  | 1      | SPISIDL | 1      |        | SPIBEC2 | SPIBEC1 | SPIBEC0       | SRMPT        | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242 | -      | 1      | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE           | SSEN         | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244 | FRMEN  | SPIFSD | SPIFPOL |        | _      | _       | _       | _             | _            | _      | _      | _      | _      | _      | SPIFE  | SPIBEN | 0000          |

| SPI1BUF      | 0248 |        |        |         |        |        |         | SPI     | 1 Transmit an | nd Receive B | uffer  |        |        |        |        |        |        | 0000          |

| SPI2STAT     | 0260 | SPIEN  | _      | SPISIDL | 1      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0       | SRMPT        | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1     | 0262 | _      | _      | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE           | SSEN         | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2     | 0264 | FRMEN  | SPIFSD | SPIFPOL | -      | _      | _       | _       | _             | _            | _      | _      | _      | _      | _      | SPIFE  | SPIBEN | 0000          |

| SPI2BUF      | 0268 |        |        |         |        |        |         | SPI     | 2 Transmit an | nd Receive B | uffer  |        |        |        |        |        |        | 0000          |

| SPI3STAT     | 0280 | SPIEN  | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0       | SRMPT        | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI3CON1     | 0282 | _      | _      | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE           | SSEN         | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI3CON2     | 0284 | FRMEN  | SPIFSD | SPIFPOL | _      | _      | _       | _       | _             | _            | _      | _      | _      | _      | _      | SPIFE  | SPIBEN | 0000          |

| SPI3BUF      | 0288 |        |        |         |        |        |         | SPI     | 3 Transmit an | nd Receive B | uffer  |        |        |        |        |        |        | 0000          |

PIC24FJ256DA210 FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-13: PORTA REGISTER MAP<sup>(1)</sup>

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit2   | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|--------|--------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 02C0 | TRISA15 | TRISA14 | _      | _      | _      | TRISA10 | TRISA9 | _     | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | C6FF          |

| PORTA        | 02C2 | RA15    | RA14    | _      | _      | 1      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA         | 02C4 | LATA15  | LATA14  | -      | -      | 1      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA         | 02C6 | ODA15   | ODA14   | _      | _      | _      | ODA10   | ODA9   | _     | ODA7   | ODA6   | ODA5   | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Reset values shown are for 100-pin devices.

Note 1: PORTA and all associated bits are unimplemented on 64-pin devices and read as '0'. Bits are available on 100-pin devices only, unless otherwise noted.

#### **TABLE 4-14: PORTB REGISTER MAP**

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 02CE | ODB15   | ODB14   | ODB13   | ODB12   | ODB11   | ODB10   | ODB9   | ODB8   | ODB7   | ODB6   | ODB5   | ODB4   | ODB3   | ODB2   | ODB1   | ODB0   | 0000          |

Legend: Reset values are shown in hexadecimal.

TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS

| Intermed Course                         | Vector | IVT     | AIVT    | Inte     | errupt Bit Locat | ions         |

|-----------------------------------------|--------|---------|---------|----------|------------------|--------------|

| Interrupt Source                        | Number | Address | Address | Flag     | Enable           | Priority     |

| ADC1 Conversion Done                    | 13     | 00002Eh | 00012Eh | IFS0<13> | IEC0<13>         | IPC3<6:4>    |

| Comparator Event                        | 18     | 000038h | 000138h | IFS1<2>  | IEC1<2>          | IPC4<10:8>   |

| CRC Generator                           | 67     | 00009Ah | 00019Ah | IFS4<3>  | IEC4<3>          | IPC16<14:12> |

| CTMU Event                              | 77     | 0000AEh | 0001AEh | IFS4<13> | IEC4<13>         | IPC19<6:4>   |

| External Interrupt 0                    | 0      | 000014h | 000114h | IFS0<0>  | IEC0<0>          | IPC0<2:0>    |

| External Interrupt 1                    | 20     | 00003Ch | 00013Ch | IFS1<4>  | IEC1<4>          | IPC5<2:0>    |

| External Interrupt 2                    | 29     | 00004Eh | 00014Eh | IFS1<13> | IEC1<13>         | IPC7<6:4>    |

| External Interrupt 3                    | 53     | 00007Eh | 00017Eh | IFS3<5>  | IEC3<5>          | IPC13<6:4>   |

| External Interrupt 4                    | 54     | 000080h | 000180h | IFS3<6>  | IEC3<6>          | IPC13<10:8>  |

| Graphics Controller                     | 100    | 0000DCh | 0001DCh | IFS6<4>  | IEC6<4>          | IPC25<2:0>   |

| I2C1 Master Event                       | 17     | 000036h | 000136h | IFS1<1>  | IEC1<1>          | IPC4<6:4>    |

| I2C1 Slave Event                        | 16     | 000034h | 000134h | IFS1<0>  | IEC1<0>          | IPC4<2:0>    |

| I2C2 Master Event                       | 50     | 000078h | 000178h | IFS3<2>  | IEC3<2>          | IPC12<10:8>  |

| I2C2 Slave Event                        | 49     | 000076h | 000176h | IFS3<1>  | IEC3<1>          | IPC12<6:4>   |

| I2C3 Master Event                       | 85     | 0000BEh | 0001BEh | IFS5<5>  | IEC5<5>          | IPC21<6:4>   |

| I2C3 Slave Event                        | 84     | 0000BCh | 0001BCh | IFS5<4>  | IEC5<4>          | IPC21<2:0>   |

| Input Capture 1                         | 1      | 000016h | 000116h | IFS0<1>  | IEC0<1>          | IPC0<6:4>    |

| Input Capture 2                         | 5      | 00001Eh | 00011Eh | IFS0<5>  | IEC0<5>          | IPC1<6:4>    |

| Input Capture 3                         | 37     | 00005Eh | 00015Eh | IFS2<5>  | IEC2<5>          | IPC9<6:4>    |

| Input Capture 4                         | 38     | 000060h | 000160h | IFS2<6>  | IEC2<6>          | IPC9<10:8>   |

| Input Capture 5                         | 39     | 000062h | 000162h | IFS2<7>  | IEC2<7>          | IPC9<14:12>  |

| Input Capture 6                         | 40     | 000064h | 000164h | IFS2<8>  | IEC2<8>          | IPC10<2:0>   |

| Input Capture 7                         | 22     | 000040h | 000140h | IFS1<6>  | IEC1<6>          | IPC5<10:8>   |

| Input Capture 8                         | 23     | 000042h | 000142h | IFS1<7>  | IEC1<7>          | IPC5<14:12>  |

| Input Capture 9                         | 93     | 0000CEh | 0001CEh | IFS5<13> | IEC5<13>         | IPC23<6:4>   |

| Input Change Notification (ICN)         | 19     | 00003Ah | 00013Ah | IFS1<3>  | IEC1<3>          | IPC4<14:12>  |

| Low-Voltage Detect (LVD)                | 72     | 0000A4h | 0001A4h | IFS4<8>  | IEC4<8>          | IPC18<2:0>   |

| Output Compare 1                        | 2      | 000018h | 000118h | IFS0<2>  | IEC0<2>          | IPC0<10:8>   |

| Output Compare 2                        | 6      | 000020h | 000120h | IFS0<6>  | IEC0<6>          | IPC1<10:8>   |

| Output Compare 3                        | 25     | 000046h | 000146h | IFS1<9>  | IEC1<9>          | IPC6<6:4>    |

| Output Compare 4                        | 26     | 000048h | 000148h | IFS1<10> | IEC1<10>         | IPC6<10:8>   |

| Output Compare 5                        | 41     | 000066h | 000166h | IFS2<9>  | IEC2<9>          | IPC10<6:4>   |

| Output Compare 6                        | 42     | 000068h | 000168h | IFS2<10> | IEC2<10>         | IPC10<10:8>  |

| Output Compare 7                        | 43     | 00006Ah | 00016Ah | IFS2<11> | IEC2<11>         | IPC10<14:12> |

| Output Compare 8                        | 44     | 00006Ch | 00016Ch | IFS2<12> | IEC2<12>         | IPC11<2:0>   |

| Output Compare 9                        | 92     | 0000CCh | 0001CCh | IFS5<12> | IEC5<12>         | IPC23<2:0>   |

| Enhanced Parallel Master Port (EPMP)(1) | 45     | 00006Eh | 00016Eh | IFS2<13> | IEC2<13>         | IPC11<6:4>   |

| Real-Time Clock and Calendar (RTCC)     | 62     | 000090h | 000190h | IFS3<14> | IEC3<14>         | IPC15<10:8>  |

| SPI1 Error                              | 9      | 000026h | 000126h | IFS0<9>  | IEC0<9>          | IPC2<6:4>    |

| SPI1 Event                              | 10     | 000028h | 000128h | IFS0<10> | IEC0<10>         | IPC2<10:8>   |

| SPI2 Error                              | 32     | 000054h | 000154h | IFS2<0>  | IEC2<0>          | IPC8<2:0>    |

| SPI2 Event                              | 33     | 000056h | 000156h | IFS2<1>  | IEC2<1>          | IPC8<6:4>    |

| SPI3 Error                              | 90     | 0000C8h | 0001C8h | IFS5<10> | IEC5<10>         | IPC22<10:8>  |

| SPI3 Event                              | 91     | 0000CAh | 0001CAh | IFS5<11> | IEC5<11>         | IPC22<14:12> |

Note 1: Not available in 64-pin devices (PIC24FJXXXDAX06).

#### REGISTER 7-29: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0    | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1  | R/W-0  | R/W-0  |

|--------|--------|--------|--------|-----|--------|--------|--------|

| _      | OC7IP2 | OC7IP1 | OC7IP0 |     | OC6IP2 | OC6IP1 | OC6IP0 |

| bit 15 | _      | _      |        |     | _      | _      | bit 8  |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1  | R/W-0  | R/W-0  |

|-------|--------|--------|--------|-----|--------|--------|--------|

| _     | OC5IP2 | OC5IP1 | OC5IP0 | _   | IC6IP2 | IC6IP1 | IC6IP0 |

| bit 7 |        |        |        |     |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 OC7IP<2:0>: Output Compare Channel 7 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 OC6IP<2:0>: Output Compare Channel 6 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 OC5IP<2:0>: Output Compare Channel 5 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 IC6IP<2:0>: Input Capture Channel 6 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

#### REGISTER 7-39: IPC22: INTERRUPT PRIORITY CONTROL REGISTER 22

| U-0    | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|--------|---------|---------|---------|-----|---------|---------|---------|

| _      | SPI3IP2 | SPI3IP1 | SPI3IP0 | _   | SPF3IP2 | SPF3IP1 | SPF3IP0 |

| bit 15 |         |         |         |     |         |         | bit 8   |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| _     | U4TXIP2 | U4TXIP1 | U4TXIP0 | _   | U4RXIP2 | U4RXIP1 | U4RXIP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 SPI3IP<2:0>: SPI3 Event Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 SPF3IP<2:0>: SPI3 Fault Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 **U4TXIP<2:0>:** UART4 Transmitter Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

.

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 U4RXIP<2:0>: UART4 Receiver Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

#### REGISTER 10-2: ANSB: PORTB ANALOG FUNCTION SELECTION REGISTER

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1 | R/W-1 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| ANSB15 | ANSB14 | ANSB13 | ANSB12 | ANSB11 | ANSB10 | ANSB9 | ANSB8 |

| bit 15 |        |        |        |        |        |       | bit 8 |

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ANSB7 | ANSB6 | ANSB5 | ANSB4 | ANSB3 | ANSB2 | ANSB1 | ANSB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 ANSB<15:0>: Analog Function Selection bits

1 = Pin is configured in Analog mode; I/O port read is disabled

0 = Pin is configured in Digital mode; I/O port read is enabled

#### REGISTER 10-3: ANSC: PORTC ANALOG FUNCTION SELECTION REGISTER

| U-0    | R/W-1  | R/W-1  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|-----|-----|-----|-----|-------|

| _      | ANSC14 | ANSC13 | _   | _   | _   | _   | _     |

| bit 15 |        |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-1                | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|----------------------|-----|-----|-----|-------|

| _     | _   | _   | ANSC4 <sup>(1)</sup> | _   | _   | _   | _     |

| bit 7 |     |     |                      |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-13 ANSC<14:13>: Analog Function Selection bits

1 = Pin is configured in Analog mode; I/O port read is disabled0 = Pin is configured in Digital mode; I/O port read is enabled

bit 12-5 Unimplemented: Read as '0'

bit 4 ANSC4: Analog Function Selection bit<sup>(1)</sup>

1 = Pin is configured in Analog mode; I/O port read is disabled

0 = Pin is configured in Digital mode; I/O port read is enabled

bit 3-0 **Unimplemented:** Read as '0'

Note 1: This bit is not available on 64-pin devices (PIC24FJXXXDAX06).

NOTES:

#### REGISTER 17-1: UxMODE: UARTX MODE REGISTER

| R/W-0                 | U-0 | R/W-0 | R/W-0               | R/W-0 | U-0 | R/W-0 | R/W-0 |

|-----------------------|-----|-------|---------------------|-------|-----|-------|-------|

| UARTEN <sup>(1)</sup> | _   | USIDL | IREN <sup>(2)</sup> | RTSMD | _   | UEN1  | UEN0  |

| bit 15                |     |       |                     |       |     |       | bit 8 |

| R/W-0, HC | R/W-0  | R/W-0, HC | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 |

|-----------|--------|-----------|-------|-------|--------|--------|-------|

| WAKE      | LPBACK | ABAUD     | RXINV | BRGH  | PDSEL1 | PDSEL0 | STSEL |

| bit 7     |        |           |       |       |        |        | bit 0 |

Legend:HC = Hardware Clearable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 **UARTEN:** UARTx Enable bit<sup>(1)</sup>

1 = UARTx is enabled; all UARTx pins are controlled by UARTx as defined by UEN<1:0>

0 = UARTx is disabled; all UARTx pins are controlled by port latches; UARTx power consumption is minimal

bit 14 **Unimplemented:** Read as '0'

bit 13 USIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12 IREN: IrDA® Encoder and Decoder Enable bit(2)

1 = IrDA encoder and decoder are enabled

0 = IrDA encoder and decoder are disabled

bit 11 RTSMD: Mode Selection for UxRTS Pin bit

$1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

$0 = \overline{UxRTS}$  pin is in Flow Control mode

bit 10 Unimplemented: Read as '0'

bit 9-8 **UEN<1:0>:** UARTx Enable bits

11 = UxTX, UxRX and BCLKx pins are enabled and used; UxCTS pin is controlled by port latches

10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

01 = UxTX, UxRX and  $\overline{\text{UxRTS}}$  pins are enabled and used;  $\overline{\text{UxCTS}}$  pin is controlled by port latches

00 = UxTX and UxRX pins are enabled and used;  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}/\text{BCLKx}$  pins are controlled by port

bit 7 WAKE: Wake-up on Start Bit Detect During Sleep Mode Enable bit

1 = UARTx will continue to sample the UxRX pin; interrupt is generated on the falling edge, bit is cleared in hardware on the following rising edge

0 = No wake-up is enabled

bit 6 LPBACK: UARTx Loopback Mode Select bit

1 = Enable Loopback mode

0 = Loopback mode is disabled

bit 5 ABAUD: Auto-Baud Enable bit

1 = Enable baud rate measurement on the next character – requires reception of a Sync field (55h); cleared in hardware upon completion

0 = Baud rate measurement is disabled or completed

Note 1: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

2: This feature is only available for the 16x BRG mode (BRGH = 0).

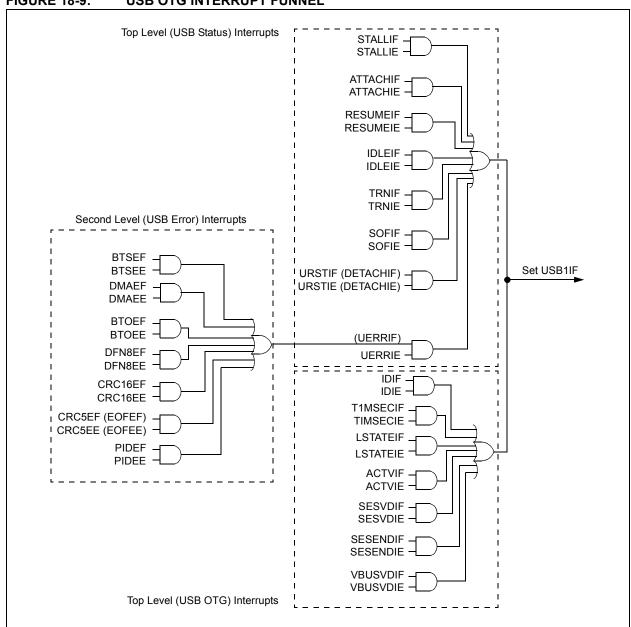

#### 18.3 USB Interrupts

The USB OTG module has many conditions that can be configured to cause an interrupt. All interrupt sources use the same interrupt vector.

Figure 18-9 shows the interrupt logic for the USB module. There are two layers of interrupt registers in the USB module. The top level consists of overall USB status interrupts; these are enabled and flagged in the U1IE and U1IR registers, respectively. The second

level consists of USB error conditions, which are enabled and flagged in the U1EIR and U1EIE registers. An interrupt condition in any of these triggers a USB Error Interrupt Flag (UERRIF) in the top level.

Interrupts may be used to trap routine events in a USB transaction. Figure 18-10 provides some common events within a USB frame and their corresponding interrupts.

FIGURE 18-9: USB OTG INTERRUPT FUNNEL

#### REGISTER 18-5: U1PWRC: USB POWER CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   |     | _   |     |     | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0, HS | U-0 | U-0 | R/W-0   | U-0 | U-0 | R/W-0, HC | R/W-0  |

|-----------|-----|-----|---------|-----|-----|-----------|--------|

| UACTPND   | _   | _   | USLPGRD | _   | _   | USUSPND   | USBPWR |

| bit 7     |     |     |         |     |     |           | bit 0  |

| Legend: HS = Hardware Settable bit |                  | HC = Hardware Clearable bit        |                    |  |  |

|------------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit                   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                  | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-8 **Unimplemented:** Read as '0'

bit 7 **UACTPND:** USB Activity Pending bit

1 = Module should not be suspended at the moment (requires the USLPGRD bit to be set)

0 = Module may be suspended or powered down

bit 6-5 **Unimplemented:** Read as '0'

bit 4 USLPGRD: Sleep/Suspend Guard bit

1 = Indicate to the USB module that it is about to be suspended or powered down

0 = No suspend

bit 3-2 **Unimplemented:** Read as '0'

bit 1 USUSPND: USB Suspend Mode Enable bit

1 = USB OTG module is in Suspend mode; USB clock is gated and the transceiver is placed in a

low-power state

0 = Normal USB OTG operation

bit 0 USBPWR: USB Operation Enable bit

1 = USB OTG module is enabled 0 = USB OTG module is disabled<sup>(1)</sup>

Note 1: Do not clear this bit unless the HOSTEN, USBEN and OTGEN bits (U1CON<3,0> and U1OTGCON<2>) are all cleared.

#### 21.1.3 DATA SHIFT DIRECTION

The LENDIAN bit (CRCCON1<3>) is used to control the shift direction. By default, the CRC will shift data through the engine, MSb first. Setting LENDIAN (= 1) causes the CRC to shift data, LSb first. This setting allows better integration with various communication schemes and removes the overhead of reversing the bit order in software. Note that this only changes the direction the data is shifted into the engine. The result of the CRC calculation will still be a normal CRC result, not a reverse CRC result.

#### 21.1.4 INTERRUPT OPERATION

The module generates an interrupt that is configurable by the user for either of two conditions.

If CRCISEL is '0', an interrupt is generated when the VWORD<4:0> bits make a transition from a value of '1' to '0'. If CRCISEL is '1', an interrupt will be generated after the CRC operation finishes and the module sets the CRCGO bit to '0'. Manually setting CRCGO to '0' will not generate an interrupt. Note that when an interrupt occurs, the CRC calculation would not yet be complete. The module will still need (PLEN + 1)/2 clock cycles after the interrupt is generated until the CRC calculation is finished.

#### 21.1.5 TYPICAL OPERATION

To use the module for a typical CRC calculation:

- 1. Set the CRCEN bit to enable the module.

- 2. Configure the module for desired operation:

- a) Program the desired polynomial using the CRCXORL and CRCXORH registers, and the PLEN<4:0> bits.

- b) Configure the data width and shift direction using the DWIDTH and LENDIAN bits.

- c) Select the desired interrupt mode using the CRCISEL bit.

- 3. Preload the FIFO by writing to the CRCDATL and CRCDATH registers until the CRCFUL bit is set or no data is left.

- 4. Clear old results by writing 00h to CRCWDATL and CRCWDATH. The CRCWDAT registers can also be left unchanged to resume a previously halted calculation.

- 5. Set the CRCGO bit to start calculation.

- 6. Write remaining data into the FIFO as space becomes available.

- 7. When the calculation completes, CRCGO is automatically cleared. An interrupt will be generated if CRCISEL = 1.

- 8. Read CRCWDATL and CRCWDATH for the result of the calculation.

There are eight registers used to control programmable CRC operation:

- CRCCON1

- CRCCON2

- CRCXORL

- CRCXORH

- CRCDATL

- CRCDATH

- CRCWDATL

- CRCWDATH

The CRCCON1 and CRCCON2 registers (Register 21-1 and Register 21-2) control the operation of the module and configure the various settings.

registers CRCXOR (Register 21-3 Register 21-4) select the polynomial terms to be used in the CRC equation. The CRCDAT and CRCWDAT registers are each register pairs that serve as buffers for the double-word input data, and CRC processed output, respectively.

#### REGISTER 22-9: G1W1ADRL: GPU WORK AREA 1 START ADDRESS REGISTER LOW

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| W1ADR15 | W1ADR14 | W1ADR13 | W1ADR12 | W1ADR11 | W1ADR10 | W1ADR9 | W1ADR8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| W1ADR7 | W1ADR6 | W1ADR5 | W1ADR4 | W1ADR3 | W1ADR2 | W1ADR1 | W1ADR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 W1ADR<15:0>: GPU Work Area 1 Start Address Low bits

Work area address must point to an even byte address in memory.

#### REGISTER 22-10: G1W1ADRH: GPU WORK AREA 1 START ADDRESS REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   |       |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| W1ADR23 | W1ADR22 | W1ADR21 | W1ADR20 | W1ADR19 | W1ADR18 | W1ADR17 | W1ADR16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 W1ADR<23:16>: GPU Work Area 1 Start Address High bits

Work area address must point to an even byte address in memory.

#### REGISTER 22-11: G1W2ADRL: GPU WORK AREA 2 START ADDRESS REGISTER LOW

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| W2ADR15 | W2ADR14 | W2ADR13 | W2ADR12 | W2ADR11 | W2ADR10 | W2ADR9 | W2ADR8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|   | R/W-0  |

|---|--------|--------|--------|--------|--------|--------|--------|--------|

|   | W2ADR7 | W2ADR6 | W2ADR5 | W2ADR4 | W2ADR3 | W2ADR2 | W2ADR1 | W2ADR0 |

| t | oit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 W2ADR<15:0>: GPU Work Area 2 Start Address Low bits

Work area address must point to an even byte address in memory.

#### **REGISTER 27-6: DEVREV: DEVICE REVISION REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   | _   | _   | _   | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|--------|-----|-----|-----|-----|-----|-----|-----|

| _      | _   | _   | _   | _   | _   | _   | _   |

| bit 15 |     |     |     |     |     |     |     |

| U-0   | U-0 | U-0 | U-0 | R    | R    | R    | R     |

|-------|-----|-----|-----|------|------|------|-------|

| _     | _   | _   | _   | REV3 | REV2 | REV1 | REV0  |

| bit 7 |     |     |     |      |      |      | bit 0 |

Legend: R = Readable bit U = Unimplemented bit

bit 23-4 Unimplemented: Read as '0'

bit 3-0 **REV<3:0>:** Device revision identifier bits

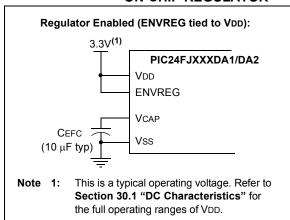

#### 27.2 On-Chip Voltage Regulator

All PIC24FJ256DA210 family devices power their core digital logic at a nominal 1.8V. This may create an issue for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the PIC24FJ256DA210 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator is controlled by the ENVREG pin. Tying VDD to the pin enables the regulator, which in turn, provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR capacitor (such as ceramic) must be connected to the VCAP pin (Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor (CEFC) is provided in **Section 30.1 "DC Characteristics"**.

## 27.2.1 VOLTAGE REGULATOR LOW-VOLTAGE DETECTION

When the on-chip regulator is enabled, it provides a constant voltage of 1.8V nominal to the digital core logic.

The regulator can provide this level from a VDD of about 2.1V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels. In order to prevent "brown-out" conditions when the voltage drops too low for the regulator, the Brown-out Reset occurs. Then the regulator output follows VDD with a typical voltage drop of 300 mV.

To provide information about when the regulator voltage starts reducing, the on-chip regulator includes a simple Low-Voltage Detect circuit, which sets the

Low-Voltage Detect Interrupt Flag, LVDIF (IFS4<8>). This can be used to generate an interrupt to trigger an orderly shutdown.

## FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

#### 27.2.2 ON-CHIP REGULATOR AND POR

When the voltage regulator is enabled, it takes approximately 10  $\mu s$  for it to generate output. During this time, designated as TVREG, code execution is disabled. TVREG is applied every time the device resumes operation after any power-down, including Sleep mode. TVREG is determined by the status of the VREGS bit (RCON<8>) and the WUTSEL Configuration bits (CW3<11:10>). Refer to Section 30.0 "Electrical Characteristics" for more information on TVREG.

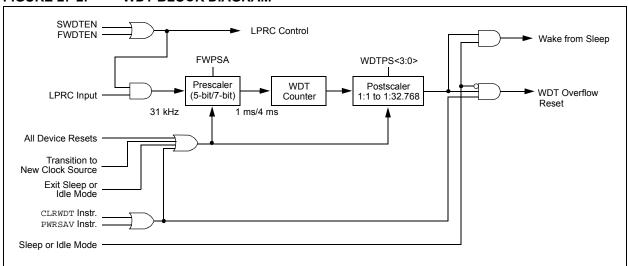

#### 27.3.1 WINDOWED OPERATION

The Watchdog Timer has an optional Fixed-Window mode of operation. In this Windowed mode, CLRWDT instructions can only reset the WDT during the last 1/4 of the programmed WDT period. A CLRWDT instruction executed before that window causes a WDT Reset, similar to a WDT time-out.

Windowed WDT mode is enabled by programming the WINDIS Configuration bit (CW1<6>) to '0'.

#### 27.3.2 CONTROL REGISTER

The WDT is enabled or disabled by the FWDTEN Configuration bit. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN Control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

FIGURE 27-2: WDT BLOCK DIAGRAM

# 27.4 Program Verification and Code Protection

PIC24FJ256DA210 family devices provide two complimentary methods to protect application code from overwrites and erasures. These also help to protect the device from inadvertent configuration changes during run time.

#### 27.4.1 GENERAL SEGMENT PROTECTION

For all devices in the PIC24FJ256DA210 family, the on-chip program memory space is treated as a single block, known as the General Segment (GS). Code protection for this block is controlled by one Configuration bit, GCP. This bit inhibits external reads and writes to the program memory space. It has no direct effect in normal execution mode.

Write protection is controlled by the GWRP bit in the Configuration Word. When GWRP is programmed to '0', internal write and erase operations to program memory are blocked.

#### 27.4.2 CODE SEGMENT PROTECTION

In addition to global General Segment protection, a separate subrange of the program memory space can be individually protected against writes and erases. This area can be used for many purposes where a separate block of write and erase-protected code is needed, such as bootloader applications. Unlike common boot block implementations, the specially protected segment in the PIC24FJ256DA210 family devices can be located by the user anywhere in the program space and configured in a wide range of sizes.

Code segment protection provides an added level of protection to a designated area of program memory by disabling the NVM safety interlock whenever a write or erase address falls within a specified range. It does not override General Segment protection controlled by the GCP or GWRP bits. For example, if GCP and GWRP are enabled, enabling segmented code protection for the bottom half of program memory does not undo General Segment protection for the top half.

The size and type of protection for the segmented code range are configured by the WPFPx, WPEND, WPCFG and WPDIS bits in Configuration Word 3. Code segment protection is enabled by programming the WPDIS bit (= 0). The WPFP bits specify the size of the segment to be protected, by specifying the 512-word code page that is the start or end of the protected segment. The specified region is inclusive, therefore, this page will also be protected.

The WPEND bit determines if the protected segment uses the top or bottom of the program space as a boundary. Programming WPEND (= 0) sets the bottom of program memory (000000h) as the lower boundary of the protected segment. Leaving WPEND unprogrammed (= 1) protects the specified page through the last page of implemented program memory, including the Configuration Word locations.

A separate bit, WPCFG, is used to protect the last page of program space, including the Flash Configuration Words. Programming WPCFG (= 0) protects the last page in addition to the pages selected by the WPEND and WPFP<7:0> bits setting. This is useful in circumstances where write protection is needed for both the code segment in the bottom of the memory and the Flash Configuration Words.

The various options for segment code protection are shown in Table 27-2.

NOTES:

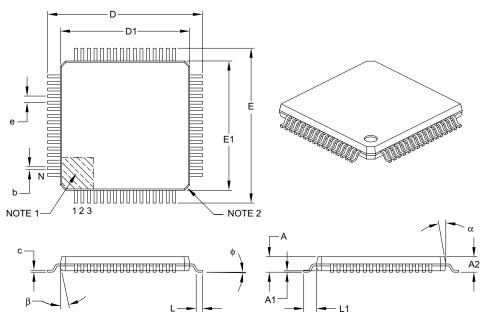

#### 31.2 Package Details

The following sections give the technical details of the packages.

### 64-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |           |      |  |

|--------------------------|------------------|-------------|-----------|------|--|

|                          | Dimension Limits | MIN         | NOM       | MAX  |  |

| Number of Leads          | N                |             | 64        |      |  |

| Lead Pitch               | е                |             | 0.50 BSC  |      |  |

| Overall Height           | A                | -           | _         | 1.20 |  |

| Molded Package Thickness | A2               | 0.95        | 1.00      | 1.05 |  |

| Standoff                 | A1               | 0.05        | _         | 0.15 |  |

| Foot Length              | L                | 0.45        | 0.60      | 0.75 |  |

| Footprint                | L1               | 1.00 REF    |           |      |  |

| Foot Angle               | ф                | 0°          | 3.5°      | 7°   |  |

| Overall Width            | E                |             | 12.00 BSC |      |  |

| Overall Length           | D                |             | 12.00 BSC |      |  |

| Molded Package Width     | E1               |             | 10.00 BSC |      |  |

| Molded Package Length    | D1               |             | 10.00 BSC |      |  |

| Lead Thickness           | С                | 0.09        | _         | 0.20 |  |

| Lead Width               | b                | 0.17        | 0.22      | 0.27 |  |

| Mold Draft Angle Top     | α                | 11°         | 12°       | 13°  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°       | 13°  |  |

#### Notes

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

### **INDEX**

| A                                                    |     | Shared I/O Port Structure                                      | 157 |

|------------------------------------------------------|-----|----------------------------------------------------------------|-----|

| A/D Conversion                                       |     | SPI Master, Frame Master Connection                            | 220 |

| 10-Bit High-Speed A/D Converter                      | 325 | SPI Master, Frame Slave Connection                             | 220 |

| A/D Converter                                        |     | SPI Master/Slave Connection                                    |     |

| Analog Input Model                                   |     | (Enhanced Buffer Modes)                                        | 219 |

| Transfer Function                                    |     | SPI Master/Slave Connection                                    |     |

| AC Characteristics                                   | 333 | (Standard Mode)                                                | 219 |

| ADC Conversion Timing                                | 395 | SPI Slave, Frame Master Connection                             | 220 |

| CLKO and I/O Timing                                  |     | SPI Slave, Frame Slave Connection                              | 220 |

| Internal RC Accuracy                                 |     | SPIx Module (Enhanced Mode)                                    | 213 |

| Alternate Interrupt Vector Table (AIVT)              |     | SPIx Module (Standard Mode)                                    | 212 |

| Alternative Master                                   |     | System Clock                                                   | 141 |

| EPMP                                                 | 273 | Triple Comparator Module                                       | 335 |

| Assembler                                            | 270 | UART (Simplified)                                              | 231 |

| MPASM Assembler                                      | 360 | USB OTG                                                        |     |

| WII / COW / COCHIOCI                                 | 000 | Device Mode Power Modes                                        | 241 |

| В                                                    |     | USB OTG Interrupt Funnel                                       | 248 |

| Block Diagram                                        |     | USB OTG Module                                                 | 240 |

| CRC                                                  | 297 | Watchdog Timer (WDT)                                           | 356 |

| Block Diagrams                                       |     | С                                                              |     |

| 10-Bit High-Speed A/D Converter                      | 326 | _                                                              |     |

| 16-Bit Asynchronous Timer3 and Timer5                |     | C Compilers                                                    |     |

| 16-Bit Synchronous Timer2 and Timer4                 |     | MPLAB C18                                                      |     |

| 16-Bit Timer1 Module                                 |     | Charge Time Measurement Unit (CTMU)                            |     |

| 32-Bit Timer2/3 and Timer4/5                         | 192 | Key Features                                                   | 343 |

| 96 MHz PLL                                           | 150 | Charge Time Measurement Unit. See CTMU.                        |     |

| Accessing Program Space Using Table                  |     | Code Examples                                                  |     |

| Operations                                           | 77  | Basic Sequence for Clock Switching in                          |     |

| Addressing for Table Registers                       |     | Assembly                                                       | 149 |

| BDT Mapping for Endpoint Buffering Modes             | 244 | Configuring UART1 I/O Input/Output                             | 400 |

| CALL Stack Frame                                     |     | Functions (PPS)                                                |     |

| Comparator Voltage Reference                         | 341 | EDS Read From Program Memory in Assembly                       |     |

| CPU Programmer's Model                               | 41  | EDS Read in Assembly                                           |     |

| CRC Shift Engine Detail                              | 297 | EDS Write in Assembly                                          |     |

| CTMU Connections and Internal Configuration          |     | Erasing a Program Memory Block (Assembly)                      |     |

| for Capacitance Measurement                          | 343 | I/O Port Read/Write in 'C'                                     |     |

| CTMU Typical Connections and Internal                |     | I/O Port Read/Write in Assembly                                |     |

| Configuration for Pulse Delay Generation             | 344 | Initiating a Programming Sequence<br>PWRSAV Instruction Syntax |     |

| CTMU Typical Connections and Internal                |     | Setting the RTCWREN Bit                                        |     |

| Configuration for Time Measurement                   | 344 | Single-Word Flash Programming                                  |     |

| Data Access From Program Space                       |     | Single-Word Flash Programming                                  | 00  |

| Address Generation                                   |     | ('C' Language)                                                 | 86  |

| Graphics Module Overview                             |     | Code Protection                                                |     |

| I <sup>2</sup> C Module                              | 224 | Code Segment Protection                                        |     |

| Individual Comparator Configurations,                | 000 | Configuration Options                                          |     |

| CREF = 0                                             | 336 | Configuration Protection                                       |     |

| Individual Comparator Configurations,                | 207 | Comparator Voltage Reference                                   |     |

| CREF = 1 and CVREFP = 0                              | 337 | Configuring                                                    |     |

| Individual Comparator ConfigurationS,                | 227 | Configuration Bits                                             |     |

| CREF = 1 and CVREFP = 1                              |     | Core Features                                                  |     |

| Input Capture                                        |     | CPU                                                            |     |

| On-Chip Regulator Connections                        |     | Arithmetic Logic Unit (ALU)                                    | 43  |

| Output Compare (Double Buffered                      | 202 | Control Registers                                              |     |

| Output Compare (Double-Buffered,                     | 204 | Core Registers                                                 |     |

| 16-Bit PWM Mode)<br>PCI24FJ256DA210 Family (General) |     | Programmer's Model                                             |     |

| PIC24F CPU Core                                      |     | CRC                                                            |     |

| PSV Operation (Higher Word)                          |     | 32-Bit Programmable Cyclic                                     |     |

| PSV Operation (Lower Word)                           |     | Redundancy Check                                               | 297 |

| Reset System                                         |     | Polynomials                                                    |     |

| RTCC                                                 |     | Setup Examples for 16 and 32-Bit Polynomials                   | 298 |

| 11100                                                | 200 | User Interface                                                 |     |

| ANSF (PORTF Analog Function Selection) | 162    | G1STAT (Graphics Control Status)           | 310 |

|----------------------------------------|--------|--------------------------------------------|-----|

| ANSG (PORTG Analog Function Selection) | 162    | G1VSYNC (Vertical Synchronization Control) | 318 |

| BDnSTAT Prototype (Buffer Descriptor n |        | G1W1ADRH (GPU Work Area 1                  |     |

| Status, CPU Mode)                      | 247    | Start Address High)                        | 313 |

| BDnSTAT Prototype (Buffer Descriptor n |        | G1W1ADRL (GPU Work Area 1                  |     |

| Status, USB Mode)                      | 246    | Start Address Low)                         | 313 |

| CLKDIV (Clock Divider)                 | 145    | G1W2ADRH (GPU Work Area 2                  |     |

| CLKDIV2 (Clock Divider 2)              |        | Start Address High                         | 314 |

| CMSTAT (Comparator Status)             | 339    | G1W2ADRL (GPU Work Area 2                  |     |

| CMxCON (Comparator x Control)          | 338    | Start Address Low)                         | 313 |

| CORCON (CPU Core Control)              | 43, 98 | I2CxCON (I2Cx Control)                     | 226 |

| CRCCON1 (CRC Control 1)                |        | I2CxMSK (I2Cx Slave Mode Address Mask)     | 230 |

| CRCCON2 (CRC Control 2)                |        | I2CxSTAT (I2Cx Status)                     | 228 |

| CRCDATH (CRC Data High)                |        | ICxCON1 (Input Capture x Control 1)        |     |

| CRCDATL (CRC Data Low)                 |        | ICxCON2 (Input Capture x Control 2)        |     |

| CRCWDATH (CRC Shift High)              |        | IEC0 (Interrupt Enable Control 0)          |     |

| CRCWDATL (CRC Shift Low)               |        | IEC1 (Interrupt Enable Control 1)          |     |

| CRCXORH (CRC XOR High)                 |        | IEC2 (Interrupt Enable Control 2)          |     |

| CRCXORL (CRC XOR Polynomial,           |        | IEC3 (Interrupt Enable Control 3)          |     |

| Low Byte)                              | 301    | IEC4 (Interrupt Enable Control 4)          |     |

| CTMUCON (CTMU Control)                 |        | IEC5 (Interrupt Enable Control 5)          |     |

| · · · · · · · · · · · · · · · · · · ·  |        |                                            |     |

| CTMUICON (CTMU Current Control)        | 340    | IEC6 (Interrupt Enable Control 6)          |     |

| CVRCON (Comparator Voltage             | 240    | IFS0 (Interrupt Flag Status 0)             |     |

| Reference Control)                     |        | IFS1 (Interrupt Flag Status 1)             |     |

| CW1 (Flash Configuration Word 1)       |        | IFS2 (Interrupt Flag Status 2)             |     |

| CW2 (Flash Configuration Word 2)       |        | IFS3 (Interrupt Flag Status 3)             |     |

| CW3 (Flash Configuration Word 3)       |        | IFS4 (Interrupt Flag Status 4)             |     |

| CW4 (Flash Configuration Word 4)       |        | IFS5 (Interrupt Flag Status 5)             |     |

| DEVID (Device ID)                      |        | IFS6 (Interrupt Flag Status 6)             |     |

| DEVREV (Device Revision)               |        | INTCON1 (Interrupt Control 1)              |     |

| G1ACTDA (Active Display Area)          | 317    | INTCON2 (Interrupt Control 2)              |     |

| G1CHRX (Character X-Coordinate         |        | INTTREG (Interrupt Controller Test         |     |

| Print Position)                        | 321    | IPC0 (Interrupt Priority Control 0)        |     |

| G1CHRY (Character Y-Coordinate         |        | IPC1 (Interrupt Priority Control 1)        |     |

| Print Position)                        |        | IPC10 (Interrupt Priority Control 10)      |     |

| G1CLUT (Color Look-up Table Control)   | 319    | IPC11 (Interrupt Priority Control 11)      |     |

| G1CLUTRD (Color Look-up Table Memory   |        | IPC12 (Interrupt Priority Control 12)      | 129 |

| Read Data)                             | 320    | IPC13 (Interrupt Priority Control 13)      | 130 |

| G1CLUTWR (Color Look-up Table Memory   |        | IPC15 (Interrupt Priority Control 15)      | 131 |

| Write Data)                            | 320    | IPC16 (Interrupt Priority Control 16)      | 132 |

| G1CMDH (GPU Command High)              | 306    | IPC18 (Interrupt Priority Control 18)      | 133 |

| G1CMDL (GPU Command Low)               | 306    | IPC19 (Interrupt Priority Control 19)      | 133 |

| G1CON1 (Display Control 1)             | 307    | IPC2 (Interrupt Priority Control 2)        | 119 |

| G1CON2 (Display Control 2)             | 308    | IPC20 (Interrupt Priority Control 20)      | 134 |

| G1CON3 (Display Control 3)             | 309    | IPC21 (Interrupt Priority Control 21)      | 135 |

| G1DBEN (Data I/O Pad Enable)           |        | IPC22 (Interrupt Priority Control 22)      | 136 |

| G1DBLCON (Display Blanking Control)    | 318    | IPC23 (Interrupt Priority Control 23)      |     |

| G1DPADRH (Display Buffer Start         |        | IPC25 (Interrupt Priority Control 25)      | 138 |

| Address High)                          | 315    | IPC3 (Interrupt Priority Control 3)        |     |

| G1DPADRL (Display Buffer Start         |        | IPC4 (Interrupt Priority Control 4)        |     |

| Address Low)                           | 315    | IPC5 (Interrupt Priority Control 5)        |     |

| G1DPDPH (Display Buffer Height)        |        | IPC6 (Interrupt Priority Control 6)        |     |

| G1DPHT (Display Total Height)          |        | IPC7 (Interrupt Priority Control 7)        |     |

| G1DPW (Display Buffer Width)           |        | IPC8 (Interrupt Priority Control 8)        |     |

| G1DPWT (Display Total Width)           |        | IPC9 (Interrupt Priority Control 9)        |     |

| G1HSYNC (Horizontal                    |        | IPCn (Interrupt Priority Control 0-23)     |     |

| Synchronization Control)               | 317    | MINSEC (RTCC Minutes and Seconds Value)    |     |

| G1IE (GFX Interrupt Enable)            |        | MTHDY (RTCC Month and Day Value)           |     |

| G1IPU (Inflate Processor Status)       |        | NVMCON (Flash Memory Control)              |     |

| ,                                      |        | · · · · · · · · · · · · · · · · · · ·      |     |

| G1IR (GFX Interrupt Status)            |        | OCXCON1 (Output Compare x Control 1)       |     |

| G1MRGN (Interrupt Advance)             |        | OCXCON2 (Output Compare x Control 2)       |     |

| G1PUH (GPU Work Area Height)           |        | OSCCON (Oscillator Control)                | 143 |

| CILCUM CICU VVOIK ACEA VVICIIII        | 314    |                                            |     |