Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 192KB (192K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 12K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p34l1cefby |

# **Contents**

| 1 | Intro | duction |                                                 | 7  |

|---|-------|---------|-------------------------------------------------|----|

|   | 1.1   | Docum   | ent overview                                    | 7  |

|   | 1.2   | Descrip | tion                                            | 7  |

|   | 1.3   | Device  | comparison                                      | 7  |

|   | 1.4   | Block d | iagram                                          | 9  |

|   | 1.5   |         | e details                                       |    |

|   |       | 1.5.1   | High performance e200z0 core processor          |    |

|   |       | 1.5.2   | Crossbar switch (XBAR)                          |    |

|   |       | 1.5.3   | Enhanced direct memory access (eDMA)            |    |

|   |       | 1.5.4   | Flash memory                                    |    |

|   |       | 1.5.5   | Static random access memory (SRAM)              |    |

|   |       | 1.5.6   | Interrupt controller (INTC)                     |    |

|   |       | 1.5.7   | System status and configuration module (SSCM)   | 16 |

|   |       | 1.5.8   | System clocks and clock generation              |    |

|   |       | 1.5.9   | Frequency-modulated phase-locked loop (FMPLL)   | 17 |

|   |       | 1.5.10  | Main oscillator                                 | 17 |

|   |       | 1.5.11  | Internal RC oscillator                          | 17 |

|   |       | 1.5.12  | Periodic interrupt timer (PIT)                  | 18 |

|   |       | 1.5.13  | System timer module (STM)                       | 18 |

|   |       | 1.5.14  | Software watchdog timer (SWT)                   | 18 |

|   |       | 1.5.15  | Fault collection unit (FCU)                     | 18 |

|   |       | 1.5.16  | System integration unit – Lite (SIUL)           | 19 |

|   |       | 1.5.17  | Boot and censorship                             | 19 |

|   |       | 1.5.18  | Error correction status module (ECSM)           | 19 |

|   |       | 1.5.19  | Peripheral bridge (PBRIDGE)                     | 20 |

|   |       | 1.5.20  | Controller area network (FlexCAN)               | 20 |

|   |       | 1.5.21  | Safety port (FlexCAN)                           | 21 |

|   |       | 1.5.22  | Serial communication interface module (LINFlex) | 22 |

|   |       | 1.5.23  | Deserial serial peripheral interface (DSPI)     | 23 |

|   |       | 1.5.24  | Pulse width modulator (FlexPWM)                 | 23 |

|   |       | 1.5.25  | eTimer                                          |    |

|   |       | 1.5.26  | Analog-to-digital converter (ADC) module        | 25 |

|   |       | 1.5.27  | Cross triggering unit (CTU)                     |    |

|   |       | 1.5.28  | Nexus Development Interface (NDI)               | 26 |

Table 4. SPC560P34/SPC560P40 series block summary

| Block                                             | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                 | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                          | Block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                          |

| Clock generation module (MC_CGM)                  | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Controller area network (FlexCAN)                 | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Cross triggering unit (CTU)                       | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Crossbar switch (XBAR)                            | Supports simultaneous connections between two master ports and three slave ports; supports a 32-bit address bus width and a 32-bit data bus width                                                                                                                                                                 |

| Cyclic redundancy check (CRC)                     | CRC checksum generator                                                                                                                                                                                                                                                                                            |

| Deserial serial peripheral interface (DSPI)       | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Enhanced direct memory access (eDMA)              | Performs complex data transfers with minimal intervention from a host processor via "n" programmable channels                                                                                                                                                                                                     |

| Enhanced timer (eTimer)                           | Provides enhanced programmable up/down modulo counting                                                                                                                                                                                                                                                            |

| Error correction status module (ECSM)             | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| External oscillator (XOSC)                        | Provides an output clock used as input reference for FMPLL_0 or as reference clock for specific modules depending on system needs                                                                                                                                                                                 |

| Fault collection unit (FCU)                       | Provides functional safety to the device                                                                                                                                                                                                                                                                          |

| Flash memory                                      | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| Frequency-modulated phase-<br>locked loop (FMPLL) | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Interrupt controller (INTC)                       | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                   | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Mode entry module (MC_ME)                         | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Periodic interrupt timer (PIT)                    | Produces periodic interrupts and triggers                                                                                                                                                                                                                                                                         |

| Peripheral bridge (PBRIDGE)                       | Is the interface between the system bus and on-chip peripherals                                                                                                                                                                                                                                                   |

| Power control unit (MC_PCU)                       | Reduces the overall power consumption by disconnecting parts of the device from the power supply via a power switching device; device components are grouped into sections called "power domains" which are controlled by the PCU                                                                                 |

The flash memory module provides the following features:

- As much as 320 KB flash memory

- 6 blocks (32 KB + 2x16 KB + 32 KB + 32 KB + 128 KB) code flash memory

- 4 blocks (16 KB + 16 KB + 16 KB + 16 KB) data flash memory

- Full Read-While-Write (RWW) capability between code flash memory and data flash memory

- Four 128-bit wide prefetch buffers to provide single cycle in-line accesses (prefetch buffers can be configured to prefetch code or data or both)

- Typical flash memory access time: no wait-state for buffer hits, 2 wait-states for page buffer miss at 64 MHz

- Hardware managed flash memory writes handled by 32-bit RISC Krypton engine

- Hardware and software configurable read and write access protections on a per-master basis

- Configurable access timing allowing use in a wide range of system frequencies

- Multiple-mapping support and mapping-based block access timing (up to 31 additional cycles) allowing use for emulation of other memory types

- Software programmable block program/erase restriction control

- Erase of selected block(s)

- Read page sizes

- Code flash memory: 128 bits (4 words)

- Data flash memory: 32 bits (1 word)

- ECC with single-bit correction, double-bit detection for data integrity

- Code flash memory: 64-bit ECC

- Data flash memory: 32-bit ECC

- Embedded hardware program and erase algorithm

- Erase suspend and program abort

- Censorship protection scheme to prevent flash memory content visibility

- Hardware support for EEPROM emulation

#### 1.5.5 Static random access memory (SRAM)

The SPC560P34/SPC560P40 SRAM module provides up to 20 KB of general-purpose memory.

The SRAM module provides the following features:

- Supports read/write accesses mapped to the SRAM from any master

- Up to 20 KB general purpose SRAM

- Supports byte (8-bit), half word (16-bit), and word (32-bit) writes for optimal use of memory

- Typical SRAM access time: no wait-state for reads and 32-bit writes; 1 wait-state for 8and 16-bit writes if back-to-back with a read to same memory block

The RC oscillator provides these features:

- Nominal frequency 16 MHz

- ±5% variation over voltage and temperature after process trim

- Clock output of the RC oscillator serves as system clock source in case loss of lock or loss of clock is detected by the PLL

- RC oscillator is used as the default system clock during startup

#### 1.5.12 Periodic interrupt timer (PIT)

The PIT module implements these features:

- 4 general-purpose interrupt timers

- 32-bit counter resolution

- Clocked by system clock frequency

- Each channel usable as trigger for a DMA request

#### 1.5.13 System timer module (STM)

The STM implements these features:

- One 32-bit up counter with 8-bit prescaler

- Four 32-bit compare channels

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

#### 1.5.14 Software watchdog timer (SWT)

The SWT has the following features:

- 32-bit time-out register to set the time-out period

- Programmable selection of window mode or regular servicing

- Programmable selection of reset or interrupt on an initial time-out

- Master access protection

- Hard and soft configuration lock bits

- Reset configuration inputs allow timer to be enabled out of reset

#### 1.5.15 Fault collection unit (FCU)

The FCU provides an independent fault reporting mechanism even if the CPU is malfunctioning.

The FCU module has the following features:

- FCU status register reporting the device status

- Continuous monitoring of critical fault signals

- User selection of critical signals from different fault sources inside the device

- Critical fault events trigger 2 external pins (user selected signal protocol) that can be used externally to reset the device and/or other circuitry (for example, a safety relay)

- Faults are latched into a register

platform memory errors reported by error-correcting codes and/or generic access error information for certain processor cores.

The Error Correction Status Module supports a number of miscellaneous control functions for the platform. The ECSM includes these features:

- Registers for capturing information on platform memory errors if error-correcting codes (ECC) are implemented

- For test purposes, optional registers to specify the generation of double-bit memory errors are enabled on the SPC560P34/SPC560P40.

The sources of the ECC errors are:

- Flash memory

- SRAM

#### 1.5.19 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- Duplicated periphery

- Master access privilege level per peripheral (per master: read access enable; write access enable)

- Write buffering for peripherals

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

### 1.5.20 Controller area network (FlexCAN)

The SPC560P34/SPC560P40 MCU contains one controller area network (FlexCAN) module. This module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module contains 32 message buffers.

20/103 Doc ID 16100 Rev 7

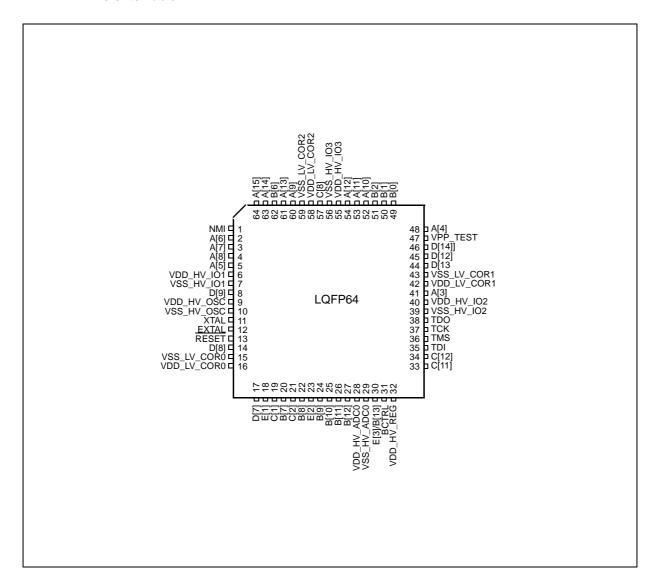

# 2 Package pinouts and signal descriptions

## 2.1 Package pinouts

The LQFP pinouts are shown in the following figures. For pin signal descriptions, please refer to *Table 7*.

Figure 2. 64-pin LQFP pinout – Full featured configuration (top view)

Table 7. Pin muxing (continued)

| Port  | PCR      | Alternate                         | Functions                                    | Peripheral <sup>(3)</sup>                        | 1/0                           | Pad sp  | peed <sup>(5)</sup> | Pin    |         |

|-------|----------|-----------------------------------|----------------------------------------------|--------------------------------------------------|-------------------------------|---------|---------------------|--------|---------|

| pin   | register | function <sup>(1),(2)</sup>       | Functions                                    | Peripheral                                       | direc-<br>tion <sup>(4)</sup> | SRC = 0 | SRC = 1             | 64-pin | 100-pin |

| A[11] | PCR[11]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[11]<br>SCK<br>A[0]<br>A[2]<br>EIRQ[10]  | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL | I/O<br>I/O<br>O O –           | Slow    | Medium              | 53     | 82      |

| A[12] | PCR[12]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[12]<br>SOUT<br>A[2]<br>B[2]<br>EIRQ[11] | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL | I/O<br>O<br>O<br>O            | Slow    | Medium              | 54     | 83      |

| A[13] | PCR[13]  | ALT0 ALT1 ALT2 ALT3 — — —         | GPIO[13]  — B[2] — SIN FAULT[0] EIRQ[12]     | SIUL  FlexPWM_0  DSPI_2 FlexPWM_0 SIUL           | \frac{1}{0}                   | Slow    | Medium              | 61     | 95      |

| A[14] | PCR[14]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[14]                                     | SIUL Safety Port_0  SIUL                         | I/O<br>O<br>—<br>—<br>I       | Slow    | Medium              | 63     | 99      |

| A[15] | PCR[15]  | ALT0 ALT1 ALT2 ALT3 — —           | GPIO[15]  RXD EIRQ[14]                       | SIUL  —  —  —  Safety Port_0 SIUL                | I/O<br>—<br>—<br>—<br>—<br>I  | Slow    | Medium              | 64     | 100     |

|       |          |                                   |                                              | Port B (16-bit)                                  |                               |         |                     |        |         |

| B[0]  | PCR[16]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[16]<br>TXD<br>—<br>DEBUG[0]<br>EIRQ[15] | SIUL<br>FlexCAN_0<br>—<br>SSCM<br>SIUL           | I/O<br>O<br>—<br>—<br>I       | Slow    | Medium              | 49     | 76      |

| B[1]  | PCR[17]  | ALT0 ALT1 ALT2 ALT3 — —           | GPIO[17]  —  DEBUG[1]  RXD  EIRQ[16]         | SIUL  SSCM FlexCAN_0 SIUL                        | I/O<br>—<br>—<br>—<br>I       | Slow    | Medium              | 50     | 77      |

#### 3 Electrical characteristics

#### 3.1 Introduction

This section contains device electrical characteristics as well as temperature and power considerations.

This microcontroller contains input protection against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down resistors, which are provided by the device for most general purpose pins.

The following tables provide the device characteristics and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

#### Caution:

All of the following parameter values can vary depending on the application and must be confirmed during silicon characterization or silicon reliability trial.

#### 3.2 Parameter classification

The electrical parameters are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 8* are used and the parameters are tagged accordingly in the tables where appropriate.

Table 8. Parameter classifications

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

Note: The classification is shown in the column labeled "C" in the parameter tables where appropriate.

Table 10. Recommended operating conditions (5.0 V) (continued)

| Symbol                                   |    | Dovernotor                             | Canditions                         | Valu                         | ue  | 11:4 |  |                  |  |      |

|------------------------------------------|----|----------------------------------------|------------------------------------|------------------------------|-----|------|--|------------------|--|------|

| Symbol                                   |    | Parameter                              | Conditions                         | Min Max <sup>(1)</sup>       |     |      |  | Conditions Min M |  | Unit |

|                                          |    | 5.0.V.ADC 0 supply and                 | _                                  | 4.5                          | 5.5 |      |  |                  |  |      |

| V <sub>DD_HV_ADC0</sub>                  | SR | riigii reference voltage               | Relative to V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> - 0.1 |     | V    |  |                  |  |      |

| V <sub>SS_HV_ADC0</sub>                  | SR | ADC_0 ground and low reference voltage | _                                  | 0                            | 0   | V    |  |                  |  |      |

| V <sub>DD_LV_REGCOR</sub> (3),(4)        | СС | Internal supply voltage                | _                                  | _                            | _   | V    |  |                  |  |      |

| V <sub>SS_LV_REGCOR</sub> <sup>(3)</sup> | SR | Internal reference voltage             | _                                  | 0                            | 0   | V    |  |                  |  |      |

| V <sub>DD_LV_CORx</sub> (3),(4)          | СС | Internal supply voltage                | _                                  | _                            | _   | V    |  |                  |  |      |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>   | SR | Internal reference voltage             | _                                  | 0                            | 0   | V    |  |                  |  |      |

| T <sub>A</sub>                           | SR | Ambient temperature                    | f <sub>CPU</sub> = 60 MHz          | -40                          | 125 | °C   |  |                  |  |      |

| 'A                                       | SK | under bias                             | f <sub>CPU</sub> = 64 MHz          | -40                          | 105 | °C   |  |                  |  |      |

Full functionality cannot be guaranteed when voltage drops below 4.5 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

Table 11. Recommended operating conditions (3.3 V)

| Symbol                                |    | Parameter                                            | Conditions                         | Val                          | Unit                    |   |  |  |

|---------------------------------------|----|------------------------------------------------------|------------------------------------|------------------------------|-------------------------|---|--|--|

| Symbol                                |    | raiailletei                                          | Min Max <sup>(1)</sup>             |                              |                         |   |  |  |

| V <sub>SS</sub>                       | SR | Device ground                                        | _                                  | 0                            | 0                       | V |  |  |

| V <sub>DD_HV_IOx</sub> <sup>(2)</sup> | SR | 3.3 V input/output supply voltage                    | _                                  | 3.0                          | 3.6                     | ٧ |  |  |

| V <sub>SS_HV_IOx</sub>                | SR | Input/output ground voltage                          | _                                  | 0                            | 0                       | ٧ |  |  |

|                                       | SR | 3.3 V crystal oscillator amplifier supply voltage    | _                                  | 3.0                          | 3.6                     |   |  |  |

| V <sub>DD_HV_OSC</sub>                |    |                                                      | Relative to V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | $V_{DD\_HV\_IOx} + 0.1$ | > |  |  |

| V <sub>SS_HV_OSC</sub>                | SR | 3.3 V crystal oscillator amplifier reference voltage | ı                                  | 0                            | 0                       | > |  |  |

<sup>2.</sup> The difference between each couple of voltage supplies must be less than 100 mV,  $V_{DD\_HV\_IOy} - V_{DD\_HV\_IOx} < 100$  mV.

<sup>3.</sup> To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

<sup>4.</sup> The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent.

- V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted.

- V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_RECORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

Table 15. Approved NPN ballast components

| Part   | Manufacturer | Approved derivatives <sup>(1)</sup> |

|--------|--------------|-------------------------------------|

| BC817  | Infineon     | BC817-16; BC817-25; BC817SU         |

| BC617  | NXP          | BC817-16; BC817-25                  |

|        | ST           | BCP56-16                            |

| BCP56  | Infineon     | BCP56-10; BCP56-16                  |

| BCF 30 | ON Semi      | BCP56-10                            |

|        | NXP          | BCP56-10; BCP56-16                  |

<sup>1.</sup> For automotive applications please check with the appropriate transistor vendor for automotive grade certification

Table 16. Voltage regulator electrical characteristics

| Symbol                    |                                                                                                                                    | С | Parameter                                                            | Conditions                                                                                                                                                              | Value |     |     | Unit  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|-------|

| Symbol                    |                                                                                                                                    | C | Farameter                                                            | Conditions                                                                                                                                                              | Min   | Тур | Max | Ullit |

| V <sub>DD_LV_REGCOR</sub> | _LV_REGCOR C C P Output voltage under maximum load run supply current configuration Post-trimming                                  |   | 1.15                                                                 | _                                                                                                                                                                       | 1.32  | V   |     |       |

| C <sub>DEC1</sub>         | S<br>R                                                                                                                             | _ | External decoupling/stability ceramic capacitor                      | BJT from <i>Table 15</i> . Three capacitors (i.e. X7R or X8R capacitors) with nominal value of 10 µF                                                                    | 19.5  | 30  | _   | μF    |

|                           |                                                                                                                                    |   |                                                                      | BJT BC817, one capacitance of 22 µF                                                                                                                                     | 14.3  | 22  | _   | μF    |

| R <sub>REG</sub>          | S<br>R                                                                                                                             | _ | Resulting ESR of either one or all three C <sub>DEC1</sub>           | Absolute maximum value<br>between 100 kHz and<br>10 MHz                                                                                                                 | _     | _   | 45  | mΩ    |

| C <sub>DEC2</sub>         | S R External decoupling/stability ceramic capacitor  External decoupling/stability or X8R capacitors) with nominal value of 440 nF |   | 120<br>0                                                             | 176<br>0                                                                                                                                                                | _     | nF  |     |       |

| C <sub>DEC3</sub>         | S<br>R                                                                                                                             |   | External decoupling/stability ceramic capacitor on VDD_HV_REG        | nominal value of 440 nF  Three capacitors (i.e. X7R or X8R capacitors) with nominal value of 10 µF; C <sub>DEC3</sub> has to be equal or greater than C <sub>DEC1</sub> |       | 30  | _   | μF    |

| L <sub>Reg</sub>          | S<br>R                                                                                                                             | _ | Resulting ESL of $V_{DD\_HV\_REG}$ BCTRL and $V_{DD\_LV\_CORx}$ pins | _                                                                                                                                                                       | _     | _   | 5   | nΗ    |

56/103 Doc ID 16100 Rev 7

## 3.10.2 DC electrical characteristics (5 V)

*Table 19* gives the DC electrical characteristics at 5 V ( $4.5 \text{ V} < \text{V}_{DD\_HV\_IOx} < 5.5 \text{ V}$ , NVUSRO[PAD3V5V] = 0).

Table 19. DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)

| Symbol C          |   | Poromotor                                                                     | Conditions                             | Val                         | Unit                        |      |    |

|-------------------|---|-------------------------------------------------------------------------------|----------------------------------------|-----------------------------|-----------------------------|------|----|

| Symbol            |   | Parameter                                                                     | Conditions                             | Min                         | Max                         | Unit |    |

| V                 | D | Low level input voltage                                                       | _                                      | -0.4 <sup>(1)</sup>         | _                           | V    |    |

| V <sub>IL</sub>   | Р | Low level input voltage                                                       | _                                      | _                           | 0.35 V <sub>DD_HV_IOx</sub> | V    |    |

|                   | Р |                                                                               |                                        | 0.65 V <sub>DD_HV_IOx</sub> | _                           | V    |    |

| V <sub>IH</sub>   | D | High level input voltage                                                      |                                        |                             | $V_{DD_{-HV_{(1)}}}$ + 0.4  | V    |    |

| V <sub>HYS</sub>  | Т | Schmitt trigger hysteresis                                                    | _                                      | 0.1 V <sub>DD_HV_IOx</sub>  | _                           | V    |    |

| V <sub>OL_S</sub> | Р | Slow, low level output voltage                                                | I <sub>OL</sub> = 3 mA                 | _                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |    |

| V <sub>OH_S</sub> | Р | Slow, high level output voltage                                               | $I_{OH} = -3 \text{ mA}$               | 0.8 V <sub>DD_HV_IOx</sub>  | _                           | V    |    |

| V <sub>OL_M</sub> | Р | Medium, low level output voltage $I_{OL} = 3 \text{ mA}$ — $0.1 V_{DD\_HV\_}$ |                                        | 0.1 V <sub>DD_HV_IOx</sub>  | V                           |      |    |

| V <sub>OH_M</sub> | Р | Medium, high level output voltage                                             | $I_{OH} = -3 \text{ mA}$               | 0.8 V <sub>DD_HV_IOx</sub>  | _                           | V    |    |

| V <sub>OL_F</sub> | Р | Fast, low level output voltage                                                | I <sub>OL</sub> = 14 mA                | _                           | 0.1 V <sub>DD_HV_IOx</sub>  | V    |    |

| V <sub>OH_F</sub> | Р | Fast, high level output voltage                                               | $I_{OH} = -14 \text{ mA}$              | 0.8 V <sub>DD_HV_IOx</sub>  | _                           | V    |    |

| 1                 | Р | Equivalent pull-up current                                                    | $V_{IN} = V_{IL}$                      | -130                        | _                           | μA   |    |

| I <sub>PU</sub>   | ı | Г                                                                             | Equivalent pull-up current             | $V_{IN} = V_{IH}$           |                             | -10  | μΛ |

| l                 | Р | Equivalent pull-down current                                                  | $V_{IN} = V_{IL}$                      | 10                          | _                           | μA   |    |

| I <sub>PD</sub>   |   | Equivalent pull-down current                                                  | $V_{IN} = V_{IH}$                      | 1                           | 130                         | μΛ   |    |

| I <sub>IL</sub>   | Р | Input leakage current (all bidirectional ports) $T_A = -40 \text{ to } 12$    |                                        | -1                          | 1                           | μА   |    |

| I <sub>IL</sub>   | Р | Input leakage current (all ADC input-only ports)                              | $T_A = -40 \text{ to } 125 \text{ °C}$ | -0.5                        | 0.5                         | μA   |    |

| C <sub>IN</sub>   | D | Input capacitance                                                             |                                        |                             | 10                          | pF   |    |

<sup>1. &</sup>quot;SR" parameter values must not exceed the absolute maximum ratings shown in Table 9.

70

65

mΑ

Value Conditions<sup>(1)</sup> **Symbol** C **Parameter** Unit Min Тур Max  $C_1 = 25 pF, 40 MHz$ 22  $V_{DD} = 5.0 \text{ V} \pm 10\%,$  $C_1 = 25 \text{ pF}, 64 \text{ MHz}$ 33 PAD3V5V = 0Root medium square  $C_1 = 100 \text{ pF}, 40 \text{ MHz}$ 56 С I/O current for FAST mΑ I<sub>RMSFST</sub> С  $C_1 = 25 \text{ pF}, 40 \text{ MHz}$ 14 configuration  $V_{DD} = 3.3 \text{ V} \pm 10\%,$  $C_1 = 25 \text{ pF}, 64 \text{ MHz}$ 20 PAD3V5V = 1 $C_1 = 100 pF, 40 MHz$ 35

$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$

$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$

Table 24. I/O consumption (continued)

SD

R

**I**AVGSEG

Sum of all the static

I/O current within a

supply segment

#### 3.11 Main oscillator electrical characteristics

The SPC560P34/SPC560P40 provides an oscillator/resonator driver.

Table 25. Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)

| Symbol         |    | С  | Parameter                         | Conditions | Va  | lue   | Unit |    |    |    |   |                                      |        |   |    |    |

|----------------|----|----|-----------------------------------|------------|-----|-------|------|----|----|----|---|--------------------------------------|--------|---|----|----|

| Syllib         | Oi | J  | Farameter                         | Min Max    |     | Oilit |      |    |    |    |   |                                      |        |   |    |    |

| fosc           | SR | —  | Oscillator frequency              |            | 4   | 40    | MHz  |    |    |    |   |                                      |        |   |    |    |

| g <sub>m</sub> | _  | Р  | Transconductance                  |            | 6.5 | 25    | mA/V |    |    |    |   |                                      |        |   |    |    |

| Vosc           | _  | Т  | Oscillation amplitude on XTAL pin |            | 1   | _     | V    |    |    |    |   |                                      |        |   |    |    |

| toscsu         | _  | Т  | Start-up time <sup>(1),(2)</sup>  |            | 8   | _     | ms   |    |    |    |   |                                      |        |   |    |    |

|                |    | Т  | 4 MHz                             | 5          | 30  |       |      |    |    |    |   |                                      |        |   |    |    |

|                |    | Т  |                                   | 8 MHz      | 5   | 26    |      |    |    |    |   |                                      |        |   |    |    |

|                | СС | СС | СС                                | СС         | СС  | СС    | СС   | СС | СС | СС | Т | XTAL load capacitance <sup>(3)</sup> | 12 MHz | 5 | 23 | nf |

| CL             |    |    |                                   |            |     |       |      |    |    |    | Т | TAL load capacitatice                | 16 MHz | 5 | 19 | pf |

|                |    | Т  |                                   | 20 MHz     | 5   | 16    |      |    |    |    |   |                                      |        |   |    |    |

|                |    | Т  |                                   | 40 MHz     | 5   | 8     |      |    |    |    |   |                                      |        |   |    |    |

<sup>1.</sup> The start-up time is dependent upon crystal characteristics, board leakage, etc. High ESR and excessive capacitive loads can cause long start-up time.

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 to 125 °C, unless otherwise specified

<sup>2.</sup> Stated maximum values represent peak consumption that lasts only a few ns during I/O transition.

<sup>2.</sup> Value captured when amplitude reaches 90% of XTAL

<sup>3.</sup> This value is determined by the crystal manufacturer and board design. For 4 MHz to 40 MHz crystals specified for this oscillator, load capacitors should not exceed these limits.

Table 28. FMPLL electrical characteristics (continued)

| Symbol              | С | Po                                                | ramatar                                             | Conditions <sup>(1)</sup>                                                                 | Va                                | lue                      | Unit               |   |                       |

|---------------------|---|---------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|--------------------|---|-----------------------|

| Symbol              |   | Га                                                | Parameter                                           |                                                                                           | Min                               | Max                      | Oilit              |   |                       |

| f <sub>FREE</sub>   | Р | Free-running frequ                                | uency                                               | Measured using clock division—typically /16                                               | 20                                | 150                      | MHz                |   |                       |

| t <sub>CYC</sub>    | D | System clock perio                                | od                                                  | _                                                                                         | _                                 | 1 /<br>f <sub>SYS</sub>  | ns                 |   |                       |

| f <sub>LORL</sub>   | D | Loss of reference                                 | frequency window <sup>(3)</sup>                     | Lower limit                                                                               | 1.6                               | 3.7                      | MHz                |   |                       |

| f <sub>LORH</sub>   | D | Loss of ference                                   | nequency window.                                    | Upper limit                                                                               | 24                                | 56                       | IVII IZ            |   |                       |

| f <sub>SCM</sub>    | D | Self-clocked mode                                 | e frequency <sup>(4),(5)</sup>                      | _                                                                                         | 20                                | 150                      | MHz                |   |                       |

|                     | Т |                                                   |                                                     |                                                                                           | Short-term jitter <sup>(10)</sup> | f <sub>SYS</sub> maximum | -4                 | 4 | % f <sub>CLKOUT</sub> |

| C <sub>JITTER</sub> |   | T CLKOUT period jitter <sup>(6),(7),(8),(9)</sup> | Long-term jitter<br>(average over 2 ms<br>interval) | f <sub>PLLIN</sub> = 16 MHz<br>(resonator), f <sub>PLLCLK</sub> at<br>64 MHz, 4000 cycles | _                                 | 10                       | ns                 |   |                       |

| t <sub>lpll</sub>   | D | PLL lock time <sup>(11), (</sup>                  | (12)                                                | _                                                                                         | _                                 | 200                      | μs                 |   |                       |

| t <sub>dc</sub>     | D | Duty cycle of refer                               | ence                                                | _                                                                                         | 40                                | 60                       | %                  |   |                       |

| f <sub>LCK</sub>    | D | Frequency LOCK                                    | range                                               | _                                                                                         | -6                                | 6                        | % f <sub>SYS</sub> |   |                       |

| f <sub>UL</sub>     | D | Frequency un-LO                                   | CK range                                            | _                                                                                         | -18                               | 18                       | % f <sub>SYS</sub> |   |                       |

| f <sub>CS</sub>     | D | Modulation depth                                  |                                                     | Center spread                                                                             | ±0.25                             | ±4.0<br>(13)             | % f <sub>SYS</sub> |   |                       |

| f <sub>DS</sub>     | D |                                                   |                                                     | Down spread                                                                               | -0.5                              | -8.0                     |                    |   |                       |

| f <sub>MOD</sub>    | D | Modulation freque                                 | ncy <sup>(14)</sup>                                 | _                                                                                         | _                                 | 70                       | kHz                |   |                       |

- 1.  $V_{DD\_LV\_CORx} = 1.2 \text{ V} \pm 10\%$ ;  $V_{SS} = 0 \text{ V}$ ;  $T_A = -40 \text{ to } 125 \text{ °C}$ , unless otherwise specified

- 2. Considering operation with PLL not bypassed.

- 3. "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self clocked mode.

- Self clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

- f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

- 6. This value is determined by the crystal manufacturer and board design.

- 7. Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DD\_LV\_COR0</sub> and V<sub>SS\_LV\_COR0</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

- 8. Proper PC board layout procedures must be followed to achieve specifications.

- 9. Values are obtained with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of  $C_{\text{JITTER}}$  and either  $f_{\text{CS}}$  or  $f_{\text{DS}}$  (depending on whether center spread or down spread modulation is enabled).

- 10. Short term jitter is measured on the clock rising edge at cycle n and cycle n+4.

- 11. This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

- 12. This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

- 13. This value is true when operating at frequencies above 60 MHz, otherwise f<sub>CS</sub> is 2% (above 64 MHz).

- 14. Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

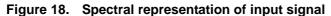

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time  $(T_S)$ . The filter is typically designed to act as anti-aliasing.

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period  $(T_C)$ . Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 11* between the ideal and real sampled voltage on  $C_S$ :

#### **Equation 11**

$$\frac{v_A}{v_{A2}} = \frac{c_{P1} + c_{P2} + c_F}{c_{P1} + c_{P2} + c_F + c_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

#### **Equation 12**

$$C_F > 2048 \cdot C_S$$

- 4.  $C_L$  includes device and package capacitance ( $C_{PKG}$  < 5 pF).

- 5. The configuration PAD3V5 = 1 when V<sub>DD</sub> = 5 V is only transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

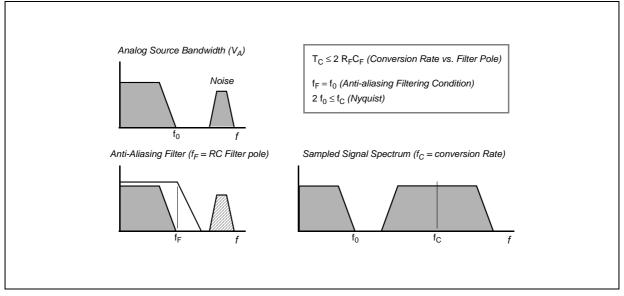

## 3.17.2 IEEE 1149.1 interface timing

Table 38. JTAG pin AC electrical characteristics

| No | Symbol                                  |    | С | Parameter                                                     | Conditions | Value |     | Unit |

|----|-----------------------------------------|----|---|---------------------------------------------------------------|------------|-------|-----|------|

| -  |                                         |    |   | r ai ainetei                                                  | Conditions | Min   | Max | Jill |

| 1  | t <sub>JCYC</sub>                       | CC | D | TCK cycle time                                                | _          | 100   | _   | ns   |

| 2  | t <sub>JDC</sub>                        | СС | D | TCK clock pulse width (measured at V <sub>DD_HV_IOx</sub> /2) |            | 40    | 60  | ns   |

| 3  | t <sub>TCKRISE</sub>                    | CC | D | TCK rise and fall times (40%–70%)                             | _          | _     | 3   | ns   |

| 4  | $t_{\rm TMSS}, t_{\rm TDIS}$            | CC | D | TMS, TDI data setup time                                      | _          | 5     | _   | ns   |

| 5  | t <sub>TMSH,</sub><br>t <sub>TDIH</sub> | СС | D | TMS, TDI data hold time —                                     |            | 25    |     | ns   |

| 6  | t <sub>TDOV</sub>                       | СС | D | TCK low to TDO data valid                                     | _          | _     | 40  | ns   |

| 7  | t <sub>TDOI</sub>                       | СС | D | TCK low to TDO data invalid —                                 |            | 0     | _   | ns   |

| 8  | t <sub>TDOHZ</sub>                      | CC | D | TCK low to TDO high impedance                                 | _          | 40    | _   | ns   |

| 9  | t <sub>BSDV</sub>                       | СС | D | TCK falling edge to output valid                              | _          | _     | 50  | ns   |

| 10 | t <sub>BSDVZ</sub>                      | СС | D | TCK falling edge to output valid out of high impedance        | _          | _     | 50  | ns   |

| 11 | t <sub>BSDHZ</sub>                      | СС | D | TCK falling edge to output high impedance                     | _          | _     | 50  | ns   |

| 12 | t <sub>BSDST</sub>                      | СС | D | Boundary scan input valid to TCK rising edge                  | _          | 50    | —   | ns   |

| 13 | t <sub>BSDHT</sub>                      | СС | D | TCK rising edge to boundary scan input invalid                | _          | 50    |     | ns   |

Figure 22. JTAG test clock input timing

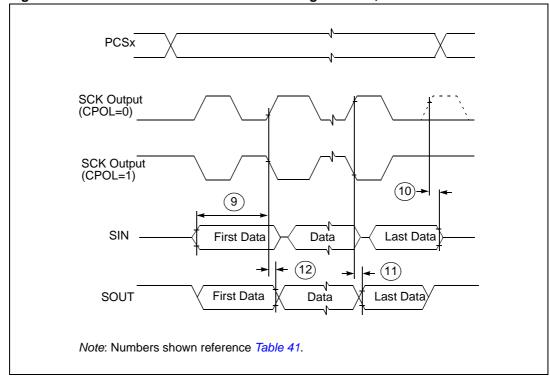

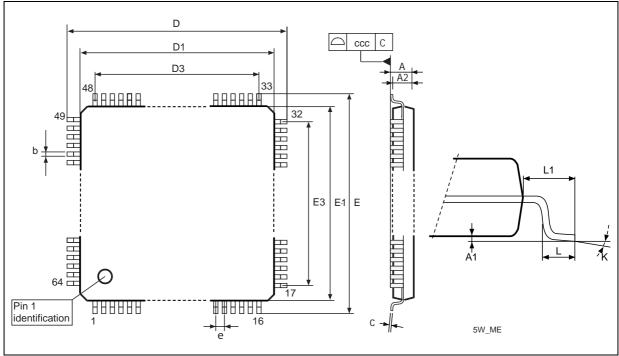

Figure 34. DSPI modified transfer format timing - Master, CPHA = 1

# 4 Package characteristics

# 4.1 ECOPACK<sup>®</sup>

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK® is an ST trademark.

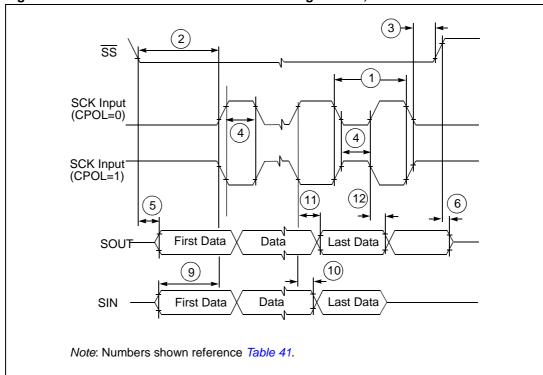

## 4.2.2 LQFP64 mechanical outline drawing

Figure 39. LQFP64 package mechanical drawing

Table 43. LQFP64 package mechanical data

|        | Dimensions |      |      |                       |        |        |  |  |  |  |  |

|--------|------------|------|------|-----------------------|--------|--------|--|--|--|--|--|

| Symbol |            | mm   |      | inches <sup>(1)</sup> |        |        |  |  |  |  |  |

|        | Min        | Тур  | Max  | Min                   | Тур    | Max    |  |  |  |  |  |

| А      | _          | _    | 1.6  | _                     | _      | 0.063  |  |  |  |  |  |

| A1     | 0.05       | _    | 0.15 | 0.002                 | _      | 0.0059 |  |  |  |  |  |

| A2     | 1.35       | 1.4  | 1.45 | 0.0531                | 0.0551 | 0.0571 |  |  |  |  |  |

| b      | 0.17       | 0.22 | 0.27 | 0.0067                | 0.0087 | 0.0106 |  |  |  |  |  |

| С      | 0.09       | _    | 0.2  | 0.0035                | _      | 0.0079 |  |  |  |  |  |

| D      | 11.8       | 12   | 12.2 | 0.4646                | 0.4724 | 0.4803 |  |  |  |  |  |

| D1     | 9.8        | 10   | 10.2 | 0.3858                | 0.3937 | 0.4016 |  |  |  |  |  |

| D3     | _          | 7.5  | _    | _                     | 0.2953 | _      |  |  |  |  |  |

| Е      | 11.8       | 12   | 12.2 | 0.4646                | 0.4724 | 0.4803 |  |  |  |  |  |

| E1     | 9.8        | 10   | 10.2 | 0.3858                | 0.3937 | 0.4016 |  |  |  |  |  |

| E3     | _          | 7.5  | _    | _                     | 0.2953 | _      |  |  |  |  |  |

| е      | _          | 0.5  | _    | _                     | 0.0197 | _      |  |  |  |  |  |

| L      | 0.45       | 0.6  | 0.75 | 0.0177                | 0.0236 | 0.0295 |  |  |  |  |  |

| L1     | _          | 1    | _    | _                     | 0.0394 | _      |  |  |  |  |  |

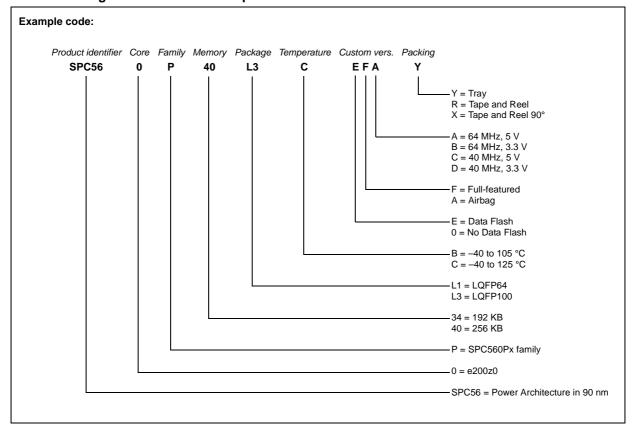

# 5 Ordering information

Figure 40. Commercial product code structure

96/103 Doc ID 16100 Rev 7

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com