#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 64                                                                       |

| Program Memory Size        | 192KB (192K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 12K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p34l3cefar |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | Feature                             | SPC560P34 SPC560P40<br>Full-featured Full-featured |                                             |  |  |

|------------------|-------------------------------------|----------------------------------------------------|---------------------------------------------|--|--|

| eDMA (enhanc     | ed direct memory access) channels   | 16                                                 |                                             |  |  |

| FlexCAN (cont    | roller area network)                | 1 <sup>(1)</sup>                                   | 2 <sup>(1),(2)</sup>                        |  |  |

| Safety port      |                                     | No                                                 | Yes (via second FlexCAN module)             |  |  |

| FCU (fault colle | ection unit)                        | Y                                                  | es                                          |  |  |

| CTU (cross trig  | ggering unit)                       | Yes                                                | Yes                                         |  |  |

| eTimer           |                                     | 1 (16-bit, 6                                       | channels)                                   |  |  |

| FlexPWM (puls    | se-width modulation) channels       | 8<br>(capture capabity not<br>supported)           | 8<br>(capture capability not<br>supported)  |  |  |

| Analog-to-digita | al converter (ADC)                  | 1 (10-bit, 1                                       | 6 channels)                                 |  |  |

| LINFlex          |                                     | 2<br>(1 × Master/Slave,<br>1 × Master only)        | 2<br>(1 × Master/Slave,<br>1 × Master only) |  |  |

| DSPI (deserial   | serial peripheral interface)        | 2                                                  | 3                                           |  |  |

| CRC (cyclic red  | dundancy check) unit                | Y                                                  | es                                          |  |  |

| Junction tempe   | erature sensor                      | Ν                                                  | 10                                          |  |  |

| JTAG controlle   | r                                   | Y                                                  | es                                          |  |  |

| Nexus port con   | ntroller (NPC)                      | Yes (Nexu                                          | us Class 1)                                 |  |  |

|                  | Digital power supply <sup>(3)</sup> | 3.3 V or 5 V single supp                           | ly with external transistor                 |  |  |

| Supply           | Analog power supply                 | 3.3 V                                              | or 5 V                                      |  |  |

| Supply           | Internal RC oscillator              | 16                                                 | MHz                                         |  |  |

|                  | External crystal oscillator         | 4-40                                               | ) MHz                                       |  |  |

| Packages         |                                     | LQFP64<br>LQFP100                                  |                                             |  |  |

| Temperature      | Standard ambient temperature        | -40 to                                             | 125 °C                                      |  |  |

| remperature      | Standard ampient temperature        | -40 10                                             | 125 0                                       |  |  |

#### Table 2. SPC560P34/SPC560P40 device comparison (continued)

1. Each FlexCAN module has 32 message buffers.

2. One FlexCAN module can act as a safety port with a bit rate as high as 8 Mbit/s at 64 MHz.

3. The different supply voltages vary according to the part number ordered.

SPC560P34/SPC560P40 is available in two configurations having different features: Full-featured and airbag. *Table 3* shows the main differences between the two versions of the SPC560P40 MCU.

The crossbar provides the following features:

- 3 master ports:

- e200z0 core complex instruction port

- e200z0 core complex Load/Store Data port

- eDMA

- 3 slave ports:

- Flash memory (Code and Data)

- SRAM

- Peripheral bridge

- 32-bit internal address, 32-bit internal data paths

- Fixed Priority Arbitration based on Port Master

- Temporary dynamic priority elevation of masters

### 1.5.3 Enhanced direct memory access (eDMA)

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 16 programmable channels, with minimal intervention from the host processor. The hardware micro architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels.

The eDMA module provides the following features:

- 16 channels support independent 8-, 16- or 32-bit single value or block transfers

- Supports variable-sized queues and circular queues

- Source and destination address registers are independently configured to either postincrement or to remain constant

- Each transfer is initiated by a peripheral, CPU, or eDMA channel request

- Each eDMA channel can optionally send an interrupt request to the CPU on completion of a single value or block transfer

- DMA transfers possible between system memories, DSPIs, ADC, FlexPWM, eTimer and CTU

- Programmable DMA channel multiplexer allows assignment of any DMA source to any available DMA channel with as many as 30 request sources

- eDMA abort operation through software

### 1.5.4 Flash memory

The SPC560P34/SPC560P40 provides 320 KB of programmable, non-volatile, flash memory. The non-volatile memory (NVM) can be used for instruction and/or data storage. The flash memory module is interfaced to the system bus by a dedicated flash memory controller. It supports a 32-bit data bus width at the system bus port, and a 128-bit read data interface to flash memory. The module contains four 128-bit wide prefetch buffers. Prefetch buffer hits allow no-wait responses. Normal flash memory array accesses are registered and are forwarded to the system bus on the following cycle, incurring two wait-states.

### 1.5.8 System clocks and clock generation

The following list summarizes the system clock and clock generation on the SPC560P34/SPC560P40:

- Lock detect circuitry continuously monitors lock status

- Loss of clock (LOC) detection for PLL outputs

- Programmable output clock divider (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and eTimer module running at the same frequency as the e200z0h core

- Internal 16 MHz RC oscillator for rapid start-up and safe mode: supports frequency trimming by user application

### 1.5.9 Frequency-modulated phase-locked loop (FMPLL)

The FMPLL allows the user to generate high speed system clocks from a 4–40 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock. The PLL multiplication factor, output clock divider ratio are all software configurable.

The FMPLL has the following major features:

- Input clock frequency: 4–40 MHz

- Maximum output frequency: 64 MHz

- Voltage controlled oscillator (VCO)—frequency 256–512 MHz

- Reduced frequency divider (RFD) for reduced frequency operation without forcing the FMPLL to relock

- Frequency-modulated PLL

- Modulation enabled/disabled through software

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency): programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

### 1.5.10 Main oscillator

The main oscillator provides these features:

- Input frequency range: 4–40 MHz

- Crystal input mode or oscillator input mode

- PLL reference

### 1.5.11 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

platform memory errors reported by error-correcting codes and/or generic access error information for certain processor cores.

The Error Correction Status Module supports a number of miscellaneous control functions for the platform. The ECSM includes these features:

- Registers for capturing information on platform memory errors if error-correcting codes (ECC) are implemented

- For test purposes, optional registers to specify the generation of double-bit memory errors are enabled on the SPC560P34/SPC560P40.

The sources of the ECC errors are:

- Flash memory

- SRAM

### 1.5.19 Peripheral bridge (PBRIDGE)

The PBRIDGE implements the following features:

- Duplicated periphery

- Master access privilege level per peripheral (per master: read access enable; write access enable)

- Write buffering for peripherals

- Checker applied on PBRIDGE output toward periphery

- Byte endianess swap capability

### 1.5.20 Controller area network (FlexCAN)

The SPC560P34/SPC560P40 MCU contains one controller area network (FlexCAN) module. This module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to be used primarily as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth. The FlexCAN module contains 32 message buffers.

The FlexCAN module provides the following features:

- Full implementation of the CAN protocol specification, version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- Up to 8-bytes data length

- Programmable bit rate up to 1 Mbit/s

- 32 message buffers of up to 8-bytes data length

- Each message buffer configurable as Rx or Tx, all supporting standard and extended messages

- Programmable loop-back mode supporting self-test operation

- 3 programmable mask registers

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independent of the transmission medium (an external transceiver is assumed)

- High immunity to EMI

- Short latency time due to an arbitration scheme for high-priority messages

- Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a 6-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- Programmable clock source

- System clock

- Direct oscillator clock to avoid PLL jitter

## 1.5.21 Safety port (FlexCAN)

The SPC560P34/SPC560P40 MCU has a second CAN controller synthesized to run at high bit rates to be used as a safety port. The CAN module of the safety port provides the following features:

- Identical to the FlexCAN module

- Bit rate up to 8 Mbit/s at 64 MHz CPU clock using direct connection between CAN modules (no physical transceiver required)

- 32 message buffers of up to 8-bytes data length

- Can be used as a second independent CAN module

The FlexPWM block implements the following features:

- 16-bit resolution for center, edge-aligned, and asymmetrical PWMs

- Clock frequency same as that used for e200z0h core

- PWM outputs can operate as complementary pairs or independent channels

- Can accept signed numbers for PWM generation

- Independent control of both edges of each PWM output

- Synchronization to external hardware or other PWM supported

- Double buffered PWM registers

- Integral reload rates from 1 to 16

- Half cycle reload capability

- Multiple ADC trigger events can be generated per PWM cycle via hardware

- Write protection for critical registers

- Fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Independent top and bottom deadtime insertion

- Each complementary pair can operate with its own PWM frequency and deadtime values

- Individual software-control for each PWM output

- All outputs can be programmed to change simultaneously via a "Force Out" event

- PWMX pin can optionally output a third PWM signal from each submodule

- Channels not used for PWM generation can be used for buffered output compare functions

- Channels not used for PWM generation can be used for input capture functions

- Enhanced dual-edge capture functionality

- eDMA support with automatic reload

- 2 fault inputs

- Capture capability for PWMA, PWMB, and PWMX channels not supported

| Port  | PCR      | Alternate                         | Functions                                  | Peripheral <sup>(3)</sup>                            | I/O                           | Pad s   | beed <sup>(5)</sup> | F      | Pin     |

|-------|----------|-----------------------------------|--------------------------------------------|------------------------------------------------------|-------------------------------|---------|---------------------|--------|---------|

| pin   | register | function <sup>(1),(2)</sup>       | FUNCTIONS                                  | Peripheral                                           | direc-<br>tion <sup>(4)</sup> | SRC = 0 | SRC = 1             | 64-pin | 100-pin |

| D[11] | PCR[59]  | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[59]<br>B[0]<br>—                      | SIUL<br>FlexPWM_0<br>—<br>—                          | I/O<br>O<br>—                 | Slow    | Medium              | _      | 54      |

| D[12] | PCR[60]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[60]<br>X[1]<br>—<br>RXD               | SIUL<br>FlexPWM_0<br>—<br>LIN_1                      | I/O<br>O<br>—<br>I            | Slow    | Medium              | 45     | 70      |

| D[13] | PCR[61]  | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[61]<br>A[1]<br>—                      | SIUL<br>FlexPWM_0<br>—<br>—                          | I/O<br>O<br>—                 | Slow    | Medium              | 44     | 67      |

| D[14] | PCR[62]  | ALTO<br>ALT1<br>ALT2<br>ALT3      | GPIO[62]<br>B[1]<br>—<br>—                 | SIUL<br>FlexPWM_0<br>—<br>—                          | I/O<br>O<br>                  | Slow    | Medium              | 46     | 73      |

| D[15] | PCR[63]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[63]<br>—<br>—<br>AN[10]<br>emu. AN[4] | SIUL<br>—<br>—<br>ADC_0<br>emu. ADC_1 <sup>(6)</sup> | Input only                    | _       | _                   | _      | 41      |

|       |          |                                   |                                            | Port E (16-bit)                                      |                               |         |                     |        |         |

| E[1]  | PCR[65]  | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[65]<br>—<br>—<br>—<br>AN[4]           | SIUL<br>—<br>—<br>—<br>ADC_0                         | Input only                    | _       | _                   | 18     | 27      |

| E[2]  | PCR[66]  | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[66]<br>—<br>—<br>—<br>AN[5]           | SIUL<br>—<br>—<br>—<br>ADC_0                         | Input only                    | _       | _                   | 23     | 32      |

| E[3]  | PCR[67]  | ALTO<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[67]<br>—<br>—<br>—<br>AN[6]           | SIUL<br>—<br>—<br>—<br>ADC_0                         | Input only                    | _       | _                   | 30     | 42      |

Table 7.Pin muxing (continued)

# **3 Electrical characteristics**

### 3.1 Introduction

This section contains device electrical characteristics as well as temperature and power considerations.

This microcontroller contains input protection against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down resistors, which are provided by the device for most general purpose pins.

The following tables provide the device characteristics and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

### Caution:

All of the following parameter values can vary depending on the application and must be confirmed during silicon characterization or silicon reliability trial.

## 3.2 Parameter classification

The electrical parameters are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 8* are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### Table 8.Parameter classifications

Note: The classification is shown in the column labeled "C" in the parameter tables where appropriate.

|                                                  |    | <b>D</b>                                         |                                       | Va                              | lue                          |      |

|--------------------------------------------------|----|--------------------------------------------------|---------------------------------------|---------------------------------|------------------------------|------|

| Symbol                                           |    | Parameter                                        | Conditions                            | Min                             | Max <sup>(1)</sup>           | Unit |

|                                                  |    | 2 2 V voltago regulator                          | —                                     | 3.0                             | 3.6                          |      |

| $V_{DD_HV_REG}$                                  | SR | 3.3 V voltage regulator<br>supply voltage        | Relative to<br>V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> -0.1     | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

|                                                  |    |                                                  | —                                     | 3.0                             | 5.5                          |      |

| V <sub>DD_HV_ADC0</sub>                          | SR | 3.3 V ADC_0 supply and<br>high reference voltage | Relative to<br>V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> -<br>0.1 | 5.5                          | V    |

| V <sub>SS_HV_ADC0</sub>                          | SR | ADC_0 ground and low<br>reference voltage        | _                                     | 0                               | 0                            | V    |

| V <sub>DD_LV_REGCOR</sub> <sup>(3)</sup><br>,(4) | сс | Internal supply voltage                          | _                                     | _                               | _                            | V    |

| $V_{SS_LV_REGCOR}^{(3)}$                         | SR | Internal reference<br>voltage                    | _                                     | 0                               | 0                            | V    |

| V <sub>DD_LV_CORx</sub> <sup>(3),(4)</sup>       | СС | Internal supply voltage                          | —                                     | —                               | —                            | V    |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>           | SR | Internal reference<br>voltage                    | _                                     | 0                               | 0                            | V    |

| т.                                               | SR | Ambient temperature                              | f <sub>CPU</sub> = 60 MHz             | -40                             | 125                          | °C   |

| Τ <sub>Α</sub>                                   |    | under bias                                       | f <sub>CPU</sub> = 64 MHz             | -40                             | 105                          | °C   |

Table 11. Recommended operating conditions (3.3 V) (continued)

Full functionality cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and 1. I/Os DC electrical specification may not be guaranteed.

2. The difference between each couple of voltage supplies must be less than 100 mV,  $|V_{DD_{HV_{IOY}}} V_{DD_HV_IOx} | < 100 \text{ mV}.$

3. To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an on-chip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

4. The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent. - V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LY\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted. - V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_RECORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

Figure 8 shows the constraints of the different power supplies.

## 3.5 Thermal characteristics

### 3.5.1 Package thermal characteristics

### Table 12.LQFP thermal characteristics

| Symbol             | Parameter                                                | Conditions            | Туріса  | Unit   |      |

|--------------------|----------------------------------------------------------|-----------------------|---------|--------|------|

| Symbol             | Falametei                                                | Conditions            | 100-pin | 64-pin | Onic |

| R <sub>θJA</sub>   | Thermal resistance junction-to-ambient, natural          | Single layer board—1s | 63      | 57     | °C/W |

| ΝθJΑ               | convection <sup>(1)</sup>                                | Four layer board—2s2p | 51      | 41     | °C/W |

| $R_{\thetaJB}$     | Thermal resistance junction-to-board <sup>(2)</sup>      | Four layer board—2s2p | 33      | 22     | °C/W |

| $R_{\theta JCtop}$ | Thermal resistance junction-to-case (top) <sup>(3)</sup> | Single layer board—1s | 15      | 13     | °C/W |

| $\Psi_{JB}$        | Junction-to-board, natural convection <sup>(4)</sup>     | Operating conditions  | 33      | 22     | °C/W |

| $\Psi_{JC}$        | Junction-to-case, natural convection <sup>(5)</sup>      | Operating conditions  | 1       | 1      | °C/W |

1. Junction-to-ambient thermal resistance determined per JEDEC JESD51-7. Thermal test board meets JEDEC specification for this package.

2. Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package. When Greek letters are not available, the symbols are typed as RthJB or Theta-JB.

3. Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

4. Thermal characterization parameter indicating the temperature difference between the board and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JB.

5. Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JC.

### 3.5.2 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from *Equation 1*:

Equation 1:  $T_J = T_A + (R_{\theta JA} * P_D)$

where:

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in *Equation 2* as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

### 3.10.2 DC electrical characteristics (5 V)

Table 19 gives the DC electrical characteristics at 5 V (4.5 V <  $V_{DD_HV_IOx}$  < 5.5 V, NVUSRO[PAD3V5V] = 0).

|                   |   | <b>D</b>                                            |                          | Va                          | lue                            | Unit |  |

|-------------------|---|-----------------------------------------------------|--------------------------|-----------------------------|--------------------------------|------|--|

| Symbol            | С | Parameter                                           | Conditions               | Min                         | Max                            |      |  |

|                   | D |                                                     | —                        | -0.4 <sup>(1)</sup>         | —                              | V    |  |

| V <sub>IL</sub>   | Р | Low level input voltage                             |                          |                             | 0.35 V <sub>DD_HV_IOx</sub>    | V    |  |

|                   | Р |                                                     | —                        | 0.65 V <sub>DD_HV_IOx</sub> | —                              | V    |  |

| $V_{IH}$          | D | High level input voltage                            | _                        | _                           | $V_{\text{DD}_{HV,IOx}} + 0.4$ | V    |  |

| V <sub>HYS</sub>  | Т | Schmitt trigger hysteresis                          | _                        | 0.1 V <sub>DD_HV_IOx</sub>  | —                              | V    |  |

| V <sub>OL_S</sub> | Р | Slow, low level output voltage                      | I <sub>OL</sub> = 3 mA   | _                           | 0.1 V <sub>DD_HV_IOx</sub>     | V    |  |

| V <sub>OH_S</sub> | Р | Slow, high level output voltage                     | I <sub>OH</sub> = -3 mA  | 0.8 V <sub>DD_HV_IOx</sub>  | —                              | V    |  |

| $V_{OL_M}$        | Ρ | Medium, low level output voltage                    | I <sub>OL</sub> = 3 mA   | _                           | 0.1 V <sub>DD_HV_IOx</sub>     | V    |  |

| V <sub>OH_M</sub> | Ρ | Medium, high level output voltage                   | I <sub>OH</sub> = -3 mA  | 0.8 V <sub>DD_HV_IOx</sub>  | _                              | V    |  |

| $V_{OL_F}$        | Р | Fast, low level output voltage                      | I <sub>OL</sub> = 14 mA  | _                           | 0.1 V <sub>DD_HV_IOx</sub>     | V    |  |

| $V_{OH_F}$        | Р | Fast, high level output voltage                     | I <sub>OH</sub> = -14 mA | 0.8 V <sub>DD_HV_IOx</sub>  | —                              | V    |  |

| 1                 | Р | Equivalent pull-up current                          | $V_{IN} = V_{IL}$        | -130                        | —                              | μA   |  |

| I <sub>PU</sub>   | F |                                                     | $V_{IN} = V_{IH}$        | _                           | -10                            | μΑ   |  |

| I <sub>PD</sub>   | Р | Equivalent pull-down current                        | $V_{IN} = V_{IL}$        | 10                          | —                              | μA   |  |

| чРD               | 1 |                                                     | $V_{IN} = V_{IH}$        |                             | 130                            | μΛ   |  |

| Ι <sub>ΙL</sub>   | Ρ | Input leakage current<br>(all bidirectional ports)  | $T_A = -40$ to 125 °C    | -1                          | 1                              | μA   |  |

| IIL               | Р | Input leakage current<br>(all ADC input-only ports) | $T_A = -40$ to 125 °C    | -0.5                        | 0.5                            | μA   |  |

| C <sub>IN</sub>   | D | Input capacitance                                   | —                        | _                           | 10                             | pF   |  |

Table 19. DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)

1. "SR" parameter values must not exceed the absolute maximum ratings shown in Table 9.

| Symbol                  | с |         | Parameter                                     | Conditions                                                    |                                    | Valu   | e <sup>(1)</sup> | Unit |  |

|-------------------------|---|---------|-----------------------------------------------|---------------------------------------------------------------|------------------------------------|--------|------------------|------|--|

| Symbol                  | C |         |                                               |                                                               |                                    | Тур    | Max              | Unit |  |

|                         |   |         | RUN—Maximum mode <sup>(2)</sup>               |                                                               | 40 MHz                             | 44     | 55               |      |  |

| I <sub>DD_LV_CORx</sub> | т |         | RUN-Maximum mode                              |                                                               | 64 MHz                             | 52     | 65               |      |  |

|                         | P | 1       |                                               | RUN—Typical mode <sup>(3)</sup>                               | V <sub>DD_LV_CORx</sub> externally | 40 MHz | 38               | 46   |  |

|                         |   | ţ       | forced at 1.3 V                               | 64 MHz                                                        | 45                                 | 54     |                  |      |  |

|                         |   | current | HALT mode <sup>(4)</sup>                      |                                                               | —                                  | 1.5    | 10               |      |  |

|                         |   |         | STOP mode <sup>(5)</sup>                      |                                                               | —                                  | 1      | 10               | mA   |  |

| I <sub>DD_ADC</sub>     | т | Supply  | ADC                                           | V <sub>DD_HV_ADC0</sub> at 3.3 V<br>f <sub>ADC</sub> = 16 MHz | ADC_0                              | 3      | 4                |      |  |

| I <sub>DD_OSC</sub>     | Т |         | Oscillator                                    | $V_{DD_HV_OSC}$ at 3.3 V                                      | 8 MHz                              | 2.6    | 3.2              |      |  |

| I <sub>DD_HV_REG</sub>  | D |         | Internal regulator module current consumption | $V_{DD_{HV_{REG}}}$ at 5.5 V                                  |                                    | _      | 10               |      |  |

Table 22.Supply current (3.3 V, NVUSRO[PAD3V5V] = 1)

1. All values to be confirmed after characterization/data collection.

Maximum mode: FlexPWM, ADC, CTU, DSPI, LINFlex, FlexCAN, 15 output pins, PLL\_0 enabled, 125 °C ambient. I/O supply current excluded.

- Typical mode configurations: DSPI, LINFlex, FlexCAN, 15 output pins, PLL\_0, 105 °C ambient. I/O supply current excluded.

- 4. Halt mode configurations: Code fetched from SRAM, code flash memory and data flash memory in low power mode, OSC/PLL\_0 are OFF, core clock frozen, all peripherals disabled.

- 5. STOP "P" mode Device Under Test (DUT) configuration: Code fetched from SRAM, code flash memory and data flash memory off, OSC/PLL\_0 are OFF, core clock frozen, all peripherals disabled.

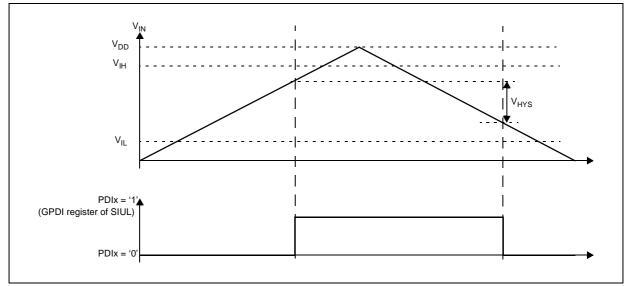

### 3.10.4 Input DC electrical characteristics definition

*Figure 14* shows the DC electrical characteristics behavior as function of time.

Figure 14. Input DC electrical characteristics definition

| Symb             | al                | с  | Parameter                         | Conditions | Va  | lue | Unit |                                      |        |   |        |    |

|------------------|-------------------|----|-----------------------------------|------------|-----|-----|------|--------------------------------------|--------|---|--------|----|

| Symb             | 01                | C  | Faranieter                        | Conditions | Min | Max | Unit |                                      |        |   |        |    |

| f <sub>OSC</sub> | SR                | —  | Oscillator frequency 4 40         |            |     | 40  | MHz  |                                      |        |   |        |    |

| 9 <sub>m</sub>   | —                 | Ρ  | Transconductance                  |            | 4   | 20  | mA/V |                                      |        |   |        |    |

| V <sub>OSC</sub> | —                 | Т  | Oscillation amplitude on XTAL pin |            | 1   | —   | V    |                                      |        |   |        |    |

| toscsu           |                   | Т  | Start-up time <sup>(1),(2)</sup>  |            | 8   | —   | ms   |                                      |        |   |        |    |

|                  |                   | Т  |                                   | 4 MHz      | 5   | 30  |      |                                      |        |   |        |    |

|                  |                   | Т  |                                   | 8 MHz      | 5   | 26  |      |                                      |        |   |        |    |

| 6                | C <sub>L</sub> CC | сс | сс                                | сс         | сс  | сс  | Т    | XTAL load capacitance <sup>(3)</sup> | 12 MHz | 5 | 23     | nf |

| UL               |                   |    |                                   |            |     |     |      |                                      | Т      |   | 16 MHz | 5  |

|                  |                   | Т  |                                   | 20 MHz     | 5   | 16  |      |                                      |        |   |        |    |

|                  |                   |    |                                   | 40 MHz     | 5   | 8   |      |                                      |        |   |        |    |

Table 26.Main oscillator output electrical characteristics (3.3 V,<br/>NVUSRO[PAD3V5V] = 1)

1. The start-up time is dependent upon crystal characteristics, board leakage, etc. High ESR and excessive capacitive loads can cause long start-up time.

2. Value captured when amplitude reaches 90% of XTAL

3. This value is determined by the crystal manufacturer and board design. For 4 MHz to 40 MHz crystals specified for this oscillator, load capacitors should not exceed these limits.

Table 27.Input clock characteristics

| Sym               | hol | Parameter                |      | Unit |      |      |

|-------------------|-----|--------------------------|------|------|------|------|

| Synn              | 501 | Faiainetei               | Min  | Тур  | Max  | Unit |

| f <sub>OSC</sub>  | SR  | Oscillator frequency     | 4    | —    | 40   | MHz  |

| f <sub>CLK</sub>  | SR  | Frequency in bypass      | _    | —    | 64   | MHz  |

| t <sub>rCLK</sub> | SR  | Rise/fall time in bypass | _    | _    | 1    | ns   |

| t <sub>DC</sub>   | SR  | Duty cycle               | 47.5 | 50   | 52.5 | %    |

## 3.12 FMPLL electrical characteristics

### Table 28. FMPLL electrical characteristics

| Symbol                                           | C Parameter |                                                          | Conditions <sup>(1)</sup> | Va  | Unit |      |

|--------------------------------------------------|-------------|----------------------------------------------------------|---------------------------|-----|------|------|

| Symbol                                           | C           | Farameter                                                | Conditions                | Min | Max  | Onit |

| f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub> | D           | PLL reference frequency range <sup>(2)</sup>             | Crystal reference         | 4   | 40   | MHz  |

| f <sub>PLLIN</sub>                               | D           | Phase detector input frequency range (after pre-divider) | _                         | 4   | 16   | MHz  |

| f <sub>FMPLLOUT</sub>                            | D           | Clock frequency range in normal mode                     | _                         | 16  | 64   | MHz  |

|                     |   |                                                    |                                                     | ,                                                                                         | Va    | lue                     |                       |

|---------------------|---|----------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------------------------|-----------------------|

| Symbol              | С | Pa                                                 | rameter                                             | Conditions <sup>(1)</sup>                                                                 | Min   | Max                     | Unit                  |

| f <sub>FREE</sub>   | Ρ | Free-running frequ                                 | Jency                                               | Measured using clock<br>division—typically /16                                            | 20    | 150                     | MHz                   |

| t <sub>CYC</sub>    | D | System clock period                                | bd                                                  | -                                                                                         | _     | 1 /<br>f <sub>SYS</sub> | ns                    |

| f <sub>LORL</sub>   | D | Loss of reference                                  | frequency window <sup>(3)</sup>                     | Lower limit                                                                               | 1.6   | 3.7                     | MHz                   |

| f <sub>LORH</sub>   | D | Loss of reference                                  |                                                     | Upper limit                                                                               | 24    | 56                      |                       |

| f <sub>SCM</sub>    | D | Self-clocked mode                                  | e frequency <sup>(4),(5)</sup>                      | —                                                                                         | 20    | 150                     | MHz                   |

|                     |   |                                                    | Short-term jitter <sup>(10)</sup>                   | f <sub>SYS</sub> maximum                                                                  | -4    | 4                       | % f <sub>CLKOUT</sub> |

| C <sub>JITTER</sub> | Т | CLKOUT period<br>jitter <sup>(6),(7),(8),(9)</sup> | Long-term jitter<br>(average over 2 ms<br>interval) | f <sub>PLLIN</sub> = 16 MHz<br>(resonator), f <sub>PLLCLK</sub> at<br>64 MHz, 4000 cycles | _     | 10                      | ns                    |

| t <sub>lpll</sub>   | D | PLL lock time <sup>(11), (</sup>                   | 12)                                                 | —                                                                                         | —     | 200                     | μs                    |

| t <sub>dc</sub>     | D | Duty cycle of refer                                | ence                                                | —                                                                                         | 40    | 60                      | %                     |

| f <sub>LCK</sub>    | D | Frequency LOCK                                     | range                                               | —                                                                                         | -6    | 6                       | % f <sub>SYS</sub>    |

| f <sub>UL</sub>     | D | Frequency un-LO                                    | CK range                                            | —                                                                                         | -18   | 18                      | % f <sub>SYS</sub>    |

| f <sub>CS</sub>     | D | Modulation depth                                   |                                                     | Center spread                                                                             | ±0.25 | ±4.0<br>(13)            | % f <sub>SYS</sub>    |

| f <sub>DS</sub>     | D | ]                                                  |                                                     | Down spread                                                                               | -0.5  | -8.0                    |                       |

| f <sub>MOD</sub>    | D | Modulation freque                                  | ncy <sup>(14)</sup>                                 | —                                                                                         | —     | 70                      | kHz                   |

Table 28. FMPLL electrical characteristics (continued)

1.  $V_{DD_LV_CORx}$  = 1.2 V ±10%;  $V_{SS}$  = 0 V;  $T_A$  = -40 to 125 °C, unless otherwise specified

2. Considering operation with PLL not bypassed.

3. "Loss of Reference Frequency" window is the reference frequency range outside of which the PLL is in self clocked mode.

Self clocked mode frequency is the frequency that the PLL operates at when the reference frequency falls outside the f<sub>LOR</sub> window.

f<sub>VCO</sub> self clock range is 20–150 MHz. f<sub>SCM</sub> represents f<sub>SYS</sub> after PLL output divider (ERFD) of 2 through 16 in enhanced mode.

6. This value is determined by the crystal manufacturer and board design.

7. Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>SYS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DD\_LV\_COR0</sub> and V<sub>SS\_LV\_COR0</sub> and variation in crystal oscillator frequency increase the C<sub>JITTER</sub> percentage for a given interval.

8. Proper PC board layout procedures must be followed to achieve specifications.

Values are obtained with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

10. Short term jitter is measured on the clock rising edge at cycle n and cycle n+4.

11. This value is determined by the crystal manufacturer and board design. For 4 MHz to 20 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

12. This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

13. This value is true when operating at frequencies above 60 MHz, otherwise f<sub>CS</sub> is 2% (above 64 MHz).

14. Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

## 3.15.3 Start-up/Switch-off timings

| Symbol                  |        | с | Parameter                                        | Conditions <sup>(1)</sup> | Value |     |     | Unit |

|-------------------------|--------|---|--------------------------------------------------|---------------------------|-------|-----|-----|------|

| Symbol                  |        | 0 | Falameter                                        | Conditions                | Min   | Тур | Max | Unit |

| T <sub>FLARSTEXIT</sub> | с<br>с | Т | Delay for Flash module to exit reset mode        | Code flash<br>memory      | _     | _   | 125 |      |

|                         |        | Т |                                                  | Data flash memory         |       |     | 125 |      |

| T <sub>FLALPEXIT</sub>  | C<br>C | D | Delay for Flash module to exit low-power mode    | Code flash<br>memory      | _     |     | 0.5 |      |

| T <sub>FLAPDEXIT</sub>  | C<br>C | - | T Delay for Flash module to exit power-down mode | Code flash<br>memory      | _     |     | 30  | μs   |

|                         |        |   |                                                  | Data flash memory         |       |     | 30  |      |

| T <sub>FLALPENTRY</sub> | C<br>C | D | Delay for Flash module to enter low-power mode   | Code flash<br>memory      |       | _   | 0.5 |      |

#### Table 35. Start-up time/Switch-off time

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

# **3.16 AC** specifications

### 3.16.1 Pad AC specifications

### Table 36. Output pin transition times

| Symbol          |    | с  | Parameter                                                              | Conditions <sup>(1)</sup> |                                                                                        | Value                                            |                         |                   | Unit |    |    |

|-----------------|----|----|------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------|-------------------|------|----|----|

|                 |    |    | Falameter                                                              |                           |                                                                                        | Min                                              | Тур                     | Max               |      |    |    |

|                 |    | D  | Output transition time output pin <sup>(2)</sup><br>SLOW configuration | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0<br>$V_{DD} = 3.3 V \pm 10\%,$<br>PAD3V5V = 1 | —                                                | —                       | 50                | ns   |    |    |

|                 |    | Т  |                                                                        | C <sub>L</sub> = 50 pF    |                                                                                        | _                                                | _                       | 100               |      |    |    |

| +               | сс | D  |                                                                        | C <sub>L</sub> = 100 pF   |                                                                                        | _                                                | _                       | 125               |      |    |    |

| t <sub>tr</sub> |    | D  |                                                                        | C <sub>L</sub> = 25 pF    |                                                                                        | _                                                | _                       | 40                |      |    |    |

|                 |    | Т  |                                                                        | C <sub>L</sub> = 50 pF    |                                                                                        |                                                  |                         | 50                |      |    |    |

|                 |    | D  |                                                                        | C <sub>L</sub> = 100 pF   |                                                                                        | _                                                | _                       | 75                |      |    |    |

|                 | -  | D  |                                                                        | C <sub>L</sub> = 25 pF    | $V_{DD} = 5.0 V \pm 10\%$ ,<br>PAD3V5V = 0                                             | _                                                | _                       | 10                | -    |    |    |

|                 |    | Т  |                                                                        | C <sub>L</sub> = 50 pF    |                                                                                        |                                                  |                         | 20                |      |    |    |

| +               |    | сс | 00                                                                     | 00                        | D                                                                                      | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 100 pF | SIUL.PCRx.SRC = 1 | _    | _  | 40 |

| t <sub>tr</sub> |    | D  | MEDIUM configuration                                                   | C <sub>L</sub> = 25 pF    | V <sub>DD</sub> = 3.3 V ± 10%,                                                         | _                                                | _                       | 12                | ns   |    |    |

|                 |    | Т  |                                                                        | Т                         |                                                                                        | C <sub>L</sub> = 50 pF                           | PAD3V5V = 1             | _                 | —    | 25 |    |

|                 |    | D  |                                                                        | C <sub>L</sub> = 100 pF   | SIUL.PCRx.SRC = 1                                                                      |                                                  |                         | 40                |      |    |    |

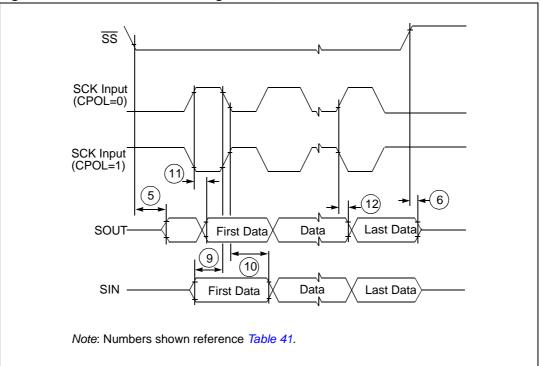

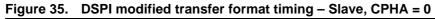

Figure 32. DSPI classic SPI timing – Slave, CPHA = 1

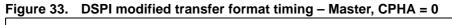

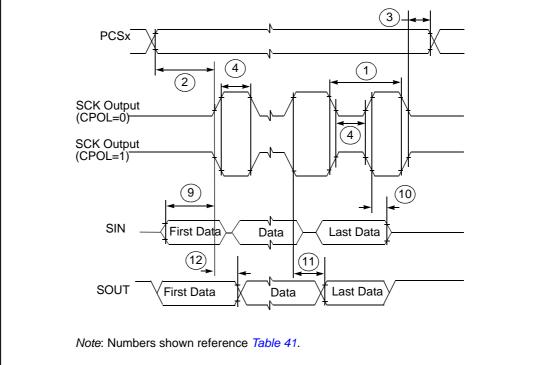

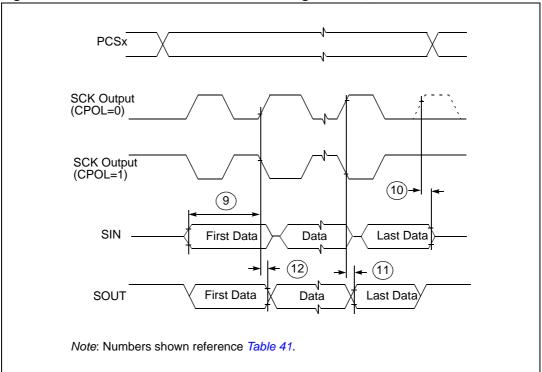

Figure 34. DSPI modified transfer format timing – Master, CPHA = 1

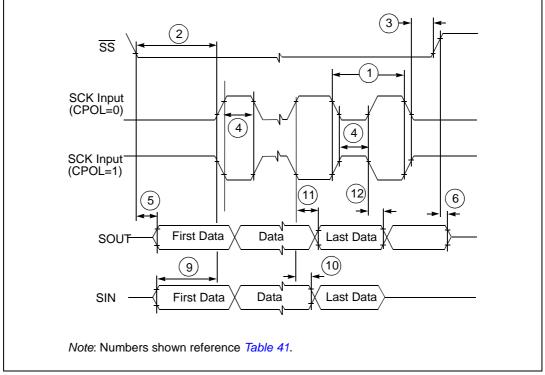

Figure 36. DSPI modified transfer format timing – Slave, CPHA = 1

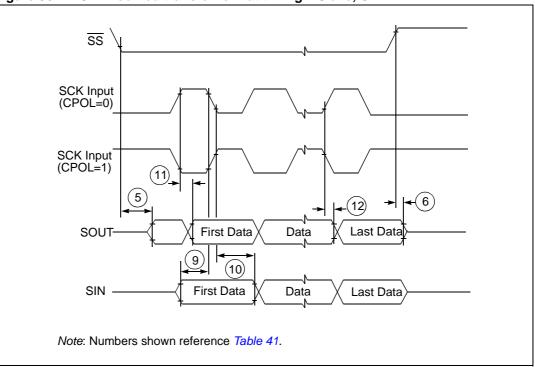

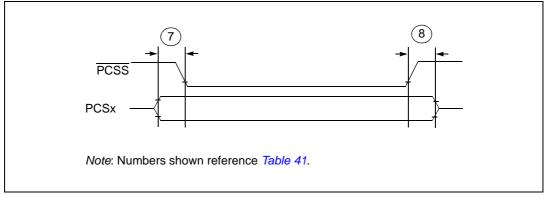

### Figure 37. DSPI PCS Strobe (PCSS) timing

# 4 Package characteristics

# 4.1 ECOPACK<sup>®</sup>

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <u>www.st.com</u>. ECOPACK<sup>®</sup> is an ST trademark.

|             | 1                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23-Dec-2010 | 3<br>(continued) | Updated "Main oscillator electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)"<br>table<br>Updated "Main oscillator electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)"<br>table<br>"Input clock characteristics" table: updated $f_{CLK}$ max value<br>"PLLMRFM electrical specifications ( $V_{DDPLL}$ = 1.08 V to 1.32 V, $V_{SS}$ = $V_{SSPLL}$ = 0 V,<br>$T_A = T_L$ to $T_H$ )" table:<br>- Updated supply voltage range for $V_{DDPLL}$ in the table title<br>- Updated f <sub>SCM</sub> max value<br>- Updated f <sub>MOD</sub> max value<br>- Updated f <sub>MOD</sub> max value<br>Updated "16 MHz RC oscillator electrical characteristics" table<br>Updated "ADC conversion characteristics" table<br>"Program and erase specifications" table:<br>- $T_{wprogram}$ : updated initial max and max values<br>- $T_{BKPRO}$ 64 KB: updated initial max and max values<br>- added information about "erase time" for Data Flash<br>"Flash module life" table:<br>- P/E, 32 KB: added typ value<br>Replaced "Pad AC specifications (5.0 V, NVUSRO[PAD3V5V] = 0)" and "Pad AC<br>specifications (3.3 V, INVUSRO[PAD3V5V] = 1)" tables with "Output pin transition<br>times" table<br>"JTAG pin AC electrical characteristics" table:<br>- $t_{TOOV}$ : updated min value and removed max value<br>"Nexus debug port timing" table: removed the rows "t <sub>MCYC</sub> ", "t <sub>MDOV</sub> ", "t <sub>MSEOV</sub> ", and<br>"t <sub>EVTOV</sub> "<br>Updated "External interrupt timing (IRQ pin)" table<br>Updated "DSPI timing" table<br>Updated "DSPI timing" table |

### Table 45. Document revision history (continued)