Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| _                          |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Details                    |                                                                          |

| Product Status             | Obsolete                                                                 |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 20K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p40l1befby |

Table 2. SPC560P34/SPC560P40 device comparison (continued)

|                  | Feature                             | SPC560P34<br>Full-featured                  | SPC560P40<br>Full-featured                  |

|------------------|-------------------------------------|---------------------------------------------|---------------------------------------------|

| eDMA (enhance    | ed direct memory access) channels   | 1                                           | 6                                           |

| FlexCAN (cont    | roller area network)                | 1 <sup>(1)</sup>                            | 2 <sup>(1),(2)</sup>                        |

| Safety port      |                                     | No                                          | Yes (via second FlexCAN module)             |

| FCU (fault colle | ection unit)                        | Ye                                          | es                                          |

| CTU (cross trig  | gering unit)                        | Yes                                         | Yes                                         |

| eTimer           |                                     | 1 (16-bit, 6                                | channels)                                   |

| FlexPWM (puls    | se-width modulation) channels       | 8<br>(capture capabity not<br>supported)    | 8<br>(capture capability not<br>supported)  |

| Analog-to-digita | al converter (ADC)                  | 1 (10-bit, 1                                | 6 channels)                                 |

| LINFlex          |                                     | 2<br>(1 × Master/Slave,<br>1 × Master only) | 2<br>(1 × Master/Slave,<br>1 × Master only) |

| DSPI (deserial   | serial peripheral interface)        | 2                                           | 3                                           |

| CRC (cyclic red  | dundancy check) unit                | Y                                           | es                                          |

| Junction tempe   | erature sensor                      | N                                           | lo                                          |

| JTAG controlle   | r                                   | Ye                                          | es                                          |

| Nexus port con   | ntroller (NPC)                      | Yes (Nexu                                   | ıs Class 1)                                 |

|                  | Digital power supply <sup>(3)</sup> | 3.3 V or 5 V single supp                    | ly with external transistor                 |

| Supply           | Analog power supply                 | 3.3 V                                       | or 5 V                                      |

| Supply           | Internal RC oscillator              | 161                                         | MHz                                         |

|                  | External crystal oscillator         | 4–40                                        | MHz                                         |

| Packages         |                                     |                                             | P100                                        |

| Temperature      | Standard ambient temperature        | -40 to                                      | 125 °C                                      |

<sup>1.</sup> Each FlexCAN module has 32 message buffers.

SPC560P34/SPC560P40 is available in two configurations having different features: Full-featured and airbag. *Table 3* shows the main differences between the two versions of the SPC560P40 MCU.

8/103 Doc ID 16100 Rev 7

<sup>2.</sup> One FlexCAN module can act as a safety port with a bit rate as high as 8 Mbit/s at 64 MHz.

<sup>3.</sup> The different supply voltages vary according to the part number ordered.

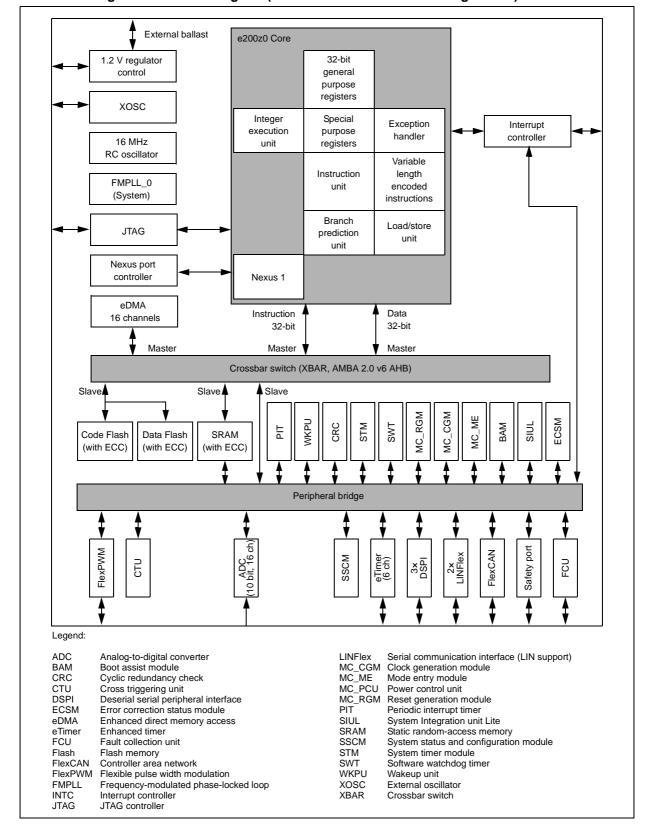

Figure 1. Block diagram (SPC560P40 full-featured configuration)

**577**

Table 4. SPC560P34/SPC560P40 series block summary

| Block                                             | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                 | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                          | Block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                          |

| Clock generation module (MC_CGM)                  | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Controller area network (FlexCAN)                 | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Cross triggering unit (CTU)                       | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Crossbar switch (XBAR)                            | Supports simultaneous connections between two master ports and three slave ports; supports a 32-bit address bus width and a 32-bit data bus width                                                                                                                                                                 |

| Cyclic redundancy check (CRC)                     | CRC checksum generator                                                                                                                                                                                                                                                                                            |

| Deserial serial peripheral interface (DSPI)       | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Enhanced direct memory access (eDMA)              | Performs complex data transfers with minimal intervention from a host processor via "n" programmable channels                                                                                                                                                                                                     |

| Enhanced timer (eTimer)                           | Provides enhanced programmable up/down modulo counting                                                                                                                                                                                                                                                            |

| Error correction status module (ECSM)             | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| External oscillator (XOSC)                        | Provides an output clock used as input reference for FMPLL_0 or as reference clock for specific modules depending on system needs                                                                                                                                                                                 |

| Fault collection unit (FCU)                       | Provides functional safety to the device                                                                                                                                                                                                                                                                          |

| Flash memory                                      | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| Frequency-modulated phase-<br>locked loop (FMPLL) | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Interrupt controller (INTC)                       | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                   | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Mode entry module (MC_ME)                         | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Periodic interrupt timer (PIT)                    | Produces periodic interrupts and triggers                                                                                                                                                                                                                                                                         |

| Peripheral bridge (PBRIDGE)                       | Is the interface between the system bus and on-chip peripherals                                                                                                                                                                                                                                                   |

| Power control unit (MC_PCU)                       | Reduces the overall power consumption by disconnecting parts of the device from the power supply via a power switching device; device components are grouped into sections called "power domains" which are controlled by the PCU                                                                                 |

The crossbar provides the following features:

- 3 master ports:

- e200z0 core complex instruction port

- e200z0 core complex Load/Store Data port

- eDMA

- 3 slave ports:

- Flash memory (Code and Data)

- SRAM

- Peripheral bridge

- 32-bit internal address, 32-bit internal data paths

- Fixed Priority Arbitration based on Port Master

- Temporary dynamic priority elevation of masters

## 1.5.3 Enhanced direct memory access (eDMA)

The enhanced direct memory access (eDMA) controller is a second-generation module capable of performing complex data movements via 16 programmable channels, with minimal intervention from the host processor. The hardware micro architecture includes a DMA engine which performs source and destination address calculations, and the actual data movement operations, along with an SRAM-based memory containing the transfer control descriptors (TCD) for the channels.

The eDMA module provides the following features:

- 16 channels support independent 8-, 16- or 32-bit single value or block transfers

- Supports variable-sized queues and circular queues

- Source and destination address registers are independently configured to either postincrement or to remain constant

- Each transfer is initiated by a peripheral, CPU, or eDMA channel request

- Each eDMA channel can optionally send an interrupt request to the CPU on completion of a single value or block transfer

- DMA transfers possible between system memories, DSPIs, ADC, FlexPWM, eTimer and CTU

- Programmable DMA channel multiplexer allows assignment of any DMA source to any available DMA channel with as many as 30 request sources

- eDMA abort operation through software

### 1.5.4 Flash memory

The SPC560P34/SPC560P40 provides 320 KB of programmable, non-volatile, flash memory. The non-volatile memory (NVM) can be used for instruction and/or data storage. The flash memory module is interfaced to the system bus by a dedicated flash memory controller. It supports a 32-bit data bus width at the system bus port, and a 128-bit read data interface to flash memory. The module contains four 128-bit wide prefetch buffers. Prefetch buffer hits allow no-wait responses. Normal flash memory array accesses are registered and are forwarded to the system bus on the following cycle, incurring two wait-states.

14/103 Doc ID 16100 Rev 7

### 1.5.8 System clocks and clock generation

The following list summarizes the system clock and clock generation on the SPC560P34/SPC560P40:

- Lock detect circuitry continuously monitors lock status

- Loss of clock (LOC) detection for PLL outputs

- Programmable output clock divider (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and eTimer module running at the same frequency as the e200z0h core

- Internal 16 MHz RC oscillator for rapid start-up and safe mode: supports frequency trimming by user application

## 1.5.9 Frequency-modulated phase-locked loop (FMPLL)

The FMPLL allows the user to generate high speed system clocks from a 4–40 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock. The PLL multiplication factor, output clock divider ratio are all software configurable.

The FMPLL has the following major features:

- Input clock frequency: 4–40 MHz

- Maximum output frequency: 64 MHz

- Voltage controlled oscillator (VCO)—frequency 256–512 MHz

- Reduced frequency divider (RFD) for reduced frequency operation without forcing the FMPLL to relock

- Frequency-modulated PLL

- Modulation enabled/disabled through software

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency): programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

### 1.5.10 Main oscillator

The main oscillator provides these features:

- Input frequency range: 4–40 MHz

- Crystal input mode or oscillator input mode

- PLL reference

### 1.5.11 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

### 1.5.23 Deserial serial peripheral interface (DSPI)

The deserial serial peripheral interface (DSPI) module provides a synchronous serial interface for communication between the SPC560P34/SPC560P40 MCU and external devices.

The DSPI modules provide these features:

- Full duplex, synchronous transfers

- Master or slave operation

- Programmable master bit rates

- Programmable clock polarity and phase

- End-of-transmission interrupt flag

- Programmable transfer baud rate

- Programmable data frames from 4 to 16 bits

- Up to 8 chip select lines available:

- 8 on DSPI\_0

- 4 each on DSPI\_1 and DSPI\_2

- 8 clock and transfer attributes registers

- Chip select strobe available as alternate function on one of the chip select pins for deglitching

- FIFOs for buffering up to 4 transfers on the transmit and receive side

- Queueing operation possible through use of the I/O processor or eDMA

- General purpose I/O functionality on pins when not used for SPI

## 1.5.24 Pulse width modulator (FlexPWM)

The pulse width modulator module (PWM) contains four PWM submodules each of which is set up to control a single half-bridge power stage. There are also three fault channels.

This PWM is capable of controlling most motor types: AC induction motors (ACIM), permanent magnet AC motors (PMAC), both brushless (BLDC) and brush DC motors (BDC), switched (SRM) and variable reluctance motors (VRM), and stepper motors.

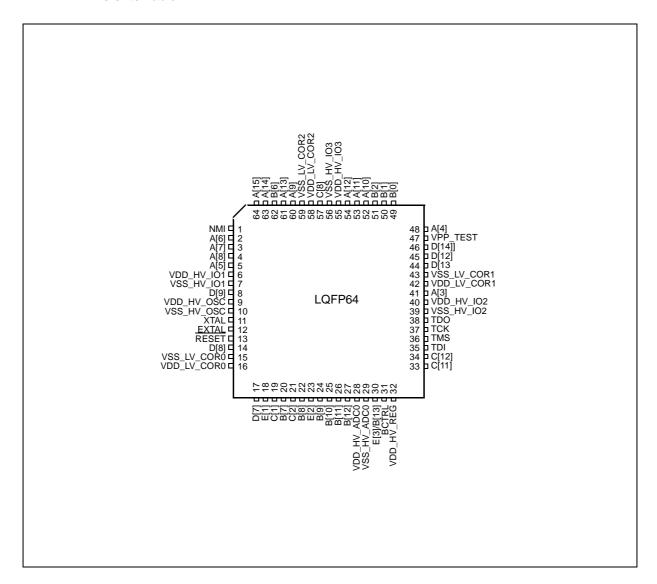

# 2 Package pinouts and signal descriptions

## 2.1 Package pinouts

The LQFP pinouts are shown in the following figures. For pin signal descriptions, please refer to *Table 7*.

Figure 2. 64-pin LQFP pinout – Full featured configuration (top view)

Table 7. Pin muxing (continued)

| Port  | PCR        | Alternate                   | Formations    | D: I 1(3)                 | I/O                           | Pad s   | peed <sup>(5)</sup> | Pin     |         |         |      |   |   |   |      |        |   |    |

|-------|------------|-----------------------------|---------------|---------------------------|-------------------------------|---------|---------------------|---------|---------|---------|------|---|---|---|------|--------|---|----|

| pin   | register   | function <sup>(1),(2)</sup> | Functions     | Peripheral <sup>(3)</sup> | direc-<br>tion <sup>(4)</sup> | SRC = 0 | SRC = 1             | 64-pin  | 100-pin |         |      |   |   |   |      |        |   |    |

|       |            | ALT0<br>ALT1                | GPIO[49]      | SIUL<br>—                 | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| D[1]  | PCR[49]    | ALT2                        |               | _                         | _                             | Slow    | Medium              | _       | 3       |         |      |   |   |   |      |        |   |    |

|       |            | ALT3                        | EXT_TRG       | CTU_0                     | 0                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT0                        | GPIO[50]      | SIUL                      | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| D[2]  | PCR[50]    | ALT1                        | _             | _                         | _                             | Slow    | Medium              |         | 97      |         |      |   |   |   |      |        |   |    |

| رکال  | r Civ[30]  | ALT2                        |               | _                         | _                             | Siow    | Mediaiii            |         | 31      |         |      |   |   |   |      |        |   |    |

|       |            | ALT3                        | X[3]          | FlexPWM_0                 | 0                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT0                        | GPIO[51]      | SIUL                      | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| D[3]  | PCR[51]    | ALT1                        |               | _                         | _                             | Slow    | Medium              | _       | 89      |         |      |   |   |   |      |        |   |    |

| ردا   | . 0.4[0.1] | ALT2                        |               | _                         | _                             | 0.011   | Wodiam              |         | 00      |         |      |   |   |   |      |        |   |    |

|       |            | ALT3                        | A[3]          | FlexPWM_0                 | 0                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT0                        | GPIO[52]      | SIUL                      | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| D[4]  | PCR[52]    | ALT1                        |               | _                         | _                             | Slow    | Medium              | _       | 90      |         |      |   |   |   |      |        |   |    |

| ر. ا  |            | ALT2                        | _             | _                         | _                             | Cion    | Wiodiaiii           |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT3                        | B[3]          | FlexPWM_0                 | 0                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       | PCR[53]    | ALT0                        | GPIO[53]      | SIUL                      | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| DIEI  |            | ALT1                        | CS3           | DSPI_0                    | 0                             | Clave   | Medium              |         | 22      |         |      |   |   |   |      |        |   |    |

| D[5]  |            | ALT2                        | F[0]          | FCU_0                     | 0                             | Slow    | Medium              | _       | 22      |         |      |   |   |   |      |        |   |    |

|       |            | ALT3                        | _             | _                         | _                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT0                        | GPIO[54]      | SIUL                      | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT1                        | CS2           | DSPI_0                    | 0                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| D[6]  | PCR[54]    | PCR[54]                     | PCR[54]       | PCR[54]                   | PCR[54]                       | PCR[54] | PCR[54]             | PCR[54] | PCR[54] | PCR[54] | ALT2 | _ | _ | _ | Slow | Medium | _ | 23 |

|       |            |                             |               |                           |                               |         |                     |         |         |         | ALT3 | _ | _ | _ |      |        |   |    |

|       |            | _                           | FAULT[1]      | FlexPWM_0                 | I                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT0                        | GPIO[55]      | SIUL                      | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| D[7]  | PCR[55]    | ALT1                        | CS3           | DSPI_1                    | 0                             | Slow    | Medium              | 17      | 26      |         |      |   |   |   |      |        |   |    |

| ر. ا  | . 0.1(00)  | ALT2                        | F[1]          | FCU_0                     | 0                             | 0.011   | Woodani             |         | 20      |         |      |   |   |   |      |        |   |    |

|       |            | ALT3                        | CS4           | DSPI_0                    | 0                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT0                        | GPIO[56]      | SIUL                      | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| D[8]  | PCR[56]    | ALT1                        | CS2           | DSPI_1                    | 0                             | Slow    | Medium              | 14      | 21      |         |      |   |   |   |      |        |   |    |

| D[0]  | r Civ[30]  | ALT2                        |               | _                         | _                             | Siow    | Mediaiii            | 14      | 21      |         |      |   |   |   |      |        |   |    |

|       |            | ALT3                        | CS5           | DSPI_0                    | 0                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT0                        | GPIO[57]      | SIUL                      | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| Dioi  | DCD[E7]    | ALT1                        | X[0]          | FlexPWM_0                 | 0                             | Class   | Modium              | 0       | 15      |         |      |   |   |   |      |        |   |    |

| D[9]  | PCR[57]    | ALT2                        | TXD           | LIN_1                     | 0                             | Slow    | Medium              | 8       | 15      |         |      |   |   |   |      |        |   |    |

|       |            | ALT3                        |               |                           | _                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

|       |            | ALT0                        | GPIO[58] SIUL |                           | I/O                           |         |                     |         |         |         |      |   |   |   |      |        |   |    |

| D[10] | DCD[E0]    | ALT1                        | A[0]          | FlexPWM_0                 | 0                             | Slow    | Medium              | _       | 53      |         |      |   |   |   |      |        |   |    |

| D[10] | PCR[58]    | ALT2                        | _             | _                         | _                             | SiOW    | wealuifi            | _       | 55      |         |      |   |   |   |      |        |   |    |

|       |            | ALT3                        | _             | _                         | _                             |         |                     |         |         |         |      |   |   |   |      |        |   |    |

Value **Symbol Conditions** Unit **Parameter** Max<sup>(2)</sup> Min Absolute sum of all input currents 50 -50 mΑ I<sub>INJSUM</sub> R during overload condition S Storage temperature -55 150 °C  $T_{STG}$ R S °C Junction temperature under bias -40 150  $T_{\rm J}$ R

Table 9. Absolute maximum ratings<sup>(1)</sup> (continued)

- Functional operating conditions are given in the DC electrical characteristics. Absolute maximum ratings are stress ratings

only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device

reliability or cause permanent damage to the device.

- 2. Absolute maximum voltages are currently maximum burn-in voltages.

- 3. The difference between each couple of voltage supplies must be less than 300 mV,  $|V_{DD\ HV\ IOV} V_{DD\ HV\ IOX}| < 300$  mV.

- 4. Guaranteed by device validation.

- 5. Minimum value of  $TV_{DD}$  must be guaranteed until  $V_{DD\_HV\_REG}$  reaches 2.6 V (maximum value of  $V_{PORH}$ )

- 6. Only when  $V_{DD\_HV\_IOx} < 5.2 \text{ V}$

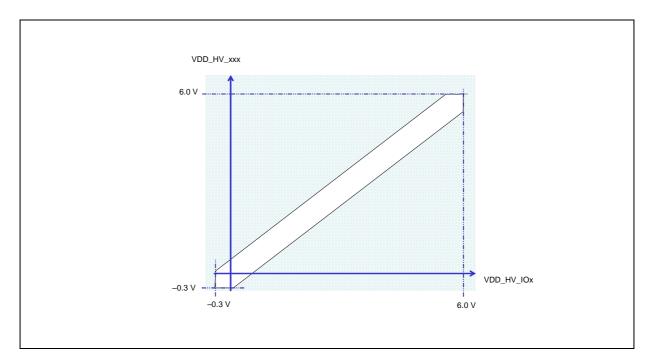

Figure 6 shows the constraints of the different power supplies.

Figure 6. Power supplies constraints ( $-0.3 \text{ V} \le \text{V}_{DD \text{ HV IOx}} \le 6.0 \text{ V}$ )

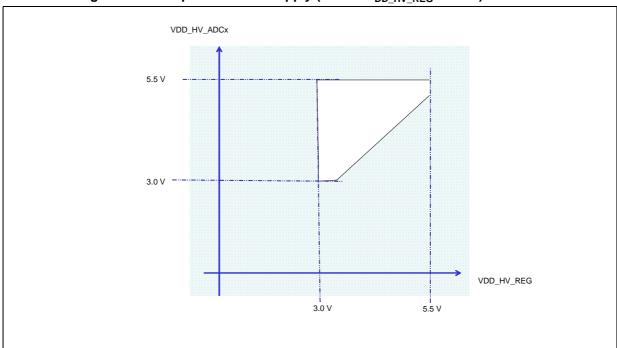

The SPC560P34/SPC560P40 supply architecture allows the ADC supply to be managed independently from the standard  $V_{DD\_HV}$  supply. *Figure 7* shows the constraints of the ADC power supply.

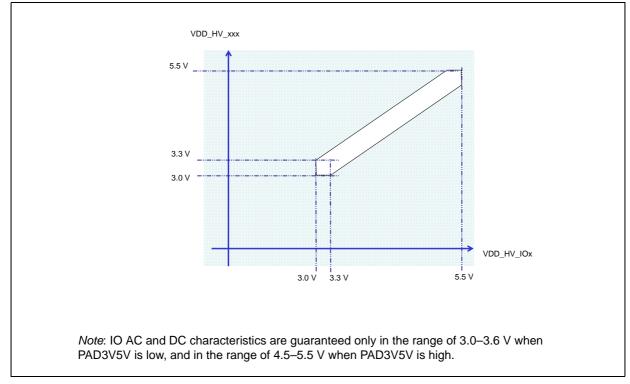

Figure 8. Power supplies constraints (3.0 V  $\leq$  V<sub>DD\_HV\_IOx</sub>  $\leq$  5.5 V)

The SPC560P34/SPC560P40 supply architecture allows the ADC supply to be managed independently from the standard  $V_{DD\_HV}$  supply. *Figure 9* shows the constraints of the ADC power supply.

Figure 9. Independent ADC supply (3.0 V  $\leq$  V<sub>DD HV REG</sub>  $\leq$  5.5 V)

### 3.8.2 Voltage monitor electrical characteristics

The device implements a power on reset module to ensure correct power-up initialization, as well as three low voltage detectors to monitor the  $V_{DD}$  and the  $V_{DD\_LV}$  voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply

- $\bullet$  LVDHV5 monitors V<sub>DD</sub> when application uses device in the 5.0 V  $\pm$  10% range

- LVDLVCOR monitors low voltage digital power domain

Table 17. Low voltage monitor electrical characteristics

| Cumbal                   | С | Baramatar                                     | Conditions <sup>(1)</sup> | Value |       | Unit |

|--------------------------|---|-----------------------------------------------|---------------------------|-------|-------|------|

| Symbol                   |   | Parameter                                     | Conditions                | Min   | Max   | Unit |

| V <sub>PORH</sub>        | Т | Power-on reset threshold                      | _                         | 1.5   | 2.7   | V    |

| V <sub>PORUP</sub>       | Р | Supply for functional POR module              | T <sub>A</sub> = 25 °C    | 1.0   | _     | V    |

| V <sub>REGLVDMOK_H</sub> | Р | Regulator low voltage detector high threshold | _                         | _     | 2.95  | V    |

| V <sub>REGLVDMOK_L</sub> | Р | Regulator low voltage detector low threshold  | _                         | 2.6   | _     | V    |

| V <sub>FLLVDMOK_H</sub>  | Р | Flash low voltage detector high threshold     | _                         | _     | 2.95  | V    |

| V <sub>FLLVDMOK_L</sub>  | Р | Flash low voltage detector low threshold      | _                         | 2.6   | _     | V    |

| V <sub>IOLVDMOK_H</sub>  | Р | I/O low voltage detector high threshold       | _                         | _     | 2.95  | V    |

| V <sub>IOLVDMOK_L</sub>  | Р | I/O low voltage detector low threshold        | _                         | 2.6   | _     | V    |

| V <sub>IOLVDM5OK_H</sub> | Р | I/O 5 V low voltage detector high threshold   | _                         | _     | 4.4   | V    |

| V <sub>IOLVDM5OK_L</sub> | Р | I/O 5 V low voltage detector low threshold    | _                         | 3.8   | _     | V    |

| V <sub>MLVDDOK_H</sub>   | Р | Digital supply low voltage detector high      | _                         | _     | 1.145 | V    |

| V <sub>MLVDDOK_L</sub>   | Р | Digital supply low voltage detector low       | _                         | 1.08  | —     | V    |

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 °C to  $T_{A~MAX}$ , unless otherwise specified

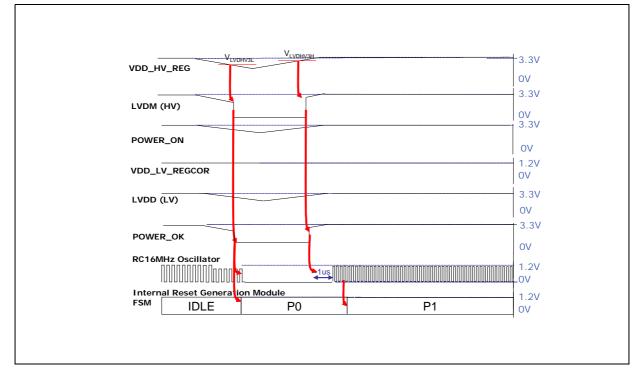

## 3.9 Power up/down sequencing

To prevent an overstress event or a malfunction within and outside the device, the SPC560P34/SPC560P40 implements the following sequence to ensure each module is started only when all conditions for switching it ON are available:

- A POWER\_ON module working on voltage regulator supply controls the correct startup of the regulator. This is a key module ensuring safe configuration for all voltage regulator functionality when supply is below 1.5 V. Associated POWER\_ON (or POR) signal is active low.

- Several low voltage detectors, working on voltage regulator supply monitor the voltage

of the critical modules (voltage regulator, I/Os, flash memory and low voltage domain).

LVDs are gated low when POWER ON is active.

- A POWER\_OK signal is generated when all critical supplies monitored by the LVD are available. This signal is active high and released to all modules including I/Os, flash

Figure 13. Brown-out typical sequence

## 3.10 DC electrical characteristics

## 3.10.1 NVUSRO register

Portions of the device configuration, such as high voltage supply and watchdog enable/disable after reset are controlled via bit values in the non-volatile user options (NVUSRO) register.

For a detailed description of the NVUSRO register, please refer to the device reference manual.

### NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. *Table 18* shows how NVUSRO[PAD3V5V] controls the device configuration.

Table 18. PAD3V5V field description

| Value <sup>(1)</sup> | Description                  |

|----------------------|------------------------------|

| 0                    | High voltage supply is 5.0 V |

| 1                    | High voltage supply is 3.3 V |

1. Default manufacturing value before flash initialization is '1' (3.3 V).

## 3.10.5 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in *Table 23*.

Table 23. I/O supply segment

| Dookogo | Supply segment |             |             |             |             |  |  |  |

|---------|----------------|-------------|-------------|-------------|-------------|--|--|--|

| Package | 1              | 2           | 3           | 4           | 5           |  |  |  |

| LQFP100 | pin15-pin26    | pin27-pin46 | pin51-pin61 | pin64-pin86 | pin89–pin10 |  |  |  |

| LQFP64  | pin8–pin17     | pin18-pin30 | pin33-pin38 | pin41-pin54 | pin57–pin5  |  |  |  |

Table 24. I/O consumption

| Symbol                             |    | С | Parameter                                       | Conditions <sup>(1)</sup>             |                                                   | Value                                     |                                                   | )                             | Unit                                              |               |            |                                                   |   |   |    |

|------------------------------------|----|---|-------------------------------------------------|---------------------------------------|---------------------------------------------------|-------------------------------------------|---------------------------------------------------|-------------------------------|---------------------------------------------------|---------------|------------|---------------------------------------------------|---|---|----|

|                                    |    |   | Farameter                                       | Condi                                 | Conditions                                        |                                           | Тур                                               | Max                           | Oilit                                             |               |            |                                                   |   |   |    |

| I <sub>SWTSLW</sub> <sup>(2)</sup> | СС | D | Dynamic I/O current for SLOW                    | C <sub>I</sub> = 25 pF                | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _                                         | _                                                 | 20                            | mA                                                |               |            |                                                   |   |   |    |

| 'SWTSLW` '                         | C  |   | configuration                                   | OL = 25 μΓ                            | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1     | _                                         | _                                                 | 16                            | IIIA                                              |               |            |                                                   |   |   |    |

| I <sub>SWTMED</sub> <sup>(2)</sup> | 00 | D | Dynamic I/O current for MEDIUM C <sub>1</sub> = | C <sub>1</sub> = 25 pF                | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _                                         |                                                   | 29                            | mA                                                |               |            |                                                   |   |   |    |

| SWTMED                             | С  |   | configuration                                   | Ο[ – 25 μι                            | $V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 | _                                         | _                                                 | 17                            | IIIA                                              |               |            |                                                   |   |   |    |

| (2)                                | C  | С | С                                               | D                                     | Dynamic I/O current for FAST                      | C <sub>1</sub> = 25 pF                    | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _                             | _                                                 | 110           | mA         |                                                   |   |   |    |

| I <sub>SWTFST</sub> <sup>(2)</sup> |    |   | D                                               |                                       | ט                                                 |                                           |                                                   |                               |                                                   | configuration | O[ - 20 pi | $V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 | _ | _ | 50 |

|                                    |    |   |                                                 | C <sub>L</sub> = 25 pF, 2 MHz         |                                                   | _                                         | _                                                 | 2.3                           |                                                   |               |            |                                                   |   |   |    |

|                                    | С  |   |                                                 |                                       |                                                   |                                           |                                                   | C <sub>L</sub> = 25 pF, 4 MHz | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _             | _          | 3.2                                               |   |   |    |

| l                                  |    | D | Root medium square I/O current for SLOW         | C <sub>L</sub> = 100 pF, 2 MHz        |                                                   | _                                         | _                                                 | 6.6                           | mA                                                |               |            |                                                   |   |   |    |

| I <sub>RMSSLW</sub>                | С  | ט | ט                                               | configuration                         | C <sub>L</sub> = 25 pF, 2 MHz                     |                                           | _                                                 | _                             | 1.6                                               | mA            |            |                                                   |   |   |    |

|                                    |    |   |                                                 | C <sub>L</sub> = 25 pF, 4 MHz         | $V_{DD} = 3.3 V \pm 10\%,$<br>PAD3V5V = 1         | _                                         | _                                                 | 2.3                           |                                                   |               |            |                                                   |   |   |    |

|                                    |    |   |                                                 | C <sub>L</sub> = 100 pF, 2 MHz        |                                                   | _                                         | _                                                 | 4.7                           |                                                   |               |            |                                                   |   |   |    |

|                                    |    |   |                                                 | $C_L = 25 \text{ pF}, 13 \text{ MHz}$ | .,                                                | _                                         | _                                                 | 6.6                           |                                                   |               |            |                                                   |   |   |    |

|                                    |    |   | Root medium square                              | C <sub>L</sub> = 25 pF, 40 MHz        | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _                                         | _                                                 | 13.4                          | mA                                                |               |            |                                                   |   |   |    |

|                                    | С  | D | I/O current for                                 | C <sub>L</sub> = 100 pF, 13 MHz       |                                                   | _                                         | _                                                 | 18.3                          |                                                   |               |            |                                                   |   |   |    |

| I <sub>RMSMED</sub>                | С  | С |                                                 | MEDIUM configuration                  | $C_L = 25 \text{ pF}, 13 \text{ MHz}$             | 0.01/ . 402/                              | _                                                 | _                             | 5                                                 | mA            |            |                                                   |   |   |    |

|                                    |    |   |                                                 |                                       | $C_L = 25 \text{ pF}, 40 \text{ MHz}$             | $V_{DD} = 3.3 V \pm 10\%,$<br>PAD3V5V = 1 | _                                                 | _                             | 8.5                                               |               |            |                                                   |   |   |    |

|                                    |    |   |                                                 | C <sub>L</sub> = 100 pF, 13 MHz       |                                                   | _                                         | _                                                 | 11                            |                                                   |               |            |                                                   |   |   |    |

In particular two different transient periods can be distinguished:

A first and quick charge transfer from the internal capacitance C<sub>P1</sub> and C<sub>P2</sub> to the sampling capacitance C<sub>S</sub> occurs (C<sub>S</sub> is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which C<sub>P2</sub> is reported in parallel to C<sub>P1</sub> (call C<sub>P</sub> = C<sub>P1</sub> + C<sub>P2</sub>), the two capacitances C<sub>P</sub> and C<sub>S</sub> are in series, and the time constant is

### **Equation 5**

$$\tau_1 = (R_{SW} + R_{AD}) \bullet \frac{C_P \bullet C_S}{C_P + C_S}$$

Equation 5 can again be simplified considering only  $C_S$  as an additional worst condition. In reality, the transient is faster, but the A/D converter circuitry has been designed to be robust also in the very worst case: the sampling time  $T_S$  is always much longer than the internal time constant:

#### **Equation 6**

$$\tau_1 < (R_{SW} + R_{AD}) \cdot C_S \ll T_S$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed also on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to *Equation 7*:

#### **Equation 7**

$$V_{A1} \bullet (C_S + C_{P1} + C_{P2}) = V_A \bullet (C_{P1} + C_{P2})$$

A second charge transfer involves also C<sub>F</sub> (that is typically bigger than the on-chip capacitance) through the resistance R<sub>L</sub>: again considering the worst case in which C<sub>P2</sub> and C<sub>S</sub> were in parallel to C<sub>P1</sub> (since the time constant in reality would be faster), the time constant is:

#### **Equation 8**

$$\tau_2 < R_L \bullet (C_S + C_{P1} + C_{P2})$$

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraints on  $R_1$  sizing is obtained:

#### **Equation 9**

$$8.5 \bullet \tau_2 = 8.5 \bullet R_L \bullet (C_S + C_{P1} + C_{P2}) < T_S$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . Equation 10 must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

### **Equation 10**

$${\rm V}_{\rm A2} \bullet ({\rm C}_{\rm S} + {\rm C}_{\rm P1} + {\rm C}_{\rm P2} + {\rm C}_{\rm F}) \\ = {\rm V}_{\rm A} \bullet {\rm C}_{\rm F} + {\rm V}_{\rm A1} \bullet ({\rm C}_{\rm P1} + {\rm C}_{\rm P2} + {\rm C}_{\rm S})$$

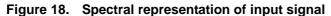

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time  $(T_S)$ . The filter is typically designed to act as anti-aliasing.

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period  $(T_C)$ . Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 11* between the ideal and real sampled voltage on  $C_S$ :

#### **Equation 11**

$$\frac{v_A}{v_{A2}} = \frac{c_{P1} + c_{P2} + c_F}{c_{P1} + c_{P2} + c_F + c_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

#### **Equation 12**

$$C_F > 2048 \cdot C_S$$

Value Conditions<sup>(1)</sup> **Symbol Parameter** Unit Min Тур Max  $C_{L} = 25 pF$ 4  $V_{DD} = 5.0 \text{ V} \pm 10\%,$ PAD3V5V = 0 $C_L = 50 pF$ 6 SIUL.PCRx.SRC = 1  $C_1 = 100 pF$ 12 Output transition time output pin<sup>(2)</sup> CC D ns  $t_{tr}$ FAST configuration  $C_{L} = 25 \text{ pF}$ 4  $V_{DD} = 3.3 \text{ V} \pm 10\%,$  $C_{L} = 50 \text{ pF}$ PAD3V5V = 17 SIUL.PCRx.SRC = 1  $C_1 = 100 pF$ 12  $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$ Symmetric transition time, same drive t<sub>SYM</sub> CC T ns strength between N and P transistor  $V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$ 5

Table 36. Output pin transition times (continued)

- 1.  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 °C to  $T_{A~MAX}$ , unless otherwise specified.

- 2.  $C_L$  includes device and package capacitances ( $C_{PKG} < 5 pF$ ).

- 3. Transition timing of both positive and negative slopes will differ maximum 50%.

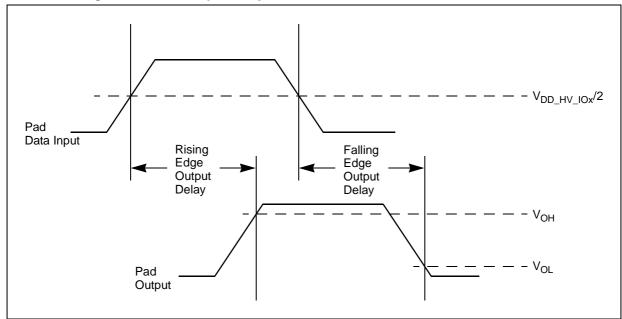

Figure 19. Pad output delay

# 3.17 AC timing characteristics

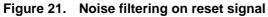

## 3.17.1 RESET pin characteristics

The SPC560P34/SPC560P40 implements a dedicated bidirectional RESET pin.

V<sub>RESET</sub>

V<sub>I</sub>

V<sub>I</sub>

V<sub>I</sub>

V<sub>I</sub>

device reset forced by V<sub>RESET</sub>

t<sub>POR</sub>

device start-up phase

Figure 20. Start-up reset requirements

Table 37. RESET electrical characteristics

| Symbol             |               | С | Donomotor                                                                                         | Conditions <sup>(1)</sup>                                                                       |                     | Value <sup>(2</sup> | 2)                    | 11:4                                                                             |   |                                                                                  |                                                                                   |   |    |    |  |

|--------------------|---------------|---|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------|---------------------|-----------------------|----------------------------------------------------------------------------------|---|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---|----|----|--|

| Symbo              |               |   | Parameter                                                                                         | Conditions                                                                                      | Min                 | Тур                 | Max                   | Unit                                                                             |   |                                                                                  |                                                                                   |   |    |    |  |

| V <sub>IH</sub>    | S<br>R        | Р | Input high level CMOS (Schmitt Trigger)                                                           | _                                                                                               | 0.65V <sub>DD</sub> |                     | V <sub>DD</sub> + 0.4 | V                                                                                |   |                                                                                  |                                                                                   |   |    |    |  |

| V <sub>IL</sub>    | S<br>R        | Р | Input low level CMOS (Schmitt Trigger)                                                            | _                                                                                               | -0.4                | l                   | 0.35V <sub>DD</sub>   | V                                                                                |   |                                                                                  |                                                                                   |   |    |    |  |

| V <sub>HYS</sub>   | $\circ \circ$ | С | Input hysteresis CMOS (Schmitt Trigger)                                                           | _                                                                                               | 0.1V <sub>DD</sub>  | 1                   | I                     | V                                                                                |   |                                                                                  |                                                                                   |   |    |    |  |

|                    |               |   |                                                                                                   | Push Pull, $I_{OL} = 2$ mA,<br>$V_{DD} = 5.0$ V $\pm$ 10%, PAD3V5V $=$ 0<br>(recommended)       | ı                   | l                   | 0.1V <sub>DD</sub>    |                                                                                  |   |                                                                                  |                                                                                   |   |    |    |  |

| V <sub>OL</sub>    | C<br>C        | Р | Output low level                                                                                  | Push Pull, $I_{OL} = 1 \text{ mA}$ ,<br>$V_{DD} = 5.0 \text{ V} \pm 10\%$ , PAD3V5V = $1^{(3)}$ |                     |                     | 0.1V <sub>DD</sub>    | V                                                                                |   |                                                                                  |                                                                                   |   |    |    |  |

|                    |               |   |                                                                                                   | Push Pull, $I_{OL}$ = 1 mA,<br>$V_{DD}$ = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended)             | _                   | _                   | 0.5                   |                                                                                  |   |                                                                                  |                                                                                   |   |    |    |  |

|                    |               |   |                                                                                                   | $C_L = 25 \text{ pF},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$                | _                   | _                   | 10                    |                                                                                  |   |                                                                                  |                                                                                   |   |    |    |  |

|                    |               |   |                                                                                                   | $C_L = 50 \text{ pF},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$                |                     | _                   | 20                    |                                                                                  |   |                                                                                  |                                                                                   |   |    |    |  |

|                    | С             | D | Output transition time output pin <sup>(4)</sup> MEDIUM                                           | $C_L = 100 \text{ pF},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$               | 1                   |                     | 40                    | ns                                                                               |   |                                                                                  |                                                                                   |   |    |    |  |

| t <sub>tr</sub>    | С             |   |                                                                                                   |                                                                                                 |                     |                     | configuration         | $C_L = 25 \text{ pF},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$ | 1 | l                                                                                | 12                                                                                |   |    |    |  |

|                    |               |   |                                                                                                   |                                                                                                 |                     |                     |                       |                                                                                  |   | $C_L = 50 \text{ pF},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$ | 1                                                                                 | l | 25 |    |  |

|                    |               |   |                                                                                                   |                                                                                                 |                     |                     |                       |                                                                                  |   |                                                                                  | $C_L = 100 \text{ pF},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$ | 1 | l  | 40 |  |

| W <sub>FRST</sub>  | S<br>R        | Р | RESET input filtered pulse                                                                        | _                                                                                               | _                   | -                   | 40                    | ns                                                                               |   |                                                                                  |                                                                                   |   |    |    |  |

| W <sub>NFRST</sub> | S<br>R        | Р | RESET input not filtered pulse                                                                    | _                                                                                               | 500                 | 1                   | ı                     | ns                                                                               |   |                                                                                  |                                                                                   |   |    |    |  |

| t <sub>POR</sub>   | СС            | D | Maximum delay before internal reset is released after all V <sub>DD_HV</sub> reach nominal supply | Monotonic V <sub>DD_HV</sub> supply ramp                                                        | _                   | _                   | 1                     | ms                                                                               |   |                                                                                  |                                                                                   |   |    |    |  |

|                    | _             |   | Mask will in                                                                                      | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                                                      | 10                  | _                   | 150                   |                                                                                  |   |                                                                                  |                                                                                   |   |    |    |  |

| I <sub>WPU</sub>   | C             | Р | Weak pull-up current absolute value                                                               | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$                                          | 10                  | _                   | 150                   | μΑ                                                                               |   |                                                                                  |                                                                                   |   |    |    |  |

|                    |               |   | associate value                                                                                   | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^{(5)}$                                    | 10                  | _                   | 250                   |                                                                                  |   |                                                                                  |                                                                                   |   |    |    |  |

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_{A}$  = -40 to 125 °C, unless otherwise specified

<sup>3.</sup> This is a transient configuration during power-up, up to the end of reset PHASE2 (refer to RGM module section of device reference manual).

<sup>2.</sup> All values need to be confirmed during device validation.

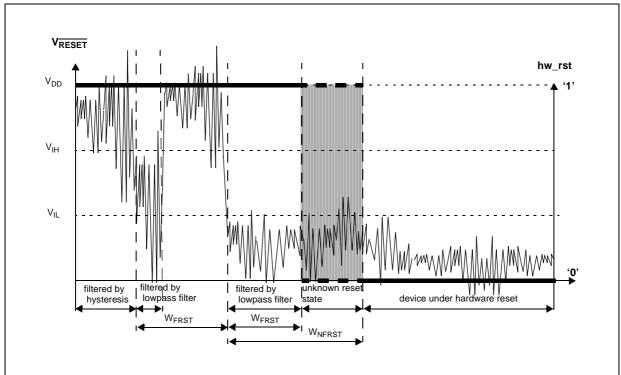

Figure 24. JTAG boundary scan timing

## 3.17.3 Nexus timing

Table 39. Nexus debug port timing<sup>(1)</sup>

| NI- | Complete           |    |   | <b>D</b> anamatan           |                  | Value |     | 1111             |

|-----|--------------------|----|---|-----------------------------|------------------|-------|-----|------------------|

| No. | Symbo              | OI | С | Parameter                   | Min              | Тур   | Max | Unit             |

| 1   | t <sub>TCYC</sub>  | CC | D | TCK cycle time              | 4 <sup>(2)</sup> | _     | _   | t <sub>CYC</sub> |

| 2   | t <sub>NTDIS</sub> | СС | D | TDI data setup time         | 5                | _     | _   | ns               |

| 2   | t <sub>NTMSS</sub> | СС | D | TMS data setup time         | 5                | _     | _   | ns               |

| 3   | t <sub>NTDIH</sub> | СС | D | TDI data hold time          | 25               | _     | _   | ns               |

| 3   | t <sub>NTMSH</sub> | СС | D | TMS data hold time          | 25               | _     | _   | ns               |

| 4   | t <sub>TDOV</sub>  | СС | D | TCK low to TDO data valid   | 10               | _     | 20  | ns               |

| 5   | t <sub>TDOI</sub>  | СС | D | TCK low to TDO data invalid | _                | _     | _   | ns               |

<sup>1.</sup> All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal.

<sup>2.</sup> Lower frequency is required to be fully compliant to standard.

IRQ 1

Figure 28. External interrupt timing

## 3.17.5 DSPI timing

Table 41. DSPI timing<sup>(1)</sup>

| Iabit | <del>;</del> 41.    | וטט   | 1 (111 | ning` ′                     |                                               |                        |                        |       |

|-------|---------------------|-------|--------|-----------------------------|-----------------------------------------------|------------------------|------------------------|-------|

| No.   | Symi                | h a l | С      | Parameter                   | Conditions                                    | Val                    | ue                     | Unit  |

| NO.   | Syllii              | DOI   | C      | Farameter                   | Conditions                                    | Min                    | Max                    | Unit  |

| 1     | 4                   | СС    | D      | DSPI cycle time             | Master (MTFE = 0)                             | 60                     | _                      | no    |

| •     | t <sub>SCK</sub>    | CC    | D      | DSFI Cycle time             | Slave (MTFE = 0)                              | 60                     | _                      | ns    |

| 2     | t <sub>CSC</sub>    | СС    | D      | CS to SCK delay             | _                                             | 16                     | _                      | ns    |

| 3     | t <sub>ASC</sub>    | СС    | D      | After SCK delay             | _                                             | 26                     | _                      | ns    |

| 4     | t <sub>SDC</sub>    | СС    | D      | SCK duty cycle              | _                                             | 0.4 * t <sub>SCK</sub> | 0.6 * t <sub>SCK</sub> | ns    |

| 5     | t <sub>A</sub>      | СС    | D      | Slave access time           | SS active to SOUT valid                       | _                      | 30                     | ns    |

| 6     | t <sub>DIS</sub>    | СС    | D      | Slave SOUT disable time     | SS inactive to SOUT high impedance or invalid | _                      | 16                     | ns    |

| 7     | t <sub>PCSC</sub>   | СС    | D      | PCSx to PCSS time           | _                                             | 13                     | _                      | ns    |

| 8     | t <sub>PASC</sub>   | СС    | D      | PCSS to PCSx time           | _                                             | 13                     | _                      | ns    |

|       |                     |       |        |                             | Master (MTFE = 0)                             | 35                     | _                      |       |

| 9     | t <sub>SUI</sub>    | СС    | D      | Data setup time for inputs  | Slave                                         | 4                      | _                      | ns ns |

| 9     |                     | CC    |        | Data setup time for inputs  | Master (MTFE = 1, CPHA = 0)                   | 35                     | _                      |       |

|       |                     |       |        |                             | Master (MTFE = 1, CPHA = 1)                   | 35                     | _                      |       |

|       |                     |       |        |                             | Master (MTFE = 0)                             | <b>-</b> 5             | _                      |       |

| 10    |                     | СС    |        | Data hald time for incuts   | Slave                                         | 4                      | _                      | 200   |

| 10    | 0 t <sub>HI</sub> C |       | ט      | D Data hold time for inputs | Master (MTFE = 1, CPHA = 0)                   | 11                     | _                      | ns    |

|       |                     |       |        |                             | Master (MTFE = 1, CPHA = 1)                   | -5                     | _                      |       |