Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 20K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p40l1cefar |

# **Contents**

| 1 | Intro | duction |                                                 | 7  |

|---|-------|---------|-------------------------------------------------|----|

|   | 1.1   | Docum   | ent overview                                    | 7  |

|   | 1.2   | Descrip | tion                                            | 7  |

|   | 1.3   | Device  | comparison                                      | 7  |

|   | 1.4   | Block d | iagram                                          | 9  |

|   | 1.5   |         | e details                                       |    |

|   |       | 1.5.1   | High performance e200z0 core processor          |    |

|   |       | 1.5.2   | Crossbar switch (XBAR)                          |    |

|   |       | 1.5.3   | Enhanced direct memory access (eDMA)            |    |

|   |       | 1.5.4   | Flash memory                                    |    |

|   |       | 1.5.5   | Static random access memory (SRAM)              |    |

|   |       | 1.5.6   | Interrupt controller (INTC)                     |    |

|   |       | 1.5.7   | System status and configuration module (SSCM)   | 16 |

|   |       | 1.5.8   | System clocks and clock generation              |    |

|   |       | 1.5.9   | Frequency-modulated phase-locked loop (FMPLL)   | 17 |

|   |       | 1.5.10  | Main oscillator                                 | 17 |

|   |       | 1.5.11  | Internal RC oscillator                          | 17 |

|   |       | 1.5.12  | Periodic interrupt timer (PIT)                  | 18 |

|   |       | 1.5.13  | System timer module (STM)                       | 18 |

|   |       | 1.5.14  | Software watchdog timer (SWT)                   | 18 |

|   |       | 1.5.15  | Fault collection unit (FCU)                     | 18 |

|   |       | 1.5.16  | System integration unit – Lite (SIUL)           | 19 |

|   |       | 1.5.17  | Boot and censorship                             | 19 |

|   |       | 1.5.18  | Error correction status module (ECSM)           | 19 |

|   |       | 1.5.19  | Peripheral bridge (PBRIDGE)                     | 20 |

|   |       | 1.5.20  | Controller area network (FlexCAN)               | 20 |

|   |       | 1.5.21  | Safety port (FlexCAN)                           | 21 |

|   |       | 1.5.22  | Serial communication interface module (LINFlex) | 22 |

|   |       | 1.5.23  | Deserial serial peripheral interface (DSPI)     | 23 |

|   |       | 1.5.24  | Pulse width modulator (FlexPWM)                 | 23 |

|   |       | 1.5.25  | eTimer                                          |    |

|   |       | 1.5.26  | Analog-to-digital converter (ADC) module        | 25 |

|   |       | 1.5.27  | Cross triggering unit (CTU)                     |    |

|   |       | 1.5.28  | Nexus Development Interface (NDI)               | 26 |

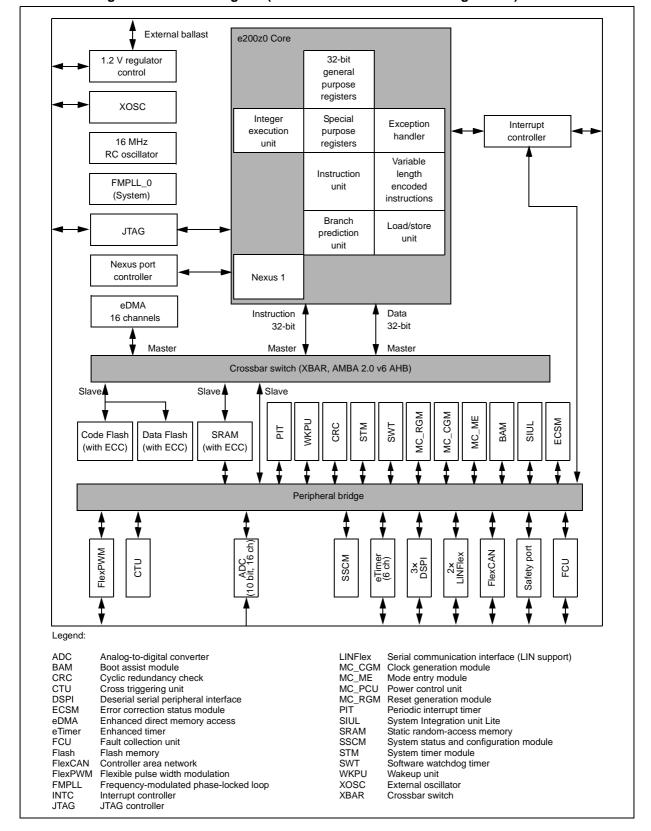

Figure 1. Block diagram (SPC560P40 full-featured configuration)

**577**

#### Digital part:

- 16 input channels

- 4 analog watchdogs comparing ADC results against predefined levels (low, high, range) before results are stored in the appropriate ADC result location

- 2 modes of operation: Motor Control mode or Regular mode

- Regular mode features

- Register based interface with the CPU: control register, status register and 1 result register per channel

- ADC state machine managing 3 request flows: regular command, hardware injected command and software injected command

- Selectable priority between software and hardware injected commands

- DMA compatible interface

- CTU-controlled mode features

- Triggered mode only

- 4 independent result queues (1x16 entries, 2x8 entries, 1x4 entries)

- Result alignment circuitry (left justified and right justified)

- 32-bit read mode allows to have channel ID on one of the 16-bit part

- DMA compatible interfaces

### 1.5.27 Cross triggering unit (CTU)

The cross triggering unit allows automatic generation of ADC conversion requests on user selected conditions without CPU load during the PWM period and with minimized CPU load for dynamic configuration.

It implements the following features:

- Double buffered trigger generation unit with up to 8 independent triggers generated from external triggers

- Trigger generation unit configurable in sequential mode or in triggered mode

- Each trigger can be appropriately delayed to compensate the delay of external low pass filter

- Double buffered global trigger unit allowing eTimer synchronization and/or ADC command generation

- Double buffered ADC command list pointers to minimize ADC-trigger unit update

- Double buffered ADC conversion command list with up to 24 ADC commands

- Each trigger capable of generating consecutive commands

- ADC conversion command allows to control ADC channel, single or synchronous sampling, independent result queue selection

#### 1.5.28 Nexus Development Interface (NDI)

The NDI (Nexus Development Interface) block is compliant with Nexus Class 1 of the IEEE-ISTO 5001-2003 standard. This development support is supplied for MCUs without requiring external address and data pins for internal visibility. The NDI block is an integration of several individual Nexus blocks that are selected to provide the development support interface for this device. The NDI block interfaces to the host processor and internal busses to provide development support as per the IEEE-ISTO 5001-2003 Nexus Class 1 standard.

26/103 Doc ID 16100 Rev 7

Table 5. Supply pins (continued)

|                         | Supply                                                                                                                                                 |        |         |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|--|--|

| Symbol                  | Description                                                                                                                                            | 64-pin | 100-pin |  |  |

| V <sub>DD_LV_COR2</sub> | 1.2 V supply pins for core logic and code Flash. Decoupling capacitor must be connected between these pins and the nearest V <sub>SS_LV_COR</sub> pin. | 58     | 92      |  |  |

| V <sub>SS_LV_COR2</sub> | 1.2 V supply pins for core logic and code Flash. Decoupling capacitor must be connected betwee.n these pins and the nearest $V_{DD\_LV\_COR}$ pin.     | 59     | 93      |  |  |

Analog supply/ground and high/low reference lines are internally physically separate, but are shorted via a double-bonding connection on V<sub>DD\_HV\_ADCx</sub>/V<sub>SS\_HV\_ADCx</sub> pins.

## 2.2.2 System pins

*Table 6* and *Table 7* contain information on pin functions for the SPC560P34/SPC560P40 devices. The pins listed in *Table 6* are single-function pins. The pins shown in *Table 7* are multi-function pins, programmable via their respective pad configuration register (PCR) values.

Table 6. System pins

| Symbol         | Description                                                                                                                                                            | Direction     | Pad sp  | peed <sup>(1)</sup> | Pin    |         |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|---------------------|--------|---------|--|--|--|

| Symbol         | Description                                                                                                                                                            | Direction     | SRC = 0 | SRC = 1             | 64-pin | 100-pin |  |  |  |

| Dedicated pins |                                                                                                                                                                        |               |         |                     |        |         |  |  |  |

| NMI            | Non-maskable Interrupt                                                                                                                                                 | Input only    | Slow    | _                   | 1      | 1       |  |  |  |

| XTAL           | Analog output of the oscillator amplifier circuit—needs to be grounded if oscillator is used in bypass mode                                                            | _             | _       | -                   | 11     | 18      |  |  |  |

| EXTAL          | Analog input of the oscillator amplifier circuit, when the oscillator is not in bypass mode Analog input for the clock generator when the oscillator is in bypass mode | _             | _       | _                   | 12     | 19      |  |  |  |

| TDI            | JTAG test data input                                                                                                                                                   | Input only    | Slow    | _                   | 35     | 58      |  |  |  |

| TMS            | JTAG state machine control                                                                                                                                             | Input only    | Slow    | _                   | 36     | 59      |  |  |  |

| TCK            | JTAG clock                                                                                                                                                             | Input only    | Slow    | _                   | 37     | 60      |  |  |  |

| TDO            | JTAG test data output                                                                                                                                                  | Output only   | Slow    | Fast                | 38     | 61      |  |  |  |

|                | Reset pir                                                                                                                                                              | 1             |         |                     |        |         |  |  |  |

| RESET          | Bidirectional reset with Schmitt trigger characteristics and noise filter                                                                                              | Bidirectional | Medium  | _                   | 13     | 20      |  |  |  |

| _              | Test pin                                                                                                                                                               |               |         |                     |        |         |  |  |  |

| VPP_TEST       | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                           | _             | _       | _                   | 47     | 74      |  |  |  |

<sup>1.</sup> SRC values refer to the value assigned to the Slew Rate Control bits of the pad configuration register.

34/103 Doc ID 16100 Rev 7

Table 7. Pin muxing (continued)

| Port  | PCR      | Alternate                         | Functions                                    | Peripheral <sup>(3)</sup>                        | 1/0                           | Pad sp  | peed <sup>(5)</sup> | F                 | Pin     |

|-------|----------|-----------------------------------|----------------------------------------------|--------------------------------------------------|-------------------------------|---------|---------------------|-------------------|---------|

| pin   | register | function <sup>(1),(2)</sup>       | Functions                                    | Peripheral                                       | direc-<br>tion <sup>(4)</sup> | SRC = 0 | SRC = 1             | 1 64-pin 53 61 63 | 100-pin |

| A[11] | PCR[11]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[11]<br>SCK<br>A[0]<br>A[2]<br>EIRQ[10]  | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL | I/O<br>I/O<br>O O –           | Slow    | Medium              | 53                | 82      |

| A[12] | PCR[12]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[12]<br>SOUT<br>A[2]<br>B[2]<br>EIRQ[11] | SIUL<br>DSPI_2<br>FlexPWM_0<br>FlexPWM_0<br>SIUL | I/O<br>O<br>O<br>O            | Slow    | Medium              | 54                | 83      |

| A[13] | PCR[13]  | ALT0 ALT1 ALT2 ALT3 — — —         | GPIO[13]  — B[2] — SIN FAULT[0] EIRQ[12]     | SIUL  FlexPWM_0  DSPI_2 FlexPWM_0 SIUL           | \frac{1}{0}                   | Slow    | Medium              | 61                | 95      |

| A[14] | PCR[14]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[14]                                     | SIUL Safety Port_0  SIUL                         | I/O<br>O<br>—<br>—<br>I       | Slow    | Medium              | 63                | 99      |

| A[15] | PCR[15]  | ALT0 ALT1 ALT2 ALT3 — —           | GPIO[15]  RXD EIRQ[14]                       | SIUL  —  —  —  Safety Port_0 SIUL                | I/O<br>—<br>—<br>—<br>—<br>I  | Slow    | Medium              | 64                | 100     |

|       |          |                                   |                                              | Port B (16-bit)                                  |                               |         |                     |                   |         |

| B[0]  | PCR[16]  | ALT0<br>ALT1<br>ALT2<br>ALT3<br>— | GPIO[16]<br>TXD<br>—<br>DEBUG[0]<br>EIRQ[15] | SIUL<br>FlexCAN_0<br>—<br>SSCM<br>SIUL           | I/O<br>O<br>—<br>—<br>I       | Slow    | Medium              | 49                | 76      |

| B[1]  | PCR[17]  | ALT0 ALT1 ALT2 ALT3 — —           | GPIO[17]  —  DEBUG[1]  RXD  EIRQ[16]         | SIUL  SSCM FlexCAN_0 SIUL                        | I/O<br>—<br>—<br>—<br>I       | Slow    | Medium              | 50                | 77      |

Table 7. Pin muxing (continued)

| Port  | PCR            | Alternate                   | -         | D: 1 1(3)                 | 1/0                           | Pad sp    | peed <sup>(5)</sup> | Pin    |         |  |

|-------|----------------|-----------------------------|-----------|---------------------------|-------------------------------|-----------|---------------------|--------|---------|--|

| pin   | register       | function <sup>(1),(2)</sup> | Functions | Peripheral <sup>(3)</sup> | direc-<br>tion <sup>(4)</sup> | SRC = 0   | SRC = 1             | 64-pin | 100-pin |  |

|       |                | ALT0                        | GPIO[18]  | SIUL                      | I/O                           |           |                     |        |         |  |

|       |                | ALT1                        | TXD       | LIN_0                     | 0                             |           |                     |        |         |  |

| B[2]  | PCR[18]        | ALT2                        | _         | _                         | _                             | Slow      | Medium              | 51     | 79      |  |

|       |                | ALT3                        | DEBUG[2]  | SSCM                      | _                             |           |                     |        |         |  |

|       |                |                             | EIRQ[17]  | SIUL                      | I                             |           |                     |        |         |  |

|       |                | ALT0                        | GPIO[19]  | SIUL                      | I/O                           |           |                     |        |         |  |

|       |                | ALT1                        |           | _                         | _                             |           |                     |        |         |  |

| B[3]  | B[3] PCR[19]   | ALT2                        | _         | _                         | _                             | Slow      | Medium              | _      | 80      |  |

|       |                |                             |           | ALT3                      | DEBUG[3]                      | SSCM      | _                   |        |         |  |

|       |                | _                           | RXD       | LIN_0                     | I                             |           |                     |        |         |  |

|       |                | ALT0                        | GPIO[22]  | SIUL                      | I/O                           |           |                     |        |         |  |

|       |                | ALT1                        | CLKOUT    | Control                   | 0                             |           |                     |        |         |  |

| B[6]  | PCR[22]        | ALT2                        | CS2       | DSPI_2                    | 0                             | Slow      | Medium              | 62     | 96      |  |

|       |                | ALT3                        | _         | _                         | _                             |           |                     |        |         |  |

|       |                | _                           | EIRQ[18]  | SIUL                      | I                             |           |                     |        |         |  |

|       |                | ALT0                        | GPIO[23]  | SIUL                      |                               |           |                     |        |         |  |

|       |                | ALT1                        | _         | _                         |                               |           |                     |        |         |  |

| רבו   | DCDIOOI        | ALT2                        | _         | _                         | lanut ank                     | ut only — |                     | 20     | 29      |  |

| B[7]  | PCR[23]        | ALT3                        | _         | _                         | Input only                    | _         | _                   | 20     | 29      |  |

|       |                | _                           | AN[0]     | ADC_0                     |                               |           |                     |        |         |  |

|       |                | _                           | RXD       | LIN_0                     |                               |           |                     |        |         |  |

|       |                | ALT0                        | GPIO[24]  | SIUL                      |                               |           |                     |        |         |  |

|       |                | ALT1                        | _         | _                         |                               |           |                     |        |         |  |

| D101  | DCD[04]        | ALT2                        | _         | _                         | Innut only                    |           |                     | 22     | 24      |  |

| B[8]  | PCR[24]        | ALT3                        | _         | _                         | Input only                    | _         | _                   | 22     | 31      |  |

|       |                | _                           | AN[1]     | ADC_0                     |                               |           |                     |        |         |  |

|       |                | _                           | ETC[5]    | eTimer_0                  |                               |           |                     |        |         |  |

|       |                | ALT0                        | GPIO[25]  | SIUL                      |                               |           |                     |        |         |  |

|       |                | ALT1                        | _         | _                         |                               |           |                     |        |         |  |

| B[9]  | PCR[25]        | ALT2                        | _         | _                         | Input only                    | _         | _                   | 24     | 35      |  |

|       |                | ALT3                        | _         | _                         |                               |           |                     |        |         |  |

|       |                | _                           | AN[11]    | ADC_0                     |                               |           |                     |        |         |  |

|       |                | ALT0                        | GPIO[26]  | SIUL                      |                               |           |                     |        |         |  |

|       |                | ALT1                        |           | _                         |                               |           |                     |        | 36      |  |

| B[10] | PCR[26]        | ALT2                        | _         | _                         | Input only                    | _         | _                   | 25     |         |  |

|       | - <del>-</del> | ALT3                        | _         | _                         |                               |           |                     |        |         |  |

|       |                | _                           | AN[12]    | ADC_0                     |                               |           |                     |        |         |  |

Table 7. Pin muxing (continued)

| Port  | PCR      | Alternate                   |            | D (3)                     | 1/0                           | Pad s   | peed <sup>(5)</sup> | P      | Pin     |

|-------|----------|-----------------------------|------------|---------------------------|-------------------------------|---------|---------------------|--------|---------|

| pin   | register | function <sup>(1),(2)</sup> | Functions  | Peripheral <sup>(3)</sup> | direc-<br>tion <sup>(4)</sup> | SRC = 0 | SRC = 1             | 64-pin | 100-pin |

|       |          | ALT0                        | GPIO[27]   | SIUL                      |                               |         |                     |        |         |

|       |          | ALT1                        | _          | _                         |                               |         |                     |        |         |

| B[11] | PCR[27]  | ALT2                        | _          | _                         | Input only                    | _       | _                   | 26     | 37      |

|       |          | ALT3                        | _          | _                         |                               |         |                     |        |         |

|       |          | _                           | AN[13]     | ADC_0                     |                               |         |                     |        |         |

|       |          | ALT0                        | GPIO[28]   | SIUL                      |                               |         |                     |        |         |

|       |          | ALT1                        | _          | _                         |                               |         |                     |        |         |

| B[12] | PCR[28]  | ALT2                        | _          | _                         | Input only                    | _       | _                   | 27     | 38      |

|       |          | ALT3                        | _          | _                         |                               |         |                     |        |         |

|       |          | _                           | AN[14]     | ADC_0                     |                               |         |                     |        |         |

|       |          | ALT0                        | GPIO[29]   | SIUL                      |                               |         |                     |        |         |

|       |          | ALT1                        | _          | _                         |                               |         |                     |        |         |

|       |          | ALT2                        | _          | _                         |                               |         |                     |        |         |

| B[13] | PCR[29]  | ALT3                        | _          | _                         | Input only                    | _       | _                   | 30     | 42      |

|       |          | _                           | AN[6]      | ADC_0                     |                               |         |                     |        |         |

|       |          | _                           | emu. AN[0] | emu. ADC_1 <sup>(6)</sup> |                               |         |                     |        |         |

|       |          | _                           | RXD        | LIN_1                     |                               |         |                     |        |         |

|       |          | ALT0                        | GPIO[30]   | SIUL                      |                               |         |                     |        |         |

|       |          | ALT1                        | _          | _                         |                               |         |                     |        |         |

|       |          | ALT2                        | _          | _                         |                               |         |                     |        |         |

| B[14] | PCR[30]  | ALT3                        | _          | _                         | Input only                    |         |                     |        | 44      |

| D[14] | FUN[30]  | _                           | AN[7]      | ADC_0                     | input only                    | _       | _                   | _      | 44      |

|       |          | _                           | emu. AN[1] | emu. ADC_1 <sup>(6)</sup> |                               |         |                     |        |         |

|       |          | _                           | ETC[4]     | eTimer_0                  |                               |         |                     |        |         |

|       |          | _                           | EIRQ[19]   | SIUL                      |                               |         |                     |        |         |

|       |          | ALT0                        | GPIO[31]   | SIUL                      |                               |         |                     |        |         |

|       |          | ALT1                        | _          | _                         |                               |         |                     |        |         |

|       |          | ALT2                        | _          | _                         |                               |         |                     |        |         |

| B[15] | PCR[31]  | ALT3                        | _          | _                         | Input only                    | _       | _                   | _      | 43      |

|       |          | _                           | AN[8]      | ADC_0                     |                               |         |                     |        |         |

|       |          | _                           | emu. AN[2] | emu. ADC_1 <sup>(6)</sup> |                               |         |                     |        |         |

|       |          | _                           | EIRQ[20]   | SIUL                      |                               |         |                     |        |         |

|       |          |                             |            | Port C (16-bit)           |                               |         |                     |        |         |

|       |          | ALT0                        | GPIO[32]   | SIUL                      |                               |         |                     |        |         |

|       |          | ALT1                        | _          | _                         |                               |         |                     |        |         |

| CIOI  | DCD[33]  | ALT2                        | _          | _                         | Input only                    |         |                     |        | 15      |

| C[0]  | PCR[32]  | ALT3                        | _          | _                         | Input only                    |         | _                   | _      | 45      |

|       |          | _                           | AN[9]      | ADC_0                     |                               |         |                     |        |         |

|       |          | _                           | emu. AN[3] | emu. ADC_1 <sup>(6)</sup> |                               |         |                     |        |         |

# 3.3 Absolute maximum ratings

Table 9. Absolute maximum ratings<sup>(1)</sup>

| 0                                     |        | Danier (au                                                                                                                                                | 0                                  |                    | 11!(                                  |      |  |

|---------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------|---------------------------------------|------|--|

| Symbol                                |        | Parameter                                                                                                                                                 | Conditions                         | Min                | Max <sup>(2)</sup>                    | Unit |  |

| V <sub>SS</sub>                       | S<br>R | Device ground                                                                                                                                             | _                                  | 0                  | 0                                     | V    |  |

| V <sub>DD_HV_IOx</sub> <sup>(3)</sup> | S<br>R | 3.3 V/5.0 V input/output supply voltage (supply).  Code flash memory supply with VDD_HV_IO3 and data flash memory with VDD_HV_IO2                         | _                                  | -0.3               | 6.0                                   | V    |  |

| V <sub>SS_HV_IOx</sub>                | S<br>R | 3.3 V/5.0 V input/output supply voltage (ground).  Code flash memory ground with V <sub>SS_HV_IO3</sub> and data flash memory with V <sub>SS_HV_IO2</sub> | _                                  | -0.1               | 0.1                                   | >    |  |

|                                       | s      | 3.3 V/5.0 V crystal oscillator amplifier                                                                                                                  | _                                  | -0.3               | 6.0                                   |      |  |

| V <sub>DD_HV_OSC</sub>                | R      | supply voltage (supply)                                                                                                                                   | Relative to V <sub>DD_HV_IOx</sub> | -0.3               | $V_{DD\_HV\_IOx} + 0.3$               | ٧    |  |

| V <sub>SS_HV_OSC</sub>                | S<br>R | 3.3 V/5.0 V crystal oscillator amplifier supply voltage (ground)                                                                                          | _                                  | -0.1               | 0.1                                   | V    |  |

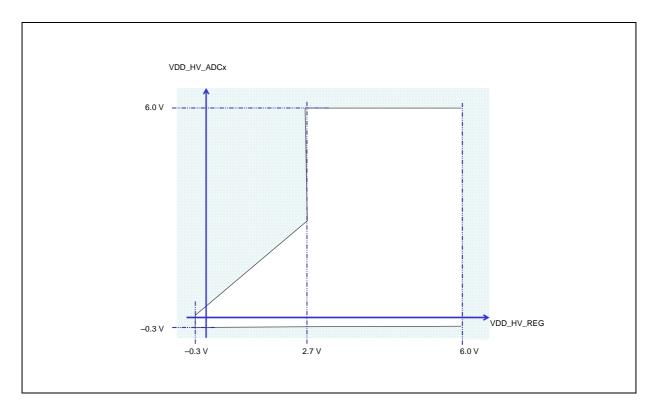

| .,                                    | S<br>R | 3.3 V/5.0 V ADC_0 supply and high-<br>reference voltage                                                                                                   | V <sub>DD_HV_REG</sub><br>< 2.7 V  | -0.3               | V <sub>DD_HV_REG</sub> + 0.3          | V    |  |

| V <sub>DD_HV_ADC0</sub>               |        |                                                                                                                                                           | V <sub>DD_HV_REG</sub> > 2.7 V     | -0.3               | 6.0                                   | V    |  |

| V <sub>SS_HV_ADC0</sub>               | S<br>R | 3.3 V/5.0 V ADC_0 ground and low-reference voltage                                                                                                        | _                                  | -0.1               | 0.1                                   | V    |  |

|                                       | s      | 3.3 V/5.0 V voltage-regulator supply                                                                                                                      | _                                  | -0.3               | 6.0                                   |      |  |

| $V_{DD\_HV\_REG}$                     | R      | voltage                                                                                                                                                   | Relative to V <sub>DD_HV_IOx</sub> | -0.3               | $V_{DD\_HV\_IOx} + 0.3$               | V    |  |

| $TV_DD$                               | S<br>R | Slope characteristics on all V <sub>DD</sub> during power up <sup>(4)</sup> with respect to ground (V <sub>SS</sub> )                                     | _                                  | 3.0 <sup>(5)</sup> | 500 x 10 <sup>3</sup><br>(0.5 [V/μs]) | V/s  |  |

| V <sub>DD_LV_CORx</sub>               | C<br>C | 1.2 V supply pins for core logic (supply)                                                                                                                 | _                                  | -0.1               | 1.5                                   | V    |  |

| V <sub>SS_LV_CORx</sub>               | S<br>R | 1.2 V supply pins for core logic (ground)                                                                                                                 | _                                  | -0.1               | 0.1                                   | V    |  |

|                                       | s      | Voltage on any pin with respect to                                                                                                                        | _                                  | -0.3               | 6.0                                   |      |  |

| V <sub>IN</sub>                       | R      | ground (V <sub>SS_HV_IOx</sub> )                                                                                                                          | Relative to V <sub>DD_HV_IOx</sub> | -0.3               | V <sub>DD_HV_IOx</sub> + 0.3          | V    |  |

| I <sub>INJPAD</sub>                   | S<br>R | Input current on any pin during overload condition                                                                                                        | _                                  | -10                | 10                                    | mA   |  |

46/103 Doc ID 16100 Rev 7

Figure 7. Independent ADC supply (–0.3 V  $\leq$  V<sub>DD\_HV\_REG</sub>  $\leq$  6.0 V)

# 3.4 Recommended operating conditions

Table 10. Recommended operating conditions (5.0 V)

| 0                                     |    | B                                                    | O a malitia ma                     | Val                          | ue                           | 11!  |

|---------------------------------------|----|------------------------------------------------------|------------------------------------|------------------------------|------------------------------|------|

| Symbol                                |    | Parameter                                            | Conditions                         | Min                          | Max <sup>(1)</sup>           | Unit |

| V <sub>SS</sub>                       | SR | Device ground                                        | _                                  | 0                            | 0                            | V    |

| V <sub>DD_HV_IOx</sub> <sup>(2)</sup> | SR | 5.0 V input/output supply voltage                    | _                                  | 4.5                          | 5.5                          | ٧    |

| V <sub>SS_HV_IOx</sub>                | SR | Input/output ground voltage                          | _                                  | 0                            | 0                            | ٧    |

|                                       |    | 5.0 V crystal oscillator amplifier supply voltage    | _                                  | 4.5                          | 5.5                          |      |

| V <sub>DD_HV_OSC</sub>                | SR |                                                      | Relative to V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | $V_{DD\_HV\_IOx} + 0.1$      | V    |

| V <sub>SS_HV_OSC</sub>                | SR | 5.0 V crystal oscillator amplifier reference voltage | _                                  | 0                            | 0                            | V    |

|                                       |    | 5.0 V voltage regulator                              | _                                  | 4.5                          | 5.5                          |      |

| $V_{DD\_HV\_REG}$                     | SR | supply voltage                                       | Relative to V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | V <sub>DD_HV_IOx</sub> + 0.1 | V    |

Table 11. Recommended operating conditions (3.3 V) (continued)

| Ob. al                                   |     | Bananatan                              | O a malitia ma                     | Va                              | lue                     | 1116 |

|------------------------------------------|-----|----------------------------------------|------------------------------------|---------------------------------|-------------------------|------|

| Symbol                                   |     | Parameter Conditions                   |                                    | Min                             | Max <sup>(1)</sup>      | Unit |

|                                          |     | supply voltage                         | _                                  | 3.0                             | 3.6                     |      |

| $V_{DD\_HV\_REG}$                        | SR  |                                        | Relative to V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1    | $V_{DD\_HV\_IOx} + 0.1$ | V    |

|                                          |     | 3.3 V ADC_0 supply and                 | _                                  | 3.0                             | 5.5                     |      |

| V <sub>DD_HV_ADC0</sub>                  | SR  | high reference voltage                 | Relative to V <sub>DD_HV_REG</sub> | V <sub>DD_HV_REG</sub> –<br>0.1 | 5.5                     | V    |

| V <sub>SS_HV_ADC0</sub>                  | SR  | ADC_0 ground and low reference voltage | _                                  | 0                               | 0                       | V    |

| V <sub>DD_LV_REGCOR</sub> (3),(4)        | СС  | Internal supply voltage                | _                                  | _                               | _                       | V    |

| V <sub>SS_LV_REGCOR</sub> <sup>(3)</sup> | SR  | Internal reference voltage             | _                                  | 0                               | 0                       | V    |

| $V_{DD\_LV\_CORx}^{(3),(4)}$             | СС  | Internal supply voltage                | _                                  | _                               | _                       | V    |

| V <sub>SS_LV_CORx</sub> <sup>(3)</sup>   | SR  | Internal reference voltage             | _                                  | 0                               | 0                       | V    |

| т.                                       | SR  | Ambient temperature                    | f <sub>CPU</sub> = 60 MHz          | -40                             | 125                     | °C   |

| T <sub>A</sub>                           | SIX | under bias                             | f <sub>CPU</sub> = 64 MHz          | -40                             | 105                     | °C   |

Full functionality cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

Figure 8 shows the constraints of the different power supplies.

<sup>2.</sup> The difference between each couple of voltage supplies must be less than 100 mV,  $V_{DD\_HV\_IOy} - V_{DD\_HV\_IOx} < 100$  mV.

<sup>3.</sup> To be connected to emitter of external NPN. Low voltage supplies are not under user control—they are produced by an onchip voltage regulator—but for the device to function properly the low voltage grounds (V<sub>SS\_LV\_xxx</sub>) must be shorted to high voltage grounds (V<sub>SS\_HV\_xxx</sub>) and the low voltage supply pins (V<sub>DD\_LV\_xxx</sub>) must be connected to the external ballast emitter.

<sup>4.</sup> The low voltage supplies (V<sub>DD\_LV\_xxx</sub>) are not all independent.

- V<sub>DD\_LV\_COR1</sub> and V<sub>DD\_LV\_COR2</sub> are shorted internally via double bonding connections with lines that provide the low voltage supply to the data flash memory module. Similarly, V<sub>SS\_LV\_COR1</sub> and V<sub>SS\_LV\_COR2</sub> are internally shorted.

- V<sub>DD\_LV\_REGCOR</sub> and V<sub>DD\_LV\_RECORx</sub> are physically shorted internally, as are V<sub>SS\_LV\_REGCOR</sub> and V<sub>SS\_LV\_CORx</sub>.

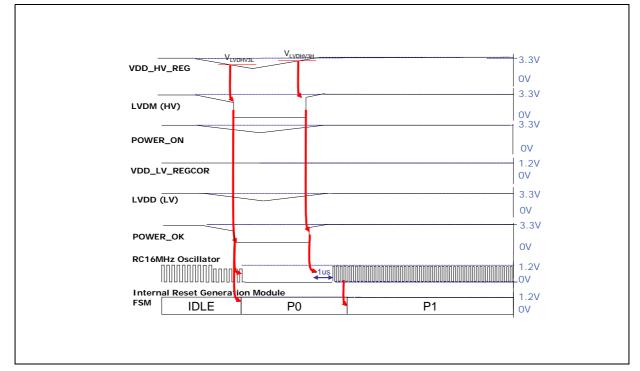

Figure 13. Brown-out typical sequence

## 3.10 DC electrical characteristics

## 3.10.1 NVUSRO register

Portions of the device configuration, such as high voltage supply and watchdog enable/disable after reset are controlled via bit values in the non-volatile user options (NVUSRO) register.

For a detailed description of the NVUSRO register, please refer to the device reference manual.

### NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. *Table 18* shows how NVUSRO[PAD3V5V] controls the device configuration.

Table 18. PAD3V5V field description

| Value <sup>(1)</sup> | Description                  |

|----------------------|------------------------------|

| 0                    | High voltage supply is 5.0 V |

| 1                    | High voltage supply is 3.3 V |

1. Default manufacturing value before flash initialization is '1' (3.3 V).

Table 20. Supply current (5.0 V, NVUSRO[PAD3V5V] = 0)

| Symbol                  | С | C Parameter |                                                                                                        | Conditions                                     |        | Value <sup>(1)</sup> |     | Unit |

|-------------------------|---|-------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------|--------|----------------------|-----|------|

| Symbol                  | C |             | Farameter                                                                                              | Conditions                                     |        | Тур                  | Max |      |

|                         | Т |             | RUN—Maximum mode <sup>(2)</sup>                                                                        |                                                | 40 MHz | 44                   | 55  |      |

| I <sub>DD_LV_CORx</sub> | Р |             | NON—Maximum mode.                                                                                      |                                                | 64 MHz | 52                   | 65  |      |

|                         | Т |             | RUN—Typical mode <sup>(3)</sup>                                                                        | V <sub>DD_LV_CORx</sub> externally             | 40 MHz | 38                   | 46  |      |

|                         | 1 |             | forced at 1.3 V                                                                                        | 64 MHz                                         | 45     | 54                   |     |      |

|                         | Р | ţ           | HALT mode <sup>(4)</sup>                                                                               |                                                | _      | 1.5                  | 10  |      |

|                         | Г | rren        | STOP mode <sup>(5)</sup> Flash during read  VDD_HV_FL at 5.0 V  Flash during erase  VDD_HV_FL at 5.0 V | _                                              | 1      | 10                   |     |      |

|                         | Т | ly cu       | Flash during read                                                                                      | V <sub>DD_HV_FL</sub> at 5.0 V                 | _      | 8                    | 10  | mA   |

| I <sub>DD_FLASH</sub>   |   | ddnS        | Flash during erase operation on 1 flash module                                                         | V <sub>DD_HV_FL</sub> at 5.0 V                 | _      | 15                   | 19  |      |

| I <sub>DD_ADC</sub>     | Т |             | ADC                                                                                                    | $V_{DD\_HV\_ADC0}$ at 5.0 V $f_{ADC}$ = 16 MHz | ADC_0  | 3                    | 4   |      |

| I <sub>DD_OSC</sub>     | Т |             | Oscillator                                                                                             | V <sub>DD_HV_OSC</sub> at 5.0 V                | 8 MHz  | 2.6                  | 3.2 |      |

| I <sub>DD_HV_REG</sub>  | D |             | Internal regulator module current consumption                                                          | V <sub>DD_HV_REG</sub> at 5.5 V                |        |                      | 10  |      |

<sup>1.</sup> All values to be confirmed after characterization/data collection.

Maximum mode: FlexPWM, ADC, CTU, DSPI, LINFlex, FlexCAN, 15 output pins, PLL\_0 enabled, 125 °C ambient. I/O supply current excluded.

<sup>3.</sup> Typical mode configurations: DSPI, LINFlex, FlexCAN, 15 output pins, PLL\_0, 105 °C ambient. I/O supply current excluded.

<sup>4.</sup> Halt mode configurations: Code fetched from SRAM, code flash memory and data flash memory in low power mode, OSC/PLL\_0 are OFF, core clock frozen, all peripherals disabled.

<sup>5.</sup> STOP "P" mode Device Under Test (DUT) configuration: Code fetched from SRAM, code flash memory and data flash memory off, OSC/PLL\_0 are OFF, core clock frozen, all peripherals disabled.

In particular two different transient periods can be distinguished:

A first and quick charge transfer from the internal capacitance C<sub>P1</sub> and C<sub>P2</sub> to the sampling capacitance C<sub>S</sub> occurs (C<sub>S</sub> is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which C<sub>P2</sub> is reported in parallel to C<sub>P1</sub> (call C<sub>P</sub> = C<sub>P1</sub> + C<sub>P2</sub>), the two capacitances C<sub>P</sub> and C<sub>S</sub> are in series, and the time constant is

#### **Equation 5**

$$\tau_1 = (R_{SW} + R_{AD}) \bullet \frac{C_P \bullet C_S}{C_P + C_S}$$

Equation 5 can again be simplified considering only  $C_S$  as an additional worst condition. In reality, the transient is faster, but the A/D converter circuitry has been designed to be robust also in the very worst case: the sampling time  $T_S$  is always much longer than the internal time constant:

#### **Equation 6**

$$\tau_1 < (R_{SW} + R_{AD}) \cdot C_S \ll T_S$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed also on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to *Equation 7*:

#### **Equation 7**

$$V_{A1} \bullet (C_S + C_{P1} + C_{P2}) = V_A \bullet (C_{P1} + C_{P2})$$

A second charge transfer involves also C<sub>F</sub> (that is typically bigger than the on-chip capacitance) through the resistance R<sub>L</sub>: again considering the worst case in which C<sub>P2</sub> and C<sub>S</sub> were in parallel to C<sub>P1</sub> (since the time constant in reality would be faster), the time constant is:

#### **Equation 8**

$$\tau_2 < R_L \bullet (C_S + C_{P1} + C_{P2})$$

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $T_S$ , a constraints on  $R_1$  sizing is obtained:

#### **Equation 9**

$$8.5 \bullet \tau_2 = 8.5 \bullet R_L \bullet (C_S + C_{P1} + C_{P2}) < T_S$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . Equation 10 must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

#### **Equation 10**

$${\rm V}_{\rm A2} \bullet ({\rm C}_{\rm S} + {\rm C}_{\rm P1} + {\rm C}_{\rm P2} + {\rm C}_{\rm F}) \\ = {\rm V}_{\rm A} \bullet {\rm C}_{\rm F} + {\rm V}_{\rm A1} \bullet ({\rm C}_{\rm P1} + {\rm C}_{\rm P2} + {\rm C}_{\rm S})$$

### 3.14.2 ADC conversion characteristics

Table 30. ADC conversion characteristics

| Carrelle el                    |               | _ | Parameter.                                                                                                        | O (1)                                                                                                  | Value            |     |          | Unit     |  |

|--------------------------------|---------------|---|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------|-----|----------|----------|--|

| Symbo                          | OI            | С | Parameter                                                                                                         | Conditions <sup>(1)</sup>                                                                              | Min              | Тур | Max      |          |  |

| f <sub>CK</sub>                | S<br>R        |   | ADC clock frequency (depends on ADC configuration) (The duty cycle depends on ADC clock <sup>(2)</sup> frequency) | _                                                                                                      | 3 <sup>(3)</sup> | _   | 60       | MHz      |  |

| f <sub>s</sub>                 | S<br>R        | _ | Sampling frequency                                                                                                | _                                                                                                      |                  | _   | 1.53     | MHz      |  |

| t <sub>s</sub>                 | _             | D | Sampling time <sup>(4)</sup>                                                                                      | $f_{ADC}$ = 20 MHz, INPSAMP = 3<br>$f_{ADC}$ = 9 MHz, INPSAMP = 255                                    | 125<br>—         | _   | <br>28.2 | ns<br>µs |  |

| t <sub>c</sub>                 | _             | Р | Conversion time <sup>(5)</sup>                                                                                    | f <sub>ADC</sub> = 20 MHz <sup>(6)</sup> , INPCMP = 1                                                  | 0.65<br>0        | _   | _        | μs       |  |

| t <sub>ADC_P</sub>             | S<br>R        | _ | ADC power-up delay (time needed for ADC to settle exiting from software power down; PWDN bit = 0)                 |                                                                                                        |                  | _   | 1.5      | μs       |  |

| C <sub>S</sub> <sup>(7)</sup>  | _             | D | ADC input sampling capacitance                                                                                    | _                                                                                                      | _                | _   | 2.5      | pF       |  |

| C <sub>P1</sub> <sup>(7)</sup> | _             | D | ADC input pin capacitance 1                                                                                       | _                                                                                                      | _                | _   | 3        | pF       |  |

| C <sub>P2</sub> <sup>(7)</sup> | ı             | D | ADC input pin capacitance 2                                                                                       | _                                                                                                      |                  | _   | 1        | pF       |  |

| R <sub>SW</sub> <sup>(7)</sup> | _             | D | Internal resistance of analog source                                                                              | $V_{DD\_HV\_ADC0} = 5 \text{ V} \pm 10\%$<br>$V_{DD\_HV\_ADC0} = 3.3 \text{ V} \pm 10\%$               | _                | _   | 0.6      | kΩ<br>kΩ |  |

| R <sub>AD</sub> <sup>(7)</sup> | _             | D | Internal resistance of analog source                                                                              | _                                                                                                      | _                | _   | 2        | kΩ       |  |

| I <sub>INJ</sub>               | _             | Т | Input current injection                                                                                           | Current injection on one ADC input, different from the converted one. Remains within TUE specification |                  | _   | 5        | mA       |  |

| INL                            | $\circ \circ$ | Р | Integral non-linearity                                                                                            | No overload                                                                                            | -1.5             | _   | 1.5      | LSB      |  |

| DNL                            | $\circ$       | Р | Differential non-linearity                                                                                        | No overload                                                                                            | -1.0             | _   | 1.0      | LSB      |  |

| E <sub>O</sub>                 | $\circ$       | Т | Offset error                                                                                                      | _                                                                                                      |                  | ±1  | _        | LSB      |  |

| E <sub>G</sub>                 | CC            | Т | Gain error                                                                                                        | _                                                                                                      |                  | ±1  | _        | LSB      |  |

| TUE                            | СС            | Р | Total unadjusted error without current injection                                                                  | _                                                                                                      | -2.5             | _   | 2.5      | LSB      |  |

| TUE                            | СС            | Т | Total unadjusted error with current injection                                                                     | _                                                                                                      | -3               | _   | 3        | LSB      |  |

<sup>1.</sup> V<sub>DD</sub> = 3.3 V to 3.6 V / 4.5 V to 5.5 V, T<sub>A</sub> = -40 °C to T<sub>A MAX</sub>, unless otherwise specified and analog input voltage from V<sub>SS\_HV\_ADC0</sub> to V<sub>DD\_HV\_ADC0</sub>.

<sup>2.</sup> AD\_clk clock is always half of the ADC module input clock defined via the auxiliary clock divider for the ADC.

<sup>3.</sup> When configured to allow 60 MHz ADC, the minimum ADC clock speed is 9 MHz, below which the precision is lost.

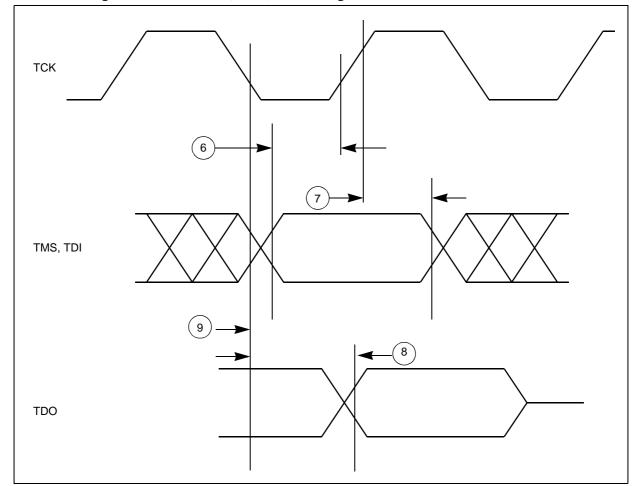

Figure 27. Nexus TDI, TMS, TDO timing

# 3.17.4 External interrupt timing (IRQ pin)

Table 40. External interrupt timing<sup>(1)</sup>

| No. | Symbol            |     | С | Parameter                            | Conditions | Value        |     | Unit             |

|-----|-------------------|-----|---|--------------------------------------|------------|--------------|-----|------------------|

| NO. | Эупп              | iOi | ) | Farameter                            | Conditions | Min          | Max | Ullit            |

| 1   | t <sub>IPWL</sub> | CC  | D | IRQ pulse width low                  | _          | 4            | _   | t <sub>CYC</sub> |

| 2   | t <sub>IPWH</sub> | СС  | D | IRQ pulse width high                 | _          | 4            | _   | t <sub>CYC</sub> |

| 3   | t <sub>ICYC</sub> | СС  | D | IRQ edge to edge time <sup>(2)</sup> | _          | 4 + N<br>(3) | _   | t <sub>CYC</sub> |

- 1. IRQ timing specified at  $f_{SYS} = 64$  MHz and  $V_{DD\_HV\_IOx} = 3.0$  V to 5.5 V,  $T_A = T_L$  to  $T_H$ , and  $C_L = 200$  pF with SRC = 0b00

- 2. Applies when IRQ pins are configured for rising edge or falling edge events, but not both.

- 3. N = ISR time to clear the flag

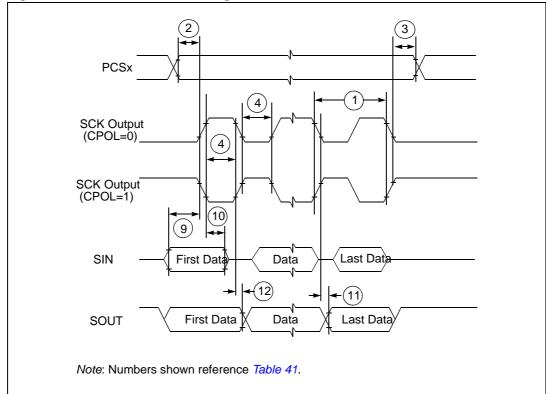

Table 41. DSPI timing<sup>(1)</sup> (continued)

| No. | Cumi             | hal | С                      | Parameter                   | Conditions                     | Value |     | Unit  |

|-----|------------------|-----|------------------------|-----------------------------|--------------------------------|-------|-----|-------|

| NO. | Symbol C         |     | Symbol C Farameter Con |                             | Conditions                     | Min   | Max | Ullit |

|     |                  |     |                        |                             | Master (MTFE = 0)              | _     | 12  |       |

|     |                  |     |                        |                             | Slave                          | _     | 36  |       |

| 11  | t <sub>SUO</sub> | СС  | D                      | Data valid (after SCK edge) | Master (MTFE = 1,<br>CPHA = 0) | _     | 12  | ns    |

|     |                  |     |                        |                             | Master (MTFE = 1,<br>CPHA = 1) | _     | 12  |       |

|     |                  |     |                        |                             | Master (MTFE = 0)              | -2    | _   |       |

| 12  | tua              | СС  | D                      | Data hold time for outputs  | Slave                          | 6     |     | ] nc  |

| 12  | t <sub>HO</sub>  |     |                        | Data Hold time for outputs  | Master (MTFE = 1, CPHA = 0)    | 6 —   |     | ns    |

|     |                  |     |                        |                             | Master (MTFE = 1, CPHA = 1)    | -2    | _   |       |

<sup>1.</sup> All timing are provided with 50 pF capacitance on output, 1 ns transition time on input signal

Table 42. LQFP100 package mechanical data

|                    |        | Dimensions |        |                       |        |        |  |  |

|--------------------|--------|------------|--------|-----------------------|--------|--------|--|--|

| Symbol             |        | mm         |        | inches <sup>(1)</sup> |        |        |  |  |

|                    | Min    | Тур        | Max    | Min                   | Тур    | Max    |  |  |

| Α                  | _      | _          | 1.600  | _                     | _      | 0.0630 |  |  |

| A1                 | 0.050  | _          | 0.150  | 0.0020                | _      | 0.0059 |  |  |

| A2                 | 1.350  | 1.400      | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |

| b                  | 0.170  | 0.220      | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |  |

| С                  | 0.090  | _          | 0.200  | 0.0035                | _      | 0.0079 |  |  |

| D                  | 15.800 | 16.000     | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| D1                 | 13.800 | 14.000     | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| D3                 | _      | 12.000     | _      | _                     | 0.4724 | _      |  |  |

| Е                  | 15.800 | 16.000     | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| E1                 | 13.800 | 14.000     | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| E3                 | _      | 12.000     | _      | _                     | 0.4724 | _      |  |  |

| е                  | _      | 0.500      | _      | _                     | 0.0197 | _      |  |  |

| L                  | 0.450  | 0.600      | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1                 | _      | 1.000      | _      | _                     | 0.0394 | _      |  |  |

| k                  | 0.0°   | 3.5°       | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |  |

| ccc <sup>(2)</sup> |        | 0.08       |        |                       | 0.0031 | I      |  |  |

<sup>1.</sup> Values in inches are converted from millimeters (mm) and rounded to four decimal digits.

<sup>2.</sup> Tolerance

# 4.2.2 LQFP64 mechanical outline drawing

Figure 39. LQFP64 package mechanical drawing

Table 43. LQFP64 package mechanical data

|        |      |      | Dimer | nsions                |        |        |  |

|--------|------|------|-------|-----------------------|--------|--------|--|

| Symbol |      | mm   |       | inches <sup>(1)</sup> |        |        |  |

|        | Min  | Тур  | Max   | Min                   | Тур    | Max    |  |

| А      | _    | _    | 1.6   | _                     | _      | 0.063  |  |

| A1     | 0.05 | _    | 0.15  | 0.002                 | _      | 0.0059 |  |

| A2     | 1.35 | 1.4  | 1.45  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.17 | 0.22 | 0.27  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.09 | _    | 0.2   | 0.0035                | _      | 0.0079 |  |

| D      | 11.8 | 12   | 12.2  | 0.4646                | 0.4724 | 0.4803 |  |

| D1     | 9.8  | 10   | 10.2  | 0.3858                | 0.3937 | 0.4016 |  |

| D3     | _    | 7.5  | _     | _                     | 0.2953 | _      |  |

| Е      | 11.8 | 12   | 12.2  | 0.4646                | 0.4724 | 0.4803 |  |

| E1     | 9.8  | 10   | 10.2  | 0.3858                | 0.3937 | 0.4016 |  |

| E3     | _    | 7.5  | _     | _                     | 0.2953 | _      |  |

| е      | _    | 0.5  | _     | _                     | 0.0197 | _      |  |

| L      | 0.45 | 0.6  | 0.75  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | _    | 1    | _     | _                     | 0.0394 | _      |  |

Table 43. LQFP64 package mechanical data (continued)

|                    | Dimensions |      |      |        |                       |      |  |  |

|--------------------|------------|------|------|--------|-----------------------|------|--|--|

| Symbol             |            | mm   |      |        | inches <sup>(1)</sup> |      |  |  |

|                    | Min        | Тур  | Max  | Min    | Тур                   | Max  |  |  |

| k                  | 0.0°       | 3.5° | 7.0° | 0.0°   | 3.5°                  | 7.0° |  |  |

| ccc <sup>(2)</sup> | 0.08       |      |      | 0.0031 |                       |      |  |  |

<sup>1.</sup> Values in inches are converted from millimeters (mm) and rounded to four decimal digits.

<sup>2.</sup> Tolerance

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com