Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 20K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p40l1cefby |

#### 1.5 Feature details

#### 1.5.1 High performance e200z0 core processor

The e200z0 Power Architecture core provides the following features:

- High performance e200z0 core processor for managing peripherals and interrupts

- Single issue 4-stage pipeline in-order execution 32-bit Power Architecture CPU

- Harvard architecture

- Variable length encoding (VLE), allowing mixed 16- and 32-bit instructions

- Results in smaller code size footprint

- Minimizes impact on performance

- Branch processing acceleration using lookahead instruction buffer

- Load/store unit

- 1-cycle load latency

- Misaligned access support

- No load-to-use pipeline bubbles

- Thirty-two 32-bit general purpose registers (GPRs)

- Separate instruction bus and load/store bus Harvard architecture

- Hardware vectored interrupt support

- Reservation instructions for implementing read-modify-write constructs

- Long cycle time instructions, except for guarded loads, do not increase interrupt latency

- Extensive system development support through Nexus debug port

- Non-maskable interrupt support

#### 1.5.2 Crossbar switch (XBAR)

The XBAR multi-port crossbar switch supports simultaneous connections between three master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 32-bit data bus width.

The crossbar allows for two concurrent transactions to occur from any master port to any slave port; but one of those transfers must be an instruction fetch from internal flash memory. If a slave port is simultaneously requested by more than one master port, arbitration logic will select the higher priority master and grant it ownership of the slave port. All other masters requesting that slave port will be stalled until the higher priority master completes its transactions. Requesting masters will be treated with equal priority and will be granted access a slave port in round-robin fashion, based upon the ID of the last master to be granted access.

### 1.5.6 Interrupt controller (INTC)

The interrupt controller (INTC) provides priority-based preemptive scheduling of interrupt requests, suitable for statically scheduled hard real-time systems. The INTC handles 128 selectable-priority interrupt sources.

For high-priority interrupt requests, the time from the assertion of the interrupt request by the peripheral to the execution of the interrupt service routine (ISR) by the processor has been minimized. The INTC provides a unique vector for each interrupt request source for quick determination of which ISR has to be executed. It also provides a wide number of priorities so that lower priority ISRs do not delay the execution of higher priority ISRs. To allow the appropriate priorities for each source of interrupt request, the priority of each interrupt request is software configurable.

When multiple tasks share a resource, coherent accesses to that resource need to be supported. The INTC supports the priority ceiling protocol (PCP) for coherent accesses. By providing a modifiable priority mask, the priority can be raised temporarily so that all tasks which share the same resource can not preempt each other.

The INTC provides the following features:

- Unique 9-bit vector for each separate interrupt source

- 8 software triggerable interrupt sources

- 16 priority levels with fixed hardware arbitration within priority levels for each interrupt source

- Ability to modify the ISR or task priority: modifying the priority can be used to implement the priority ceiling protocol for accessing shared resources.

- 1 external high priority interrupt (NMI) directly accessing the main core and I/O processor (IOP) critical interrupt mechanism

### 1.5.7 System status and configuration module (SSCM)

The system status and configuration module (SSCM) provides central device functionality.

The SSCM includes these features:

- System configuration and status

- Memory sizes/status

- Device mode and security status

- Determine boot vector

- Search code flash for bootable sector

- DMA status

- Debug status port enable and selection

- Bus and peripheral abort enable/disable

### 1.5.8 System clocks and clock generation

The following list summarizes the system clock and clock generation on the SPC560P34/SPC560P40:

- Lock detect circuitry continuously monitors lock status

- Loss of clock (LOC) detection for PLL outputs

- Programmable output clock divider (÷1, ÷2, ÷4, ÷8)

- FlexPWM module and eTimer module running at the same frequency as the e200z0h core

- Internal 16 MHz RC oscillator for rapid start-up and safe mode: supports frequency trimming by user application

### 1.5.9 Frequency-modulated phase-locked loop (FMPLL)

The FMPLL allows the user to generate high speed system clocks from a 4–40 MHz input clock. Further, the FMPLL supports programmable frequency modulation of the system clock. The PLL multiplication factor, output clock divider ratio are all software configurable.

The FMPLL has the following major features:

- Input clock frequency: 4–40 MHz

- Maximum output frequency: 64 MHz

- Voltage controlled oscillator (VCO)—frequency 256–512 MHz

- Reduced frequency divider (RFD) for reduced frequency operation without forcing the FMPLL to relock

- Frequency-modulated PLL

- Modulation enabled/disabled through software

- Triangle wave modulation

- Programmable modulation depth (±0.25% to ±4% deviation from center frequency): programmable modulation frequency dependent on reference frequency

- Self-clocked mode (SCM) operation

#### 1.5.10 Main oscillator

The main oscillator provides these features:

- Input frequency range: 4–40 MHz

- Crystal input mode or oscillator input mode

- PLL reference

#### 1.5.11 Internal RC oscillator

This device has an RC ladder phase-shift oscillator. The architecture uses constant current charging of a capacitor. The voltage at the capacitor is compared by the stable bandgap reference voltage.

### 1.5.16 System integration unit – Lite (SIUL)

The SPC560P34/SPC560P40 SIUL controls MCU pad configuration, external interrupt, general purpose I/O (GPIO), and internal peripheral multiplexing.

The pad configuration block controls the static electrical characteristics of I/O pins. The GPIO block provides uniform and discrete input/output control of the I/O pins of the MCU.

The SIUL provides the following features:

- Centralized general purpose input output (GPIO) control of up to 49 input/output pins and 16 analog input-only pads (package dependent)

- All GPIO pins can be independently configured to support pull-up, pull-down, or no pull

- Reading and writing to GPIO supported both as individual pins and 16-bit wide ports

- All peripheral pins, except ADC channels, can be alternatively configured as both general purpose input or output pins

- ADC channels support alternative configuration as general purpose inputs

- Direct readback of the pin value is supported on all pins through the SIUL

- Configurable digital input filter that can be applied to some general purpose input pins for noise elimination

- Up to 4 internal functions can be multiplexed onto 1 pin

### 1.5.17 Boot and censorship

Different booting modes are available in the SPC560P34/SPC560P40: booting from internal flash memory and booting via a serial link.

The default booting scheme uses the internal flash memory (an internal pull-down resistor is used to select this mode). Optionally, the user can boot via FlexCAN or LINFlex (using the boot assist module software).

A censorship scheme is provided to protect the content of the flash memory and offer increased security for the entire device.

A password mechanism is designed to grant the legitimate user access to the non-volatile memory.

#### Boot assist module (BAM)

The BAM is a block of read-only memory that is programmed once and is identical for all SPC560Pxx devices that are based on the e200z0h core. The BAM program is executed every time the device is powered on if the alternate boot mode has been selected by the user.

The BAM provides the following features:

- Serial bootloading via FlexCAN or LINFlex

- Ability to accept a password via the used serial communication channel to grant the legitimate user access to the non-volatile memory

#### 1.5.18 Error correction status module (ECSM)

The ECSM provides a myriad of miscellaneous control functions regarding program-visible information about the platform configuration and revision levels, a reset status register, a software watchdog timer, wakeup control for exiting sleep modes, and information on

## 1.5.31 On-chip voltage regulator (VREG)

The on-chip voltage regulator module provides the following features:

- Uses external NPN (negative-positive-negative) transistor

- Regulates external 3.3 V/5.0 V down to 1.2 V for the core logic

- Low voltage detection on the internal 1.2 V and I/O voltage 3.3 V

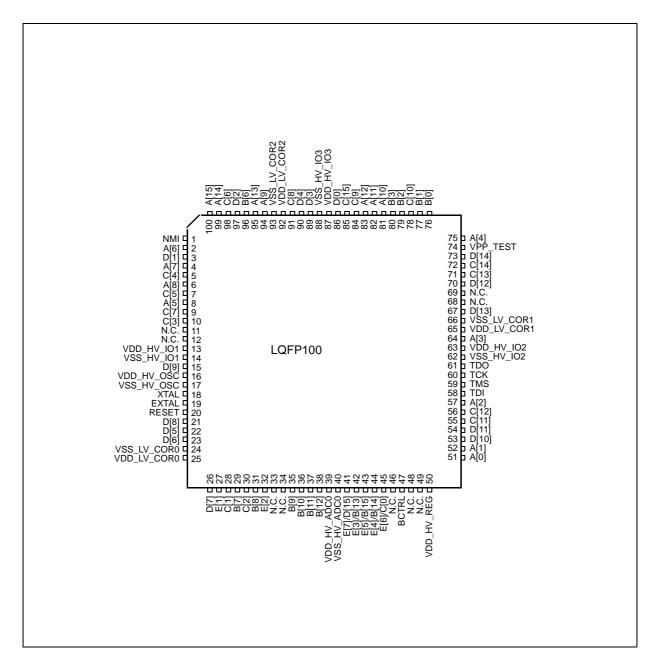

Figure 5. 100-pin LQFP pinout – Airbag configuration (top view)

32/103 Doc ID 16100 Rev 7

Table 5. Supply pins (continued)

|                         | Supply                                                                                                                                                 |        |         |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|--|--|--|

| Symbol                  | Description                                                                                                                                            | 64-pin | 100-pin |  |  |  |

| V <sub>DD_LV_COR2</sub> | 1.2 V supply pins for core logic and code Flash. Decoupling capacitor must be connected between these pins and the nearest V <sub>SS_LV_COR</sub> pin. | 58     | 92      |  |  |  |

| V <sub>SS_LV_COR2</sub> | 1.2 V supply pins for core logic and code Flash. Decoupling capacitor must be connected betwee.n these pins and the nearest $V_{DD\_LV\_COR}$ pin.     | 59     | 93      |  |  |  |

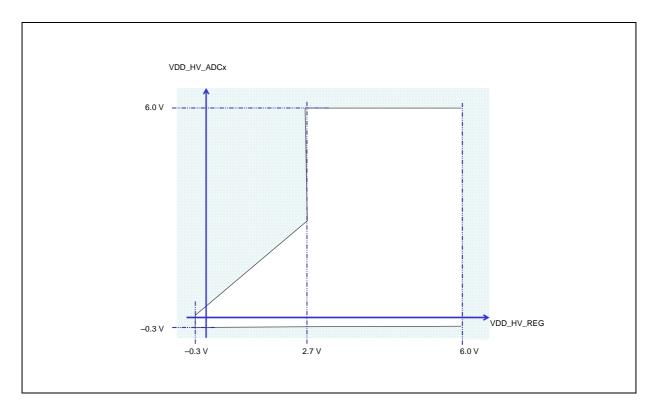

Analog supply/ground and high/low reference lines are internally physically separate, but are shorted via a double-bonding connection on V<sub>DD\_HV\_ADCx</sub>/V<sub>SS\_HV\_ADCx</sub> pins.

## 2.2.2 System pins

*Table 6* and *Table 7* contain information on pin functions for the SPC560P34/SPC560P40 devices. The pins listed in *Table 6* are single-function pins. The pins shown in *Table 7* are multi-function pins, programmable via their respective pad configuration register (PCR) values.

Table 6. System pins

| Symbol   | Description                                                                                                                                                            | Direction     | Pad sp  | peed <sup>(1)</sup> | Pin    |         |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|---------------------|--------|---------|

| Symbol   | Description                                                                                                                                                            | Direction     | SRC = 0 | SRC = 1             | 64-pin | 100-pin |

|          | Dedicated p                                                                                                                                                            | oins          |         |                     |        |         |

| NMI      | Non-maskable Interrupt                                                                                                                                                 | Input only    | Slow    | _                   | 1      | 1       |

| XTAL     | Analog output of the oscillator amplifier circuit—needs to be grounded if oscillator is used in bypass mode                                                            | _             | _       | -                   | 11     | 18      |

| EXTAL    | Analog input of the oscillator amplifier circuit, when the oscillator is not in bypass mode Analog input for the clock generator when the oscillator is in bypass mode | _             | _       | _                   | 12     | 19      |

| TDI      | JTAG test data input                                                                                                                                                   | Input only    | Slow    | _                   | 35     | 58      |

| TMS      | JTAG state machine control                                                                                                                                             | Input only    | Slow    | _                   | 36     | 59      |

| TCK      | JTAG clock                                                                                                                                                             | Input only    | Slow    | _                   | 37     | 60      |

| TDO      | JTAG test data output                                                                                                                                                  | Output only   | Slow    | Fast                | 38     | 61      |

|          | Reset pir                                                                                                                                                              | 1             |         |                     |        |         |

| RESET    | Bidirectional reset with Schmitt trigger characteristics and noise filter                                                                                              | Bidirectional | Medium  | _                   | 13     | 20      |

| _        | Test pin                                                                                                                                                               |               |         |                     |        |         |

| VPP_TEST | Pin for testing purpose only. To be tied to ground in normal operating mode.                                                                                           | _             | _       | _                   | 47     | 74      |

<sup>1.</sup> SRC values refer to the value assigned to the Slew Rate Control bits of the pad configuration register.

34/103 Doc ID 16100 Rev 7

Figure 7. Independent ADC supply (–0.3 V  $\leq$  V<sub>DD\_HV\_REG</sub>  $\leq$  6.0 V)

# 3.4 Recommended operating conditions

Table 10. Recommended operating conditions (5.0 V)

| 0                                     |    | B                                                    | O a malitia ma                     | Val                                | ue                           | 11!                     |   |

|---------------------------------------|----|------------------------------------------------------|------------------------------------|------------------------------------|------------------------------|-------------------------|---|

| Symbol                                |    | Parameter                                            | Parameter Conditions               |                                    | Max <sup>(1)</sup>           | Unit                    |   |

| V <sub>SS</sub>                       | SR | Device ground                                        | _                                  | 0                                  | 0                            | V                       |   |

| V <sub>DD_HV_IOx</sub> <sup>(2)</sup> | SR | 5.0 V input/output supply voltage                    | _                                  | 4.5                                | 5.5                          | ٧                       |   |

| V <sub>SS_HV_IOx</sub>                | SR | Input/output ground voltage                          | _                                  | 0                                  | 0                            | ٧                       |   |

|                                       | SR | SR                                                   | 5.0 V crystal oscillator           | _                                  | 4.5                          | 5.5                     |   |

| V <sub>DD_HV_OSC</sub>                |    |                                                      | amplifier supply voltage           | Relative to V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1 | $V_{DD\_HV\_IOx} + 0.1$ | V |

| V <sub>SS_HV_OSC</sub>                | SR | 5.0 V crystal oscillator amplifier reference voltage | _                                  | 0                                  | 0                            | V                       |   |

|                                       |    | 5.0 V voltage regulator                              | _                                  | 4.5                                | 5.5                          |                         |   |

| $V_{DD\_HV\_REG}$                     | SR | supply voltage                                       | Relative to V <sub>DD_HV_IOx</sub> | V <sub>DD_HV_IOx</sub> - 0.1       | V <sub>DD_HV_IOx</sub> + 0.1 | V                       |   |

Table 15. Approved NPN ballast components

| Part   | Manufacturer | Approved derivatives <sup>(1)</sup> |

|--------|--------------|-------------------------------------|

| BC817  | Infineon     | BC817-16; BC817-25; BC817SU         |

| BC617  | NXP          | BC817-16; BC817-25                  |

|        | ST           | BCP56-16                            |

| BCP56  | Infineon     | BCP56-10; BCP56-16                  |

| BCF 30 | ON Semi      | BCP56-10                            |

|        | NXP          | BCP56-10; BCP56-16                  |

<sup>1.</sup> For automotive applications please check with the appropriate transistor vendor for automotive grade certification

Table 16. Voltage regulator electrical characteristics

| Symbol                    |        | С | Parameter                                                            | Conditions                                                                                                                            |          | Value    |      | Unit |

|---------------------------|--------|---|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------|----------|------|------|

|                           |        | C | Farameter                                                            | Conditions                                                                                                                            | Min      | Тур      | Max  |      |

| V <sub>DD_LV_REGCOR</sub> | C      | Р | Output voltage under maximum load run supply current configuration   | Post-trimming                                                                                                                         | 1.15     | _        | 1.32 | V    |

| C <sub>DEC1</sub> SR      |        | _ | External decoupling/stability ceramic capacitor                      | BJT from <i>Table 15</i> . Three capacitors (i.e. X7R or X8R capacitors) with nominal value of 10 µF                                  | 19.5     | 30       | _    | μF   |

|                           |        |   |                                                                      | BJT BC817, one capacitance of 22 µF                                                                                                   | 14.3     | 22       | _    | μF   |

| R <sub>REG</sub>          | S<br>R | _ | Resulting ESR of either one or all three C <sub>DEC1</sub>           | Absolute maximum value<br>between 100 kHz and<br>10 MHz                                                                               | _        | _        | 45   | mΩ   |

| C <sub>DEC2</sub>         | S<br>R | _ | External decoupling/stability ceramic capacitor                      | Four capacitances (i.e. X7R or X8R capacitors) with nominal value of 440 nF                                                           | 120<br>0 | 176<br>0 | _    | nF   |

| C <sub>DEC3</sub>         | S<br>R |   | External decoupling/stability ceramic capacitor on VDD_HV_REG        | Three capacitors (i.e. X7R or X8R capacitors) with nominal value of 10 $\mu$ F; $C_{DEC3}$ has to be equal or greater than $C_{DEC1}$ | 19.5     | 30       | _    | μF   |

| L <sub>Reg</sub>          | S<br>R | _ | Resulting ESL of $V_{DD\_HV\_REG}$ BCTRL and $V_{DD\_LV\_CORx}$ pins | _                                                                                                                                     | _        | _        | 5    | nΗ   |

56/103 Doc ID 16100 Rev 7

### 3.8.2 Voltage monitor electrical characteristics

The device implements a power on reset module to ensure correct power-up initialization, as well as three low voltage detectors to monitor the  $V_{DD}$  and the  $V_{DD\_LV}$  voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply

- $\bullet$  LVDHV5 monitors V<sub>DD</sub> when application uses device in the 5.0 V  $\pm$  10% range

- LVDLVCOR monitors low voltage digital power domain

Table 17. Low voltage monitor electrical characteristics

| Cumbal                               | С                                              | Baramatar                                     | Conditions <sup>(1)</sup> | Val  | lue   | Unit |

|--------------------------------------|------------------------------------------------|-----------------------------------------------|---------------------------|------|-------|------|

| Symbol                               |                                                | Parameter                                     | Conditions                | Min  | Max   | Unit |

| V <sub>PORH</sub>                    | Т                                              | Power-on reset threshold                      | _                         | 1.5  | 2.7   | V    |

| V <sub>PORUP</sub>                   | Р                                              | Supply for functional POR module              | T <sub>A</sub> = 25 °C    | 1.0  | _     | V    |

| V <sub>REGLVDMOK_H</sub>             | Р                                              | Regulator low voltage detector high threshold | _                         | _    | 2.95  | V    |

| V <sub>REGLVDMOK_L</sub>             | P Regulator low voltage detector low threshold |                                               | _                         | 2.6  | _     | V    |

| V <sub>FLLVDMOK_H</sub>              | Р                                              | Flash low voltage detector high threshold     | _                         | _    | 2.95  | V    |

| V <sub>FLLVDMOK_L</sub>              | Р                                              | Flash low voltage detector low threshold      | _                         | 2.6  | _     | V    |

| V <sub>IOLVDMOK_H</sub>              | Р                                              | I/O low voltage detector high threshold       | _                         | _    | 2.95  | V    |

| V <sub>IOLVDMOK_L</sub>              | Р                                              | I/O low voltage detector low threshold        | _                         | 2.6  | _     | V    |

| V <sub>IOLVDM5OK_H</sub>             | Р                                              | I/O 5 V low voltage detector high threshold   | _                         | _    | 4.4   | V    |

| V <sub>IOLVDM5OK_L</sub> P I/O 5 V I |                                                | I/O 5 V low voltage detector low threshold    | _                         | 3.8  | _     | V    |

| V <sub>MLVDDOK_H</sub>               | Р                                              | Digital supply low voltage detector high      | _                         | _    | 1.145 | V    |

| V <sub>MLVDDOK_L</sub>               | Р                                              | Digital supply low voltage detector low       | _                         | 1.08 | —     | V    |

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 °C to  $T_{A~MAX}$ , unless otherwise specified

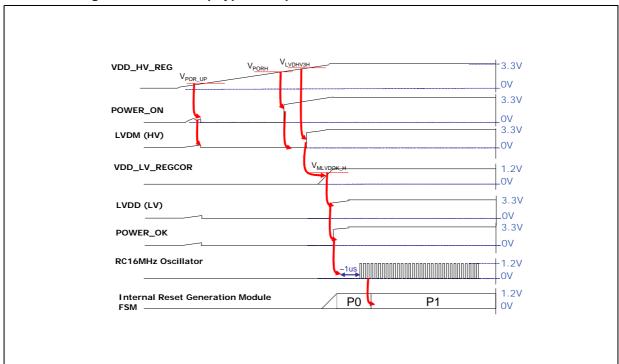

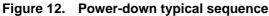

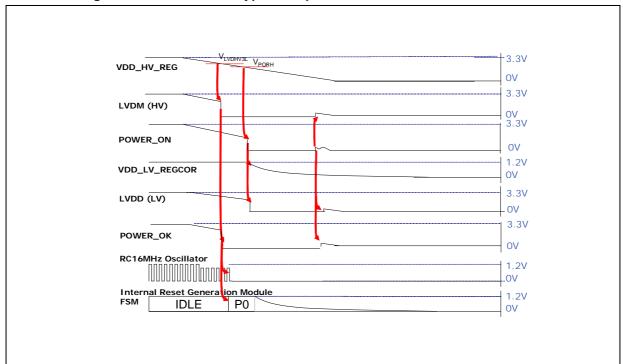

# 3.9 Power up/down sequencing

To prevent an overstress event or a malfunction within and outside the device, the SPC560P34/SPC560P40 implements the following sequence to ensure each module is started only when all conditions for switching it ON are available:

- A POWER\_ON module working on voltage regulator supply controls the correct startup of the regulator. This is a key module ensuring safe configuration for all voltage regulator functionality when supply is below 1.5 V. Associated POWER\_ON (or POR) signal is active low.

- Several low voltage detectors, working on voltage regulator supply monitor the voltage

of the critical modules (voltage regulator, I/Os, flash memory and low voltage domain).

LVDs are gated low when POWER ON is active.

- A POWER\_OK signal is generated when all critical supplies monitored by the LVD are available. This signal is active high and released to all modules including I/Os, flash

memory and 16 MHz RC oscillator needed during power-up phase and reset phase. When POWER\_OK is low the associated modules are set into a safe state.

Figure 11. Power-up typical sequence

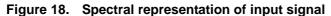

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time  $(T_S)$ . The filter is typically designed to act as anti-aliasing.

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period  $(T_C)$ . Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 11* between the ideal and real sampled voltage on  $C_S$ :

#### **Equation 11**

$$\frac{v_A}{v_{A2}} = \frac{c_{P1} + c_{P2} + c_F}{c_{P1} + c_{P2} + c_F + c_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

#### **Equation 12**

$$C_F > 2048 \cdot C_S$$

- 4. During the sampling time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>s</sub>. After the end of the sampling time t<sub>s</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>s</sub> depend on programming.

- 5. This parameter includes the sampling time t<sub>s</sub>.

- 6. 20 MHz ADC clock. Specific prescaler is programmed on MC\_PLL\_CLK to provide 20 MHz clock to the ADC.

- 7. See Figure 16.

## 3.15 Flash memory electrical characteristics

### 3.15.1 Program/Erase characteristics

Table 31. Program and erase specifications

| Symbol                   | С | Parameter                                                     | Min | Typ <sup>(1)</sup> | Initial<br>Max <sup>(2)</sup> | Max <sup>(3)</sup> | Unit |   |                                                              |   |     |     |      |    |

|--------------------------|---|---------------------------------------------------------------|-----|--------------------|-------------------------------|--------------------|------|---|--------------------------------------------------------------|---|-----|-----|------|----|

| T <sub>wprogram</sub>    | Р | Word Program Time for data flash memory <sup>(4)</sup>        | _   | 30                 | 70                            | 500                | μs   |   |                                                              |   |     |     |      |    |

| T <sub>dwprogram</sub>   | Р | Double Word Program Time for code flash memory <sup>(4)</sup> | _   | 22                 | 50                            | 500                | μs   |   |                                                              |   |     |     |      |    |

| T <sub>BKPRG</sub> P     |   | Bank Program (256 KB) <sup>(4)(5)</sup>                       | _   | 0.73               | 0.83                          | 17.5               | s    |   |                                                              |   |     |     |      |    |

|                          |   | Bank Program (64 KB) <sup>(4)(5)</sup>                        | _   | 0.49               | 1.2                           | 4.1                | s    |   |                                                              |   |     |     |      |    |

| Т                        | D | P                                                             | P   | Б                  | Б                             | Р                  | Р    | P | 16 KB Block Pre-program and Erase Time for code flash memory | _ | 300 | 500 | 5000 | ms |

| T <sub>16kpperase</sub>  |   | 16 KB Block Pre-program and Erase Time for data flash memory  | _   | 700                | 800                           | 5000               | 1113 |   |                                                              |   |     |     |      |    |

| T <sub>32kpperase</sub>  | Р | 32 KB Block Pre-program and Erase Time                        | _   | 400                | 600                           | 5000               | ms   |   |                                                              |   |     |     |      |    |

| T <sub>128kpperase</sub> | Р | 128 KB Block Pre-program and Erase Time                       | _   | 800                | 1300                          | 7500               | ms   |   |                                                              |   |     |     |      |    |

| t <sub>ESRT</sub>        | Р | Program and erase specifications <sup>(6)</sup>               | 10  | 1                  | 1                             | _                  | ms   |   |                                                              |   |     |     |      |    |

Typical program and erase times assume nominal supply values and operation at 25 °C. All times are subject to change pending device characterization.

6. Time between erase suspend resume and next erase suspend request.

<sup>2.</sup> Initial factory condition: < 100 program/erase cycles, 25 °C, typical supply voltage.

<sup>3.</sup> The maximum program and erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

<sup>4.</sup> Actual hardware programming times. This does not include software overhead.

<sup>5.</sup> Typical Bank programming time assumes that all cells are programmed in a single pulse. In reality some cells will require more than one pulse, adding a small overhead to total bank programming time (see "Initial Max" column).

## 3.15.3 Start-up/Switch-off timings

Table 35. Start-up time/Switch-off time

| Symbol                  |    | _ | C Parameter Conditions <sup>(1)</sup>          |                   |     | Value |     |      |  |

|-------------------------|----|---|------------------------------------------------|-------------------|-----|-------|-----|------|--|

| Symbol                  |    | ) | ratametei                                      | Conditions        | Min | Тур   | Max | Unit |  |

| T <sub>FLARSTEXIT</sub> | СС | Т | Delay for Flash module to exit reset mode      | Code flash memory | _   | _     | 125 |      |  |

|                         | C  | Т |                                                | Data flash memory | _   | _     | 125 |      |  |

| T <sub>FLALPEXIT</sub>  | СС | D | Delay for Flash module to exit low-power mode  | Code flash memory | _   | _     | 0.5 | 110  |  |

| T <sub>FLAPDEXIT</sub>  | CC | Т | Delay for Flash module to exit power-down mode | Code flash memory | _   | _     | 30  | μs   |  |

|                         | C  | Т | mode                                           | Data flash memory | _   | _     | 30  |      |  |

| T <sub>FLALPENTRY</sub> | СС | D | Delay for Flash module to enter low-power mode | Code flash memory | _   | _     | 0.5 |      |  |

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 to 125 °C, unless otherwise specified.

# 3.16 AC specifications

## 3.16.1 Pad AC specifications

Table 36. Output pin transition times

| Sum             | Symbol C |   | Parameter                                        | Co                      | nditions <sup>(1)</sup>                           | Value |     |     | - Unit |

|-----------------|----------|---|--------------------------------------------------|-------------------------|---------------------------------------------------|-------|-----|-----|--------|

| Sylli           |          |   | raiailletei                                      | rarameter Conc          |                                                   | Min   | Тур | Max | Onit   |

|                 |          | D |                                                  | C <sub>L</sub> = 25 pF  |                                                   |       |     | 50  |        |

|                 |          | Т |                                                  | C <sub>L</sub> = 50 pF  | $V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0 | _     | _   | 100 |        |

|                 | СС       | D | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 100 pF |                                                   | _     | _   | 125 | ns     |

| t <sub>tr</sub> | CC       | D | SLOW configuration                               | C <sub>L</sub> = 25 pF  |                                                   | _     | _   | 40  | 115    |

|                 |          | Т |                                                  | C <sub>L</sub> = 50 pF  | $V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1 | _     | _   | 50  |        |

|                 |          | D |                                                  | C <sub>L</sub> = 100 pF |                                                   | _     | _   | 75  |        |

|                 |          | D |                                                  | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 \text{ V} \pm 10\%,$                | _     | _   | 10  |        |

|                 |          | Т |                                                  | C <sub>L</sub> = 50 pF  | PAD3V5V = 0                                       | _     | _   | 20  |        |

|                 | СС       | D | Output transition time output pin <sup>(2)</sup> | C <sub>L</sub> = 100 pF | SIUL.PCRx.SRC = 1                                 | _     | _   | 40  |        |

| t <sub>tr</sub> | CC       | D | MEDIUM configuration                             | C <sub>L</sub> = 25 pF  | = 25 pF $V_{DD} = 3.3 \text{ V} \pm 10\%$         |       | _   | 12  | ns     |

|                 |          | Т |                                                  | C <sub>L</sub> = 50 pF  | PAD3V5V = 1                                       | _     | _   | 25  |        |

|                 |          | D |                                                  | C <sub>L</sub> = 100 pF | SIUL.PCRx.SRC = 1                                 | _     | _   | 40  |        |

Value Conditions<sup>(1)</sup> Symbol **Parameter** Unit Min Тур Max  $C_{L} = 25 pF$ 4  $V_{DD} = 5.0 \text{ V} \pm 10\%,$ PAD3V5V = 0 $C_L = 50 pF$ 6 SIUL.PCRx.SRC = 1  $C_1 = 100 pF$ 12 Output transition time output pin<sup>(2)</sup> CC D ns  $t_{tr}$ FAST configuration  $C_{L} = 25 \text{ pF}$ 4  $V_{DD} = 3.3 \text{ V} \pm 10\%,$  $C_{L} = 50 \text{ pF}$ PAD3V5V = 17 SIUL.PCRx.SRC = 1  $C_1 = 100 pF$ 12  $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$ Symmetric transition time, same drive t<sub>SYM</sub> CC T ns strength between N and P transistor  $V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$ 5

Table 36. Output pin transition times (continued)

- 1.  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 °C to  $T_{A~MAX}$ , unless otherwise specified.

- 2.  $C_L$  includes device and package capacitances ( $C_{PKG} < 5 pF$ ).

- 3. Transition timing of both positive and negative slopes will differ maximum 50%.

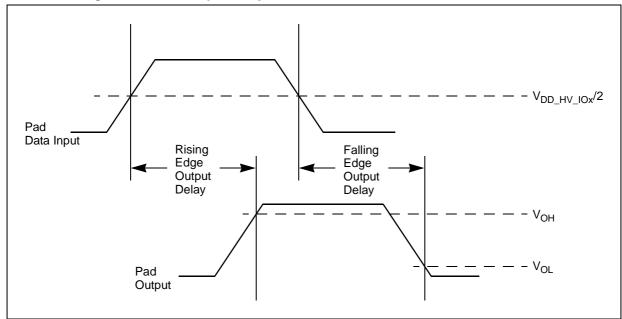

Figure 19. Pad output delay

# 3.17 AC timing characteristics

# 3.17.1 RESET pin characteristics

The SPC560P34/SPC560P40 implements a dedicated bidirectional RESET pin.

Figure 23. JTAG test access port timing

# 4 Package characteristics

# 4.1 ECOPACK<sup>®</sup>

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK® is an ST trademark.

# 4.2.2 LQFP64 mechanical outline drawing

Figure 39. LQFP64 package mechanical drawing

Table 43. LQFP64 package mechanical data

|        |      |      | Dimer | nsions |        |        |

|--------|------|------|-------|--------|--------|--------|

| Symbol |      | mm   |       |        |        |        |

|        | Min  | Тур  | Max   | Min    | Тур    | Max    |

| А      | _    | _    | 1.6   | _      | _      | 0.063  |

| A1     | 0.05 | _    | 0.15  | 0.002  | _      | 0.0059 |

| A2     | 1.35 | 1.4  | 1.45  | 0.0531 | 0.0551 | 0.0571 |

| b      | 0.17 | 0.22 | 0.27  | 0.0067 | 0.0087 | 0.0106 |

| С      | 0.09 | _    | 0.2   | 0.0035 | _      | 0.0079 |

| D      | 11.8 | 12   | 12.2  | 0.4646 | 0.4724 | 0.4803 |

| D1     | 9.8  | 10   | 10.2  | 0.3858 | 0.3937 | 0.4016 |

| D3     | _    | 7.5  | _     | _      | 0.2953 | _      |

| Е      | 11.8 | 12   | 12.2  | 0.4646 | 0.4724 | 0.4803 |

| E1     | 9.8  | 10   | 10.2  | 0.3858 | 0.3937 | 0.4016 |

| E3     | _    | 7.5  | _     | _      | 0.2953 | _      |

| е      | _    | 0.5  | _     | _      | 0.0197 | _      |

| L      | 0.45 | 0.6  | 0.75  | 0.0177 | 0.0236 | 0.0295 |

| L1     | _    | 1    | _     | _      | 0.0394 | _      |

Table 45. Document revision history (continued)

| Date        | Revision    | Changes                                                                                                                                      |

|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 2000        |             | <ul><li>Updated the "DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 0)" section:</li></ul>                                          |

| 24 May 2040 | 2           | <ul> <li>Deleted all rows concerning RESET</li> <li>Deleted "I<sub>VPP</sub>" row</li> <li>Added the max value for C<sub>IN</sub></li> </ul> |

| 21-May-2010 | (continued) | Added the "I/O pad current specification" section                                                                                            |

|             |             | Updated the Order codes table.                                                                                                               |

|             |             | Added "Appendix A"                                                                                                                           |

|             |             | "Introduction" section:                                                                                                                      |

|             |             | Changed title (was "Overview")                                                                                                               |

|             |             | <ul> <li>Updated contents</li> </ul>                                                                                                         |

|             |             | "SPC560P34/SPC560P40 device comparison" table:                                                                                               |

|             |             | Added sentence above table                                                                                                                   |

|             |             | - Removed "FlexRay" row                                                                                                                      |

|             |             | - "FlexCAN" row: removed link to footnote 2 for SPC560P34                                                                                    |

|             |             | <ul><li>Updated "Safety port" row for SPC560P34</li><li>Updated "DSPI" row for SPC560P34</li></ul>                                           |

|             |             | "SPC560P34/SPC560P40 block diagram": added the following blocks: MC_CGM,                                                                     |

|             |             | MC_ME, MC_PCU, MC_RGM, CRC, and SSCM                                                                                                         |

|             |             | Added "SPC560P34/SPC560P40 series block summary" table                                                                                       |

|             |             | "Pin muxing" section: removed information on "Symmetric pads"                                                                                |

|             |             | "Electrical characteristics" section:                                                                                                        |

|             |             | <ul><li>Updated "Caution" note</li><li>Demoted "NVUSRO register" section to subsection of "DC electrical characteristics"</li></ul>          |

|             |             | section                                                                                                                                      |

|             |             | <ul><li>– "NVUSRO register" section: deleted "NVUSRO[WATCHDOG_EN] field description" section</li></ul>                                       |

| 23-Dec-2010 | 3           | Updated "EMI testing specifications" table "Low voltage monitor electrical characteristics" table: updated V <sub>MLVDDOK</sub> H max value  |

|             |             | "DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)" table: removed VOL_SYM, and VOH SYM rows                                        |

|             |             | "Supply current (5.0 V, NVUSRO[PAD3V5V] = 0)" table:                                                                                         |

|             |             | <ul> <li>I<sub>DD_LV_CORE</sub>, RUN—Maximum mode, 40/64 MHz: updated typ/max values</li> </ul>                                              |

|             |             | <ul> <li>I<sub>DD_LV_CORE</sub>, RUN—Airbag mode, 40/64 MHz: updated typ/max values</li> </ul>                                               |

|             |             | - I <sub>DD_LV_CORE</sub> , RUN—Maximum mode, "P" parameter classification: removed                                                          |

|             |             | - I <sub>DD_FLASH</sub> : removed rows                                                                                                       |

|             |             | - I <sub>DD_ADC</sub> , Maximum mode: updated typ/max values                                                                                 |

|             |             | - I <sub>DD_OSC</sub> : updated max value                                                                                                    |

|             |             | Updated "DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)" table "Supply current (3.3 V, NVUSRO[PAD3V5V] = 1)" table:              |

|             |             | - I <sub>DD_LV_CORE</sub> , RUN—Maximum mode, 40/64 MHz: updated typ/max values                                                              |

|             |             | <ul> <li>I<sub>DD_LV_CORE</sub>, RUN—Airbag mode, 40/64 MHz: updated typ/max values</li> </ul>                                               |

|             |             | - I <sub>DD_FLASH</sub> : removed rows                                                                                                       |

|             |             | - I <sub>DD_ADC</sub> , Maximum mode: updated typ/max values                                                                                 |

|             |             | - I <sub>DD_OSC</sub> : updated max value                                                                                                    |

|             |             | Added "I/O consumption" table Removed "I/O weight" table                                                                                     |

Table 45. Document revision history (continued)

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-Dec-2010 | 3<br>(continued) | Updated "Main oscillator electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)" table  Updated "Main oscillator electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)" table  "Input clock characteristics" table: updated f <sub>CLK</sub> max value  "PLLMRFM electrical specifications (V <sub>DDPLL</sub> = 1.08 V to 1.32 V, V <sub>SS</sub> = V <sub>SSPLL</sub> = 0 V, T <sub>A</sub> = T <sub>L</sub> to T <sub>H</sub> )" table:  - Updated supply voltage range for V <sub>DDPLL</sub> in the table title  - Updated supply voltage range for V <sub>DDPLL</sub> in the table title  - Updated f <sub>SCM</sub> max value  - Updated "16 MHz RC oscillator electrical characteristics" table  Updated "ADC conversion characteristics" table:  - T <sub>wprogram</sub> : updated initial max and max values  - T <sub>BKPRG</sub> 64 KB: updated initial max and max values  - added information about "erase time" for Data Flash  "Flash module life" table:  - P/E, 32 KB: added typ value  - P/E, 128 KB: added typ value  Replaced "Pad AC specifications (5.0 V, NVUSRO[PAD3V5V] = 0)" and "Pad AC specifications (3.3 V, INVUSRO[PAD3V5V] = 1)" tables with "Output pin transition times" table  "JTAG pin AC electrical characteristics" table:  - t <sub>TDOV</sub> : updated max value  - t <sub>TDOHZ</sub> : added min value and removed max value  "Nexus debug port timing" table: removed the rows "t <sub>MCYC</sub> ", "t <sub>MDOV</sub> ", "t <sub>MSEOV</sub> ", and "t <sub>EVTOV</sub> "  Updated "External interrupt timing (IRQ pin)" table  Updated "OsPI timing" table  Updated "Ordering information" section |