#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 64                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 20K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                              |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p40l3ceaar |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.                                                                                                                                                                                                                                                                                                                                                        | Device summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 1                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Table 2.                                                                                                                                                                                                                                                                                                                                                        | SPC560P34/SPC560P40 device comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                                    |

| Table 3.                                                                                                                                                                                                                                                                                                                                                        | SPC560P40 device configuration differences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 9                                                                                                                  |

| Table 4.                                                                                                                                                                                                                                                                                                                                                        | SPC560P34/SPC560P40 series block summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |

| Table 5.                                                                                                                                                                                                                                                                                                                                                        | Supply pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33                                                                                                                   |

| Table 6.                                                                                                                                                                                                                                                                                                                                                        | System pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 34                                                                                                                 |

| Table 7.                                                                                                                                                                                                                                                                                                                                                        | Pin muxing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35                                                                                                                   |

| Table 8.                                                                                                                                                                                                                                                                                                                                                        | Parameter classifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45                                                                                                                   |

| Table 9.                                                                                                                                                                                                                                                                                                                                                        | Absolute maximum ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46                                                                                                                   |

| Table 10.                                                                                                                                                                                                                                                                                                                                                       | Recommended operating conditions (5.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48                                                                                                                   |

| Table 11.                                                                                                                                                                                                                                                                                                                                                       | Recommended operating conditions (3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49                                                                                                                   |

| Table 12.                                                                                                                                                                                                                                                                                                                                                       | LQFP thermal characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52                                                                                                                   |

| Table 13.                                                                                                                                                                                                                                                                                                                                                       | EMI testing specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54                                                                                                                   |

| Table 14.                                                                                                                                                                                                                                                                                                                                                       | ESD ratings,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54                                                                                                                   |

| Table 15.                                                                                                                                                                                                                                                                                                                                                       | Approved NPN ballast components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                                                                                                                   |

| Table 16.                                                                                                                                                                                                                                                                                                                                                       | Voltage regulator electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56                                                                                                                   |

| Table 17.                                                                                                                                                                                                                                                                                                                                                       | Low voltage monitor electrical characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

| Table 18.                                                                                                                                                                                                                                                                                                                                                       | PAD3V5V field description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59                                                                                                                   |

| Table 19.                                                                                                                                                                                                                                                                                                                                                       | DC electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

| Table 20.                                                                                                                                                                                                                                                                                                                                                       | Supply current (5.0 V, NVUSRO[PAD3V5V] = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

| Table 21.                                                                                                                                                                                                                                                                                                                                                       | DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

| Table 22.                                                                                                                                                                                                                                                                                                                                                       | Supply current (3.3 V, NVUSRO[PAD3V5V] = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                                                                   |

| T-1-1- 00                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C 4                                                                                                                  |

| Table 23.                                                                                                                                                                                                                                                                                                                                                       | I/O supply segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

| Table 23.<br>Table 24.                                                                                                                                                                                                                                                                                                                                          | I/O consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                 | I/O consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64<br>65                                                                                                             |

| Table 24.                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>I/O consumption</li> <li>Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)</li> <li>Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64<br>65<br>66                                                                                                       |

| Table 24.<br>Table 25.                                                                                                                                                                                                                                                                                                                                          | I/O consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64<br>65<br>66<br>66                                                                                                 |

| Table 24.<br>Table 25.<br>Table 26.                                                                                                                                                                                                                                                                                                                             | I/O consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64<br>65<br>66<br>66<br>66                                                                                           |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.                                                                                                                                                                                                                                                                                                                | I/O consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64<br>65<br>66<br>66<br>66<br>68                                                                                     |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.<br>Table 28.                                                                                                                                                                                                                                                                                                   | <ul> <li>I/O consumption</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64<br>65<br>66<br>66<br>66<br>68<br>73                                                                               |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.<br>Table 28.<br>Table 29.                                                                                                                                                                                                                                                                                      | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64<br>65<br>66<br>66<br>66<br>68<br>73<br>74                                                                         |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.<br>Table 28.<br>Table 29.<br>Table 30.<br>Table 31.<br>Table 32.                                                                                                                                                                                                                                               | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life                                                                                                                                                                                                                                                                                                                                                                                                              | 64<br>65<br>66<br>66<br>68<br>73<br>74<br>75                                                                         |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.<br>Table 28.<br>Table 29.<br>Table 30.<br>Table 31.<br>Table 32.<br>Table 33.                                                                                                                                                                                                                                  | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory read access timing                                                                                                                                                                                                                                                                                                                                                                      | 64<br>65<br>66<br>66<br>68<br>73<br>74<br>75<br>75                                                                   |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.<br>Table 28.<br>Table 29.<br>Table 30.<br>Table 31.<br>Table 32.<br>Table 33.<br>Table 34.                                                                                                                                                                                                                     | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory power supply DC electrical characteristics                                                                                                                                                                                                                                                                                                                                              | 64<br>65<br>66<br>66<br>68<br>73<br>74<br>75<br>75<br>75                                                             |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.<br>Table 28.<br>Table 29.<br>Table 30.<br>Table 31.<br>Table 32.<br>Table 33.                                                                                                                                                                                                                                  | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory power supply DC electrical characteristics         Start-up time/Switch-off time                                                                                                                                                                                                                                                                                                        | 64<br>66<br>66<br>68<br>73<br>74<br>75<br>75<br>75<br>75                                                             |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.<br>Table 28.<br>Table 29.<br>Table 30.<br>Table 31.<br>Table 32.<br>Table 33.<br>Table 34.                                                                                                                                                                                                                     | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory power supply DC electrical characteristics         Start-up time/Switch-off time         Output pin transition times                                                                                                                                                                                                                                                                    | 64<br>66<br>66<br>68<br>73<br>74<br>75<br>75<br>75<br>76<br>76                                                       |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.<br>Table 28.<br>Table 30.<br>Table 30.<br>Table 31.<br>Table 32.<br>Table 33.<br>Table 34.<br>Table 35.<br>Table 36.<br>Table 37.                                                                                                                                                                              | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory power supply DC electrical characteristics         Start-up time/Switch-off time         Output pin transition times         RESET electrical characteristics                                                                                                                                                                                                                           | 64<br>65<br>66<br>66<br>68<br>73<br>73<br>75<br>75<br>75<br>75<br>76<br>76<br>79                                     |

| Table 24.<br>Table 25.<br>Table 26.<br>Table 27.<br>Table 28.<br>Table 29.<br>Table 30.<br>Table 31.<br>Table 32.<br>Table 33.<br>Table 34.<br>Table 35.<br>Table 36.                                                                                                                                                                                           | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory power supply DC electrical characteristics         Start-up time/Switch-off time         Output pin transition times         RESET electrical characteristics                                                                                                                                                                                                                           | 64<br>65<br>66<br>66<br>68<br>73<br>74<br>75<br>75<br>75<br>75<br>76<br>79<br>80                                     |

| Table 24.         Table 25.         Table 26.         Table 27.         Table 28.         Table 30.         Table 30.         Table 31.         Table 33.         Table 33.         Table 34.         Table 35.         Table 36.         Table 37.         Table 38.         Table 39.                                                                         | I/O consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64<br>65<br>66<br>66<br>68<br>73<br>75<br>75<br>75<br>75<br>76<br>76<br>79<br>80<br>82                               |

| Table 24.         Table 25.         Table 26.         Table 27.         Table 28.         Table 29.         Table 30.         Table 31.         Table 31.         Table 33.         Table 33.         Table 33.         Table 34.         Table 35.         Table 36.         Table 37.         Table 38.         Table 39.         Table 39.         Table 30. | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory power supply DC electrical characteristics         Start-up time/Switch-off time         Output pin transition times         RESET electrical characteristics                                                                                                                                                                                                                           | 64<br>65<br>66<br>66<br>68<br>73<br>75<br>75<br>75<br>75<br>76<br>76<br>79<br>80<br>82                               |

| Table 24.         Table 25.         Table 26.         Table 27.         Table 28.         Table 29.         Table 30.         Table 31.         Table 32.         Table 33.         Table 34.         Table 35.         Table 36.         Table 37.         Table 38.         Table 39.         Table 30.                                                       | I/O consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\begin{array}{c} 64\\ 65\\ 66\\ 66\\ 66\\ 73\\ 75\\ 75\\ 75\\ 76\\ 76\\ 79\\ 80\\ 82\\ 84\\ 85\\ \end{array}$       |

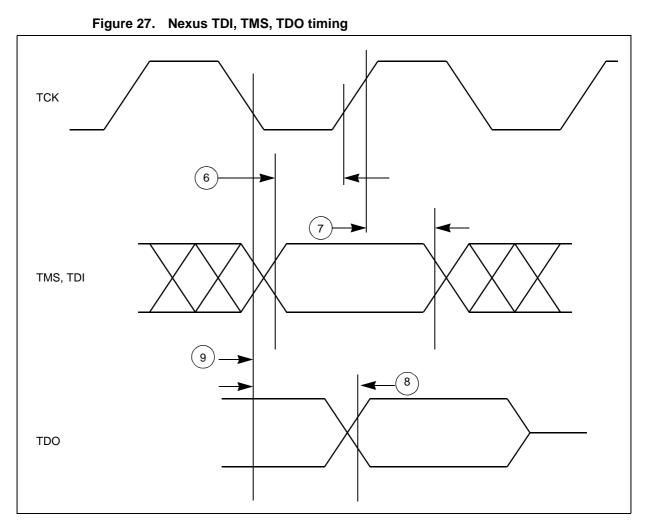

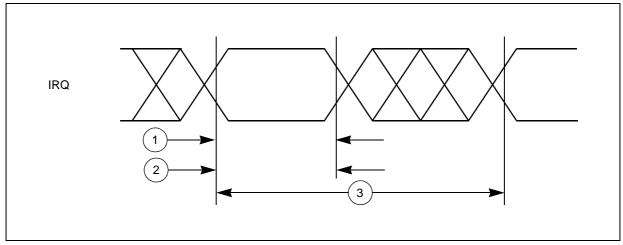

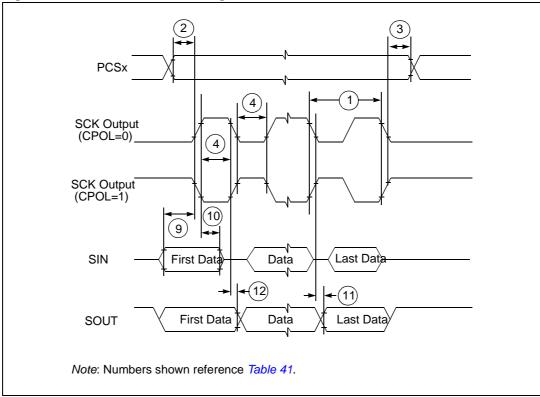

| Table 24.         Table 25.         Table 26.         Table 27.         Table 28.         Table 29.         Table 30.         Table 31.         Table 32.         Table 33.         Table 34.         Table 35.         Table 36.         Table 37.         Table 38.         Table 39.         Table 40.         Table 41.         Table 42.                   | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory read access timing         Flash memory power supply DC electrical characteristics         Start-up time/Switch-off time         Output pin transition times         RESET electrical characteristics         JTAG pin AC electrical characteristics         Nexus debug port timing         DSPI timing         LQFP100 package mechanical data                                        | $\begin{array}{c} 64\\ 65\\ 66\\ 66\\ 68\\ 73\\ 75\\ 75\\ 75\\ 76\\ 76\\ 79\\ 80\\ 82\\ 84\\ 85\\ 93\\ \end{array}$  |

| Table 24.         Table 25.         Table 26.         Table 27.         Table 28.         Table 29.         Table 30.         Table 30.         Table 31.         Table 33.         Table 34.         Table 35.         Table 36.         Table 37.         Table 38.         Table 39.         Table 40.         Table 41.         Table 42.         Table 43. | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory read access timing         Flash memory power supply DC electrical characteristics         Start-up time/Switch-off time         Output pin transition times         RESET electrical characteristics         JTAG pin AC electrical characteristics         Nexus debug port timing         DSPI timing         LQFP100 package mechanical data         LQFP64 package mechanical data | $\begin{array}{c} 64\\ 65\\ 66\\ 66\\ 73\\ 74\\ 75\\ 75\\ 76\\ 76\\ 79\\ 80\\ 82\\ 84\\ 85\\ 93\\ 94\\ \end{array}$  |

| Table 24.         Table 25.         Table 26.         Table 27.         Table 28.         Table 29.         Table 30.         Table 31.         Table 32.         Table 33.         Table 34.         Table 35.         Table 36.         Table 37.         Table 38.         Table 39.         Table 40.         Table 41.         Table 42.                   | I/O consumption         Main oscillator output electrical characteristics (5.0 V, NVUSRO[PAD3V5V] = 0)         Main oscillator output electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)         Input clock characteristics         FMPLL electrical characteristics         16 MHz RC oscillator electrical characteristics         ADC conversion characteristics         Program and erase specifications         Flash memory module life         Flash memory read access timing         Flash memory power supply DC electrical characteristics         Start-up time/Switch-off time         Output pin transition times         RESET electrical characteristics         JTAG pin AC electrical characteristics         Nexus debug port timing         DSPI timing         LQFP100 package mechanical data                                        | 64<br>65<br>66<br>66<br>68<br>73<br>75<br>75<br>75<br>75<br>76<br>76<br>79<br>80<br>82<br>84<br>85<br>93<br>94<br>97 |

| Block                                         | Function                                                                                                                                                                                                                         |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pulse width modulator<br>(FlexPWM)            | Contains four PWM submodules, each of which capable of controlling a single half-bridge power stage and two fault input channels                                                                                                 |

| Reset generation module<br>(MC_RGM)           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                    |

| Static random-access memory<br>(SRAM)         | Provides storage for program code, constants, and variables                                                                                                                                                                      |

| System integration unit lite (SIUL)           | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration         |

| System status and configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable |

| System timer module (STM)                     | Provides a set of output compare events to support AUTOSAR <sup>(1)</sup> and operating system tasks                                                                                                                             |

| System watchdog timer (SWT)                   | Provides protection from runaway code                                                                                                                                                                                            |

| Wakeup unit (WKPU)                            | Supports up to 18 external sources that can generate interrupts or wakeup events, of which 1 can cause non-maskable interrupt requests or wakeup events                                                                          |

### Table 4. SPC560P34/SPC560P40 series block summary (continued)

1. AUTOSAR: AUTomotive Open System ARchitecture (see www.autosar.org)

## **1.5** Feature details

### 1.5.1 High performance e200z0 core processor

The e200z0 Power Architecture core provides the following features:

- High performance e200z0 core processor for managing peripherals and interrupts

- Single issue 4-stage pipeline in-order execution 32-bit Power Architecture CPU

- Harvard architecture

- Variable length encoding (VLE), allowing mixed 16- and 32-bit instructions

- Results in smaller code size footprint

- Minimizes impact on performance

- Branch processing acceleration using lookahead instruction buffer

- Load/store unit

- 1-cycle load latency

- Misaligned access support

- No load-to-use pipeline bubbles

- Thirty-two 32-bit general purpose registers (GPRs)

- Separate instruction bus and load/store bus Harvard architecture

- Hardware vectored interrupt support

- Reservation instructions for implementing read-modify-write constructs

- Long cycle time instructions, except for guarded loads, do not increase interrupt latency

- Extensive system development support through Nexus debug port

- Non-maskable interrupt support

### 1.5.2 Crossbar switch (XBAR)

The XBAR multi-port crossbar switch supports simultaneous connections between three master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 32-bit data bus width.

The crossbar allows for two concurrent transactions to occur from any master port to any slave port; but one of those transfers must be an instruction fetch from internal flash memory. If a slave port is simultaneously requested by more than one master port, arbitration logic will select the higher priority master and grant it ownership of the slave port. All other masters requesting that slave port will be stalled until the higher priority master completes its transactions. Requesting masters will be treated with equal priority and will be granted access a slave port in round-robin fashion, based upon the ID of the last master to be granted access.

The flash memory module provides the following features:

- As much as 320 KB flash memory

- 6 blocks (32 KB + 2×16 KB + 32 KB + 32 KB + 128 KB) code flash memory

- 4 blocks (16 KB + 16 KB + 16 KB + 16 KB) data flash memory

- Full Read-While-Write (RWW) capability between code flash memory and data flash memory

- Four 128-bit wide prefetch buffers to provide single cycle in-line accesses (prefetch buffers can be configured to prefetch code or data or both)

- Typical flash memory access time: no wait-state for buffer hits, 2 wait-states for page buffer miss at 64 MHz

- Hardware managed flash memory writes handled by 32-bit RISC Krypton engine

- Hardware and software configurable read and write access protections on a per-master basis

- Configurable access timing allowing use in a wide range of system frequencies

- Multiple-mapping support and mapping-based block access timing (up to 31 additional cycles) allowing use for emulation of other memory types

- Software programmable block program/erase restriction control

- Erase of selected block(s)

- Read page sizes

- Code flash memory: 128 bits (4 words)

- Data flash memory: 32 bits (1 word)

- ECC with single-bit correction, double-bit detection for data integrity

- Code flash memory: 64-bit ECC

- Data flash memory: 32-bit ECC

- Embedded hardware program and erase algorithm

- Erase suspend and program abort

- Censorship protection scheme to prevent flash memory content visibility

- Hardware support for EEPROM emulation

### 1.5.5 Static random access memory (SRAM)

The SPC560P34/SPC560P40 SRAM module provides up to 20 KB of general-purpose memory.

The SRAM module provides the following features:

- Supports read/write accesses mapped to the SRAM from any master

- Up to 20 KB general purpose SRAM

- Supports byte (8-bit), half word (16-bit), and word (32-bit) writes for optimal use of memory

- Typical SRAM access time: no wait-state for reads and 32-bit writes; 1 wait-state for 8and 16-bit writes if back-to-back with a read to same memory block

### 2.2.3 Pin multiplexing

Table 7 defines the pin list and muxing for the SPC560P34/SPC560P40 devices.

Each row of *Table 7* shows all the possible ways of configuring each pin, via alternate functions. The default function assigned to each pin after reset is the ALTO function.

SPC560P34/SPC560P40 devices provide three main I/O pad types, depending on the associated functions:

- *Slow pads* are the most common, providing a compromise between transition time and low electromagnetic emission.

- *Medium pads* provide fast enough transition for serial communication channels with controlled current to reduce electromagnetic emission.

- *Fast pads* provide maximum speed. They are used for improved NEXUS debugging capability.

Medium and Fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance. For more information, see "Pad AC Specifications" in the device datasheet.

| Port | PCR             | Alternate                   | Functions | Peripheral <sup>(3)</sup> | I/O                           | Pad sp  | Pad speed <sup>(5)</sup> |        | Pin     |  |  |

|------|-----------------|-----------------------------|-----------|---------------------------|-------------------------------|---------|--------------------------|--------|---------|--|--|

| pin  | register        | function <sup>(1),(2)</sup> | Functions | Peripheral                | direc-<br>tion <sup>(4)</sup> | SRC = 0 | SRC = 1                  | 64-pin | 100-pin |  |  |

|      | Port A (16-bit) |                             |           |                           |                               |         |                          |        |         |  |  |

|      |                 | ALT0                        | GPIO[0]   | SIUL                      | I/O                           |         |                          |        |         |  |  |

|      |                 | ALT1                        | ETC[0]    | eTimer_0                  | I/O                           |         |                          |        |         |  |  |

| A[0] | PCR[0]          | ALT2                        | SCK       | DSPI_2                    | I/O                           | Slow    | Medium                   | —      | 51      |  |  |

|      |                 | ALT3                        | F[0]      | FCU_0                     | 0                             |         |                          |        |         |  |  |

|      |                 | —                           | EIRQ[0]   | SIUL                      | Ι                             |         |                          |        |         |  |  |

|      |                 | ALT0                        | GPIO[1]   | SIUL                      | I/O                           |         |                          |        |         |  |  |

|      |                 | ALT1                        | ETC[1]    | eTimer_0                  | I/O                           |         |                          |        |         |  |  |

| A[1] | PCR[1]          | ALT2                        | SOUT      | DSPI_2                    | 0                             | Slow    | Medium                   | —      | 52      |  |  |

|      |                 | ALT3                        | F[1]      | FCU_0                     | 0                             |         |                          |        |         |  |  |

|      |                 | —                           | EIRQ[1]   | SIUL                      | Ι                             |         |                          |        |         |  |  |

|      |                 | ALT0                        | GPIO[2]   | SIUL                      | I/O                           |         |                          |        |         |  |  |

|      |                 | ALT1                        | ETC[2]    | eTimer_0                  | I/O                           |         |                          |        |         |  |  |

|      |                 | ALT2                        | —         | —                         | _                             |         |                          |        |         |  |  |

| A[2] | PCR[2]          | ALT3                        | A[3]      | FlexPWM_0                 | 0                             | Slow    | Medium                   | —      | 57      |  |  |

|      |                 | —                           | SIN       | DSPI_2                    | I                             |         |                          |        |         |  |  |

|      |                 | —                           | ABS[0]    | MC_RGM                    | I                             |         |                          |        |         |  |  |

|      |                 | —                           | EIRQ[2]   | SIUL                      | Ι                             |         |                          |        |         |  |  |

|      |                 | ALT0                        | GPIO[3]   | SIUL                      | I/O                           |         |                          |        |         |  |  |

|      | A[3] PCR[3]     | ALT1                        | ETC[3]    | eTimer_0                  | I/O                           |         |                          |        |         |  |  |

| A[3] |                 | ALT2                        | CS0       | DSPI_2                    | I/O                           | Slow    | Medium                   | 41     | 64      |  |  |

| A[3] |                 | ALT3                        | B[3]      | FlexPWM_0                 | 0                             | SIUW    | Weululli                 | 41     | 04      |  |  |

|      |                 | —                           | ABS[1]    | MC_RGM                    | I                             |         |                          |        |         |  |  |

|      |                 | —                           | EIRQ[3]   | SIUL                      | Ι                             |         |                          |        |         |  |  |

| Table 7. | Pin muxing     |

|----------|----------------|

|          | i ili ilianiig |

| Port | PCR      | Alternate                   | Functions | Peripheral <sup>(3)</sup> l/O<br>direc- |                               | Pad sp  | beed <sup>(5)</sup> | Pin    |         |

|------|----------|-----------------------------|-----------|-----------------------------------------|-------------------------------|---------|---------------------|--------|---------|

| pin  | register | function <sup>(1),(2)</sup> | Functions | Peripheral                              | direc-<br>tion <sup>(4)</sup> | SRC = 0 | SRC = 1             | 64-pin | 100-pin |

|      |          | ALT0                        | GPIO[68]  | SIUL                                    |                               |         |                     |        |         |

|      |          | ALT1                        | —         | —                                       |                               |         |                     |        |         |

| E[4] | PCR[68]  | ALT2                        | —         | —                                       | Input only                    | —       | —                   | —      | 44      |

|      |          | ALT3                        | —         | —                                       |                               |         |                     |        |         |

|      |          | —                           | AN[7]     | ADC_0                                   |                               |         |                     |        |         |

|      |          | ALT0                        | GPIO[69]  | SIUL                                    |                               |         |                     |        |         |

|      |          | ALT1                        | —         | —                                       |                               |         |                     |        |         |

| E[5] | PCR[69]  | ALT2                        | —         | —                                       | Input only                    | —       | —                   | —      | 43      |

|      |          | ALT3                        | —         | —                                       |                               |         |                     |        |         |

|      |          | —                           | AN[8]     | ADC_0                                   |                               |         |                     |        |         |