Welcome to **E-XFL.COM**

<u>Embedded - Microcontrollers - Application</u>

<u>Specific</u>: Tailored Solutions for Precision and Performance

**Embedded - Microcontrollers - Application Specific**

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

What Are <u>Embedded - Microcontrollers - Application Specific</u>?

Application charific microcontrollars are angineered to

| Details                 |                                                                               |

|-------------------------|-------------------------------------------------------------------------------|

| Product Status          | Active                                                                        |

| Applications            | Capacitive Sensing                                                            |

| Core Processor          | M8C                                                                           |

| Program Memory Type     | FLASH (16kB)                                                                  |

| Controller Series       | CY8C20xx7/S                                                                   |

| RAM Size                | 2K x 8                                                                        |

| Interface               | I <sup>2</sup> C, SPI                                                         |

| Number of I/O           | 29                                                                            |

| Voltage - Supply        | 1.71V ~ 5.5V                                                                  |

| Operating Temperature   | -40°C ~ 85°C                                                                  |

| Mounting Type           | Surface Mount                                                                 |

| Package / Case          | 32-UFQFN Exposed Pad                                                          |

| Supplier Device Package | 32-QFN (5x5)                                                                  |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c20447s-24lqxit |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Designing with PSoC Designer**

The PSoC development process can be summarized in the following four steps:

- 1. Select User Modules

- 2. Configure User Modules

- 3. Organize and Connect

- 4. Generate and Verify

#### Select Components

PSoC Designer provides a library of pre-built, pre-tested hardware peripheral components called "user modules". User modules make selecting and implementing peripheral devices, both analog and digital, simple.

### **Configure Components**

Each of the User Modules you select establishes the basic register settings that implement the selected function. They also provide parameters and properties that allow you to tailor their precise configuration to your particular application. The user module parameters permit you to establish the pulse width and duty cycle. Configure the parameters and properties to correspond to your chosen application. Enter values directly or by selecting values from drop-down menus. All the user modules are documented in datasheets that may be viewed directly in PSoC Designer or on the Cypress website. These user module datasheets explain the internal operation of the User Module and provide performance specifications. Each datasheet describes the use of each user module parameter, and other information you may need to successfully implement your design.

## **Organize and Connect**

You build signal chains at the chip level by interconnecting user modules to each other and the I/O pins. You perform the selection, configuration, and routing so that you have complete control over all on-chip resources.

#### Generate, Verify, and Debug

When you are ready to test the hardware configuration or move on to developing code for the project, you perform the "Generate Configuration Files" step. This causes PSoC Designer to generate source code that automatically configures the device to your specification and provides the software for the system. The generated code provides application programming interfaces (APIs) with high-level functions to control and respond to hardware events at run time and interrupt service routines that you can adapt as needed.

A complete code development environment allows you to develop and customize your applications in C, assembly language, or both.

## 30-ball WLCSP (24 Sensing Inputs)

Table 4. Pin Definitions – CY8C20767, CY8C20747 30-ball Part Pinout (WLCSP) [20]

|         | Туре                |                |                   |                                                                              |

|---------|---------------------|----------------|-------------------|------------------------------------------------------------------------------|

| Pin No. | Digital             | Analog         | Name              | Description                                                                  |

| A1      | IOH                 | ı              | P0[2]             | Driven Shield Output (optional)                                              |

| A2      | IOH                 | I              | P0[6]             |                                                                              |

| A3      | Pow                 | er             | $V_{\mathrm{DD}}$ | Supply voltage                                                               |

| A4      | IOH                 | I              | P0[1]             | Integrating Input                                                            |

| A5      | I/O                 | I              | P2[7]             |                                                                              |

| B1      | I/O                 | I              | P4[2]             |                                                                              |

| B2      | IOH                 | I              | P0[0]             | Driven Shield Output (optional)                                              |

| B3      | IOH                 | I              | P0[4]             |                                                                              |

| B4      | IOH                 | I              | P0[3]             | Integrating Input                                                            |

| B5      | I/O                 | I              | P2[5]             | Crystal Output (Xout)                                                        |

| C1      | I/O                 | I              | P2[2]             | Driven Shield Output (optional)                                              |

| C2      | I/O                 | I              | P2[4]             | Driven Shield Output (optional)                                              |

| C3      | I/O                 | I              | P0[7]             |                                                                              |

| C4      | IOH                 | I              | P3[2]             |                                                                              |

| C5      | I/O                 | I              | P2[3]             | Crystal Input (Xin)                                                          |

| D1      | I/O                 | ı              | P2[0]             |                                                                              |

| D2      | I/O                 | I              | P3[0]             |                                                                              |

| D3      | I/O                 | I              | P3[1]             |                                                                              |

| D4      | I/O                 | I              | P3[3]             |                                                                              |

| D5      | I/O                 | I              | P2[1]             |                                                                              |

| E1      | Inpu                | ıt             | XRES              | Active high external reset with internal pull-down <sup>[21]</sup>           |

| E2      | IOHR                | I              | P1[6]             |                                                                              |

| E3      | IOHR                | I              | P1[4]             | Optional external clock input (EXT CLK)                                      |

| E4      | IOHR                | ı              | P1[7]             | I <sup>2</sup> C SCL, SPI SS                                                 |

| E5      | IOHR                | I              | P1[5]             | I <sup>2</sup> C SDA, SPI MISO                                               |

| F1      | IOHR                | I              | P1[2]             | Driven Shield Output (optional)                                              |

| F2      | IOHR                | I              | P1[0]             | ISSP DATA <sup>[22]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[23]</sup> |

| F3      | Pow                 | er             | V <sub>SS</sub>   | Supply ground <sup>[24]</sup>                                                |

| F4      | IOHR                | I              | P1[1]             | ISSP CLK <sup>[22]</sup> , I <sup>2</sup> C SCL, SPI<br>MOSI                 |

| F5      | IOHR                | I              | P1[3]             | SPI CLK                                                                      |

| LEGEND: | A = Analog, I = Inp | out, O = Outpu | t, OH = 5 mA High | h Output Drive, R = Regulated Output                                         |

<sup>20. 27</sup> GPIOs = 24 pins for capacitive sensing+2 pins for I<sup>2</sup>C + 1 pin for modulator capacitor.

<sup>21.</sup> The internal pull down is 5KOhm.

<sup>22.</sup> On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I<sup>2</sup>C bus. Use alternate pins if you encounter issues.

<sup>23.</sup> Alternate SPI clock.

<sup>24.</sup> All VSS pins should be brought out to one common GND plane.

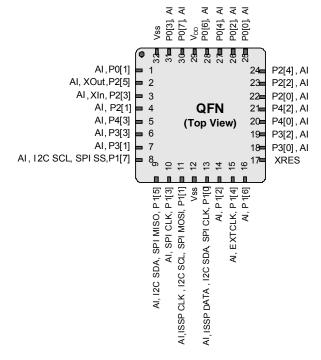

# 32-pin QFN (25 Sensing Inputs)[25]

Table 5. Pin Definitions - CY8C20437, CY8C20447/S, CY8C20467/S [26]

| Pin | Τ\      | <b>/pe</b> |          |                                                                              |

|-----|---------|------------|----------|------------------------------------------------------------------------------|

| No. | Digital | Analog     | Name     | Description                                                                  |

| 1   | IOH     | 1          | P0[1]    | Integrating input                                                            |

| 2   | I/O     |            | P2[5]    | Crystal output (XOut)                                                        |

| 3   | I/O     | ı          | P2[3]    | Crystal input (XIn)                                                          |

| 4   | I/O     | ı          | P2[1]    |                                                                              |

| 5   | I/O     | ı          | P4[3]    |                                                                              |

| 6   | I/O     |            | P3[3]    |                                                                              |

| 7   | I/O     |            | P3[1]    |                                                                              |

| 8   | IOHR    | ı          | P1[7]    | I <sup>2</sup> C SCL, SPI SS                                                 |

| 9   | IOHR    |            | P1[5]    | I <sup>2</sup> C SDA, SPI MISO                                               |

| 10  | IOHR    |            | P1[3]    | SPI CLK.                                                                     |

| 11  | IOHR    | I          | P1[1]    | ISSP CLK <sup>[27]</sup> , I <sup>2</sup> C SCL, SPI<br>MOSI.                |

| 12  | Po      | wer        | $V_{SS}$ | Ground connection <sup>[30]</sup>                                            |

| 13  | IOHR    | I          | P1[0]    | ISSP DATA <sup>[27]</sup> , I <sup>2</sup> C SDA,<br>SPI CLK <sup>[28]</sup> |

| 14  | IOHR    | I          | P1[2]    | Driven Shield Output (optional)                                              |

| 15  | IOHR    | I          | P1[4]    | Optional external clock input (EXTCLK)                                       |

| 16  | IOHR    |            | P1[6]    |                                                                              |

| 17  | In      | put        | XRES     | Active high external reset with internal pull-down <sup>[29]</sup>           |

| 18  | I/O     |            | P3[0]    |                                                                              |

| 19  | I/O     | ı          | P3[2]    |                                                                              |

| 20  | I/O     |            | P4[0]    |                                                                              |

| 21  | I/O     | ı          | P4[2]    |                                                                              |

| 22  | I/O     |            | P2[0]    |                                                                              |

| 23  | I/O     |            | P2[2]    | Driven Shield Output (optional)                                              |

| 24  | I/O     | ı          | P2[4]    | Driven Shield Output (optional)                                              |

| 25  | IOH     | ı          | P0[0]    | Driven Shield Output (optional)                                              |

| 26  | IOH     |            | P0[2]    | Driven Shield Output (optional)                                              |

| 27  | IOH     |            | P0[4]    |                                                                              |

| 28  | IOH     | ı          | P0[6]    |                                                                              |

| 29  | Po      | wer        | $V_{DD}$ |                                                                              |

| 30  | IOH     | I          | P0[7]    |                                                                              |

| 31  | IOH     |            | P0[3]    | Integrating input                                                            |

| 32  | Po      | wer        | $V_{SS}$ | Ground connection <sup>[30]</sup>                                            |

| СР  | Po      | wer        | $V_{SS}$ | Center pad must be connected to ground                                       |

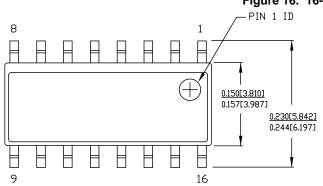

Figure 6. CY8C20437, CY8C20447/S, CY8C20467/S Device

**LEGEND** A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output.

#### Notes

- 25. The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

- it must be electrically floated and not connected to any other signal.

26. 28 GPIOs = 25 pins for capacitive sensing+2 pins for I<sup>2</sup>C + 1 pin for modulator capacitor.

- 27. On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I<sup>2</sup>C bus. Use alternate pins if you encounter issues.

- 28. Alternate SPI clock.

- 29. The internal pull down is 5KOhm.

- 30. All VSS pins should be brought out to one common GND plane.

# **Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8C20x37/47/67/S PSoC devices. For the latest electrical specifications, confirm that you have the most recent datasheet by visiting the web at http://www.cypress.com/psoc.

Absolute Maximum Ratings

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

**Table 7. Absolute Maximum Ratings**

| Symbol           | Description                                | Conditions                                                                                                                                                                          | Min                   | Тур | Max            | Units |

|------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|----------------|-------|

| T <sub>STG</sub> | Storage temperature                        | Higher storage temperatures reduce data retention time. Recommended Storage Temperature is +25 °C ± 25 °C. Extended duration storage temperatures above 85 °C degrades reliability. | <b>–</b> 55           | +25 | +125           | °C    |

| $V_{DD}$         | Supply voltage relative to V <sub>SS</sub> | -                                                                                                                                                                                   | -0.5                  | -   | +6.0           | V     |

| V <sub>IO</sub>  | DC input voltage                           | -                                                                                                                                                                                   | V <sub>SS</sub> – 0.5 | _   | $V_{DD} + 0.5$ | V     |

| $V_{IOZ}$        | DC voltage applied to tristate             | -                                                                                                                                                                                   | V <sub>SS</sub> – 0.5 | _   | $V_{DD} + 0.5$ | V     |

| I <sub>MIO</sub> | Maximum current into any port pin          | -                                                                                                                                                                                   | -25                   | -   | +50            | mA    |

| ESD              | Electro static discharge voltage           | Human body model ESD                                                                                                                                                                | 2000                  | -   | -              | V     |

| LU               | Latch up current                           | In accordance with JESD78 standard                                                                                                                                                  | ı                     | ı   | 200            | mA    |

## **Operating Temperature**

**Table 8. Operating Temperature**

| Symbol         | Description                  | Conditions                                                                                                                                                                           | Min             | Тур | Max  | Units |

|----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|------|-------|

| T <sub>A</sub> | Ambient temperature          | -                                                                                                                                                                                    | -40             | _   | +85  | °C    |

| T <sub>C</sub> | Commercial temperature range | -                                                                                                                                                                                    | 0               |     | 70   | °C    |

| TJ             | Operational die temperature  | The temperature rise from ambient to junction is package specific. See the Thermal Impedances on page 30. The user must limit the power consumption to comply with this requirement. | <del>-4</del> 0 | -   | +100 | °C    |

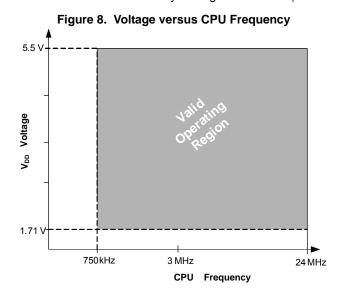

## **DC Chip-Level Specifications**

Table 9 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 9. DC Chip-Level Specifications

| Symbol                                  | Description                                   | Conditions                                                                                                                                  | Min  | Тур  | Max  | Units |

|-----------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>DD</sub> <sup>[37, 38, 39]</sup> | Supply voltage                                | See Table 14 on page 17.                                                                                                                    | 1.71 | _    | 5.50 | V     |

| I <sub>DD24</sub>                       | Supply current, IMO = 24 MHz                  | Conditions are $V_{DD} \le 3.0$ V, $T_A$ = 25 °C, CPU = 24 MHz. CapSense running at 12 MHz, no I/O sourcing current                         | -    | 2.88 | 4.00 | mA    |

| I <sub>DD12</sub>                       | Supply current, IMO = 12 MHz                  | Conditions are $V_{DD} \le 3.0 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$ , CPU = 12 MHz. CapSense running at 12 MHz, no I/O sourcing current | _    | 1.71 | 2.60 | mA    |

| I <sub>DD6</sub>                        | Supply current, IMO = 6 MHz                   | Conditions are $V_{DD} \le 3.0$ V, $T_A = 25$ °C, CPU = 6 MHz. CapSense running at 6 MHz, no I/O sourcing current                           | -    | 1.16 | 1.80 | mA    |

| I <sub>SB0</sub> [40, 41, 42, 43]       | Deep sleep current                            | $V_{DD} \le 3.0 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$ , I/O regulator turned off                                                         | -    | 0.10 | 1.1  | μΑ    |

| I <sub>SB1</sub> [40, 41, 42, 43]       | Standby current with POR, LVD and sleep timer | $V_{DD} \le 3.0 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$ , I/O regulator turned off                                                         | _    | 1.07 | 1.50 | μА    |

| I <sub>SBI2C</sub> [40, 41, 42, 43]     | Standby current with I <sup>2</sup> C enabled | Conditions are $V_{DD}$ = 3.3 V, $T_A$ = 25 °C and CPU = 24 MHz                                                                             | _    | 1.64 | -    | μА    |

## Notes

<sup>Notes

37. When V<sub>DD</sub> remains in the range from 1.71 V to 1.9 V for more than 50 µs, the slew rate when moving from the 1.71 V to 1.9 V range to greater than 2 V must be slower than 1 V/500 µs to avoid triggering POR. The only other restriction on slew rates for any other voltage range or transition is the SR<sub>POWER\_UP</sub> parameter.

38. If powering down in standby sleep mode, to properly detect and recover from a V<sub>DD</sub> brown out condition any of the following actions must be taken:

a. Bring the device out of sleep before powering down.

b. Assure that V<sub>DD</sub> falls below 100 mV before powering back up.

c. Set the No Buzz bit in the OSC\_CR0 register to keep the voltage monitoring circuit powered during sleep.

d. Increase the buzz rate to assure that the falling edge of V<sub>DD</sub> is captured. The rate is configured through the PSSDC bits in the SLP\_CFG register. For the referenced registers, refer to the Technical Reference Manual. In deep sleep/standby sleep mode, additional low power voltage monitoring circuitry allows V<sub>DD</sub> brown out conditions to be detected and resets the device when V<sub>DD</sub> goes lower than 1.1 V at edge rates slower than 1 V/ms.

39. For proper CapSense block functionality, if the drop in V<sub>DD</sub> exceeds 5% of the base V<sub>DD</sub>, the rate at which V<sub>DD</sub> drops should not exceed 200 mV/s. Base V<sub>DD</sub> can</sup>

<sup>39.</sup> For proper CapSense block functionality, if the drop in VDD exceeds 5% of the base VDD, the rate at which VDD drops should not exceed 200 mV/s. Base VDD can be between 1.8 V and 5.5 V.

<sup>40.</sup> Errata: When programmable timer 0 is used in "one-shot" mode by setting bit 1 of register 0,B0h (PT0\_CFG), and the timer interrupt is used to wake the device from sleep, the interrupt service routine (ISR) may be executed twice. For more information, see the "Errata" on page 37.

41. Errata: When in sleep mode, if a GPIO interrupt happens simultaneously with a Timer0 or Sleep Timer interrupt, the GPIO interrupt may be missed, and the corresponding GPIO ISR not run. For more information, see the "Errata" on page 37.

<sup>42.</sup> Errata: If an interrupt is posted a short time (within 2.5 CPU cycles) before firmware commands the device to sleep, the interrupt will be missed. For more information, see the "Errata" on page 37.

<sup>43.</sup> Errata: Device wakes up from sleep when an analog interrupt is trigger. For more information, see the "Errata" on page 37.

## **DC GPIO Specifications**

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 1.71 V to 2.4 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 10. 3.0 V to 5.5 V DC GPIO Specifications

| Symbol                | Description                                                                  | Conditions                                                                                                                                                                                | Min                    | Тур   | Max            | Units |

|-----------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|----------------|-------|

| R <sub>PU</sub>       | Pull-up resistor                                                             | -                                                                                                                                                                                         | 4                      | 5.60  | 8              | kΩ    |

| V <sub>OH1</sub>      | High output voltage<br>Port 2 or 3 pins                                      | $I_{OH} \leq$ 10 $\mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                     | V <sub>DD</sub> – 0.20 | -     | -              | V     |

| V <sub>OH2</sub>      | High output voltage<br>Port 2 or 3 Pins                                      | I <sub>OH</sub> = 1 mA, maximum of 20 mA source current in all I/Os                                                                                                                       | V <sub>DD</sub> – 0.90 | -     | _              | V     |

| V <sub>OH3</sub>      | High output voltage Port 0 or 1 pins with LDO regulator Disabled for port 1  | $I_{OH}$ < 10 $\mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                        | V <sub>DD</sub> – 0.20 | -     | -              | ٧     |

| V <sub>OH4</sub>      | High output voltage Port 0 or 1 pins with LDO regulator Disabled for port 1  | I <sub>OH</sub> = 5 mA, maximum of 20 mA source current in all I/Os                                                                                                                       | V <sub>DD</sub> – 0.90 | -     | -              | V     |

| V <sub>OH5</sub>      | High output voltage<br>Port 1 Pins with LDO Regulator Enabled for<br>3 V out | I <sub>OH</sub> < 10 μA, V <sub>DD</sub> > 3.1 V, maximum of 4 I/Os all sourcing 5 mA                                                                                                     | 2.85                   | 3.00  | 3.30           | ٧     |

| V <sub>OH6</sub>      | High output voltage Port 1 pins with LDO regulator enabled for 3 V out       | I <sub>OH</sub> = 5 mA, V <sub>DD</sub> > 3.1 V, maximum of 20 mA source current in all I/Os                                                                                              | 2.20                   | -     | _              | V     |

| V <sub>OH7</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out            | $I_{OH}$ < 10 $\mu$ A, $V_{DD}$ > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                      | 2.35                   | 2.50  | 2.75           | V     |

| V <sub>OH8</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out            | I <sub>OH</sub> = 2 mA, V <sub>DD</sub> > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                              | 1.90                   | _     | -              | V     |

| V <sub>OH9</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out            | $I_{OH}$ < 10 $\mu$ A, $V_{DD}$ > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                      | 1.60                   | 1.80  | 2.10           | V     |

| V <sub>OH10</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out            | I <sub>OH</sub> = 1 mA, V <sub>DD</sub> > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                              | 1.20                   | -     | -              | V     |

| V <sub>OL</sub>       | Low output voltage                                                           | $I_{OL}$ = 25 mA, $V_{DD}$ > 3.3 V, maximum of 60 mA sink current on even port pins (for example, P0[2] and P1[4]) and 60 mA sink current on odd port pins (for example, P0[3] and P1[5]) | -                      | -     | 0.75           | ٧     |

| V <sub>IL</sub>       | Input low voltage                                                            | -                                                                                                                                                                                         | _                      | _     | 0.80           | V     |

| V <sub>IH</sub>       | Input high voltage                                                           | -                                                                                                                                                                                         | V <sub>DD</sub> × 0.65 | _     | $V_{DD} + 0.7$ | V     |

| V <sub>H</sub>        | Input hysteresis voltage                                                     | -                                                                                                                                                                                         | _                      | 80    | _              | mV    |

| I <sub>IL</sub>       | Input leakage (Absolute Value)                                               | -                                                                                                                                                                                         | _                      | 0.001 | 1              | μΑ    |

| C <sub>PIN</sub>      | Pin capacitance                                                              | Package and pin dependent Temp = 25 °C                                                                                                                                                    | 0.50                   | 1.70  | 7              | pF    |

|                       |                                                                              | threshold voltage of Port1 input                                                                                                                                                          | 0.8                    | V     | _              | -     |

| V <sub>IHLVT3.3</sub> |                                                                              | threshold voltage of Port1 input                                                                                                                                                          | 1.4                    | _     | _              | V     |

| V <sub>ILLVT5.5</sub> | Input Low Voltage with low threshold enable set, Enable for Port1            | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                        | 0.8                    | V     | _              |       |

| V <sub>IHLVT5.5</sub> | Input High Voltage with low threshold enable set, Enable for Port1           | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                        | 1.7                    | _     | _              | V     |

## Note

<sup>44.</sup> Errata: Pull-up resistor on port1 pins cannot be connected to a voltage that is greater than 0.7 V higher than CY8C20xx7/S VDD. For more information see item #7 in "Errata" on page 37.

Table 12. 1.71 V to 2.4 V DC GPIO Specifications (continued)

| Symbol           | Description                    | Conditions                                                                                                                                                                                | Min                    | Тур  | Max                    | Units |

|------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------------------|-------|

| V <sub>OL</sub>  | Low output voltage             | I <sub>OL</sub> = 5 mA, maximum of 20 mA sink<br>current on even port pins (for example,<br>P0[2] and P1[4]) and 30 mA sink<br>current on odd port pins (for example,<br>P0[3] and P1[5]) | -                      | -    | 0.40                   | V     |

| $V_{IL}$         | Input low voltage              | -                                                                                                                                                                                         | -                      | _    | 0.30 × V <sub>DD</sub> | V     |

| V <sub>IH</sub>  | Input high voltage             | -                                                                                                                                                                                         | 0.65 × V <sub>DD</sub> | _    | -                      | V     |

| $V_{H}$          | Input hysteresis voltage       | -                                                                                                                                                                                         | -                      | 80   | -                      | mV    |

| I <sub>IL</sub>  | Input leakage (absolute value) | -                                                                                                                                                                                         | -                      | 1    | 1000                   | nA    |

| C <sub>PIN</sub> | Capacitive load on pins        | Package and pin dependent temp = 25 °C                                                                                                                                                    | 0.50                   | 1.70 | 7                      | pF    |

Table 13. GPIO Current Sink and Source Specifications

| Supply<br>Voltage | Mode   | Port 0/1 per I/O (max) | Port 2/3/4 per I/O (max) | Total Current Even Pins (max)  Total Current Odd Pins (max) |      | Units |

|-------------------|--------|------------------------|--------------------------|-------------------------------------------------------------|------|-------|

| 1.71–2.4          | Sink   | 5                      | 5                        | 20                                                          | 30   | mA    |

| 1.71-2.4          | Source | 2                      | 0.5                      | 10 <sup>[45]</sup>                                          |      | mA    |

| 2.4–3.0           | Sink   | 10                     | 10                       | 30                                                          | 30   | mA    |

| 2.4–3.0           | Source | 2                      | 0.2                      | 10                                                          | [45] | mA    |

| 3.0–5.0           | Sink   | 25                     | 25                       | 60                                                          | 60   | mA    |

| 3.0–5.0           | Source | 5                      | 1                        | 20                                                          | [45] | mA    |

## **DC Analog Mux Bus Specifications**

Table 14 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 14. DC Analog Mux Bus Specifications

| Symbol           | Description                                            | Conditions | Min | Тур | Max | Units |

|------------------|--------------------------------------------------------|------------|-----|-----|-----|-------|

| R <sub>SW</sub>  | Switch resistance to common analog bus                 | -          | _   | _   | 800 | Ω     |

| R <sub>GND</sub> | Resistance of initialization switch to V <sub>SS</sub> | -          | _   | _   | 800 | Ω     |

The maximum pin voltage for measuring  $\rm R_{SW}$  and  $\rm R_{GND}$  is 1.8  $\rm V$

## **DC Low Power Comparator Specifications**

Table 15 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 15. DC Comparator Specifications

| Symbol             | Description                            | Conditions                                 | Min | Тур | Max | Units |

|--------------------|----------------------------------------|--------------------------------------------|-----|-----|-----|-------|

| $V_{LPC}$          | Low power comparator (LPC) common mode | Maximum voltage limited to V <sub>DD</sub> | 0.2 | 1   | 1.8 | V     |

| I <sub>LPC</sub>   | LPC supply current                     | -                                          | _   | 10  | 80  | μΑ    |

| V <sub>OSLPC</sub> | LPC voltage offset                     | -                                          | -   | 2.5 | 30  | mV    |

#### Note

45. Total current (odd + even ports)

## **AC Programming Specifications**

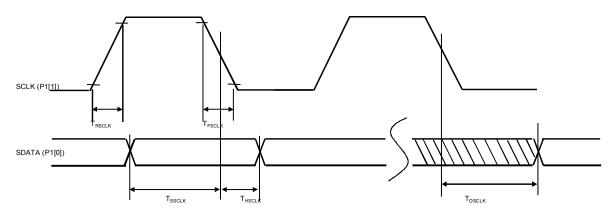

Figure 10. AC Waveform

Table 28 lists the guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

**Table 28. AC Programming Specifications**

| Symbol                               | Description                                                                            | Conditions                                                  | Min   | Тур | Max   | Units |

|--------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|-----|-------|-------|

| t <sub>RSCLK</sub>                   | Rise time of SCLK                                                                      | -                                                           | 1     | _   | 20    | ns    |

| t <sub>FSCLK</sub>                   | Fall time of SCLK                                                                      | _                                                           | 1     | _   | 20    | ns    |

| t <sub>SSCLK</sub>                   | Data setup time to falling edge of SCLK                                                | -                                                           | 40    | _   | _     | ns    |

| t <sub>HSCLK</sub>                   | Data hold time from falling edge of SCLK                                               | -                                                           | 40    | _   | _     | ns    |

| F <sub>SCLK</sub>                    | Frequency of SCLK                                                                      | _                                                           | 0     | _   | 8     | MHz   |

| t <sub>ERASEB</sub>                  | Flash erase time (block)                                                               | _                                                           | _     | _   | 18    | ms    |

| t <sub>WRITE</sub>                   | Flash block write time                                                                 | -                                                           | -     | _   | 25    | ms    |

| t <sub>DSCLK</sub>                   | Data out delay from falling edge of SCLK                                               | 3.6 < V <sub>DD</sub>                                       | _     | _   | 60    | ns    |

| t <sub>DSCLK3</sub>                  | Data out delay from falling edge of SCLK                                               | $3.0 \le V_{DD} \le 3.6$                                    | _     | _   | 85    | ns    |

| t <sub>DSCLK2</sub>                  | Data out delay from falling edge of SCLK                                               | $1.71 \le V_{DD} \le 3.0$                                   | -     | _   | 130   | ns    |

| t <sub>XRST3</sub>                   | External reset pulse width after power-up                                              | Required to enter programming mode when coming out of sleep | 300   | -   | _     | μS    |

| t <sub>XRES</sub>                    | XRES pulse length                                                                      | -                                                           | 300   | _   | -     | μS    |

| t <sub>VDDWAIT</sub> [54]            | V <sub>DD</sub> stable to wait-and-poll hold off                                       | -                                                           | 0.1   | _   | 1     | ms    |

| t <sub>VDDXRES</sub> <sup>[54]</sup> | V <sub>DD</sub> stable to XRES assertion delay                                         | -                                                           | 14.27 | _   | -     | ms    |

| t <sub>POLL</sub>                    | SDAT high pulse time                                                                   | -                                                           | 0.01  | _   | 200   | ms    |

| t <sub>ACQ</sub> <sup>[54]</sup>     | "Key window" time after a V <sub>DD</sub> ramp acquire event, based on 256 ILO clocks. | -                                                           | 3.20  | -   | 19.60 | ms    |

| t <sub>XRESINI</sub> [54]            | "Key window" time after an XRES event, based on 8 ILO clocks                           | -                                                           | 98    | _   | 615   | μS    |

Note

54. Valid from 5 to 50 °C. See the spec, CY8C20X66, CY8C20X46, CY8C20X36, CY7C643XX, CY7C604XX, CY8CTST2XX, CY8CTMG2XX, CY8C20X67, CY8C20X47, CY8C20X37, Programming Spec for more details.

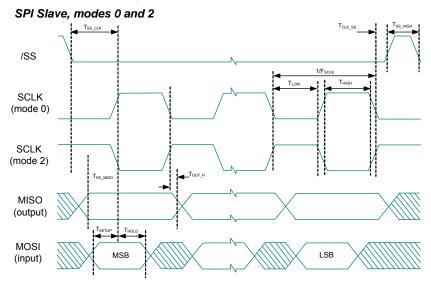

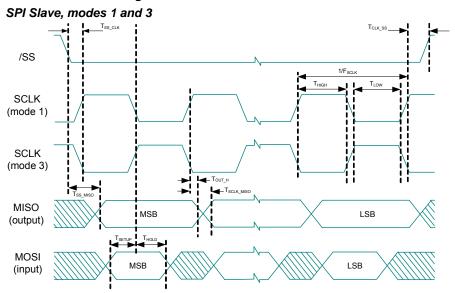

Table 31. SPI Slave AC Specifications

| Symbol                 | Description                    | Conditions | Min    | Тур | Max | Units |

|------------------------|--------------------------------|------------|--------|-----|-----|-------|

| F <sub>SCLK</sub>      | SCLK clock frequency           | _          | _      | -   | 4   | MHz   |

| t <sub>LOW</sub>       | SCLK low time                  | _          | 42     | -   | _   | ns    |

| t <sub>HIGH</sub>      | SCLK high time                 | _          | 42     | -   | _   | ns    |

| t <sub>SETUP</sub>     | MOSI to SCLK setup time        | _          | 30     | -   | _   | ns    |

| t <sub>HOLD</sub>      | SCLK to MOSI hold time         | _          | 50     | -   | _   | ns    |

| t <sub>SS_MISO</sub>   | SS high to MISO valid          | _          | _      | -   | 153 | ns    |

| t <sub>SCLK_MISO</sub> | SCLK to MISO valid             | _          | _      | _   | 125 | ns    |

| t <sub>SS_HIGH</sub>   | SS high time                   | _          | 50     | _   | _   | ns    |

| t <sub>SS_CLK</sub>    | Time from SS low to first SCLK | _          | 2/SCLK | -   | _   | ns    |

| t <sub>CLK_SS</sub>    | Time from last SCLK to SS high | _          | 2/SCLK | _   | _   | ns    |

Figure 14. SPI Slave Mode 0 and 2

Figure 15. SPI Slave Mode 1 and 3

## **Packaging Information**

This section illustrates the packaging specifications for the CY8C20x37/47/67 PSoC device, along with the thermal impedances for each package.

**Important Note** Emulation tools may require a larger area on the target PCB than the chip's footprint. For a detailed description of the emulation tools' dimensions, refer to the document titled *PSoC Emulator Pod Dimensions* at <a href="http://www.cypress.com/design/MR10161">http://www.cypress.com/design/MR10161</a>.

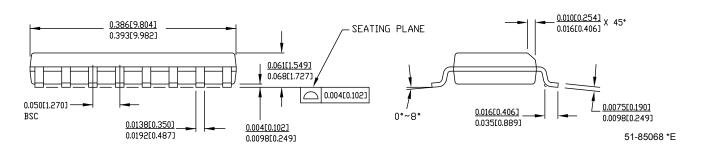

Figure 16. 16-pin (150 Mil) SOIC

#### NOTE:

- 1. DIMENSIONS IN INCHESIMM) MANK.

- 2. REFERENCE JEDEC MS-012

- 3. PACKAGE WEIGHT: refer to PMDD spec. 001-04308

| PART #  |                |  |  |  |  |

|---------|----------------|--|--|--|--|

| \$16.15 | STANDARD PKG.  |  |  |  |  |

| SZ16.15 | LEAD FREE PKG. |  |  |  |  |

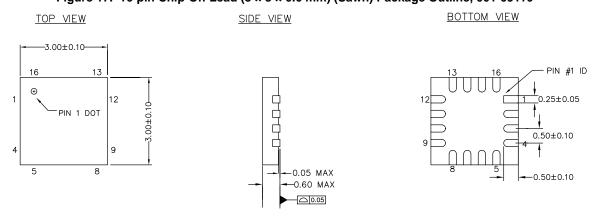

Figure 17. 16-pin Chip-On-Lead (3 x 3 x 0.6 mm) (Sawn) Package Outline, 001-09116

NOTES

1. REFERENCE JEDEC # MO-220

2. ALL DIMENSIONS ARE IN MILLIMETERS

001-09116 \*J

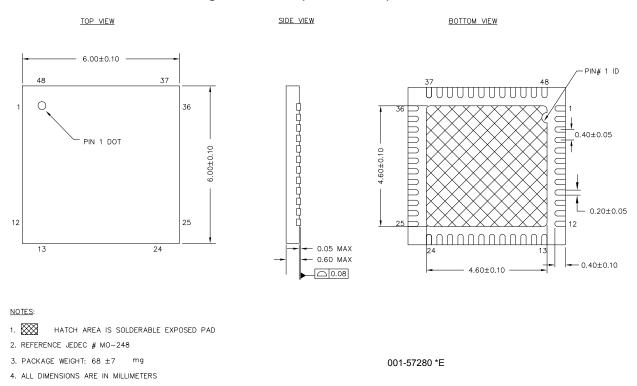

Figure 20. 48-Pin ( $6 \times 6 \times 0.6$  mm) QFN

# Important Notes

- For information on the preferred dimensions for mounting QFN packages, see the following Application Note at <a href="http://www.amkor.com/products/notes\_papers/MLFAppNote.pdf">http://www.amkor.com/products/notes\_papers/MLFAppNote.pdf</a>.

- Pinned vias for thermal conduction are not required for the low power PSoC device.

## **Thermal Impedances**

Table 32. Thermal Impedances per Package

| Package                    | Typical θ <sub>JA</sub> <sup>[57]</sup> |

|----------------------------|-----------------------------------------|

| 16-pin SOIC                | 95 °C/W                                 |

| 16-pin QFN                 | 33 °C/W                                 |

| 24-pin QFN <sup>[58]</sup> | 21 °C/W                                 |

| 32-pin QFN <sup>[58]</sup> | 20 °C/W                                 |

| 48-pin QFN <sup>[58]</sup> | 18 °C/W                                 |

| 30-ball WLCSP              | 54 °C/W                                 |

## **Capacitance on Crystal Pins**

Table 33. Typical Package Capacitance on Crystal Pins

| Package    | Package Capacitance |

|------------|---------------------|

| 32-Pin QFN | 3.2 pF              |

| 48-Pin QFN | 3.3 pF              |

## **Solder Reflow Peak Temperature**

Table 34 shows the solder reflow temperature limits that must not be exceeded.

Table 34. Solder Reflow Peak Temperature

| Package       | Maximum Peak Temperature (T <sub>C</sub> ) | Maximum Time above T <sub>C</sub> − 5 °C |

|---------------|--------------------------------------------|------------------------------------------|

| 16-pin SOIC   | 260 °C                                     | 30 seconds                               |

| 16-pin QFN    | 260 °C                                     | 30 seconds                               |

| 24-pin QFN    | 260 °C                                     | 30 seconds                               |

| 32-pin QFN    | 260 °C                                     | 30 seconds                               |

| 48-pin QFN    | 260 °C                                     | 30 seconds                               |

| 30-ball WLCSP | 260 °C                                     | 30 seconds                               |

$<sup>57.</sup> T_J = T_A + Power \times \theta_{JA}$ . 58. To achieve the thermal impedance specified for the QFN package, the center thermal pad must be soldered to the PCB ground plane.

# **Acronyms**

The following table lists the acronyms that are used in this document.

Table 36. Acronyms Used in this Document

| Acronym          | Description                             |  |  |

|------------------|-----------------------------------------|--|--|

| AC               | alternating current                     |  |  |

| ADC              | analog-to-digital converter             |  |  |

| API              | application programming interface       |  |  |

| CMOS             | complementary metal oxide semiconductor |  |  |

| CPU              | central processing unit                 |  |  |

| DAC              | digital-to-analog converter             |  |  |

| DC               | direct current                          |  |  |

| ESD              | electrostatic discharge                 |  |  |

| FSR              | full scale range                        |  |  |

| GPIO             | general purpose input/output            |  |  |

| I <sup>2</sup> C | inter-integrated circuit                |  |  |

| ICE              | in-circuit emulator                     |  |  |

| ILO              | internal low speed oscillator           |  |  |

| IMO              | internal main oscillator                |  |  |

| I/O              | input/output                            |  |  |

| ISSP             | in-system serial programming            |  |  |

| LCD              | liquid crystal display                  |  |  |

| LDO              | low dropout (regulator)                 |  |  |

| LED              | light-emitting diode                    |  |  |

| LPC              | low power comparator                    |  |  |

| LSB              | least-significant bit                   |  |  |

| LVD              | low voltage detect                      |  |  |

| MCU              | micro-controller unit                   |  |  |

| MIPS             | million instructions per second         |  |  |

| MISO             | master in slave out                     |  |  |

| MOSI             | master out slave in                     |  |  |

| MSB              | most-significant bit                    |  |  |

| OCD              | on-chip debug                           |  |  |

| PCB              | printed circuit board                   |  |  |

| POR              | power on reset                          |  |  |

| PSRR             | power supply rejection ratio            |  |  |

| PWRSYS           | power system                            |  |  |

| PSoC             | programmable system-on-chip             |  |  |

| QFN              | quad flat no-lead                       |  |  |

| SCLK             | serial I <sup>2</sup> C clock           |  |  |

| SDA              | serial I <sup>2</sup> C data            |  |  |

| SDATA            | serial ISSP data                        |  |  |

| SOIC             | small outline integrated circuit        |  |  |

| SPI              | serial peripheral interface             |  |  |

| SRAM             | static random access memory             |  |  |

| SS               | slave select                            |  |  |

| USB              | universal serial bus                    |  |  |

| WLCSP            | wafer level chip scale package          |  |  |

## **Reference Documents**

- Technical reference manual for CY20xx7 devices

- In-system Serial Programming (ISSP) protocol for 20xx7

- Host Sourced Serial Programming for 20xx7 devices

## **Document Conventions**

## **Units of Measure**

Table 37 lists all the abbreviations used to measure the PSoC devices.

Table 37. Units of Measure

| Symbol | Unit of Measure         |  |  |

|--------|-------------------------|--|--|

| °C     | degree Celsius          |  |  |

| dB     | decibel                 |  |  |

| kHz    | kilohertz               |  |  |

| ksps   | kilo samples per second |  |  |

| kΩ     | kilohm                  |  |  |

| MHz    | megahertz               |  |  |

| μΑ     | microampere             |  |  |

| μS     | microsecond             |  |  |

| mA     | milliampere             |  |  |

| mm     | millimeter              |  |  |

| ms     | millisecond             |  |  |

| mV     | millivolt               |  |  |

| nA     | nanoampere              |  |  |

| ns     | nanosecond              |  |  |

| Ω      | ohm                     |  |  |

| %      | percent                 |  |  |

| pF     | picofarad               |  |  |

| V      | volt                    |  |  |

| W      | watt                    |  |  |

### **Numeric Naming**

Hexadecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah'). Hexadecimal numbers may also be represented by a '0x' prefix, the C coding convention. Binary numbers have an appended lowercase 'b' (for example, 01010100b' or '01000011b'). Numbers not indicated by an 'h', 'b', or 0x are decimal.

## **Glossary**

Crosspoint connection Connection between any GPIO combination via analog multiplexer bus.

Differential non linearity Ideally, any two adjacent digital codes correspond to output analog voltages that are exactly

one LSB apart. Differential non-linearity is a measure of the worst case deviation from the

ideal 1 LSB step.

Hold time Hold time is the time following a clock event during which the data input to a latch or flip-

flop must remain stable in order to guarantee that the latched data is correct.

It is a serial multi-master bus used to connect low speed peripherals to MCU.

Integral nonlinearity It is a term describing the maximum deviation between the ideal output of a DAC/ADC and

the actual output level.

Latch-up current Current at which the latch-up test is conducted according to JESD78 standard (at 125

degree Celsius)

Power supply rejection ratio (PSRR) The PSRR is defined as the ratio of the change in supply voltage to the corresponding

change in output voltage of the device.

Scan The conversion of all sensor capacitances to digital values.

Setup time Period required to prepare a device, machine, process, or system for it to be ready to

function.

Signal-to-noise ratio The ratio between a capacitive finger signal and system noise.

SPI Serial peripheral interface is a synchronous serial data link standard.

#### **Errata**

This section describes the errata for the CY8C20xx7/S family. Details include errata trigger conditions, scope of impact, available workaround, and silicon revision applicability.

Contact your local Cypress Sales Representative if you have questions.

#### CY8C20xx7/S Qualification Status

Product Status: Production released.

#### CY8C20xx7/S Errata Summary

The following Errata items apply to the CY8C20xx7/S datasheet 001-69257.

#### 1. DoubleTimer0 ISR

#### **■**Problem Definition

When programmable timer 0 is used in "one-shot" mode by setting bit 1 of register 0,80h (PT0\_CFG), and the timer interrupt is used to wake the device from sleep, the interrupt service routine (ISR) may be executed twice.

#### **■**Parameters Affected

No datasheet parameters are affected.

#### ■Trigger Condition(S)

Triggered by enabling one-shot mode in the timer, and using the timer to wake from sleep mode.

#### **■**Scope of Impact

The ISR may be executed twice.

#### **■**Workaround

In the ISR, firmware should clear the one-shot bit with a statement such as "and req[B0h], FDh"

#### **■Fix Status**

Will not be fixed

#### **■**Changes

None

#### 2. Missed GPIO Interrupt

#### **■**Problem Definition

When in sleep mode, if a GPIO interrupt happens simultaneously with a Timer0 or Sleep Timer interrupt, the GPIO interrupt may be missed, and the corresponding GPIO ISR not run.

#### **■**Parameters Affected

No datasheet parameters are affected.

#### ■Trigger Condition(S)

Triggered by enabling sleep mode, then having GPIO interrupt occur simultaneously with a Timer 0 or Sleep Timer interrupt.

#### **■**Scope of Impact

The GPIO interrupt service routine will not be run.

#### ■Workaround

The system should be architected such that a missed GPIO interrupt may be detected. For example, if a GPIO is used to wake the system to perform some function, the system should detect if the function is not performed, and re-issue the GPIO interrupt. Alternatively, if a GPIO interrupt is required to wake the system, then firmware should disable the Sleep Timer and Timer0. Alternatively, the ISR's for Sleep Timer and Timer0 should manually check the state of the GPIO to determine if the host system has attempted to generate a GPIO interrupt.

#### **■Fix Status**

Will not be fixed

## ■Changes

None

## 5. Wake-up from Sleep with Hardware I2C Address match on Pins P1[0], P1[1]

#### **■**Problem Definition

I2C interface needs 20 ns hold time on SDA line with respect to falling edge of SCL, to wake-up from sleep using I2C hardware address match event.

## **■**Parameters Affected

$t_{HD:DAT}$  increased to 20 ns from 0 ns

#### ■Trigger Condition(S)

This is an issue only when all these three conditions are met:

- 1) P1.0 and P1.1 are used as I2C pins,

- 2) Wakeup from sleep with hardware address match feature is enabled, and

- 3) I2C master does not provide 20 ns hold time on SDA with respect to falling edge of SCL.

#### **■**Scope of Impact

These trigger conditions cause the device to never wake-up from sleep based on I2C address match event.

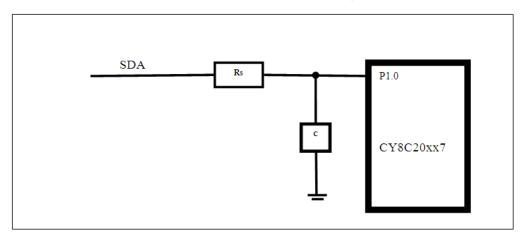

#### ■Workaround

For a design that meets all of the trigger conditions, the following suggested circuit has to be implemented as a work-around. The R and C values proposed are 100 ohm and 200 pF respectively.

## ■Fix Status

Will not be fixed

#### **■**Changes

None

## 6. I2C Port Pin Pull-up Supply Voltage

#### **■**Problem Definition

Pull-up resistor on I2C interface cannot be connected to a supply voltage that is greater than 0.7 V of CY8C20xx7/S V<sub>DD</sub>.

#### **■**Parameters Affected

None.

## ■Trigger Condition(S)

This problem occurs only when the I2C master is powered at a higher voltage than CY8C20xx7/S.

#### **■**Scope of Impact

This trigger condition will corrupt the I2C communication between the I2C host and the CY8C20xx7/S CapSense controller.

#### ■Workaround

I2C master cannot be powered at a supply voltage that is greater than 0.7 V compared to CY8C20xx7/S supply voltage.

#### **■Fix Status**

Will not be fixed

## **■**Changes

None

## 7. Port1 Pin Voltage

#### **■**Problem Definition

Pull-up resistor on port1 pins cannot be connected to a voltage that is greater than 0.7 V higher than CY8C20xx7/S V<sub>DD</sub>.

#### **■**Parameters Affected

None.

## ■Trigger Condition(S)

This problem occurs only when port1 pins are at voltage 0.7 V higher than  $V_{DD}$  of CY8C20xx7/S.

#### **■**Scope of Impact

This trigger condition will not allow CY8C20xx7/S to drive the output signal on port1 pins, input path is unaffected by this condition.

#### **■**Workaround

Port1 should not be connected to a higher voltage than V<sub>DD</sub> of CY8C20xx7/S.

#### ■Fix Status

Will not be fixed

#### **■**Changes

None

# **Document History Page**

| Document Title: CY8C20xx7/S, 1.8 V CapSense <sup>®</sup> Controller with SmartSense™ Auto-tuning 31 Buttons, 6 Sliders, Proximity Sensors<br>Sensors<br>Document Number: 001-69257 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision                                                                                                                                                                           | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| **                                                                                                                                                                                 | 3276782 | DST                | 06/27/2011         | New silicon and document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *A                                                                                                                                                                                 | 3327230 | DST                | 07/28/2011         | Changed 48-pin dimensions to 6 × 6 × 0.6 mm QFN Updated pins name in Table 3 on page 9 and removed USB column and updated dimensions for 48-pin parts in Table 35 on page 33 Updated Figure 20 on page 29 Removed ICE and Debugger sections. Removed CY3215 Development Kit and CY3280-20x66 UCC sections. Updated Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *B                                                                                                                                                                                 | 3403111 | YVA                | 10/12/2011         | Moved status from Advance to Preliminary.  Updated Ordering Information Removed the row named "48-Pin (6 × 6 mm) QFN (OCD)". Changed all 48-pin ordering code column from CY8C20XXX-24LTxx to CY8C20XXX-24LQxx. Updated 16-pin SOIC and 16-pin QFN package drawings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *C                                                                                                                                                                                 | 3473317 | DST                | 12/23/2011         | Updated Features. Updated Pinouts (Removed PSoC in captions of Figure 2, Figure 3, Figure 4 Figure 6, and Figure 7). Updated DC Chip-Level Specifications under Electrical Specifications (Updated typical value of I <sub>DD24</sub> parameter from 3.32 mA to 2.88 mA, updated typical value of I <sub>DD12</sub> parameter from 1.86 mA to 1.71 mA, updated typical value of I <sub>DD6</sub> parameter from 1.13 mA to 1.16 mA, updated maximum value of I <sub>SE</sub> parameter from 0.50 μA to 1.1 μA, added I <sub>SBI2C</sub> parameter and its details). Updated DC GPIO Specifications under Electrical Specifications (Added the parameters namely V <sub>ILLVT3.3</sub> , V <sub>IHLVT3.3</sub> , V <sub>IHLVT5.5</sub> , V <sub>IHLVT5.5</sub> and their details Table 10, added the parameters namely V <sub>ILLVT3.5</sub> , V <sub>IHLVT2.5</sub> , v <sub>IHLVT2.5</sub> and their details Table 11). Added the following sections namely DC I2C Specifications, Shield Driver D Specifications, and DC IDAC Specifications under Electrical Specifications. Updated AC Chip-Level Specifications (Added the parameter namely t <sub>JIT_IM</sub> and its details). |

| *D                                                                                                                                                                                 | 3510277 | YVA/DST            | 02/16/2012         | Added CY8C20x37/37S/47/47S/67/67S part numbers and changed title to "1. V CapSense® Controller with SmartSense™ Auto-tuning 31 Buttons, 6 Sliders" Updated Features. Modified comparator blocks in Logic Block Diagram. Replaced SmartSense with SmartSense auto-tuning. Added CY8C20xx7S part numbers in Pin Definitions. Added footnote for Table 20. Updated Table 21 and Table 22 and added Table 23. Updated F <sub>32K1</sub> min value. Updated data hold time min values. Updated CY8C206x7 part information in Table "Emulation and Programming Accessories". Updated Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *E                                                                                                                                                                                 | 3539259 | DST                | 03/01/2012         | Changed Datasheet status from Preliminary to Final. Updated all Pinouts to include Driven Shield Output (optional) information. Updated Min value for V <sub>LPC</sub> Table 15. Updated Offset and Input range in Table 16.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# **Document History Page** (continued)

| Document Title: CY8C20xx7/S, 1.8 V CapSense <sup>®</sup> Controller with SmartSense <sup>™</sup> Auto-tuning 31 Buttons, 6 Sliders, Proximity Sensors Document Number: 001-69257 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|