Welcome to **E-XFL.COM**

<u>Embedded - Microcontrollers - Application</u>

<u>Specific</u>: Tailored Solutions for Precision and Performance

Embedded - Microcontrollers - Application Specific represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

What Are <u>Embedded - Microcontrollers - Application Specific</u>?

| Details                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                    |

| Applications            | Capacitive Sensing                                                          |

| Core Processor          | M8C                                                                         |

| Program Memory Type     | FLASH (32kB)                                                                |

| Controller Series       | CY8C20xx7/S                                                                 |

| RAM Size                | 3K x 8                                                                      |

| Interface               | I <sup>2</sup> C, SPI                                                       |

| Number of I/O           | 33                                                                          |

| Voltage - Supply        | 1.71V ~ 5.5V                                                                |

| Operating Temperature   | -40°C ~ 85°C                                                                |

| Mounting Type           | Surface Mount                                                               |

| Package / Case          | 48-UFQFN Exposed Pad                                                        |

| Supplier Device Package | 48-QFN (6x6)                                                                |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c20667-24lqxi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| PSoC® Functional Overview                          | 4  |

|----------------------------------------------------|----|

| PSoC Core                                          | 4  |

| CapSense System                                    | 4  |

| Additional System Resources                        | 5  |

| Getting Started                                    |    |

| Application Notes/Design Guides                    |    |

| Development Kits                                   |    |

| Training                                           |    |

| CYPros Consultants                                 |    |

| Solutions Library                                  |    |

| Technical Support                                  | 5  |

| Designing with PSoC Designer                       |    |

| Select Components                                  | 6  |

| Configure Components                               | 6  |

| Organize and Connect                               | 6  |

| Generate, Verify, and Debug                        | 6  |

| Pinouts                                            |    |

| 16-pin SOIC (10 Sensing Inputs)                    |    |

| 16-pin QFN (10 Sensing Inputs)[9]                  |    |

| 24-pin QFN (16 Sensing Inputs)[15]                 |    |

| 30-ball WLCSP (24 Sensing Inputs)                  |    |

| 32-pin QFN (25 Sensing Inputs)[26]                 |    |

| 48-pin QFN (31 Sensing Inputs)[32]                 |    |

| Electrical Specifications                          |    |

| Absolute Maximum Ratings                           |    |

| Operating Temperature                              |    |

| DC Chip-Level Specifications                       |    |

| DC GPIO Specifications                             |    |

| DC Analog Mux Bus Specifications                   |    |

| DC Low Power Comparator Specifications             |    |

| Comparator User Module Electrical Specifications . |    |

| ADC Electrical Specifications                      |    |

| DC POR and LVD Specifications                      |    |

| DC Programming Specifications                      |    |

| DC I2C Specifications                              |    |

| Shield Driver DC Specifications                    | 20 |

| DC IDAC Specifications                  | 20 |

|-----------------------------------------|----|

| AC Chip-Level Specifications            |    |

| AC General Purpose I/O Specifications   |    |

| AC Comparator Specifications            |    |

| AC External Clock Specifications        |    |

| AC Programming Specifications           | 23 |

| AC I2C Specifications                   |    |

| Packaging Information                   | 27 |

| Thermal Impedances                      | 30 |

| Capacitance on Crystal Pins             | 30 |

| Solder Reflow Peak Temperature          | 30 |

| Development Tool Selection              | 31 |

| Software                                | 31 |

| Development Kits                        |    |

| Evaluation Tools                        |    |

| Device Programmers                      | 32 |

| Third Party Tools                       | 32 |

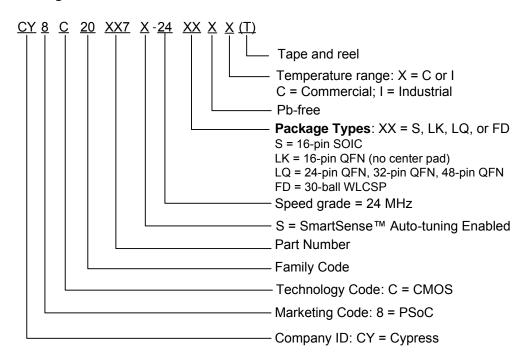

| Ordering Information                    |    |

| Ordering Code Definitions               |    |

| Acronyms                                |    |

| Reference Documents                     |    |

| Document Conventions                    |    |

| Units of Measure                        |    |

| Numeric Naming                          |    |

| Glossary                                |    |

| Errata                                  |    |

| CY8C20xx7/S Qualification Status        |    |

| CY8C20xx7/S Errata Summary              |    |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      |    |

| Products                                |    |

| PSoC® Solutions                         |    |

| Cypress Developer Community             |    |

| Leconical Support                       | 71 |

# **PSoC®** Functional Overview

The PSoC family consists of many devices with on-chip controllers. These devices are designed to replace multiple traditional MCU-based system components with one low-cost single-chip programmable component. A PSoC device includes configurable blocks of analog and digital logic, and programmable interconnect. This architecture makes it possible for you to create customized peripheral configurations, to match the requirements of each individual application. Additionally, a fast central processing unit (CPU), flash program memory, SRAM data memory, and configurable I/O are included in a range of convenient pinouts.

The architecture for this device family, as shown in the "Logic Block Diagram" on page 2, consists of three main areas:

- The core

- CapSense analog system

- System resources

A common, versatile bus allows connection between I/O and the analog system.

Each CY8C20x37/47/67/S PSoC device includes a dedicated CapSense block that provides sensing and scanning control circuitry for capacitive sensing applications. Depending on the PSoC package, up to 34 GPIOs are also included. The GPIOs provide access to the MCU and analog mux.

#### **PSoC Core**

The PSoC core is a powerful engine that supports a rich instruction set. It encompasses SRAM for data storage, an interrupt controller, sleep and watchdog timers, and IMO and ILO. The CPU core, called the M8C, is a powerful processor with speeds up to 24 MHz. The M8C is a 4-million instructions per second (MIPS), 8-bit Harvard-architecture microprocessor.

#### CapSense System

The analog system contains the capacitive sensing hardware. Several hardware algorithms are supported. This hardware performs capacitive sensing and scanning without requiring external components. The analog system is composed of the CapSense PSoC block and an internal 1 V or 1.2 V analog reference, which together support capacitive sensing of up to 31 inputs<sup>[2]</sup>. Capacitive sensing is configurable on each GPIO pin. Scanning of enabled CapSense pins is completed quickly and easily across multiple ports.

#### SmartSense™ Auto-tuning

SmartSense auto-tuning is an innovative solution from Cypress that removes manual tuning of CapSense applications. This solution is easy to use and provides robust noise immunity. It is the only auto-tuning solution that establishes, monitors, and maintains all required tuning parameters of each sensor during run time. SmartSense auto-tuning allows engineers to go from prototyping to mass production without retuning for manufacturing variations in PCB and/or overlay material properties.

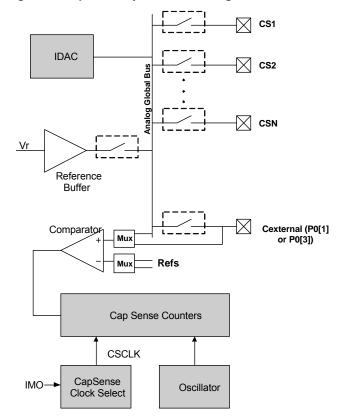

Figure 1. CapSense System Block Diagram

### Analog Multiplexer System

The analog mux bus can connect to every GPIO pin. Pins are connected to the bus individually or in any combination. The bus also connects to the analog system for analysis with the CapSense block comparator.

Switch-control logic enables selected pins to precharge continuously under hardware control. This enables capacitive measurement for applications such as touch sensing. Other multiplexer applications include:

- Complex capacitive sensing interfaces, such as sliders and touchpads.

- Chip-wide mux that allows analog input from any I/O pin.

- Crosspoint connection between any I/O pin combinations.

#### Note

2. 34 GPIOs = 31 pins for capacitive sensing+2 pins for  $I^2C + 1$  pin for modulator capacitor.

## 30-ball WLCSP (24 Sensing Inputs)

Table 4. Pin Definitions – CY8C20767, CY8C20747 30-ball Part Pinout (WLCSP) [20]

|         | Тур                 | е              |                   |                                                                              |

|---------|---------------------|----------------|-------------------|------------------------------------------------------------------------------|

| Pin No. | Digital             | Analog         | Name              | Description                                                                  |

| A1      | IOH                 | I              | P0[2]             | Driven Shield Output (optional)                                              |

| A2      | IOH                 | I              | P0[6]             |                                                                              |

| A3      | Pow                 | er             | $V_{\mathrm{DD}}$ | Supply voltage                                                               |

| A4      | IOH                 | ı              | P0[1]             | Integrating Input                                                            |

| A5      | I/O                 | I              | P2[7]             |                                                                              |

| B1      | I/O                 | I              | P4[2]             |                                                                              |

| B2      | IOH                 | I              | P0[0]             | Driven Shield Output (optional)                                              |

| B3      | IOH                 | I              | P0[4]             |                                                                              |

| B4      | IOH                 | I              | P0[3]             | Integrating Input                                                            |

| B5      | I/O                 | I              | P2[5]             | Crystal Output (Xout)                                                        |

| C1      | I/O                 | I              | P2[2]             | Driven Shield Output (optional)                                              |

| C2      | I/O                 | I              | P2[4]             | Driven Shield Output (optional)                                              |

| C3      | I/O                 | I              | P0[7]             |                                                                              |

| C4      | IOH                 | I              | P3[2]             |                                                                              |

| C5      | I/O                 | I              | P2[3]             | Crystal Input (Xin)                                                          |

| D1      | I/O                 | ı              | P2[0]             |                                                                              |

| D2      | I/O                 | I              | P3[0]             |                                                                              |

| D3      | I/O                 | I              | P3[1]             |                                                                              |

| D4      | I/O                 | I              | P3[3]             |                                                                              |

| D5      | I/O                 | I              | P2[1]             |                                                                              |

| E1      | Inpu                | ıt             | XRES              | Active high external reset with internal pull-down <sup>[21]</sup>           |

| E2      | IOHR                | I              | P1[6]             |                                                                              |

| E3      | IOHR                | I              | P1[4]             | Optional external clock input (EXT CLK)                                      |

| E4      | IOHR                | I              | P1[7]             | I <sup>2</sup> C SCL, SPI SS                                                 |

| E5      | IOHR                | I              | P1[5]             | I <sup>2</sup> C SDA, SPI MISO                                               |

| F1      | IOHR                | I              | P1[2]             | Driven Shield Output (optional)                                              |

| F2      | IOHR                | I              | P1[0]             | ISSP DATA <sup>[22]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[23]</sup> |

| F3      | Pow                 | er             | $V_{SS}$          | Supply ground <sup>[24]</sup>                                                |

| F4      | IOHR                | I              | P1[1]             | ISSP CLK <sup>[22]</sup> , I <sup>2</sup> C SCL, SPI<br>MOSI                 |

| F5      | IOHR                | I              | P1[3]             | SPI CLK                                                                      |

| LEGEND: | A = Analog, I = Inp | out, O = Outpu | t, OH = 5 mA High | h Output Drive, R = Regulated Output                                         |

<sup>20. 27</sup> GPIOs = 24 pins for capacitive sensing+2 pins for I<sup>2</sup>C + 1 pin for modulator capacitor.

<sup>21.</sup> The internal pull down is 5KOhm.

<sup>22.</sup> On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I<sup>2</sup>C bus. Use alternate pins if you encounter issues.

<sup>23.</sup> Alternate SPI clock.

<sup>24.</sup> All VSS pins should be brought out to one common GND plane.

## **DC GPIO Specifications**

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , 2.4 V to 3.0 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 1.71 V to 2.4 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 10. 3.0 V to 5.5 V DC GPIO Specifications

| Symbol                | Description                                                                       | Conditions                                                                                                                                                                                | Min                    | Тур   | Max            | Units |

|-----------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|----------------|-------|

| R <sub>PU</sub>       | Pull-up resistor                                                                  | -                                                                                                                                                                                         | 4                      | 5.60  | 8              | kΩ    |

| V <sub>OH1</sub>      | High output voltage<br>Port 2 or 3 pins                                           | $I_{OH} \leq$ 10 $\mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                     | V <sub>DD</sub> – 0.20 | _     | _              | V     |

| V <sub>OH2</sub>      | High output voltage<br>Port 2 or 3 Pins                                           | I <sub>OH</sub> = 1 mA, maximum of 20 mA source current in all I/Os                                                                                                                       | V <sub>DD</sub> – 0.90 | _     | _              | V     |

| V <sub>OH3</sub>      | High output voltage Port 0 or 1 pins with LDO regulator Disabled for port 1       | $I_{OH}$ < 10 $\mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                        | V <sub>DD</sub> – 0.20 | -     | -              | ٧     |

| V <sub>OH4</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator Disabled<br>for port 1 | I <sub>OH</sub> = 5 mA, maximum of 20 mA source current in all I/Os                                                                                                                       | V <sub>DD</sub> – 0.90 | -     | -              | ٧     |

| V <sub>OH5</sub>      | High output voltage<br>Port 1 Pins with LDO Regulator Enabled for<br>3 V out      | I <sub>OH</sub> < 10 μA, V <sub>DD</sub> > 3.1 V, maximum of 4 I/Os all sourcing 5 mA                                                                                                     | 2.85                   | 3.00  | 3.30           | ٧     |

| V <sub>OH6</sub>      | High output voltage Port 1 pins with LDO regulator enabled for 3 V out            | I <sub>OH</sub> = 5 mA, V <sub>DD</sub> > 3.1 V, maximum of 20 mA source current in all I/Os                                                                                              | 2.20                   | -     | _              | V     |

| V <sub>OH7</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | $I_{OH}$ < 10 $\mu$ A, $V_{DD}$ > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                      | 2.35                   | 2.50  | 2.75           | V     |

| V <sub>OH8</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | I <sub>OH</sub> = 2 mA, V <sub>DD</sub> > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                              | 1.90                   | _     | -              | V     |

| V <sub>OH9</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | $I_{OH}$ < 10 $\mu$ A, $V_{DD}$ > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                      | 1.60                   | 1.80  | 2.10           | V     |

| V <sub>OH10</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | I <sub>OH</sub> = 1 mA, V <sub>DD</sub> > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                              | 1.20                   | _     | -              | V     |

| V <sub>OL</sub>       | Low output voltage                                                                | $I_{OL}$ = 25 mA, $V_{DD}$ > 3.3 V, maximum of 60 mA sink current on even port pins (for example, P0[2] and P1[4]) and 60 mA sink current on odd port pins (for example, P0[3] and P1[5]) | -                      | _     | 0.75           | ٧     |

| V <sub>IL</sub>       | Input low voltage                                                                 | -                                                                                                                                                                                         | _                      | _     | 0.80           | V     |

| $V_{IH}$              | Input high voltage                                                                | _                                                                                                                                                                                         | V <sub>DD</sub> × 0.65 | _     | $V_{DD} + 0.7$ | V     |

| $V_{H}$               | Input hysteresis voltage                                                          | _                                                                                                                                                                                         | -                      | 80    | _              | mV    |

| I <sub>IL</sub>       | Input leakage (Absolute Value)                                                    | _                                                                                                                                                                                         | _                      | 0.001 | 1              | μΑ    |

| C <sub>PIN</sub>      | Pin capacitance                                                                   | Package and pin dependent Temp = 25 °C                                                                                                                                                    | 0.50                   | 1.70  | 7              | pF    |

| \ /                   |                                                                                   | threshold voltage of Port1 input                                                                                                                                                          | 0.8                    | V     | _              | _     |

| V <sub>IHLVT3.3</sub> |                                                                                   | threshold voltage of Port1 input                                                                                                                                                          | 1.4                    | -     | _              | V     |

| V <sub>ILLVT5.5</sub> |                                                                                   | threshold voltage of Port1 input                                                                                                                                                          | 0.8                    | V     | _              | _     |

| V <sub>IHLVT5.5</sub> | Input High Voltage with low threshold enable set, Enable for Port1                | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                        | 1.7                    | _     | _              | V     |

## Note

<sup>44.</sup> Errata: Pull-up resistor on port1 pins cannot be connected to a voltage that is greater than 0.7 V higher than CY8C20xx7/S VDD. For more information see item #7 in "Errata" on page 37.

Table 12. 1.71 V to 2.4 V DC GPIO Specifications (continued)

| Symbol           | Description                    | Conditions                                                                                                                                                                                | Min                    | Тур  | Max                    | Units |

|------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------------------|-------|

| V <sub>OL</sub>  | Low output voltage             | I <sub>OL</sub> = 5 mA, maximum of 20 mA sink<br>current on even port pins (for example,<br>P0[2] and P1[4]) and 30 mA sink<br>current on odd port pins (for example,<br>P0[3] and P1[5]) | -                      | -    | 0.40                   | V     |

| $V_{IL}$         | Input low voltage              | -                                                                                                                                                                                         | -                      | _    | 0.30 × V <sub>DD</sub> | V     |

| V <sub>IH</sub>  | Input high voltage             | -                                                                                                                                                                                         | 0.65 × V <sub>DD</sub> | _    | _                      | V     |

| $V_{H}$          | Input hysteresis voltage       | -                                                                                                                                                                                         | -                      | 80   | -                      | mV    |

| I <sub>IL</sub>  | Input leakage (absolute value) | -                                                                                                                                                                                         | -                      | 1    | 1000                   | nA    |

| C <sub>PIN</sub> | Capacitive load on pins        | Package and pin dependent temp = 25 °C                                                                                                                                                    | 0.50                   | 1.70 | 7                      | pF    |

Table 13. GPIO Current Sink and Source Specifications

| Supply<br>Voltage | Mode   | Port 0/1 per I/O (max) | Port 2/3/4 per I/O (max) | Total Current Even<br>Pins (max) | Total Current Odd<br>Pins (max) | Units              |  |    |

|-------------------|--------|------------------------|--------------------------|----------------------------------|---------------------------------|--------------------|--|----|

| 1.71–2.4          | Sink   | 5                      | 5                        | 20                               | 30                              | mA                 |  |    |

| 1.71-2.4          | Source | 2                      | 0.5                      | 10                               | 10 <sup>[45]</sup>              |                    |  |    |

| 2.4–3.0           | Sink   | 10                     | 10                       | 30                               | 30                              | mA                 |  |    |

| 2.4–3.0           | Source | 2                      | 0.2                      | 10 <sup>[45]</sup>               |                                 | 10 <sup>[45]</sup> |  | mA |

| 3.0–5.0           | Sink   | 25                     | 25                       | 60                               | 60                              | mA                 |  |    |

| 3.0–5.0           | Source | 5                      | 1                        | 20 <sup>[45]</sup>               |                                 | mA                 |  |    |

## **DC Analog Mux Bus Specifications**

Table 14 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 14. DC Analog Mux Bus Specifications

| Symbol           | Description                                            | Conditions | Min | Тур | Max | Units |

|------------------|--------------------------------------------------------|------------|-----|-----|-----|-------|

| R <sub>SW</sub>  | Switch resistance to common analog bus                 | -          | _   | _   | 800 | Ω     |

| R <sub>GND</sub> | Resistance of initialization switch to V <sub>SS</sub> | -          | _   | _   | 800 | Ω     |

The maximum pin voltage for measuring  $\rm R_{SW}$  and  $\rm R_{GND}$  is 1.8  $\rm V$

## **DC Low Power Comparator Specifications**

Table 15 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 15. DC Comparator Specifications

| Symbol             | Description                            | Conditions                                 | Min | Тур | Max | Units |

|--------------------|----------------------------------------|--------------------------------------------|-----|-----|-----|-------|

| $V_{LPC}$          | Low power comparator (LPC) common mode | Maximum voltage limited to V <sub>DD</sub> | 0.2 | 1   | 1.8 | V     |

| I <sub>LPC</sub>   | LPC supply current                     | -                                          | _   | 10  | 80  | μΑ    |

| V <sub>OSLPC</sub> | LPC voltage offset                     | -                                          | -   | 2.5 | 30  | mV    |

#### Note

45. Total current (odd + even ports)

## **Comparator User Module Electrical Specifications**

Table 16 lists the guaranteed maximum and minimum specifications. Unless stated otherwise, the specifications are for the entire device voltage and temperature operating range:  $-40~^{\circ}\text{C} \le \text{TA} \le 85~^{\circ}\text{C}$ , 1.71 V  $\le V_{DD} \le 5.5~\text{V}$ .

**Table 16. Comparator User Module Electrical Specifications**

| Symbol            | Description              | Conditions                          | Min | Тур | Max  | Units |

|-------------------|--------------------------|-------------------------------------|-----|-----|------|-------|

| T <sub>COMP</sub> | Comparator response time | 50 mV overdrive                     | _   | 70  | 100  | ns    |

| Offset            | -                        | Valid from 0.2 V to 1.5 V           | _   | 2.5 | 30   | mV    |

| Current           | -                        | Average DC current, 50 mV overdrive | -   | 20  | 80   | μA    |

| PSRR              | Supply voltage > 2 V     | Power supply rejection ratio        | _   | 80  | 80 - | dB    |

| FORK              | Supply voltage < 2 V     | Power supply rejection ratio        | -   | 40  |      | dB    |

| Input range       | _                        | _                                   | 0.2 |     | 1.5  | V     |

## **ADC Electrical Specifications**

Table 17. ADC User Module Electrical Specifications

| Symbol              | Description                  | Conditions                                                                                          | Min                    | Тур                    | Max                    | Units |

|---------------------|------------------------------|-----------------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|-------|

| Input               |                              |                                                                                                     | I.                     |                        |                        |       |

| V <sub>IN</sub>     | Input voltage range          | _                                                                                                   | 0                      | -                      | VREFADC                | V     |

| C <sub>IIN</sub>    | Input capacitance            | _                                                                                                   | _                      | _                      | 5                      | pF    |

| R <sub>IN</sub>     | Input resistance             | Equivalent switched cap input resistance for 8-, 9-, or 10-bit resolution                           | 1/(500fF × data clock) | 1/(400fF × data clock) | 1/(300fF × data clock) | Ω     |

| Reference           | <u> </u>                     |                                                                                                     |                        |                        |                        |       |

| V <sub>REFADC</sub> | ADC reference voltage        | _                                                                                                   | 1.14                   | _                      | 1.26                   | V     |

| Conversion Rate     |                              |                                                                                                     | •                      |                        |                        | •     |

| F <sub>CLK</sub>    | Data clock                   | Source is chip's internal main oscillator. See AC Chip-Level Specifications on page 21 for accuracy | 2.25                   | -                      | 6                      | MHz   |

| S8                  | 8-bit sample rate            | Data clock set to 6 MHz.<br>sample rate = 0.001/<br>(2^Resolution/Data Clock)                       | _                      | 23.43                  | -                      | ksps  |

| S10                 | 10-bit sample rate           | Data clock set to 6 MHz.<br>sample rate = 0.001/<br>(2^resolution/data clock)                       | _                      | 5.85                   | -                      | ksps  |

| DC Accuracy         |                              |                                                                                                     | •                      |                        |                        | •     |

| RES                 | Resolution                   | Can be set to 8, 9, or 10 bit                                                                       | 8                      | -                      | 10                     | bits  |

| DNL                 | Differential nonlinearity    | _                                                                                                   | -1                     | -                      | +2                     | LSB   |

| INL                 | Integral nonlinearity        | _                                                                                                   | -2                     | _                      | +2                     | LSB   |

| Е                   | Offset error                 | 8-bit resolution                                                                                    | 0                      | 3.20                   | 19.20                  | LSB   |

| E <sub>OFFSET</sub> | Oliset error                 | 10-bit resolution                                                                                   | 0                      | 12.80                  | 76.80                  | LSB   |

| E <sub>GAIN</sub>   | Gain error                   | For any resolution                                                                                  | <b>-</b> 5             | _                      | +5                     | %FSR  |

| Power               |                              |                                                                                                     |                        |                        |                        |       |

| I <sub>ADC</sub>    | Operating current            | _                                                                                                   | _                      | 2.10                   | 2.60                   | mA    |

| PSRR                | Power supply rejection ratio | PSRR (V <sub>DD</sub> > 3.0 V)                                                                      | _                      | 24                     | -                      | dB    |

| ONIX                | Tower supply rejection ratio | PSRR (V <sub>DD</sub> < 3.0 V)                                                                      | _                      | 30                     | _                      | dB    |

## **AC Chip-Level Specifications**

Table 24 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

## Table 24. AC Chip-Level Specifications

| Symbol                               | Description                                                | Conditions                                | Min                                                                                                                                                                                                                                     | Тур                                                                                                                                                                                                                                                                                                                                                             | Max                                         | Units |

|--------------------------------------|------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------|

| F <sub>IMO24</sub>                   | IMO frequency at 24 MHz Setting                            | -                                         | 22.8                                                                                                                                                                                                                                    | 24                                                                                                                                                                                                                                                                                                                                                              | 25.2                                        | MHz   |

| F <sub>IMO12</sub>                   | IMO frequency at 12 MHz setting                            | -                                         | 11.4                                                                                                                                                                                                                                    | 12                                                                                                                                                                                                                                                                                                                                                              | 12.6                                        | MHz   |

| F <sub>IMO6</sub>                    | IMO frequency at 6 MHz setting                             | -                                         | 5.7                                                                                                                                                                                                                                     | 6.0                                                                                                                                                                                                                                                                                                                                                             | 6.3                                         | MHz   |

| F <sub>CPU</sub>                     | CPU frequency                                              | -                                         | 0.75                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                               | 25.20                                       | MHz   |

| F <sub>32K1</sub>                    | ILO frequency                                              | -                                         | 15                                                                                                                                                                                                                                      | 32                                                                                                                                                                                                                                                                                                                                                              | 50                                          | kHz   |

| F <sub>32K_U</sub>                   | ILO untrimmed frequency                                    | -                                         | _                                                                                                                                                                                                                                       | 32                                                                                                                                                                                                                                                                                                                                                              | _                                           | kHz   |

| DC <sub>IMO</sub>                    | Duty cycle of IMO                                          | -                                         | 40                                                                                                                                                                                                                                      | 50                                                                                                                                                                                                                                                                                                                                                              | 60                                          | %     |

| DC <sub>ILO</sub>                    | ILO duty cycle                                             | -                                         | 40                                                                                                                                                                                                                                      | 50                                                                                                                                                                                                                                                                                                                                                              | 60                                          | %     |

| SR <sub>POWER_UP</sub>               | Power supply slew rate                                     | V <sub>DD</sub> slew rate during power-up | _                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                               | 250                                         | V/ms  |

| t <sub>XRST</sub>                    | External reset pulse width at power-up                     | After supply voltage is valid             | 1                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                               | _                                           | ms    |

| t <sub>XRST2</sub>                   | External reset pulse width after power-up <sup>[52]</sup>  | Applies after part has booted             | 10                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                               | _                                           | μS    |

|                                      | 6 MHz IMO cycle-to-cycle jitter (RMS)                      | -                                         | -                                                                                                                                                                                                                                       | 0.7                                                                                                                                                                                                                                                                                                                                                             | 12.6<br>6.3<br>25.20<br>50<br>-<br>60<br>60 | ns    |

|                                      | 6 MHz IMO long term N cycle-to-cycle jitter (RMS); N = 32  | -                                         | 22.8 24 25.2  11.4 12 12.6  5.7 6.0 6.3  0.75 - 25.20  15 32 50  - 32 -  40 50 60  40 50 60  wer-up - 250  alid 1  ooted 10  0.7 6.7  - 4.3 29.3  - 0.5 5.2  - 2.3 5.6  - 0.4 2.6  - 1.0 8.7  - 1.4 6.0                                 | ns                                                                                                                                                                                                                                                                                                                                                              |                                             |       |

|                                      | 6 MHz IMO period jitter (RMS)                              | -                                         | _                                                                                                                                                                                                                                       | 0.7                                                                                                                                                                                                                                                                                                                                                             | 3.3                                         | ns    |

|                                      | 12 MHz IMO cycle-to-cycle jitter (RMS)                     | -                                         | _                                                                                                                                                                                                                                       | 0.5                                                                                                                                                                                                                                                                                                                                                             | 25.2 N 12.6 N 6.3 N 25.20 N 50              | ns    |

| t <sub>JIT_IMO</sub> <sup>[53]</sup> | 12 MHz IMO long term N cycle-to-cycle jitter (RMS); N = 32 | -                                         | _                                                                                                                                                                                                                                       | 2.3                                                                                                                                                                                                                                                                                                                                                             | 5.6                                         | ns    |

|                                      | 12 MHz IMO period jitter (RMS)                             | -                                         | _                                                                                                                                                                                                                                       | 2.8     24     25.2       1.4     12     12.6       5.7     6.0     6.3       .75     -     25.20       15     32     50       -     32     -       40     50     60       -     -     250       1     -     -       -     0.7     6.7       -     4.3     29.3       -     0.5     5.2       -     2.3     5.6       -     1.0     8.7       -     1.4     6.0 | ns                                          |       |

|                                      | 24 MHz IMO cycle-to-cycle jitter (RMS)                     | _                                         | 22.8 24 25.2  11.4 12 12.6  5.7 6.0 6.3  0.75 - 25.20  15 32 50  - 32 -  40 50 60  40 50 60  40 50 60  aring power-up - 250  age is valid 1  thas booted 10  0.7 6.7  - 4.3 29.3  - 0.5 5.2  - 2.3 5.6  - 0.4 2.6  - 1.0 8.7  - 1.4 6.0 | ns                                                                                                                                                                                                                                                                                                                                                              |                                             |       |

|                                      | 24 MHz IMO long term N cycle-to-cycle jitter (RMS); N = 32 | -                                         | -                                                                                                                                                                                                                                       | 1.4                                                                                                                                                                                                                                                                                                                                                             | 6.0                                         | ns    |

|                                      | 24 MHz IMO period jitter (RMS)                             | _                                         | _                                                                                                                                                                                                                                       | 0.6                                                                                                                                                                                                                                                                                                                                                             | 4.0                                         | ns    |

Note

52. The minimum required XRES pulse length is longer when programming the device (see Table 28 on page 23).

53. See the Cypress Jitter Specifications application note, Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 for more information.

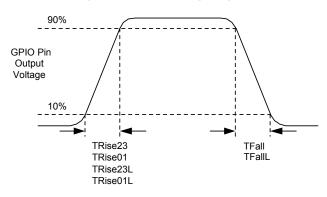

## **AC General Purpose I/O Specifications**

Table 25 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 25. AC GPIO Specifications

| Symbol               | Description                                                       | Conditions                                                          | Min | Тур | Max                                               | Units |

|----------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|-----|-----|---------------------------------------------------|-------|

| F <sub>GPIO</sub>    | GPIO operating frequency                                          | Normal strong mode Port 0, 1                                        | 0   | _   | 6 MHz for<br>1.71 V <v<sub>DD &lt; 2.40 V</v<sub> | MHz   |

| ' GPIO               | or to operating frequency                                         | Normal strong mode 1 of 0, 1                                        | 0   | _   | 12 MHz for<br>2.40 V < V <sub>DD</sub> < 5.50 V   | MHz   |

| t <sub>RISE23</sub>  | Rise time, strong mode, Cload = 50 pF<br>Ports 2 or 3             | V <sub>DD</sub> = 3.0 to 3.6 V, 10% to 90%                          | 15  | _   | 80                                                | ns    |

| t <sub>RISE23L</sub> | Rise time, strong mode low supply,<br>Cload = 50 pF, Ports 2 or 3 | V <sub>DD</sub> = 1.71 to 3.0 V, 10% to 90%                         | 15  | _   | 80                                                | ns    |

| t <sub>RISE01</sub>  | Rise time, strong mode, Cload = 50 pF<br>Ports 0 or 1             | V <sub>DD</sub> = 3.0 to 3.6 V, 10% to 90% LDO enabled or disabled  | 10  | -   | 50                                                | ns    |

| t <sub>RISE01L</sub> | Rise time, strong mode low supply,<br>Cload = 50 pF, Ports 0 or 1 | V <sub>DD</sub> = 1.71 to 3.0 V, 10% to 90% LDO enabled or disabled | 10  | -   | 80                                                | ns    |

| t <sub>FALL</sub>    | Fall time, strong mode, Cload = 50 pF all ports                   | V <sub>DD</sub> = 3.0 to 3.6 V, 10% to 90%                          | 10  | -   | 50                                                | ns    |

| t <sub>FALLL</sub>   | Fall time, strong mode low supply,<br>Cload = 50 pF, all ports    | V <sub>DD</sub> = 1.71 to 3.0 V, 10% to 90%                         | 10  | -   | 70                                                | ns    |

Figure 9. GPIO Timing Diagram

## **AC Comparator Specifications**

Table 26 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 26. AC Low Power Comparator Specifications

| Symbol           | Description                               | Conditions                                       | Min | Тур | Max | Units |

|------------------|-------------------------------------------|--------------------------------------------------|-----|-----|-----|-------|

| t <sub>LPC</sub> | Comparator response time, 50 mV overdrive | 50 mV overdrive does not include offset voltage. | -   | -   | 100 | ns    |

## **AC External Clock Specifications**

Table 27 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 27. AC External Clock Specifications

| Symbol              | Description                               | Conditions | Min   | Тур | Max   | Units |

|---------------------|-------------------------------------------|------------|-------|-----|-------|-------|

|                     | Frequency (external oscillator frequency) | _          | 0.75  | _   | 25.20 | MHz   |

| F <sub>OSCEXT</sub> | High period                               | -          | 20.60 | _   | 5300  | ns    |

| OOOLXI              | Low period                                | -          | 20.60 | _   | _     | ns    |

|                     | Power-up IMO to switch                    | 1          | 150   | -   | _     | μS    |

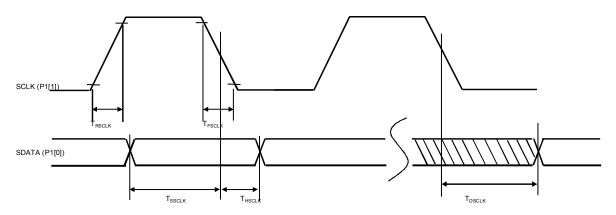

## **AC Programming Specifications**

Figure 10. AC Waveform

Table 28 lists the guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

**Table 28. AC Programming Specifications**

| Symbol                               | Description                                                                            | Conditions                                                  | Min   | Тур | Max   | Units |

|--------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|-----|-------|-------|

| t <sub>RSCLK</sub>                   | Rise time of SCLK                                                                      | -                                                           | 1     | _   | 20    | ns    |

| t <sub>FSCLK</sub>                   | Fall time of SCLK                                                                      | _                                                           | 1     | _   | 20    | ns    |

| t <sub>SSCLK</sub>                   | Data setup time to falling edge of SCLK                                                | -                                                           | 40    | _   | _     | ns    |

| t <sub>HSCLK</sub>                   | Data hold time from falling edge of SCLK                                               | -                                                           | 40    | _   | _     | ns    |

| F <sub>SCLK</sub>                    | Frequency of SCLK                                                                      | _                                                           | 0     | _   | 8     | MHz   |

| t <sub>ERASEB</sub>                  | Flash erase time (block)                                                               | _                                                           | _     | _   | 18    | ms    |

| t <sub>WRITE</sub>                   | Flash block write time                                                                 | -                                                           | -     | _   | 25    | ms    |

| t <sub>DSCLK</sub>                   | Data out delay from falling edge of SCLK                                               | 3.6 < V <sub>DD</sub>                                       | _     | _   | 60    | ns    |

| t <sub>DSCLK3</sub>                  | Data out delay from falling edge of SCLK                                               | $3.0 \le V_{DD} \le 3.6$                                    | _     | _   | 85    | ns    |

| t <sub>DSCLK2</sub>                  | Data out delay from falling edge of SCLK                                               | $1.71 \le V_{DD} \le 3.0$                                   | -     | _   | 130   | ns    |

| t <sub>XRST3</sub>                   | External reset pulse width after power-up                                              | Required to enter programming mode when coming out of sleep | 300   | -   | _     | μS    |

| t <sub>XRES</sub>                    | XRES pulse length                                                                      | -                                                           | 300   | _   | -     | μS    |

| t <sub>VDDWAIT</sub> [54]            | V <sub>DD</sub> stable to wait-and-poll hold off                                       | -                                                           | 0.1   | _   | 1     | ms    |

| t <sub>VDDXRES</sub> <sup>[54]</sup> | V <sub>DD</sub> stable to XRES assertion delay                                         | -                                                           | 14.27 | _   | _     | ms    |

| t <sub>POLL</sub>                    | SDAT high pulse time                                                                   | -                                                           | 0.01  | _   | 200   | ms    |

| t <sub>ACQ</sub> <sup>[54]</sup>     | "Key window" time after a V <sub>DD</sub> ramp acquire event, based on 256 ILO clocks. | -                                                           | 3.20  | -   | 19.60 | ms    |

| t <sub>XRESINI</sub> [54]            | "Key window" time after an XRES event, based on 8 ILO clocks                           | -                                                           | 98    | _   | 615   | μS    |

Note

54. Valid from 5 to 50 °C. See the spec, CY8C20X66, CY8C20X46, CY8C20X36, CY7C643XX, CY7C604XX, CY8CTST2XX, CY8CTMG2XX, CY8C20X67, CY8C20X47, CY8C20X37, Programming Spec for more details.

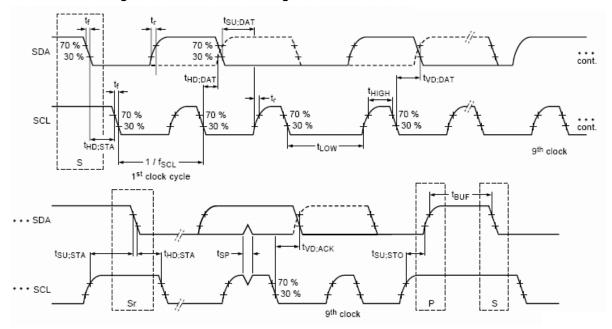

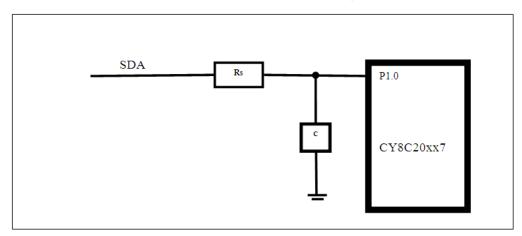

## AC I<sup>2</sup>C Specifications

Table 29 lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 29. AC Characteristics of the I<sup>2</sup>C SDA and SCL Pins

| Symbol                   | Description                                                                                 |     | ndard<br>ode | Fast Mode           |      | Units |  |

|--------------------------|---------------------------------------------------------------------------------------------|-----|--------------|---------------------|------|-------|--|

|                          |                                                                                             | Min | Max          | Min                 | Max  |       |  |

| f <sub>SCL</sub>         | SCL clock frequency                                                                         | 0   | 100          | 0                   | 400  | kHz   |  |

| t <sub>HD;STA</sub>      | Hold time (repeated) START condition. After this period, the first clock pulse is generated | 4.0 | _            | 0.6                 | -    | μs    |  |

| $t_{LOW}$                | LOW period of the SCL clock                                                                 | 4.7 | _            | 1.3                 | -    | μs    |  |

| t <sub>HIGH</sub>        | HIGH Period of the SCL clock                                                                | 4.0 | -            | 0.6                 | _    | μs    |  |

| t <sub>SU;STA</sub>      | Setup time for a repeated START condition                                                   | 4.7 | -            | 0.6                 | _    | μs    |  |

| t <sub>HD;DAT</sub> [55] | Data hold time                                                                              | 20  | 3.45         | 20                  | 0.90 | μs    |  |

| t <sub>SU;DAT</sub>      | Data setup time                                                                             | 250 | -            | 100 <sup>[56]</sup> | _    | ns    |  |

| t <sub>SU;STO</sub>      | Setup time for STOP condition                                                               | 4.0 | -            | 0.6                 | _    | μs    |  |

| t <sub>BUF</sub>         | Bus free time between a STOP and START condition                                            | 4.7 | _            | 1.3                 | _    | μs    |  |

| t <sub>SP</sub>          | Pulse width of spikes are suppressed by the input filter                                    | -   | _            | 0                   | 50   | ns    |  |

Figure 11. Definition for Timing for Fast/Standard Mode on the I<sup>2</sup>C Bus

## Notes

<sup>55.</sup> Errata: To wake up from sleep using I2C hardware address match event, I2C interface needs 20 ns hold time on SDA line with respect to falling edge of SCL. For more information see item #5 in the "Errata" on page 37.

56. A Fast-Mode I<sup>2</sup>C-bus device can be used in a standard mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU:DAT</sub> ≥ 250 ns must then be met. This automatically be the case if the device does not stretch the LOW period of the SCL signal. If such device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-Mode I<sup>2</sup>C-bus specification) before the SCL line is released.

## **Thermal Impedances**

Table 32. Thermal Impedances per Package

| Package                    | Typical θ <sub>JA</sub> <sup>[57]</sup> |

|----------------------------|-----------------------------------------|

| 16-pin SOIC                | 95 °C/W                                 |

| 16-pin QFN                 | 33 °C/W                                 |

| 24-pin QFN <sup>[58]</sup> | 21 °C/W                                 |

| 32-pin QFN <sup>[58]</sup> | 20 °C/W                                 |

| 48-pin QFN <sup>[58]</sup> | 18 °C/W                                 |

| 30-ball WLCSP              | 54 °C/W                                 |

## **Capacitance on Crystal Pins**

Table 33. Typical Package Capacitance on Crystal Pins

| Package    | Package Capacitance |

|------------|---------------------|

| 32-Pin QFN | 3.2 pF              |

| 48-Pin QFN | 3.3 pF              |

## **Solder Reflow Peak Temperature**

Table 34 shows the solder reflow temperature limits that must not be exceeded.

Table 34. Solder Reflow Peak Temperature

| Package       | Maximum Peak Temperature (T <sub>C</sub> ) | Maximum Time above T <sub>C</sub> − 5 °C |

|---------------|--------------------------------------------|------------------------------------------|

| 16-pin SOIC   | 260 °C                                     | 30 seconds                               |

| 16-pin QFN    | 260 °C                                     | 30 seconds                               |

| 24-pin QFN    | 260 °C                                     | 30 seconds                               |

| 32-pin QFN    | 260 °C                                     | 30 seconds                               |

| 48-pin QFN    | 260 °C                                     | 30 seconds                               |

| 30-ball WLCSP | 260 °C                                     | 30 seconds                               |

$<sup>57.</sup> T_J = T_A + Power \times \theta_{JA}$ . 58. To achieve the thermal impedance specified for the QFN package, the center thermal pad must be soldered to the PCB ground plane.

## **Device Programmers**

All device programmers are purchased from the Cypress Online Store.

#### CY3216 Modular Programmer

The CY3216 Modular Programmer kit features a modular programmer and the MiniProg1 programming unit. The modular programmer includes three programming module cards and supports multiple Cypress products. The kit includes:

- Modular programmer base

- Three programming module cards

- MiniProg programming unit

- PSoC Designer software CD

- Getting Started guide

- USB 2.0 cable

The CY3207ISSP is a production programmer. It includes protection circuitry and an industrial case that is more robust than the MiniProg in a production-programming environment.

CY3207ISSP In-System Serial Programmer (ISSP)

Note CY3207ISSP needs special software and is not compatible with PSoC Programmer. The kit includes:

- CY3207 programmer unit

- PSoC ISSP software CD

- 110 ~ 240 V power supply, Euro-Plug adapter

- USB 2.0 cable

### **Third Party Tools**

Several tools have been specially designed by the following third-party vendors to accompany PSoC devices during development and production. Specific details for each of these tools can be found at http://www.cypress.com under Documentation > Evaluation Boards.

# **Ordering Information**

Table 35 lists the CY8C20x37/47/67/S PSoC devices' key package features and ordering codes.

Table 35. PSoC Device Key Features and Ordering Information

| Ordering Code      | Package                    | Flash<br>(Bytes) | SRAM<br>(Bytes) | CapSense<br>Sensors | Digital I/O<br>Pins | Analog<br>Inputs [59] | XRES<br>Pin | ADC |

|--------------------|----------------------------|------------------|-----------------|---------------------|---------------------|-----------------------|-------------|-----|

| CY8C20237-24SXI    | 16-pin SOIC                | 8 K              | 1 K             | 10                  | 13                  | 13                    | Yes         | Yes |

| CY8C20247S-24SXI   | 16-pin SOIC                | 16 K             | 2 K             | 10                  | 13                  | 13                    | Yes         | Yes |

| CY8C20237-24LKXI   | 16-pin QFN                 | 8 K              | 1 K             | 10                  | 13                  | 13                    | Yes         | Yes |

| CY8C20237-24LKXIT  | 16-pin QFN (Tape and Reel) | 8 K              | 1 K             | 10                  | 13                  | 13                    | Yes         | Yes |

| CY8C20247S-24LKXI  | 16-pin QFN                 | 16 K             | 2 K             | 10                  | 13                  | 13                    | Yes         | Yes |

| CY8C20247S-24LKXIT | 16-pin QFN (Tape and Reel) | 16 K             | 2 K             | 10                  | 13                  | 13                    | Yes         | Yes |

| CY8C20337-24LQXI   | 24-pin QFN                 | 8 K              | 1 K             | 16                  | 19                  | 19                    | Yes         | Yes |

| CY8C20337-24LQXIT  | 24-pin QFN (Tape and Reel) | 8 K              | 1 K             | 16                  | 19                  | 19                    | Yes         | Yes |

| CY8C20347-24LQXI   | 24-pin QFN                 | 16 K             | 2 K             | 16                  | 19                  | 19                    | Yes         | Yes |

| CY8C20347-24LQXIT  | 24-pin QFN (Tape and Reel) | 16 K             | 2 K             | 16                  | 19                  | 19                    | Yes         | Yes |

| CY8C20347S-24LQXI  | 24-pin QFN                 | 16 K             | 2 K             | 16                  | 19                  | 19                    | Yes         | Yes |

| CY8C20347S-24LQXIT | 24-pin QFN (Tape and Reel) | 16 K             | 2 K             | 16                  | 19                  | 19                    | Yes         | Yes |

| CY8C20437-24LQXI   | 32-pin QFN                 | 8 K              | 1 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20437-24LQXIT  | 32-pin QFN (Tape and Reel) | 8 K              | 1 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20447-24LQXI   | 32-pin QFN                 | 16 K             | 2 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20447-24LQXIT  | 32-pin QFN (Tape and Reel) | 16 K             | 2 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20447S-24LQXI  | 32-pin QFN                 | 16 K             | 2 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20447S-24LQXIT | 32-pin QFN (Tape and Reel) | 16 K             | 2 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20467-24LQXI   | 32-pin QFN                 | 32 K             | 2 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20467-24LQXIT  | 32-pin QFN (Tape and Reel) | 32 K             | 2 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20467S-24LQXI  | 32-pin QFN                 | 32 K             | 2 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20467S-24LQXIT | 32-pin QFN (Tape and Reel) | 32 K             | 2 K             | 25                  | 28                  | 28                    | Yes         | Yes |

| CY8C20637-24LQXI   | 48-pin QFN                 | 8 K              | 1 K             | 31                  | 34                  | 34                    | Yes         | Yes |

| CY8C20637-24LQXIT  | 48-pin QFN (Tape and Reel) | 8 K              | 1 K             | 31                  | 34                  | 34                    | Yes         | Yes |

| CY8C20647-24LQXI   | 48-pin QFN                 | 16 K             | 2 K             | 31                  | 34                  | 34                    | Yes         | Yes |

| CY8C20647-24LQXIT  | 48-pin QFN (Tape and Reel) | 16 K             | 2 K             | 31                  | 34                  | 34                    | Yes         | Yes |

| CY8C20647S-24LQXI  | 48-pin QFN                 | 16 K             | 2 K             | 31                  | 34                  | 34                    | Yes         | Yes |

| CY8C20647S-24LQXIT | 48-pin QFN (Tape and Reel) | 16 K             | 2 K             | 31                  | 34                  | 34                    | Yes         | Yes |

| CY8C20667-24LQXI   | 48-pin QFN                 | 32 K             | 2 K             | 31                  | 34                  | 34                    | Yes         | Yes |

| CY8C20667-24LQXIT  | 48-pin QFN (Tape and Reel) | 32 K             | 2 K             | 31                  | 34                  | 34                    | Yes         | Yes |

| CY8C20667S-24LQXI  | 48-pin QFN                 | 32 K             | 2 K             | 31                  | 34                  | 34                    | Yes         | Yes |

| CY8C20667S-24LQXIT | 48-pin QFN (Tape and Reel) | 32 K             | 2 K             | 31                  | 34                  | 34                    | Yes         | Yes |

Note 59. Dual-function Digital I/O Pins also connect to the common analog mux.

Table 35. PSoC Device Key Features and Ordering Information (continued)

| Ordering Code     | Package                      |      | SRAM<br>(Bytes) | CapSense<br>Sensors | Digital I/O<br>Pins | Analog<br>Inputs [59] | XRES<br>Pin | ADC |

|-------------------|------------------------------|------|-----------------|---------------------|---------------------|-----------------------|-------------|-----|