Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 6K x 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 13x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l071cbt3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 3.15.1    | I2C bus                                                           | 0         |

|---|--------|-----------|-------------------------------------------------------------------|-----------|

|   |        | 3.15.2    | Universal synchronous/asynchronous receiver transmitter (USART) 3 | 1         |

|   |        | 3.15.3    | Low-power universal asynchronous receiver transmitter (LPUART) 3  | 1         |

|   |        | 3.15.4    | Serial peripheral interface (SPI)/Inter-integrated sound (I2S)    | 2         |

|   | 3.16   | Cyclic re | edundancy check (CRC) calculation unit                            | 2         |

|   | 3.17   | Serial w  | ire debug port (SW-DP) 3                                          | 2         |

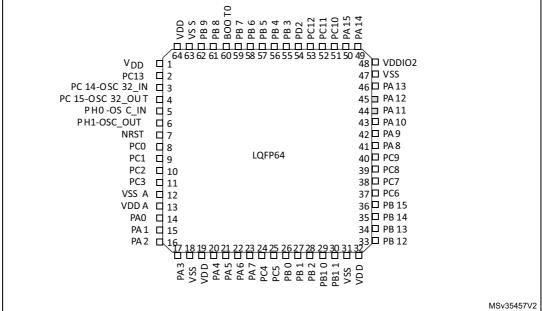

| 4 | Pin de | escripti  | ons                                                               | 3         |

| 5 | Memo   | ory map   | ping                                                              | 2         |

| 6 | Electr | rical cha | aracteristics                                                     | 3         |

|   | 6.1    | Parame    | ter conditions                                                    | 3         |

|   |        | 6.1.1     | Minimum and maximum values                                        | 3         |

|   |        | 6.1.2     | Typical values                                                    | 3         |

|   |        | 6.1.3     | Typical curves                                                    | 3         |

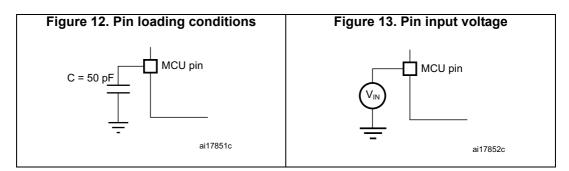

|   |        | 6.1.4     | Loading capacitor                                                 | 3         |

|   |        | 6.1.5     | Pin input voltage                                                 | 3         |

|   |        | 6.1.6     | Power supply scheme                                               | 4         |

|   |        | 6.1.7     | Current consumption measurement5                                  | 4         |

|   | 6.2    | Absolute  | e maximum ratings                                                 | 5         |

|   | 6.3    | Operatir  | ng conditions                                                     | 7         |

|   |        | 6.3.1     | General operating conditions                                      | 57        |

|   |        | 6.3.2     | Embedded reset and power control block characteristics            | 9         |

|   |        | 6.3.3     | Embedded internal reference voltage6                              | 0         |

|   |        | 6.3.4     | Supply current characteristics                                    | <b>;1</b> |

|   |        | 6.3.5     | Wakeup time from low-power mode                                   | 3         |

|   |        | 6.3.6     | External clock source characteristics                             | 5         |

|   |        | 6.3.7     | Internal clock source characteristics7                            | '9        |

|   |        | 6.3.8     | PLL characteristics                                               | 2         |

|   |        | 6.3.9     | Memory characteristics                                            | 2         |

|   |        | 6.3.10    | EMC characteristics                                               | 3         |

|   |        | 6.3.11    | Electrical sensitivity characteristics                            | 6         |

|   |        | 6.3.12    | I/O current injection characteristics                             | 7         |

|   |        | 6.3.13    | I/O port characteristics                                          | 8         |

|   |        | 6.3.14    | NRST pin characteristics                                          | 2         |

|   |        | 6.3.15    | 12-bit ADC characteristics9                                       | 3         |

|   |        |           |                                                                   |           |

DocID027101 Rev 3

| Table 3. Functionalities de | pending on the or | perating power sup | ply range (continued) |

|-----------------------------|-------------------|--------------------|-----------------------|

|                             |                   |                    |                       |

| Operating power supply         | Functionalities depending on the operating power supply range |                                  |                      |  |  |  |  |

|--------------------------------|---------------------------------------------------------------|----------------------------------|----------------------|--|--|--|--|

| range                          | ADC operation                                                 | Dynamic voltage<br>scaling range | I/O operation        |  |  |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V | Conversion time up<br>to 1.14 Msps                            | Range 1, range 2 or range 3      | Full speed operation |  |  |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V | Conversion time up<br>to 1.14 Msps                            | Range 1, range 2 or<br>range 3   | Full speed operation |  |  |  |  |

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.</li>

| Table 4. CPU frequency range | depending on d | ynamic voltage scaling |

|------------------------------|----------------|------------------------|

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

# Table 5. Functionalities depending on the working mode(from Run/active down to standby) (1)(2)

|                                           |            |       | Low-         | Low-           |     | Stop                 | S | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|-----|----------------------|---|----------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |     | Wakeup<br>capability |   | Wakeup<br>capability |

| CPU                                       | Y          |       | Y            |                |     |                      |   |                      |

| Flash memory                              | 0          | 0     | 0            | 0              |     |                      |   |                      |

| RAM                                       | Y          | Y     | Y            | Y              | Y   |                      |   |                      |

| Backup registers                          | Y          | Y     | Y            | Y              | Y   |                      | Y |                      |

| EEPROM                                    | 0          | 0     | 0            | 0              |     |                      |   |                      |

| Brown-out reset<br>(BOR)                  | 0          | 0     | 0            | 0              | 0   | 0                    | 0 | 0                    |

| DMA                                       | 0          | 0     | 0            | 0              |     |                      |   |                      |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | 0     | 0            | Ο              | 0   | 0                    | - |                      |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y     | Y            | Y              | Y   | Y                    | Y | Y                    |

| High Speed<br>Internal (HSI)              | 0          | 0     |              |                | (3) |                      |   |                      |

## 3.14.2 Low-power Timer (LPTIM)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one shot mode

- Selectable software / hardware input trigger

- Selectable clock source

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

#### 3.14.3 Basic timer (TIM6, TIM7)

These timers can be used as a generic 16-bit timebase.

#### 3.14.4 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches '0'.

#### 3.14.5 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

### 3.14.6 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

# 3.15.4 Serial peripheral interface (SPI)/Inter-integrated sound (I2S)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The USARTs with synchronous capability can also be used as SPI master.

One standard I2S interfaces (multiplexed with SPI2) is available. It can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When the I2S interfaces is configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The SPIs can be served by the DMA controller.

Refer to *Table 13* for the differences between SPI1 and SPI2.

| SPI1 | SPI2                                     |

|------|------------------------------------------|

| X    | Х                                        |

| -    | Х                                        |

| X    | Х                                        |

|      | SPI1           X           -           X |

Table 13. SPI/I2S implementation

1. X = supported.

# 3.16 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

# 3.17 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

| 1 2 3 4 5 6 7 8 9 10 11 12                                                  | 12          |

|-----------------------------------------------------------------------------|-------------|

| A (PE3) (PE1) (PB8) BOOTD (PD7) (PD5) (PB4) (PB3) (PA15) (PA14) (PA13) (PA  | PA12)       |

| ● _ ヽ_ノ`ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ                             | PA11)       |

| c (PD2) (PD0) (PC11) (VDD) (PB5) (PD2) (PD0) (PC11) (VDD) (PA               | PA10)       |

|                                                                             | PC9)        |

| _our \_/ \_/ \_/                                                            | PC6)        |

|                                                                             | vss)        |

|                                                                             | VDD)        |

| н (PC0) (NRSţ (VDD) (PD15) (PD14) (PD                                       | PD13        |

| J (VSSA) (PC1) (PC2) (PD12 (PD11) (PD                                       | PD10)       |

| K (VREF) (PC3) (PA2) (PA5) (PC4) (PD9) (PD8) (PB15) (PB14) (PB              | рв13)       |

|                                                                             | у-<br>рв12) |

| M (VDDA) (PA1) (PA4) (PA7) (PB0) (PB1) (PE7) (PE9) (PE11) (PE13) (PE14) (PE | PE15)       |

|                                                                             |             |

|                                                                             |             |

Figure 4. STM32L071xx UFBGA100 ballout - 7x 7 mm

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

DocID027101 Rev 3

|        |                         |        | Pin n  | umb     | er      |         |         |                                       |          |               |      |                                                      |                           |

|--------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|---------------|------|------------------------------------------------------|---------------------------|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                  | Additional functions      |

| 30     | 29                      | 43     | 59     | C3      | C3      | 93      | B4      | PB7                                   | I/O      | FTf           | -    | USART1_RX,<br>I2C1_SDA,<br>LPTIM1_IN2,<br>USART4_CTS | COMP2_INP,<br>VREF_PVD_IN |

| 31     | 30                      | 44     | 60     | B4      | A5      | 94      | A4      | BOOT0                                 | Ι        |               | -    | -                                                    | -                         |

| -      | -                       | 45     | 61     | B3      | B5      | 95      | A3      | PB8                                   | I/O      | FTf           | -    | I2C1_SCL                                             | -                         |

| -      | -                       | 46     | 62     | A3      | A6      | 96      | В3      | PB9                                   | I/O      | FTf           | -    | EVENTOUT,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS           | -                         |

| -      | -                       | -      | -      | -       | -       | 97      | C3      | PE0                                   | I/O      | FT            | -    | EVENTOUT                                             | -                         |

| -      | -                       | -      | -      | -       | -       | 98      | A2      | PE1                                   | I/O      | FT            | I    | EVENTOUT                                             | -                         |

| 32     | 31                      | 47     | 63     | D4      | -       | 99      | D3      | VSS                                   | S        |               | -    | -                                                    | -                         |

| -      | 32                      | 48     | 64     | E4      | A7      | 100     | C4      | VDD                                   | S        |               | -    | -                                                    | -                         |

| Table 15. STM32L071xxx | pin definition ( | continued) |

|------------------------|------------------|------------|

|------------------------|------------------|------------|

1. UFQFPN32 pinout differs from other STM32 devices except STM32L07xxx and STM32L8xxx.

Pin descriptions

DocID027101 Rev 3

5

46/136

г

|        | Table 16. Alternate functions port A |                                                                                           |                                 |                                                                                 |                   |                                                    |                                          |                                                             |                                   |  |  |

|--------|--------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------|-------------------|----------------------------------------------------|------------------------------------------|-------------------------------------------------------------|-----------------------------------|--|--|

|        |                                      | AF0                                                                                       | AF1                             | AF2                                                                             | AF3               | AF4                                                | AF5                                      | AF6                                                         | AF7                               |  |  |

| P      | ort                                  | SPI1/SPI2/I2S2/U<br>SART1/2/<br>LPUART1/LPTIM<br>1/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2<br>C1/TIM2/21 | SPI1/SPI2/I2S2/L<br>PUART1/<br>USART5/LPTIM1<br>/TIM2/3/EVENTO<br>UT/<br>SYS_AF | I2C1/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2/I2C2/U<br>SART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/E<br>VENTOUT | I2C3/LPUART1/C<br>OMP1/2/<br>TIM3 |  |  |

|        | PA0                                  | -                                                                                         | -                               | TIM2_CH1                                                                        |                   | USART2_CTS                                         | TIM2_ETR                                 | USART4_TX                                                   | COMP1_OUT                         |  |  |

|        | PA1                                  | EVENTOUT                                                                                  |                                 | TIM2_CH2                                                                        |                   | USART2_RTS_D<br>E                                  | TIM21_ETR                                | USART4_RX                                                   | -                                 |  |  |

|        | PA2                                  | TIM21_CH1                                                                                 |                                 | TIM2_CH3                                                                        |                   | USART2_TX                                          | -                                        | LPUART1_TX                                                  | COMP2_OUT                         |  |  |

|        | PA3                                  | TIM21_CH2                                                                                 |                                 | TIM2_CH4                                                                        |                   | USART2_RX                                          | -                                        | LPUART1_RX                                                  | -                                 |  |  |

|        | PA4                                  | SPI1_NSS                                                                                  | -                               | -                                                                               |                   | USART2_CK                                          | TIM22_ETR                                | -                                                           | -                                 |  |  |

|        | PA5                                  | SPI1_SCK                                                                                  | -                               | TIM2_ETR                                                                        |                   |                                                    | TIM2_CH1                                 | -                                                           | -                                 |  |  |

|        | PA6                                  | SPI1_MISO                                                                                 |                                 | TIM3_CH1                                                                        |                   | LPUART1_CTS                                        | TIM22_CH1                                | EVENTOUT                                                    | COMP1_OUT                         |  |  |

| A      | PA7                                  | SPI1_MOSI                                                                                 |                                 | TIM3_CH2                                                                        |                   | -                                                  | TIM22_CH2                                | EVENTOUT                                                    | COMP2_OUT                         |  |  |

| Port A | PA8                                  | MCO                                                                                       |                                 |                                                                                 | EVENTOUT          | USART1_CK                                          | -                                        | -                                                           | I2C3_SCL                          |  |  |

|        | PA9                                  | MCO                                                                                       |                                 | -                                                                               |                   | USART1_TX                                          | -                                        | I2C1_SCL                                                    | I2C3_SMBA                         |  |  |

|        | PA10                                 | -                                                                                         |                                 | -                                                                               |                   | USART1_RX                                          | -                                        | I2C1_SDA                                                    | -                                 |  |  |

|        | PA11                                 | SPI1_MISO                                                                                 | -                               | EVENTOUT                                                                        |                   | USART1_CTS                                         | -                                        | -                                                           | COMP1_OUT                         |  |  |

|        | PA12                                 | SPI1_MOSI                                                                                 | -                               | EVENTOUT                                                                        |                   | USART1_RTS_<br>DE                                  | -                                        | -                                                           | COMP2_OUT                         |  |  |

|        | PA13                                 | SWDIO                                                                                     | -                               |                                                                                 | -                 | -                                                  | -                                        | LPUART1_RX                                                  | -                                 |  |  |

|        | PA14                                 | SWCLK                                                                                     | -                               | -                                                                               | -                 | USART2_TX                                          | -                                        | LPUART1_TX                                                  | -                                 |  |  |

|        | PA15                                 | SPI1_NSS                                                                                  |                                 | TIM2_ETR                                                                        | EVENTOUT          | USART2_RX                                          | TIM2_CH1                                 | USART4_RTS_D<br>E                                           | -                                 |  |  |

STM32L071xx

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.6 V (for the 1.65 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 12*.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 13*.

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

## Table 39. Peripheral current consumption in Run or Sleep mode<sup>(1)</sup>

|            |                     | Typical consumption, V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C |                                                       |                                                       |                               |                      |

|------------|---------------------|----------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|----------------------|

| Peripheral |                     | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01                | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                 |

|            | CRS                 | 2.5                                                                  | 2                                                     | 2                                                     | 2                             |                      |

|            | I2C1                | 11                                                                   | 9.5                                                   | 7.5                                                   | 9                             |                      |

|            | I2C3                | 11                                                                   | 9                                                     | 7                                                     | 9                             |                      |

|            | LPTIM1              | 10                                                                   | 8.5                                                   | 6.5                                                   | 8                             |                      |

|            | LPUART1             | 8                                                                    | 6.5                                                   | 5.5                                                   | 6                             |                      |

|            | SPI2                | 9                                                                    | 4.5                                                   | 3.5                                                   | 4                             |                      |

|            | USART2              | 14.5                                                                 | 12                                                    | 9.5                                                   | 11                            |                      |

|            | USART4              | 5                                                                    | 4                                                     | 3                                                     | 5                             | µA/MHz               |

| APB1       | USART5              | 5                                                                    | 4                                                     | 3                                                     | 5                             | (f <sub>HCLK</sub> ) |

|            | TIM2                | 10.5                                                                 | 8.5                                                   | 7                                                     | 9                             |                      |

|            | TIM3                | 12                                                                   | 10                                                    | 8                                                     | 11                            |                      |

|            | TIM6                | 3.5                                                                  | 3                                                     | 2.5                                                   | 2                             |                      |

|            | TIM7                | 3.5                                                                  | 3                                                     | 2.5                                                   | 2                             |                      |

|            | WWDG                | 3                                                                    | 2                                                     | 2                                                     | 2                             |                      |

|            | ADC1 <sup>(2)</sup> | 5.5                                                                  | 5                                                     | 3.5                                                   | 4                             |                      |

|            | SPI1                | 4                                                                    | 3                                                     | 3                                                     | 2.5                           |                      |

|            | USART1              | 14.5                                                                 | 11.5                                                  | 9.5                                                   | 12                            |                      |

| APB2       | TIM21               | 7.5                                                                  | 6                                                     | 5                                                     | 5.5                           | µA/MHz               |

| APB2       | TIM22               | 7                                                                    | 6                                                     | 5                                                     | 6                             | (f <sub>HCLK</sub> ) |

|            | FIREWALL            | 1.5                                                                  | 1                                                     | 1                                                     | 0.5                           |                      |

|            | DBGMCU              | 1.5                                                                  | 1                                                     | 1                                                     | 0.5                           |                      |

|            | SYSCFG              | 2.5                                                                  | 2                                                     | 2                                                     | 1.5                           |                      |

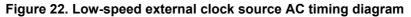

#### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 25*.

| Symbol                                     | Parameter                               | Conditions                       | Min                | Тур    | Мах                | Unit |  |

|--------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|--|

| f <sub>LSE_ext</sub>                       | User external clock source<br>frequency |                                  | 1                  | 32.768 | 1000               | kHz  |  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |  |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |  |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |  |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |  |

| C <sub>IN(LSE)</sub>                       | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |  |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |  |

| ١L                                         | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |  |

Table 43. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production

# Low-speed internal (LSI) RC oscillator

| Table 47. | LSI | oscillator | characteristics |

|-----------|-----|------------|-----------------|

|           |     |            |                 |

| Symbol                              | Parameter                                                             | Min | Тур | Max | Unit |

|-------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                         | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \leq T_A \leq 85^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                           | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                      | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

# Multi-speed internal (MSI) RC oscillator

| Symbol                                | Parameter                                                                                              | Condition   | Тур   | Max  | Unit |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------|-------------|-------|------|------|--|

|                                       |                                                                                                        | MSI range 0 | 65.5  | -    |      |  |

|                                       |                                                                                                        | MSI range 1 | 131   | -    | kHz  |  |

|                                       |                                                                                                        | MSI range 2 | 262   | -    | КПZ  |  |

| f <sub>MSI</sub>                      | Frequency after factory calibration, done at $V_{DD}$ = 3.3 V and T <sub>A</sub> = 25 °C               | MSI range 3 | 524   | -    |      |  |

|                                       |                                                                                                        | MSI range 4 | 1.05  | -    |      |  |

|                                       |                                                                                                        | MSI range 5 | 2.1   | -    | MHz  |  |

|                                       |                                                                                                        | MSI range 6 | 4.2   | -    |      |  |

| ACC <sub>MSI</sub>                    | Frequency error after factory calibration                                                              | -           | ±0.5  | -    | %    |  |

|                                       | MSI oscillator frequency drift 0 °C $\leq$ T <sub>A</sub> $\leq$ 85 °C                                 | -           | ±3    | -    |      |  |

|                                       |                                                                                                        | MSI range 0 | - 8.9 | +7.0 | %    |  |

|                                       |                                                                                                        | MSI range 1 | - 7.1 | +5.0 |      |  |

| D <sub>TEMP(MSI)</sub> <sup>(1)</sup> |                                                                                                        | MSI range 2 | - 6.4 | +4.0 |      |  |

| (                                     | MSI oscillator frequency drift<br>V <sub>DD</sub> = 3.3 V, - 40 °C $\leq$ T <sub>A</sub> $\leq$ 110 °C | MSI range 3 | - 6.2 | +3.0 |      |  |

|                                       |                                                                                                        | MSI range 4 | - 5.2 | +3.0 |      |  |

|                                       |                                                                                                        | MSI range 5 | - 4.8 | +2.0 |      |  |

|                                       |                                                                                                        | MSI range 6 | - 4.7 | +2.0 |      |  |

| D <sub>VOLT(MSI)</sub> <sup>(1)</sup> | MSI oscillator frequency drift 1.65 V $\leq$ V_{DD} $\leq$ 3.6 V, T_A = 25 °C                          | -           | -     | 2.5  | %/V  |  |

#### Table 48. MSI oscillator characteristics

# 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                                     | Conditions                                                     | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|----------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)          | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/JEDEC JS-001  | 2     | 2000                            | v    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge<br>voltage (charge device<br>model) | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/ESD STM5.3.1. | C4    | 500                             |      |

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 56. Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125$ °C conforming to JESD78A | II level A |

#### **Electrical characteristics**

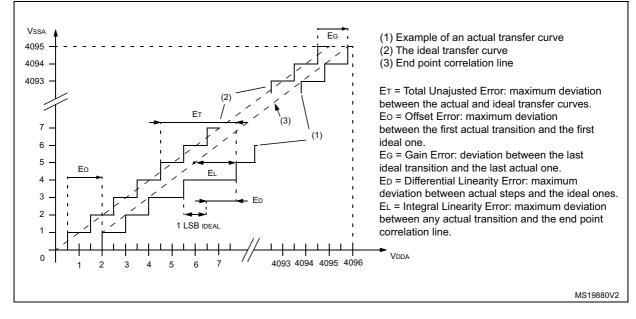

| Symbol | Parameter                    | Conditions                                                                | Min  | Тур  | Мах | Unit |  |

|--------|------------------------------|---------------------------------------------------------------------------|------|------|-----|------|--|

| ET     | Total unadjusted error       |                                                                           | -    | 2    | 5   |      |  |

| EO     | Offset error                 |                                                                           | -    | 1    | 2.5 |      |  |

| EG     | Gain error                   |                                                                           | -    | 1    | 2   | LSB  |  |

| EL     | Integral linearity error     |                                                                           | -    | 1.5  | 3   |      |  |

| ED     | Differential linearity error | 1.65 V < V <sub>REF+</sub> <v<sub>DDA &lt; 3.6 V,<br/>range 1/2/3</v<sub> | -    | 1    | 2   |      |  |

| ENOB   | Effective number of bits     |                                                                           | 10.0 | 11.0 | -   | bits |  |

| SINAD  | Signal-to-noise distortion   |                                                                           | 62   | 69   | -   |      |  |

| SNR    | Signal-to-noise ratio        |                                                                           | 61   | 69   | -   | dB   |  |

| THD    | Total harmonic distortion    |                                                                           | -    | -85  | -65 |      |  |

# Table 64. ADC accuracy<sup>(1)(2)(3)</sup> (continued)

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.12 does not affect the ADC accuracy.

3. Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

4. This number is obtained by the test board without additional noise, resulting in non-optimized value for oversampling mode.

#### Figure 30. ADC accuracy characteristics

# 6.3.18 Timer characteristics

#### **TIM timer characteristics**

The parameters given in the *Table 69* are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                               | Conditions                    | Min    | Max                     | Unit                 |  |  |  |

|------------------------|---------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|--|--|--|

| t ann                  | Timer resolution time                                   |                               | 1      | -                       | t <sub>TIMxCLK</sub> |  |  |  |

| <sup>t</sup> res(TIM)  |                                                         | f <sub>TIMxCLK</sub> = 32 MHz | 31.25  | -                       | ns                   |  |  |  |

| f                      | Timer external clock frequency on CH1                   |                               | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |  |  |

| f <sub>EXT</sub>       | to CH4                                                  | f <sub>TIMxCLK</sub> = 32 MHz | 0      | 16                      | MHz                  |  |  |  |

| Res <sub>TIM</sub>     | Timer resolution                                        | -                             |        | 16                      | bit                  |  |  |  |

|                        | 16-bit counter clock period when                        | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |  |  |

| t <sub>COUNTER</sub>   | internal clock is selected (timer's prescaler disabled) | f <sub>TIMxCLK</sub> = 32 MHz | 0.0312 | 2048                    | μs                   |  |  |  |

| t                      | Maximum possible count                                  | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |  |  |

| t <sub>MAX_COUNT</sub> |                                                         | f <sub>TIMxCLK</sub> = 32 MHz | -      | 134.2                   | S                    |  |  |  |

Table 69. TIMx characteristics<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM2, TIM6, TIM21, and TIM22 timers.

# 6.3.19 Communications interfaces

# I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm) : with a bit rate up to 100 kbit/s

- Fast-mode (Fm) : with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+) : with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timing requirements are guaranteed by design when the I<sup>2</sup>C peripheral is properly configured (refer to the reference manual for details). The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and VDDIOx is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement (refer to *Section 6.3.13: I/O port characteristics* for the I2C I/Os characteristics).

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter (see *Table 70* for the analog filter characteristics).

The analog spike filter is compliant with  $I^2C$  timings requirements only for the following voltage ranges:

- Fast mode Plus: 2.7 V  $\leq$  V\_DD  $\leq$  3.6 V and voltage scaling Range 1

- Fast mode:

- 2 V  $\leq$  V\_{DD}  $\leq$  3.6 V and voltage scaling Range 1 or Range 2.

- V<sub>DD</sub> < 2 V, voltage scaling Range 1 or Range 2, C<sub>load</sub> < 200 pF.

In other ranges, the analog filter should be disabled. The digital filter can be used instead.

Note: In Standard mode, no spike filter is required.

| Table 70. I20 | c analog | filter | characteristics <sup>(1)</sup> |  |

|---------------|----------|--------|--------------------------------|--|

|---------------|----------|--------|--------------------------------|--|

| Symbol          | Parameter                                                                 | Conditions | Min               | Мах                | Unit |

|-----------------|---------------------------------------------------------------------------|------------|-------------------|--------------------|------|

|                 |                                                                           | Range 1    |                   | 100 <sup>(3)</sup> | ns   |

| t <sub>AF</sub> | AF Maximum pulse width of spikes that are suppressed by the analog filter | Range 2    | 50 <sup>(2)</sup> | -                  |      |

|                 |                                                                           | Range 3    |                   | -                  |      |

- 1. Guaranteed by characterization results.

- 2. Spikes with widths below  $t_{\mbox{AF}(\mbox{min})}$  are filtered.

- 3. Spikes with widths above  $t_{AF(max)}$  are not filtered

#### **USART/LPUART** characteristics

The parameters given in the following table are guaranteed by design.

| Symbol   | Parameter                                                                                                        | Conditions                                                                 | Тур   | Max | Unit |  |

|----------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------|-----|------|--|

| twuusart | Wakeup time needed to<br>calculate the maximum<br>USART/LPUART baudrate<br>allowing to wake up from<br>Stop mode | Stop mode with main regulator in<br>Run mode, Range 2 or 3                 | -     | 8.7 |      |  |

|          |                                                                                                                  | Stop mode with main regulator in<br>Run mode, Range 1                      | - 8.1 |     | μs   |  |

|          |                                                                                                                  | o from<br>Stop mode with main regulator in<br>low-power mode, Range 2 or 3 |       | 12  |      |  |

|          |                                                                                                                  | Stop mode with main regulator in low-power mode, Range 1                   |       | -   | 11.4 |  |

#### Table 71. USART/LPUART characteristics

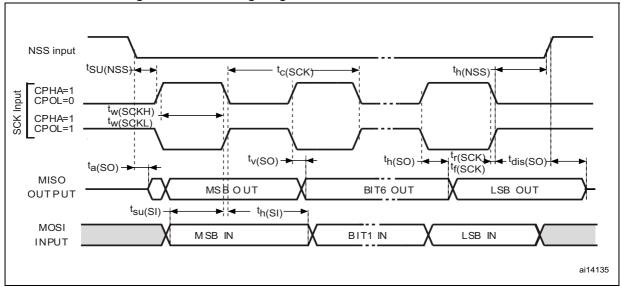

Figure 35. SPI timing diagram - slave mode and CPHA =  $1^{(1)}$

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

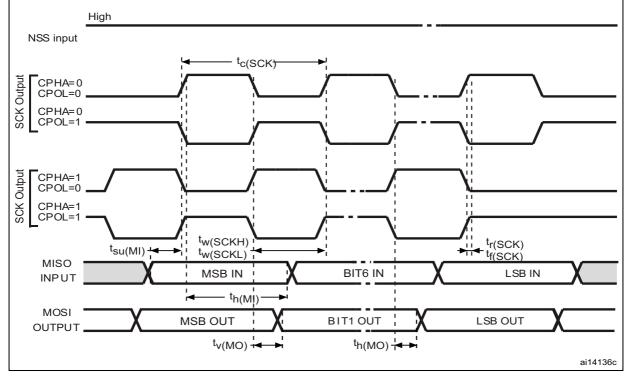

Figure 36. SPI timing diagram - master mode<sup>(1)</sup>

<sup>1.</sup> Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

# Table 79. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

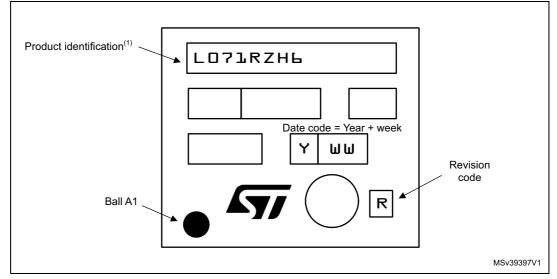

### **Device marking for TFBGA64**

The following figure gives an example of topside marking versus ball A 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Dimension      | Recommended values                             |  |  |

|----------------|------------------------------------------------|--|--|

| Pitch          | 0.4                                            |  |  |

| Dpad           | 260 µm max. (circular)                         |  |  |

|                | 220 µm recommended                             |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)          |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed. |  |  |

Table 83. WLCSP49 recommended PCB design rules (0.4 mm pitch)

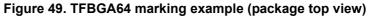

#### **Device marking for WLCSP49**

The following figure gives an example of topside marking versus ball A 1 position identifier location.

Figure 52. WLCSP49 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

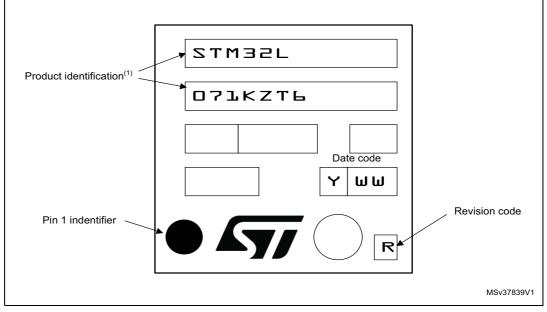

#### Device marking for LQFP32

The following figure gives an example of topside marking versus pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.