Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 6K x 8                                                                  |

| RAM Size                   | 20K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 13x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l071cbt6tr |

STM32L071xx List of tables

# List of tables

| Table 1.  | Device summary                                                                       | 1    |

|-----------|--------------------------------------------------------------------------------------|------|

| Table 2.  | Ultra-low-power STM32L071xx device features and peripheral counts                    | . 11 |

| Table 3.  | Functionalities depending on the operating power supply range                        | 15   |

| Table 4.  | CPU frequency range depending on dynamic voltage scaling                             | 16   |

| Table 5.  | Functionalities depending on the working mode                                        |      |

|           | (from Run/active down to standby)                                                    | 16   |

| Table 6.  | STM32L0xx peripherals interconnect matrix                                            | 18   |

| Table 7.  | Temperature sensor calibration values                                                | 27   |

| Table 8.  | Internal voltage reference measured values                                           | 27   |

| Table 9.  | Timer feature comparison                                                             | 28   |

| Table 10. | Comparison of I2C analog and digital filters                                         |      |

| Table 11. | STM32L071xx I <sup>2</sup> C implementation                                          | 30   |

| Table 12. | USART implementation                                                                 | 31   |

| Table 13. | SPI/I2S implementation                                                               | 32   |

| Table 14. | Legend/abbreviations used in the pinout table                                        | 38   |

| Table 15. | STM32L071xxx pin definition                                                          |      |

| Table 16. | Alternate functions port A                                                           | 46   |

| Table 17. | Alternate functions port B                                                           |      |

| Table 18. | Alternate functions port C                                                           | 48   |

| Table 19. | Alternate functions port D                                                           |      |

| Table 20. | Alternate functions port E                                                           | 50   |

| Table 21. | Alternate functions port H                                                           |      |

| Table 22. | Voltage characteristics                                                              |      |

| Table 23. | Current characteristics                                                              | 56   |

| Table 24. | Thermal characteristics                                                              |      |

| Table 25. | General operating conditions                                                         |      |

| Table 26. | Embedded reset and power control block characteristics                               |      |

| Table 27. | Embedded internal reference voltage calibration values                               |      |

| Table 28. | Embedded internal reference voltage                                                  | . 60 |

| Table 29. | Current consumption in Run mode, code with data processing running from Flash memory | . 62 |

| Table 30. | Current consumption in Run mode vs code type,                                        |      |

|           | code with data processing running from Flash memory                                  | . 62 |

| Table 31. | Current consumption in Run mode, code with data processing running from RAM          |      |

| Table 32. | Current consumption in Run mode vs code type,                                        |      |

|           | code with data processing running from RAM                                           | 64   |

| Table 33. | Current consumption in Sleep mode                                                    |      |

| Table 34. | Current consumption in Low-power run mode                                            |      |

| Table 35. | Current consumption in Low-power sleep mode                                          |      |

| Table 36. | Typical and maximum current consumptions in Stop mode                                |      |

| Table 37. | Typical and maximum current consumptions in Standby mode                             |      |

| Table 38. | Average current consumption during Wakeup                                            | 70   |

| Table 39. | Peripheral current consumption in Run or Sleep mode                                  |      |

| Table 40. | Peripheral current consumption in Stop and Standby mode                              | 73   |

| Table 41. | Low-power mode wakeup timings                                                        | 73   |

| Table 42. | High-speed external user clock characteristics                                       | 75   |

| Table 43. | Low-speed external user clock characteristics                                        | 76   |

| Table 44. | HSE oscillator characteristics                                                       | 77   |

|           |                                                                                      |      |

STM32L071xx Description

## 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM® Cortex®-M4, including ARM® Cortex®-M3 and ARM® Cortex®-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

Functional overview STM32L071xx

## 3 Functional overview

## 3.1 Low-power modes

The ultra-low-power STM32L071xx support dynamic voltage scaling to optimize its power consumption in Run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply.

There are three power consumption ranges:

- Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), with the CPU running at up to 32 MHz

- Range 2 (full V<sub>DD</sub> range), with a maximum CPU frequency of 16 MHz

- Range 3 (full V<sub>DD</sub> range), with a maximum CPU frequency limited to 4.2 MHz

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs. Sleep mode power consumption at 16 MHz is about 1 mA with all peripherals off.

#### Low-power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the low-speed clock (max 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In Low-power run mode, the clock frequency and the number of enabled peripherals are both limited.

#### Low-power sleep mode

This mode is achieved by entering Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In Low-power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the Run mode with the regulator on.

#### Stop mode with RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSE crystal and HSI RC oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The device can be woken up from Stop mode by any of the EXTI line, in 3.5 µs, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on), it can be the RTC alarm/tamper/timestamp/wakeup events, the USART/I2C/LPUART/LPTIMER wakeup events.

14/136 DocID027101 Rev 3

STM32L071xx Functional overview

#### Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USART/I2C/LPUART/LPTIMER wakeup events.

#### Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE crystal and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

#### Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in  $60 \mu s$  when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

Note:

The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

Table 3. Functionalities depending on the operating power supply range

| Operating power supply                                                     | Functionalities depending on the operating power supply range |                               |                            |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------|----------------------------|--|--|

| range                                                                      | ADC operation                                                 | Dynamic voltage scaling range | I/O operation              |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V                                           | ADC only,<br>conversion time up<br>to 570 ksps                | Range 2 or range 3            | Degraded speed performance |  |  |

| $V_{DD}$ = 1.71 to 1.8 $V^{(1)}$ ADC only, conversion time up to 1.14 Msps |                                                               | Range 1, range 2 or range 3   | Degraded speed performance |  |  |

| $V_{DD}$ = 1.8 to 2.0 $V^{(1)}$                                            | Conversion time up to 1.14 Msps                               | Range1, range 2 or range 3    | Degraded speed performance |  |  |

**Functional overview** STM32L071xx

| Table 5. Functionalities depending on the working mode          |

|-----------------------------------------------------------------|

| (from Run/active down to standby) (continued) <sup>(1)(2)</sup> |

|                                        |                                                 |                                                | Low-         | Low-           | Stop                                   | S | Standby                                |

|----------------------------------------|-------------------------------------------------|------------------------------------------------|--------------|----------------|----------------------------------------|---|----------------------------------------|

| IPs                                    | Run/Active                                      | Sleep                                          | power<br>run | power<br>sleep | Wakeup<br>capability                   |   | Wakeup<br>capability                   |

|                                        | Down to<br>140 μA/MHz<br>(from Flash<br>memory) | Down to<br>37 μΑ/ΜΗz<br>(from Flash<br>memory) |              |                | 4 μΑ (No<br>V <sub>DD</sub> =1.8 V     |   | 28 μΑ (No<br>) V <sub>DD</sub> =1.8 V  |

| Consumption                            |                                                 |                                                | Down to      | Down to        | B μA (with<br>V <sub>DD</sub> =1.8 V   |   | 5 μA (with<br>) V <sub>DD</sub> =1.8 V |

| V <sub>DD</sub> =1.8 to 3.6 V<br>(Typ) |                                                 |                                                | 8 μΑ         | 4.5 μA         | 4 μA (No<br>V <sub>DD</sub> =3.0 V     |   | 29 μΑ (No<br>) V <sub>DD</sub> =3.0 V  |

|                                        |                                                 |                                                |              |                | <br>(with RTC)<br><sub>DD</sub> =3.0 V |   | 5 μA (with<br>) V <sub>DD</sub> =3.0 V |

Legend:

- 2. The consumption values given in this table are preliminary data given for indication. They are subject to slight changes.

- 3. Some peripherals with wakeup from Stop capability can request HSI to be enabled. In this case, HSI is woken up by the peripheral, and only feeds the peripheral which requested it. HSI is automatically put off when the peripheral does not need it anymore.

- 4. UART and LPUART reception is functional in Stop mode. It generates a wakeup interrupt on Start. To generate a wakeup on address match or received frame event, the LPUART can run on LSE clock while the UART has to wake up or keep running the HSI clock.

- 5. I2C address detection is functional in Stop mode. It generates a wakeup interrupt in case of address match. It will wake up the HSI during reception.

#### 3.2 Interconnect matrix

Several peripherals are directly interconnected. This allows autonomous communication between peripherals, thus saving CPU resources and power consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, Low-power run, Low-power sleep and Stop modes.

Table 6. STM32L0xx peripherals interconnect matrix

| Interconnect source Interconnect destination |                      | Interconnect action                                               | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |

|----------------------------------------------|----------------------|-------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|

| COMPy                                        | TIM2,TIM21,<br>TIM22 | Timer input channel,<br>trigger from analog<br>signals comparison | Y   | Y     | Y                    | Y                      | ı    |

| COMPx                                        | LPTIM                | Timer input channel,<br>trigger from analog<br>signals comparison | Y   | Y     | Y                    | Y                      | Y    |

| TIMx                                         | TIMx                 | Timer triggered by other timer                                    | Y   | Υ     | Y                    | Υ                      | -    |

<sup>&</sup>quot;Y" = Yes (enable).

"O" = Optional can be enabled/disabled by software)

"-" = Not available

Functional overview STM32L071xx

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog.

The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### RTC clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC, whatever the system clock.

### Startup clock

After reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

### Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled. Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

47/

Pin descriptions STM32L071xx

Figure 4. STM32L071xx UFBGA100 ballout - 7x 7 mm

- 1. The above figure shows the package top view.

- 2. I/O supplied by VDDIO2.

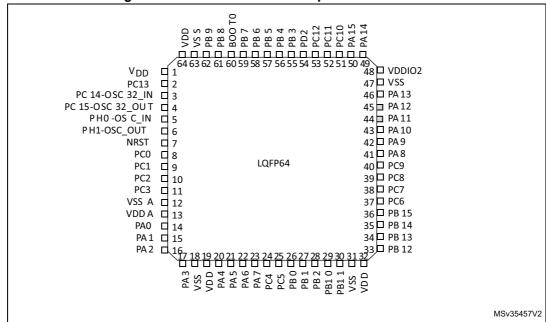

Figure 5. STM32L071xx LQFP64 pinout - 10 x 10 mm

- 1. The above figure shows the package top view.

- 2. I/O supplied by VDDIO2.

47/

Table 17. Alternate functions port B

|        |      | AF0                                                                                       | AF1                             | AF2                                                                             | AF3               | AF4                                                | AF5                                      | AF6                                                         | AF7                               |

|--------|------|-------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------|-------------------|----------------------------------------------------|------------------------------------------|-------------------------------------------------------------|-----------------------------------|

|        | Port | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/<br>LPTIM1/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I<br>2C1/TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/LPTIM<br>1/TIM2/3/EVENT<br>OUT/<br>SYS_AF | I2C1/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/<br>EVENTOUT | I2C3/LPUART1/<br>COMP1/2/<br>TIM3 |

|        | PB0  | EVENTOUT                                                                                  |                                 | TIM3_CH3                                                                        |                   | -                                                  | -                                        | -                                                           | -                                 |

|        | PB1  | -                                                                                         |                                 | TIM3_CH4                                                                        |                   | LPUART1_RTS_DE                                     | -                                        | -                                                           | -                                 |

|        | PB2  | -                                                                                         | -                               | LPTIM1_OUT                                                                      |                   | -                                                  | -                                        | -                                                           | I2C3_SMBA                         |

|        | PB3  | SPI1_SCK                                                                                  |                                 | TIM2_CH2                                                                        |                   | EVENTOUT                                           | USART1_RTS_DE                            | USART5_TX                                                   | -                                 |

|        | PB4  | SPI1_MISO                                                                                 |                                 | TIM3_CH1                                                                        |                   | TIM22_CH1                                          | USART1_CTS                               | USART5_RX                                                   | I2C3_SDA                          |

|        | PB5  | SPI1_MOSI                                                                                 |                                 | LPTIM1_IN1                                                                      | I2C1_SMBA         | TIM3_CH2/<br>TIM22_CH2                             | USART1_CK                                | USART5_CK/<br>USART5_RTS_D<br>E                             | -                                 |

|        | PB6  | USART1_TX                                                                                 | I2C1_SCL                        | LPTIM1_ETR                                                                      |                   | -                                                  | -                                        | -                                                           | -                                 |

|        | PB7  | USART1_RX                                                                                 | I2C1_SDA                        | LPTIM1_IN2                                                                      |                   | -                                                  | -                                        | USART4_CTS                                                  | -                                 |

| Port B | PB8  | -                                                                                         |                                 | -                                                                               |                   | I2C1_SCL                                           | -                                        | -                                                           | -                                 |

| ď      | PB9  | -                                                                                         |                                 | EVENTOUT                                                                        | -                 | I2C1_SDA                                           | SPI2_NSS/<br>I2S2_WS                     | -                                                           | -                                 |

|        | PB10 | -                                                                                         |                                 | TIM2_CH3                                                                        |                   | LPUART1_TX                                         | SPI2_SCK                                 | I2C2_SCL                                                    | LPUART1_RX                        |

|        | PB11 | EVENTOUT                                                                                  |                                 | TIM2_CH4                                                                        |                   | LPUART1_RX                                         | -                                        | I2C2_SDA                                                    | LPUART1_TX                        |

|        | PB12 | SPI2_NSS/I2S2_WS                                                                          |                                 | LPUART1_RTS_<br>DE                                                              |                   |                                                    | I2C2_SMBA                                | EVENTOUT                                                    | -                                 |

|        | PB13 | SPI2_SCK/I2S2_CK                                                                          |                                 | MCO                                                                             |                   | LPUART1_CTS                                        | I2C2_SCL                                 | TIM21_CH1                                                   | -                                 |

|        | PB14 | SPI2_MISO/<br>I2S2_MCK                                                                    |                                 | RTC_OUT                                                                         |                   | LPUART1_RTS_DE                                     | I2C2_SDA                                 | TIM21_CH2                                                   | -                                 |

|        | PB15 | SPI2_MOSI/<br>I2S2_SD                                                                     |                                 | RTC_REFIN                                                                       | -                 | -                                                  | -                                        | -                                                           | -                                 |

|        |      |                                                                                           |                                 | Table 20.                                                                       | Alternate fur     | ctions port E                                      |                                              |                                                             |                               |

|--------|------|-------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------|-------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|-------------------------------|

|        |      | AF0                                                                                       | AF1                             | AF2                                                                             | AF3               | AF4                                                | AF5                                          | AF6                                                         | AF7                           |

| Port   |      | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/LPTI<br>M1/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2C1<br>/TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/<br>LPTIM1/TIM2/3<br>/EVENTOUT/<br>SYS_AF | I2C1/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2<br>/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/<br>EVENTOUT | I2C3/LPUART1/<br>COMP1/2/TIM3 |

|        | PE0  | -                                                                                         |                                 | EVENTOUT                                                                        | -                 | -                                                  | -                                            | -                                                           | -                             |

|        | PE1  | -                                                                                         |                                 | EVENTOUT                                                                        | -                 | -                                                  | -                                            | -                                                           | -                             |

|        | PE2  | -                                                                                         |                                 | TIM3_ETR                                                                        | -                 | -                                                  | -                                            | -                                                           | -                             |

|        | PE3  | TIM22_CH1                                                                                 |                                 | TIM3_CH1                                                                        | ı                 | -                                                  | -                                            | -                                                           | -                             |

|        | PE4  | TIM22_CH2                                                                                 | -                               | TIM3_CH2                                                                        | -                 | -                                                  | -                                            | -                                                           | -                             |

|        | PE5  | TIM21_CH1                                                                                 | -                               | TIM3_CH3                                                                        | -                 | -                                                  | -                                            | -                                                           | -                             |

|        | PE6  | TIM21_CH2                                                                                 | -                               | TIM3_CH4                                                                        | -                 | -                                                  | -                                            | -                                                           | -                             |

| Port E | PE7  | -                                                                                         |                                 | -                                                                               | -                 | -                                                  | -                                            | USART5_CK/U<br>SART5_RTS_D<br>E                             | -                             |

| "      | PE8  | -                                                                                         |                                 | -                                                                               | -                 | -                                                  | -                                            | USART4_TX                                                   | -                             |

|        | PE9  | TIM2_CH1                                                                                  |                                 | TIM2_ETR                                                                        | -                 | -                                                  | -                                            | USART4_RX                                                   | -                             |

|        | PE10 | TIM2_CH2                                                                                  |                                 | -                                                                               | -                 | -                                                  | -                                            | USART5_TX                                                   | -                             |

|        | PE11 | TIM2_CH3                                                                                  | -                               | -                                                                               | -                 | -                                                  | -                                            | USART5_RX                                                   | -                             |

|        | PE12 | TIM2_CH4                                                                                  | -                               | SPI1_NSS                                                                        | -                 | -                                                  | -                                            | -                                                           | -                             |

|        | PE13 | -                                                                                         |                                 | SPI1_SCK                                                                        | -                 | -                                                  | -                                            | -                                                           | -                             |

|        | PE14 | -                                                                                         |                                 | SPI1_MISO                                                                       | -                 | -                                                  | -                                            | -                                                           | -                             |

|        | PE15 | -                                                                                         |                                 | SPI1_MOSI                                                                       | -                 | -                                                  | -                                            | -                                                           | -                             |

# 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 25. General operating conditions

| Symbol             | Parameter                                                                       | Conditions                                 | Min  | Max                  | Unit  |  |

|--------------------|---------------------------------------------------------------------------------|--------------------------------------------|------|----------------------|-------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                    | -                                          | 0    | 32                   |       |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                   | -                                          | 0    | 32                   | MHz   |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                   | -                                          | 0    | 32                   |       |  |

|                    |                                                                                 | BOR detector disabled                      | 1.65 | 3.6                  |       |  |

| V <sub>DD</sub>    | Standard operating voltage                                                      | BOR detector enabled, at power on          | 1.8  | 3.6                  | V     |  |

|                    |                                                                                 | BOR detector disabled, after power on      | 1.65 | 3.6                  | -     |  |

| V <sub>DDA</sub>   | Analog operating voltage (all features)                                         | Must be the same voltage as $V_{DD}^{(1)}$ | 1.65 | 3.6                  | V     |  |

| V <sub>DDIO2</sub> | Standard operating voltage                                                      | -                                          | 1.65 | 3.6                  | V     |  |

|                    | Input voltage on FT, FTf and RST pins <sup>(2)</sup>                            | $2.0~V \leq V_{DD} \leq 3.6~V$             | -0.3 | 5.5                  |       |  |

| V                  | Imput voltage on F1, F11 and R31 pins                                           | 1.65 V ≤ V <sub>DD</sub> ≤ 2.0 V           | -0.3 | 5.2                  | V     |  |

| V <sub>IN</sub>    | Input voltage on BOOT0 pin                                                      | -                                          | 0    | 5.5                  | V     |  |

|                    | Input voltage on TC pin -                                                       |                                            | -0.3 | V <sub>DD</sub> +0.3 |       |  |

|                    |                                                                                 | UFBGA100 package                           | -    | 351                  |       |  |

|                    |                                                                                 | LQFP100 package                            | -    | 488                  |       |  |

|                    | Power dissipation at $T_A$ = 85 °C (range 6) or $T_A$ =105 °C (rage 7) $^{(3)}$ | TFBGA64 package                            | -    | 313                  |       |  |

|                    |                                                                                 | LQFP64 package                             | -    | 435                  |       |  |

|                    |                                                                                 | WLCSP49 package                            | -    | 417                  |       |  |

|                    |                                                                                 | LQFP48 package                             | -    | 370                  |       |  |

|                    |                                                                                 | UFQFPN32 package                           | -    | 556                  |       |  |

| $P_{D}$            |                                                                                 | LQFP32 package                             | -    | 333                  | mW    |  |

| r <sub>D</sub>     |                                                                                 | UFBGA100 package                           | -    | 88                   | 11100 |  |

|                    |                                                                                 | LQFP100 package                            | -    | 122                  |       |  |

|                    |                                                                                 | TFBGA64 package                            | -    | 78                   |       |  |

|                    | Power dissipation at T <sub>A</sub> = 125 °C (range                             | LQFP64 package                             | -    | 109                  |       |  |

|                    | 3) (3)                                                                          | WLCSP49 package                            | -    | 104                  |       |  |

|                    |                                                                                 | LQFP48 package                             | -    | 93                   |       |  |

|                    |                                                                                 | UFQFPN32 package                           | -    | 139                  |       |  |

|                    |                                                                                 | LQFP32 package                             | =    | 83                   |       |  |

Electrical characteristics STM32L071xx

Table 25. General operating conditions (continued)

| Symbol | Parameter                            | Conditions                                                | Min | Max | Unit |

|--------|--------------------------------------|-----------------------------------------------------------|-----|-----|------|

|        |                                      | Maximum power dissipation (range 6)                       | -40 | 85  |      |

| Та     | Temperature range                    | Maximum power dissipation (range 7)                       | -40 | 105 |      |

|        |                                      | Maximum power dissipation (range 3)                       | -40 | 125 | °C   |

|        | Junction temperature range (range 6) | $-40~^{\circ}C \le T_A \le 85~^{\circ}$                   | -40 | 105 |      |

| TJ     | Junction temperature range (range 7) | $-40~^{\circ}\text{C} \le T_{A} \le 105~^{\circ}\text{C}$ | -40 | 125 |      |

|        | Junction temperature range (range 3) | -40 °C ≤ T <sub>A</sub> ≤ 125 °C                          | -40 | 130 |      |

<sup>1.</sup> It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and normal operation.

<sup>2.</sup> To sustain a voltage higher than  $V_{DD}$ +0.3V, the internal pull-up/pull-down resistors must be disabled.

<sup>3.</sup> If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_J$  max (see *Table 24: Thermal characteristics on page 56*).

| Symbol                                  | Parameter                                                                                       | Conditions | Min | Тур | Max  | Unit                     |

|-----------------------------------------|-------------------------------------------------------------------------------------------------|------------|-----|-----|------|--------------------------|

| I <sub>LPBUF</sub> <sup>(4)</sup>       | I <sub>LPBUF</sub> <sup>(4)</sup> Consumption of reference voltage buffer for VREF_OUT and COMP |            | -   | 730 | 1200 | nA                       |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup> | 1/4 reference voltage                                                                           | -          | 24  | 25  | 26   |                          |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup> | 1/2 reference voltage                                                                           | -          | 49  | 50  | 51   | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup> | 3/4 reference voltage                                                                           | -          | 74  | 75  | 76   | INCI IIVI                |

Table 28. Embedded internal reference voltage<sup>(1)</sup> (continued)

- Refer to Table 40: Peripheral current consumption in Stop and Standby mode for the value of the internal reference current consumption (I<sub>REFINT</sub>).

- 2. Guaranteed by test in production.

- 3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

- 4. Guaranteed by design.

- 5. Shortest sampling time can be determined in the application by multiple iterations.

- 6. To guarantee less than 1% VREF\_OUT deviation.

## 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 15: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code if not specified otherwise.

The current consumption values are derived from the tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 25: General operating conditions* unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time and prefetch is adjusted depending on fHCLK frequency and voltage range to provide the best CPU performance unless otherwise specified.

- When the peripherals are enabled f<sub>APB1</sub> = f<sub>APB2</sub> = f<sub>APB</sub>

- When PLL is on, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used)

- The HSE user clock applied to OSCI\_IN input follows the characteristic specified in Table 42: High-speed external user clock characteristics

- For maximum current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.6 V is applied to all supply pins

- For typical current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.0 V is applied to all supply pins if not specified otherwise

The parameters given in *Table 49*, *Table 25* and *Table 26* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

## **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

**Table 54. EMI characteristics**

| Symbol           | bol Parameter Conditions |                                                     | Monitored frequency band | Max vs.<br>frequency<br>range at<br>32 MHz | Unit |

|------------------|--------------------------|-----------------------------------------------------|--------------------------|--------------------------------------------|------|

|                  | Peak level               | V -36V                                              | 0.1 to 30 MHz            | -7                                         |      |

| 6                |                          | $V_{DD} = 3.6 \text{ V},$<br>$T_A = 25 \text{ °C},$ | 30 to 130 MHz            | 14                                         | dΒμV |

| S <sub>EMI</sub> | reak level               | LQFP100 package                                     | 130 MHz to 1 GHz         | 9                                          |      |

|                  |                          | compliant with IEC 61967-2                          | EMI Level                | 2                                          | -    |

### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 57.

Table 57. I/O current injection susceptibility

|                  |                                                      | Functional s       |                    |      |

|------------------|------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                          | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                            | -0                 | NA                 |      |

| I <sub>INJ</sub> | Injected current on PA0, PA4, PA5, PC15, PH0 and PH1 | -5                 | 0                  | mA   |

|                  | Injected current on any other FT, FTf pins           | -5 <sup>(1)</sup>  | NA                 |      |

|                  | Injected current on any other pins                   | -5 <sup>(1)</sup>  | +5                 |      |

It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Electrical characteristics STM32L071xx

## 6.3.13 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under the conditions summarized in *Table 25*. All I/Os are CMOS and TTL compliant.

Table 58. I/O static characteristics

| Symbol           | Parameter                                         | Conditions                                                                                          | Min                 | Тур                                | Max                                | Unit |  |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------------------|------|--|

| $V_{\rm IL}$     | Input low level voltage                           | TC, FT, FTf, RST<br>I/Os                                                                            | -                   | -                                  | 0.3V <sub>DD</sub>                 |      |  |

| - 112            | -                                                 | BOOT0 pin                                                                                           | -                   | -                                  | 0.14V <sub>DD</sub> <sup>(1)</sup> |      |  |

| V <sub>IH</sub>  | Input high level voltage                          | All I/Os                                                                                            | 0.7 V <sub>DD</sub> | -                                  | -                                  | V    |  |

| W                | I/O Schmitt trigger voltage hysteresis            | Standard I/Os                                                                                       | -                   | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                  |      |  |

| $V_{hys}$        | (2)                                               | BOOT0 pin                                                                                           | -                   | 0.01                               | -                                  |      |  |

|                  |                                                   | $V_{SS} \le V_{IN} \le V_{DD}$<br>All I/Os except for<br>PA11, PA12, BOOT0<br>and FTf I/Os          | -                   | -                                  | ±50                                |      |  |

|                  |                                                   | $V_{SS} \le V_{IN} \le V_{DD}$ , PA11 and PA12 I/Os                                                 | -                   | -                                  | -50/+250                           | nA   |  |

|                  |                                                   | $V_{SS} \le V_{IN} \le V_{DD}$<br>FTf I/Os                                                          | -                   | -                                  | ±100                               |      |  |

| I <sub>lkg</sub> | Input leakage current (4)                         | V <sub>DD</sub> ≤ V <sub>IN</sub> ≤ 5 V<br>All I/Os except for<br>PA11, PA12, BOOT0<br>and FTf I/Os | -                   | -                                  | 200                                | nA   |  |

|                  |                                                   | $V_{DD} \le V_{IN} \le 5 \text{ V}$ FTf I/Os                                                        | -                   | -                                  | 500                                |      |  |

|                  |                                                   | V <sub>DD</sub> ≤ V <sub>IN</sub> ≤ 5 V<br>PA11, PA12 and<br>BOOT0                                  | -                   | -                                  | 10                                 | μΑ   |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>   | $V_{IN} = V_{SS}$                                                                                   | 30                  | 45                                 | 60                                 | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup> | $V_{IN} = V_{DD}$                                                                                   | 30                  | 45                                 | 60                                 | kΩ   |  |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                                                   | -                   | 5                                  | -                                  | pF   |  |

<sup>1.</sup> Guaranteed by characterization.

88/136 DocID027101 Rev 3

<sup>2.</sup> Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

<sup>3.</sup> With a minimum of 200 mV. Guaranteed by characterization results.

<sup>4.</sup> The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

## Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_S}{f_{ADC} \times C_{ADC} \times In(2^{N+2})} - R_{ADC}$$

The simplified formula above (Equation 1) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

Table 63.  $R_{AIN}$  max for  $f_{ADC} = 16 \text{ MHz}^{(1)}$

|       |                        | B may for |       |                                               | R <sub>AIN</sub> max    | for stand               | dard chan               | nels (k $\Omega$ )      |                          |                                                            |                                                           |

|-------|------------------------|-----------|-------|-----------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------|------------------------------------------------------------|-----------------------------------------------------------|

|       | t <sub>S</sub><br>(µs) |           |       | $R_{AIN}$ max for fast channels (k $\Omega$ ) | V <sub>DD</sub> > 2.7 V | V <sub>DD</sub> > 2.4 V | V <sub>DD</sub> > 2.0 V | V <sub>DD</sub> > 1.8 V | V <sub>DD</sub> > 1.75 V | V <sub>DD</sub> > 1.65 V<br>and<br>T <sub>A</sub> > -10 °C | V <sub>DD</sub> > 1.65 V<br>and<br>T <sub>A</sub> > 25 °C |

| 1.5   | 0.09                   | 0.5       | < 0.1 | NA                                            | NA                      | NA                      | NA                      | NA                      | NA                       |                                                            |                                                           |

| 3.5   | 0.22                   | 1         | 0.2   | < 0.1                                         | NA                      | NA                      | NA                      | NA                      | NA                       |                                                            |                                                           |

| 7.5   | 0.47                   | 2.5       | 1.7   | 1.5                                           | < 0.1                   | NA                      | NA                      | NA                      | NA                       |                                                            |                                                           |

| 12.5  | 0.78                   | 4         | 3.2   | 3                                             | 1                       | NA                      | NA                      | NA                      | NA                       |                                                            |                                                           |

| 19.5  | 1.22                   | 6.5       | 5.7   | 5.5                                           | 3.5                     | NA                      | NA                      | NA                      | < 0.1                    |                                                            |                                                           |

| 39.5  | 2.47                   | 13        | 12.2  | 12                                            | 10                      | NA                      | NA                      | NA                      | 5                        |                                                            |                                                           |

| 79.5  | 4.97                   | 27        | 26.2  | 26                                            | 24                      | < 0.1                   | NA                      | NA                      | 19                       |                                                            |                                                           |

| 160.5 | 10.03                  | 50        | 49.2  | 49                                            | 47                      | 32                      | < 0.1                   | < 0.1                   | 42                       |                                                            |                                                           |

<sup>1.</sup> Guaranteed by design.

Table 64. ADC accuracy<sup>(1)(2)(3)</sup>

| Symbol | Parameter                                                                          | Conditions                                             | Min  | Тур  | Max | Unit |

|--------|------------------------------------------------------------------------------------|--------------------------------------------------------|------|------|-----|------|

| ET     | Total unadjusted error                                                             |                                                        | -    | 2    | 4   |      |

| EO     | Offset error                                                                       |                                                        | -    | 1    | 2.5 |      |

| EG     | Gain error                                                                         |                                                        | -    | 1    | 2   | LSB  |

| EL     | Integral linearity error                                                           |                                                        | -    | 1.5  | 2.5 |      |

| ED     | Differential linearity error                                                       |                                                        | -    | 1    | 1.5 |      |

|        | Effective number of bits                                                           | 1.65 V < V <sub>DDA</sub> = V <sub>RFF+</sub> < 3.6 V, | 10.2 | 11   |     |      |

| ENOB   | Effective number of bits (16-bit mode oversampling with ratio =256) <sup>(4)</sup> | range 1/2/3                                            | 11.3 | 12.1 | -   | bits |

| SINAD  | Signal-to-noise distortion                                                         |                                                        | 63   | 69   | -   |      |

|        | Signal-to-noise ratio                                                              |                                                        | 63   | 69   | -   |      |

| SNR    | Signal-to-noise ratio (16-bit mode oversampling with ratio =256) <sup>(4)</sup>    |                                                        | 70   | 76   | -   | dB   |

| THD    | Total harmonic distortion                                                          |                                                        | -    | -85  | -73 |      |

Table 73. SPI characteristics in voltage Range 2 (1)

| Symbol                                    | Parameter                         | Conditions                                               | Min     | Тур   | Max              | Unit |

|-------------------------------------------|-----------------------------------|----------------------------------------------------------|---------|-------|------------------|------|

|                                           |                                   | Master mode                                              |         |       | 8                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | SPI clock frequency               | Slave mode Transmitter<br>1.65 <v<sub>DD&lt;3.6V</v<sub> | _       | -     | 8                | MHz  |

| (SCK)                                     |                                   | Slave mode Transmitter 2.7 <v<sub>DD&lt;3.6V</v<sub>     |         |       | 8 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                     | Duty cycle of SPI clock frequency | Slave mode                                               | 30      | 50    | 70               | %    |

| t <sub>su(NSS)</sub>                      | NSS setup time                    | Slave mode, SPI presc = 2                                | 4*Tpclk | -     | -                |      |

| t <sub>h(NSS)</sub>                       | NSS hold time                     | Slave mode, SPI presc = 2                                | 2*Tpclk | -     | -                |      |

| t <sub>w(SCKH)</sub>                      | SCK high and low time             | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2          |      |

| t <sub>su(MI)</sub>                       | Data input setup time             | Master mode                                              | 0       | -     | -                |      |

| t <sub>su(SI)</sub>                       | Data input setup time             | Slave mode                                               | 3       | -     | -                |      |

| t <sub>h(MI)</sub>                        | Data input hold time              | Master mode                                              | 11      | -     | -                |      |

| t <sub>h(SI)</sub>                        | Data input noid time              | Slave mode                                               | 4.5     | -     | -                | ns   |

| t <sub>a(SO</sub>                         | Data output access time           | Slave mode                                               | 18      | -     | 52               |      |

| t <sub>dis(SO)</sub>                      | Data output disable time          | Slave mode                                               | 12      | -     | 42               |      |

| t <sub>v(SO)</sub>                        | Data output valid time            | Slave mode                                               | -       | 20    | 56.5             |      |

| t <sub>v(MO)</sub>                        |                                   | Master mode                                              | -       | 5     | 9                |      |

| t <sub>h(SO)</sub>                        | Data output hold time             | Slave mode                                               | 13      | -     | -                |      |

| t <sub>h(MO)</sub>                        | Data output noid time             | Master mode                                              | 3       | -     | -                |      |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

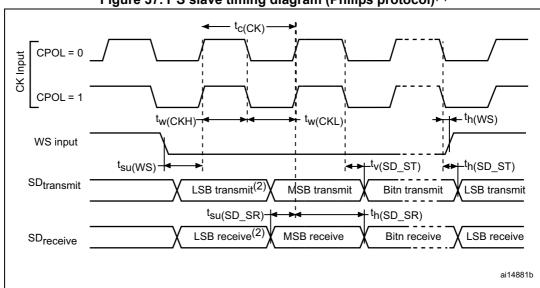

Figure 37. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels:  $0.3 \times V_{DD}$  and  $0.7 \times V_{DD}$ .

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

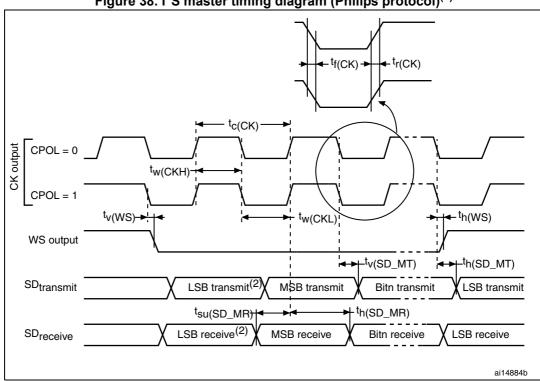

Figure 38. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

STM32L071xx Package information

Table 80. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array package mechanical data (continued)

| Symbol |     | millimeters |       |     | inches <sup>(1)</sup> |        |

|--------|-----|-------------|-------|-----|-----------------------|--------|

|        | Min | Тур         | Max   | Min | Тур                   | Max    |

| е      | -   | 0.500       | -     | -   | 0.0197                | -      |

| F      | -   | 0.750       | -     | -   | 0.0295                | -      |

| ddd    | -   | -           | 0.080 | -   | -                     | 0.0031 |

| eee    | -   | -           | 0.150 | -   | -                     | 0.0059 |

| fff    | -   | -           | 0.050 | -   | -                     | 0.0020 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

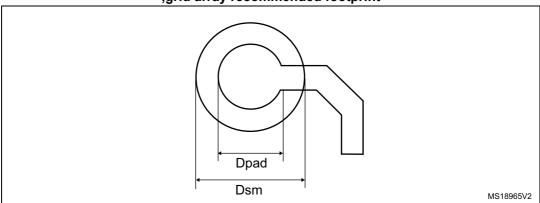

Figure 48. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball ,grid array recommended footprint

Table 81. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

|              | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |

Note: Non solder mask defined (NSMD) pads are recommended.

4 to 6 mils solder paste screen printing process.

Table 86. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat package mechanical data

|        |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| Α      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |

| A3     | -     | 0.152       | -     | -      | 0.0060                | -      |

| b      | 0.180 | 0.230       | 0.280 | 0.0071 | 0.0091                | 0.0110 |

| D      | 4.900 | 5.000       | 5.100 | 0.1929 | 0.1969                | 0.2008 |

| D1     | 3.400 | 3.500       | 3.600 | 0.1339 | 0.1378                | 0.1417 |

| D2     | 3.400 | 3.500       | 3.600 | 0.1339 | 0.1378                | 0.1417 |

| E      | 4.900 | 5.000       | 5.100 | 0.1929 | 0.1969                | 0.2008 |

| E1     | 3.400 | 3.500       | 3.600 | 0.1339 | 0.1378                | 0.1417 |

| E2     | 3.400 | 3.500       | 3.600 | 0.1339 | 0.1378                | 0.1417 |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

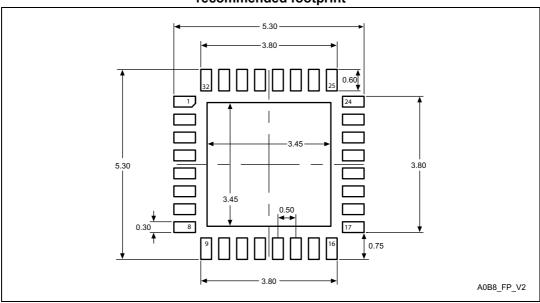

Figure 60. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat recommended footprint

1. Dimensions are expressed in millimeters.