Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 40                                                                      |

| Program Memory Size        | 192KB (192K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 6K x 8                                                                  |

| RAM Size                   | 20K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 13x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 49-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 49-WLCSP (3.29x3.26)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l071czy6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.1 Device overview

| Table 2. Ultra-low- | power STM32L071xx | device features ar | d peripheral counts |

|---------------------|-------------------|--------------------|---------------------|

|                     |                   |                    |                     |

| Perip                                                                  | heral               |                                           |          |                       |                        |                                                                             |                        |                      | STM32L<br>071VZ        | STM32L<br>071RZ                             |                        |                      |

|------------------------------------------------------------------------|---------------------|-------------------------------------------|----------|-----------------------|------------------------|-----------------------------------------------------------------------------|------------------------|----------------------|------------------------|---------------------------------------------|------------------------|----------------------|

| Flash (Kbytes)         64 Kbytes         128 Kbytes         192 Kbytes |                     |                                           |          |                       |                        |                                                                             | oytes                  |                      |                        |                                             |                        |                      |

| Data EEPRO                                                             | OM (Kbytes)         | Kbytes)         3 Kbytes         6 Kbytes |          |                       |                        |                                                                             |                        |                      |                        |                                             |                        |                      |

| RAM (Kbyte                                                             | s)                  |                                           |          |                       |                        |                                                                             | 20 Kbytes              |                      |                        |                                             |                        |                      |

|                                                                        | General-<br>purpose |                                           |          |                       |                        |                                                                             | 4                      |                      |                        |                                             |                        |                      |

| Timers                                                                 | Basic               |                                           |          |                       |                        |                                                                             | 2                      |                      |                        |                                             |                        |                      |

|                                                                        | LPTIMER             |                                           |          |                       |                        |                                                                             | 1                      |                      |                        |                                             |                        |                      |

| RTC/SYST<br>/WW                                                        |                     |                                           |          |                       |                        |                                                                             | 1/1/1/1                |                      |                        |                                             |                        |                      |

|                                                                        | SPI/I2S             | 4(3) <sup>(1)</sup> /0                    | 6(4)     | <sup>(2)</sup> /1     | 4(3) <sup>(1)</sup> /0 |                                                                             | 6(4) <sup>(2)</sup> /1 |                      | 4(3) <sup>(1)</sup> /0 | 3) <sup>(1)</sup> /0 6(4) <sup>(2)</sup> /1 |                        |                      |

| Com.<br>interfaces                                                     | l <sup>2</sup> C    | 2                                         | 2 3      |                       |                        | 3                                                                           |                        |                      | 2                      | 3                                           |                        |                      |

|                                                                        | USART               | 3                                         | 3 4      |                       |                        |                                                                             | 4                      |                      |                        | 4                                           |                        |                      |

|                                                                        | LPUART              | 1                                         |          |                       |                        |                                                                             |                        |                      |                        |                                             |                        |                      |

| GPIOs                                                                  |                     | 23                                        | 37       | 84                    | 25 <sup>(3)</sup>      | 40 <sup>(4)</sup>                                                           | 84                     | 51 <sup>(5)</sup>    | 25 <sup>(3)</sup>      | 40 <sup>(4)</sup>                           | 84                     | 51 <sup>(5)</sup>    |

| Clocks:<br>HSE/LSE/H                                                   | SI/MSI/LSI          |                                           |          |                       |                        |                                                                             | 1/1/1/1/1              |                      |                        |                                             |                        |                      |

| 12-bit synch<br>ADC<br>Number of o                                     |                     | 1<br>10                                   | 1<br>13  | 1<br>16               |                        |                                                                             |                        |                      |                        | 1<br>16                                     | 1<br>16 <sup>(5)</sup> |                      |

| Comparator                                                             | s                   |                                           | 2        |                       |                        |                                                                             |                        |                      |                        |                                             |                        |                      |

| Max. CPU fr                                                            | equency             | 32 MHz                                    |          |                       |                        |                                                                             |                        |                      |                        |                                             |                        |                      |

| Operating v                                                            | oltage              |                                           | 1.8 V to | o 3.6 V (dov          | vn to 1.65 V           | at power-do                                                                 | wn) with B0            | OR option 1          | 1.65 to 3.6 V          | / without BOF                               | R option               |                      |

| Operating<br>temperatures                                              |                     |                                           |          |                       |                        | Ambient temperature: -40 to +125 °C<br>Junction temperature: -40 to +130 °C |                        |                      |                        |                                             |                        |                      |

| Packages                                                               |                     | UFQFPN<br>32                              | LQFP48   | LQFP/<br>UFBGA<br>100 | UFQFPN/<br>LQFP32      | LQFP48,<br>WLCSP49                                                          | LQFP/<br>UFBGA<br>100  | LQFP/<br>TFBGA<br>64 | UFQFPN/<br>LQFP32      | LQFP48,<br>WLCSP49                          | LQFP/<br>UFBGA<br>100  | LQFP/<br>TFBGA<br>64 |

1. 3 SPI interfaces are USARTs operating in SPI master mode.

2. 4 SPI interfaces are USARTs operating in SPI master mode.

3. UFQFPN32 has 2 GPIOs less than LQFP32.

4. LQFP48 has three GPIOs less than WLCSP49.

5. TFBGA64 has one GPIO, one ADC input less than LQFP64.

| Table 3. Functionalities de | pending on the or | perating power sup | ply range (continued) |

|-----------------------------|-------------------|--------------------|-----------------------|

|                             |                   |                    |                       |

| Operating power supply         | Functionalities de                 | pending on the opera             | ting power supply range |

|--------------------------------|------------------------------------|----------------------------------|-------------------------|

| range                          | ADC operation                      | Dynamic voltage<br>scaling range | I/O operation           |

| V <sub>DD</sub> = 2.0 to 2.4 V | Conversion time up<br>to 1.14 Msps | Range 1, range 2 or range 3      | Full speed operation    |

| V <sub>DD</sub> = 2.4 to 3.6 V | Conversion time up<br>to 1.14 Msps | Range 1, range 2 or<br>range 3   | Full speed operation    |

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.</li>

| Table 4. CPU frequency range | depending on d | ynamic voltage scaling |

|------------------------------|----------------|------------------------|

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

# Table 5. Functionalities depending on the working mode(from Run/active down to standby) (1)(2)

|                                           |            |       | Low-         | Low-           |     | Stop                 | S | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|-----|----------------------|---|----------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |     | Wakeup<br>capability |   | Wakeup<br>capability |

| CPU                                       | Y          |       | Y            |                |     |                      |   |                      |

| Flash memory                              | 0          | 0     | 0            | 0              |     |                      |   |                      |

| RAM                                       | Y          | Y     | Y            | Y              | Y   |                      |   |                      |

| Backup registers                          | Y          | Y     | Y            | Y              | Y   |                      | Y |                      |

| EEPROM                                    | 0          | 0     | 0            | 0              |     |                      |   |                      |

| Brown-out reset<br>(BOR)                  | 0          | 0     | 0            | 0              | 0   | 0                    | 0 | 0                    |

| DMA                                       | 0          | 0     | 0            | 0              |     |                      |   |                      |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | 0     | 0            | Ο              | 0   | 0                    | - |                      |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y     | Y            | Y              | Y   | Y                    | Y | Y                    |

| High Speed<br>Internal (HSI)              | 0          | 0     |              |                | (3) |                      |   |                      |

| Interconnect<br>source | Interconnect<br>destination | Interconnect action                                                         | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |  |  |  |

|------------------------|-----------------------------|-----------------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|--|--|--|

| RTC                    | TIM21                       | Timer triggered by Auto<br>wake-up                                          | Y   | Y     | Y                    | Y                      | -    |  |  |  |

| RIC                    | LPTIM                       | Timer triggered by RTC event                                                | Y   | Y     | Y                    | Y                      | Y    |  |  |  |

| All clock<br>source    | TIMx                        | Clock source used as<br>input channel for RC<br>measurement and<br>trimming | Y   | Y     | Y                    | Y                      | -    |  |  |  |

|                        | TIMx                        | Mx Timer input channel and trigger                                          |     | Y     | Y                    | Y                      | -    |  |  |  |

| GPIO                   | LPTIM                       | Timer input channel and trigger                                             | Y   | Y     | Y                    | Y                      | Y    |  |  |  |

|                        | ADC                         | Conversion trigger                                                          | Y   | Y     | Y                    | Y                      | -    |  |  |  |

Table 6. STM32L0xx peripherals interconnect matrix (continued)

# 3.3 ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L071xx are compatible with all ARM tools and software.

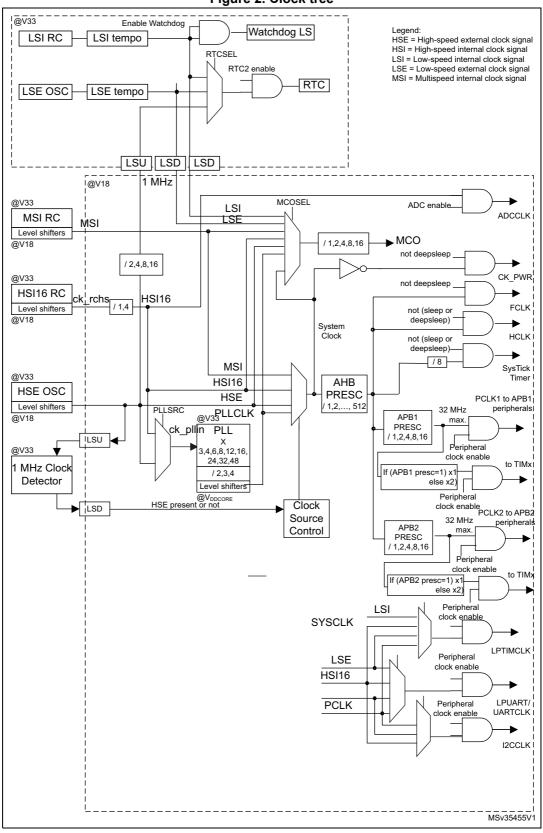

Figure 2. Clock tree

DocID027101 Rev 3

| 1 2 3 4 5 6 7 8 9 10 11 12                                                  | 12          |

|-----------------------------------------------------------------------------|-------------|

| A (PE3) (PE1) (PB8) BOOTD (PD7) (PD5) (PB4) (PB3) (PA15) (PA14) (PA13) (PA  | PA12)       |

| ● _ ヽ_ノ`ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ ヽ_ノ                             | PA11)       |

| c (PD2) (PD0) (PC11) (VDD) (PB5) (PD2) (PD0) (PC11) (VDD) (PA               | PA10)       |

|                                                                             | PC9)        |

| _our \_/ \_/ \_/                                                            | PC6)        |

|                                                                             | vss)        |

|                                                                             | VDD)        |

| н (PC0) (NRSţ (VDD) (PD15) (PD14) (PD                                       | PD13        |

| J (VSSA) (PC1) (PC2) (PD12 (PD11) (PD                                       | PD10)       |

| K (VREF) (PC3) (PA2) (PA5) (PC4) (PD9) (PD8) (PB15) (PB14) (PB              | рв13)       |

|                                                                             | у-<br>рв12) |

| M (VDDA) (PA1) (PA4) (PA7) (PB0) (PB1) (PE7) (PE9) (PE11) (PE13) (PE14) (PE | PE15)       |

|                                                                             |             |

|                                                                             |             |

Figure 4. STM32L071xx UFBGA100 ballout - 7x 7 mm

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

DocID027101 Rev 3

|   | i igure o              |        |       |       |        |        |        | -      |  |

|---|------------------------|--------|-------|-------|--------|--------|--------|--------|--|

|   | 1                      | 2      | 3     | 4     | 5      | 6      | 7      | 8      |  |

| А | PC14<br>OSC32<br>`_4₩  | (PC13) | (PB9) | (PB4) | (PB3)  | (PA15) | (PA14) | (PA13) |  |

| В | PC75<br>OSC32<br>_OUT  |        | (PB8) |       | (PD2)  | (PC11) | (PC10) | (PA12) |  |

| С | /PHO-1<br>OSC_IN       | (vss)  | (PB7) | (PB5) | (PC12) | (PA10) | (PA9)  | (PA11) |  |

| D | , ₽Пѣ<br>(osc)<br>∖QUI |        | (PB6) | (vss) | (vss)  | (vss)  | (PA8)  | (PC9)  |  |

| E |                        | (PC1)  | (PC0) |       |        |        | (PC7)  | (PC8)  |  |

| F | (VSSA)                 | (PC2)  | (PA2) | (PA5) | (PB0)  | (PC6)  | (PB15) | (PB14) |  |

| G |                        | (PA0)  | (PA3) | (PA6) | (PB1)  | (PB2)  | (PB10) | (PB13) |  |

| Н | (VDDA)                 | (PA1)  | (PA4) | (PA7) | (PC4)  | (PC5)  | (PB11) | (PB12) |  |

|   |                        |        |       |       |        |        |        |        |  |

Figure 6. STM32L071xx TFBGA64 ballout - 5x 5 mm

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

|        |                         | l      | Pin n  | umb     | er      |         |         | JIE 13. 311032                        |          |               |      |                                                     |                                        |

|--------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|---------------|------|-----------------------------------------------------|----------------------------------------|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                 | Additional functions                   |

| -      | -                       | -      | -      | -       | -       | 1       | B2      | PE2                                   | I/O      | FT            | -    | TIM3_ETR                                            | -                                      |

| -      | -                       | -      | -      | -       | -       | 2       | A1      | PE3                                   | I/O      | FT            | -    | TIM22_CH1, TIM3_CH1                                 | -                                      |

| -      | -                       | -      | -      | -       | -       | 3       | B1      | PE4                                   | I/O      | FT            | -    | TIM22_CH2, TIM3_CH2                                 | -                                      |

| -      | -                       | -      | -      | -       | -       | 4       | C2      | PE5                                   | I/O      | FT            | -    | TIM21_CH1, TIM3_CH3                                 | -                                      |

| -      | -                       | -      | -      | -       | -       | 5       | D2      | PE6                                   | I/O      | FT            | -    | TIM21_CH2, TIM3_CH4                                 | RTC_TAMP3/WKUP3                        |

| 1      | -                       | 1      | 1      | B2      | B6      | 6       | E2      | VDD                                   | S        |               | -    | -                                                   | -                                      |

| -      | -                       | 2      | 2      | A2      | В7      | 7       | C1      | PC13                                  | I/O      | FT            | -    | -                                                   | RTC_TAMP1/<br>RTC_TS/<br>RTC_OUT/WKUP2 |

| 2      | 1                       | 3      | 3      | A1      | C6      | 8       | D1      | PC14-<br>OSC32_IN<br>(PC14)           | I/O      | FT            | -    | -                                                   | OSC32_IN                               |

| 3      | 2                       | 4      | 4      | B1      | C7      | ся      | E1      | PC15-<br>OSC32_OUT<br>(PC15)          | I/O      | тс            | -    | -                                                   | OSC32_OUT                              |

| -      | -                       | 1      | -      | -       | -       | 10      | F2      | PH9                                   | I/O      | FT            | I    | -                                                   | -                                      |

| -      | -                       | -      | -      | -       | -       | 11      | G2      | PH10                                  | I/O      | FT            | -    | -                                                   | -                                      |

| -      | -                       | 5      | 5      | C1      | D6      | 12      | F1      | PH0-OSC_IN<br>(PH0)                   | I/O      | тс            | -    | -                                                   | OSC_IN                                 |

| -      | -                       | 6      | 6      | D1      | D7      | 13      | G1      | PH1-<br>OSC_OUT<br>(PH1)              | I/O      | тс            | -    | -                                                   | OSC_OUT                                |

| 4      | 3                       | 7      | 7      | E1      | D5      | 14      | H2      | NRST                                  | I/O      | -             | -    | -                                                   | -                                      |

| -      | -                       | -      | 8      | E3      | C5      | 15      | H1      | PC0                                   | I/O      | FTf           | -    | LPTIM1_IN1,<br>EVENTOUT,<br>LPUART1_RX,<br>I2C3_SCL | ADC_IN10                               |

| -      | -                       | -      | 9      | E2      | C4      | 16      | J2      | PC1                                   | I/O      | FTf           | -    | LPTIM1_OUT,<br>EVENTOUT,<br>LPUART1_TX,<br>I2C3_SDA | ADC_IN11                               |

| -      | -                       | -      | 10     | F2      | E7      | 17      | J3      | PC2                                   | I/O      | FTf           | -    | LPTIM1_IN2,<br>SPI2_MISO/I2S2_MCK                   | ADC_IN12                               |

Table 15. STM32L071xxx pin definition

| Pin number |                         |        |        |         |         |         |         |                                       |          |               |      |                                                                                                             |                      |

|------------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|---------------|------|-------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP32     | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                                                         | Additional functions |

| -          | -                       | -      | -      | -       | -       | 81      | C9      | PD0                                   | I/O      | FT            | -    | TIM21_CH1,<br>SPI2_NSS/I2S2_WS                                                                              | -                    |

| -          | -                       | -      | -      | -       | -       | 82      | B9      | PD1                                   | I/O      | FT            | -    | SPI2_SCK/I2S2_CK                                                                                            | -                    |

| -          | -                       | -      | 54     | В5      | -       | 83      | C8      | PD2                                   | I/O      | FT            | -    | LPUART1_RTS_DE,<br>TIM3_ETR,<br>USART5_RX                                                                   | -                    |

| -          | -                       | -      | -      | -       | -       | 84      | B8      | PD3                                   | I/O      | FT            | -    | USART2_CTS,<br>SPI2_MISO/I2S2_MCK                                                                           | -                    |

| -          | -                       | -      | -      | -       | -       | 85      | B7      | PD4                                   | I/O      | FT            | -    | USART2_RTS_DE,<br>SPI2_MOSI/I2S2_SD                                                                         | -                    |

| -          | -                       | -      | -      | -       | -       | 86      | A6      | PD5                                   | I/O      | FT            | -    | USART2_TX                                                                                                   | -                    |

| -          | -                       | -      | -      | -       | -       | 87      | B6      | PD6                                   | I/O      | FT            | -    | USART2_RX                                                                                                   | -                    |

| -          | -                       | -      | -      | -       | -       | 88      | A5      | PD7                                   | I/O      | FT            | -    | USART2_CK,<br>TIM21_CH2                                                                                     | -                    |

| 26         | -                       | 39     | 55     | A5      | A3      | 89      | A8      | PB3                                   | I/O      | FT            | -    | SPI1_SCK, TIM2_CH2,<br>EVENTOUT,<br>USART1_RTS_DE,<br>USART5_TX                                             | COMP2_INM            |

| 27         | 26                      | 40     | 56     | A4      | В3      | 90      | A7      | PB4                                   | I/O      | FTf           | -    | SPI1_MISO,<br>TIM3_CH1,<br>TIM22_CH1,<br>USART1_CTS,<br>USART5_RX,<br>I2C3_SDA                              | COMP2_INP            |

| 28         | 27                      | 41     | 57     | C4      | A4      | 91      | C5      | PB5                                   | I/O      | FT            | -    | SPI1_MOSI,<br>LPTIM1_IN1,<br>I2C1_SMBA,<br>TIM3_CH2/TIM22_CH2,<br>USART1_CK,<br>USART5_CK/USART5_<br>RTS_DE | COMP2_INP            |

| 29         | 28                      | 42     | 58     | D3      | В4      | 92      | B5      | PB6                                   | I/O      | FTf           | -    | USART1_TX,<br>I2C1_SCL,<br>LPTIM1_ETR,                                                                      | COMP2_INP            |

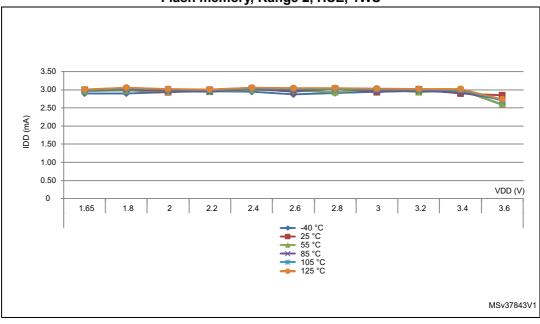

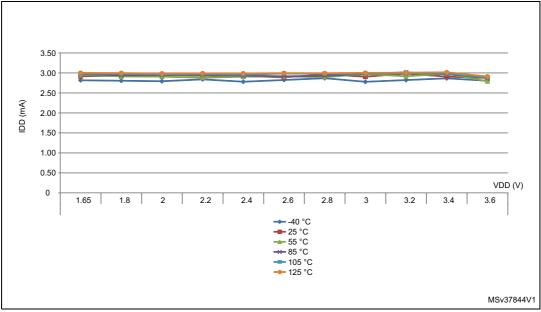

Figure 16.  $I_{DD}$  vs  $V_{DD}$ , at T<sub>A</sub>= 25/55/85/105 °C, Run mode, code running from Flash memory, Range 2, HSE, 1WS

|                     |       | Typical consumption, V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C |                  |                                                       |                               |                                |  |

|---------------------|-------|----------------------------------------------------------------------|------------------|-------------------------------------------------------|-------------------------------|--------------------------------|--|

| Peripheral          |       | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01                |                  | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                           |  |

|                     | GPIOA | 3.5                                                                  | 3                | 2.5                                                   | 2.5                           |                                |  |

|                     | GPIOB | 3.5                                                                  | 2.5              | 2                                                     | 2.5                           |                                |  |

| Cortex-<br>M0+ core | GPIOC | 8.5                                                                  | 6.5              | 5.5                                                   | 7                             | µA/MHz                         |  |

| I/O port            | GPIOD | 1                                                                    | 0.5              | 0.5                                                   | 0.5                           | (f <sub>HCLK</sub> )           |  |

|                     | GPIOE | 8                                                                    | 6                | 5                                                     | 6                             |                                |  |

|                     | GPIOH | 1.5                                                                  | 1                | 1                                                     | 0.5                           |                                |  |

|                     | CRC   | 1.5                                                                  | 1                | 1                                                     | 1                             |                                |  |

| AHB                 | FLASH | 0 <sup>(3)</sup>                                                     | 0 <sup>(3)</sup> | 0 <sup>(3)</sup>                                      | 0 <sup>(3)</sup>              | µA/MHz<br>(f <sub>HCLK</sub> ) |  |

|                     | DMA1  | 10                                                                   | 8                | 6.5                                                   | 8.5                           | (Inclk)                        |  |

| All enabled         |       | 204                                                                  | 162              | 130                                                   | 202                           | µА/МНz<br>(f <sub>HCLK</sub> ) |  |

| PWR                 |       | 2.5                                                                  | 2                | 2                                                     | 1                             | µA/MHz<br>(f <sub>HCLK</sub> ) |  |

| Table 39. Periph | neral current consum | ption in Run or S | Sleep mode <sup>(1)</sup> | (continued) |

|------------------|----------------------|-------------------|---------------------------|-------------|

|                  |                      |                   |                           |             |

Data based on differential I<sub>DD</sub> measurement between all peripherals off an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (range 1), f<sub>HCLK</sub> = 16 MHz (range 2), f<sub>HCLK</sub> = 4 MHz (range 3), f<sub>HCLK</sub> = 64kHz (Low-power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling. Not tested in production.

2. HSI oscillator is off for this measure.

3. Current consumption is negligible and close to 0  $\mu$ A.

| Symbol               | Parameter                                                                     | Conditions                                                        | Тур | Мах                                                                                               | Unit |

|----------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------|------|

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 5.0 | 8                                                                                                 |      |

|                      | Wakeup from Stop mode, regulator in Run mode                                  | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7                                                                                                 |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11                                                                                                |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 | 5.0 | 8                                                                                                 |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 2 | 5.0 | 8                                                                                                 |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 5.0 | 8                                                                                                 |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 7.3 | 13                                                                                                | μs   |

| t <sub>WUSTOP</sub>  | Wakeup from Stop mode, regulator in low-<br>power mode                        | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 13  | 23                                                                                                |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 28  | 38                                                                                                |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 51  | 65                                                                                                |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 100 | 120                                                                                               |      |

|                      |                                                                               | f <sub>HCLK</sub> = MSI = 65 kHz                                  | 190 | 260                                                                                               |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7                                                                                                 |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.0 | 11                                                                                                |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9 | 7                                                                                                 |      |

|                      | Wakeup from Stop mode, regulator in low-<br>power mode, code running from RAM | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 7.9 | 10                                                                                                |      |

|                      |                                                                               | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 4.7 | 8                                                                                                 |      |

| tumorpris            | Wakeup from Standby mode<br>FWU bit = 1                                       | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 65  | 130                                                                                               |      |

| <sup>t</sup> wustdby | Wakeup from Standby mode<br>FWU bit = 0                                       | f <sub>HCLK</sub> = MSI = 2.1 MHz                                 | 2.2 | 8<br>7<br>11<br>8<br>8<br>8<br>8<br>13<br>23<br>38<br>65<br>120<br>260<br>7<br>11<br>7<br>10<br>8 | ms   |

Table 41. Low-power mode wakeup timings (continued)

| Symbol                                | Parameter                          | Condition                                | Тур  | Мах | Unit |  |

|---------------------------------------|------------------------------------|------------------------------------------|------|-----|------|--|

|                                       |                                    | MSI range 0                              | 0.75 | -   |      |  |

|                                       |                                    | MSI range 1                              | 1    | -   |      |  |

|                                       |                                    | MSI range 2                              | 1.5  | -   |      |  |

| I <sub>DD(MSI)</sub> <sup>(2)</sup>   | MSI oscillator power consumption   | MSI range 3                              | 2.5  | -   | μA   |  |

|                                       |                                    | MSI range 4                              | 4.5  | -   |      |  |

|                                       |                                    | MSI range 5                              | 8    | -   |      |  |

|                                       |                                    | MSI range 6                              | 15   | -   |      |  |

|                                       |                                    | MSI range 0                              | 30   | -   |      |  |

|                                       |                                    | MSI range 1                              | 20   | -   |      |  |

|                                       |                                    | MSI range 2                              | 15   | -   |      |  |

|                                       |                                    | MSI range 3                              | 10   | -   | μs   |  |

| tournon                               | MSI oscillator startup time        | MSI range 4                              | 6    | -   |      |  |

| t <sub>SU(MSI)</sub>                  |                                    | MSI range 5                              | 5    | -   |      |  |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | 3.5  | -   |      |  |

|                                       |                                    | MSI range 6,<br>Voltage range 3          | 5    | -   |      |  |

|                                       |                                    | MSI range 0                              | -    | 40  | -    |  |

|                                       |                                    | MSI range 1                              | -    | 20  |      |  |

|                                       |                                    | MSI range 2                              | -    | 10  |      |  |

|                                       |                                    | MSI range 3                              | -    | 4   |      |  |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> | MSI oscillator stabilization time  | MSI range 4                              | -    | 2.5 | μs   |  |

| •STAB(MSI)                            |                                    | MSI range 5                              | -    | 2   | μο   |  |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -    | 2   |      |  |

|                                       |                                    | MSI range 3,<br>Voltage range 3          | -    | 3   |      |  |

| former                                | MSI oscillator frequency overshoot | Any range to range 5                     | -    | 4   |      |  |

| f <sub>OVER(MSI)</sub>                |                                    | Any range to range 6                     | -    | 6   | MHz  |  |

Table 48. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions        | Monitored<br>frequency band | Max vs.<br>frequency<br>range at<br>32 MHz | Unit |  |

|------------------|------------|-------------------|-----------------------------|--------------------------------------------|------|--|

| e                |            | $V_{DD} = 3.6 V,$ | 0.1 to 30 MHz               | -7                                         |      |  |

|                  | Peak level |                   | 30 to 130 MHz               | 14                                         | dBµV |  |

| S <sub>EMI</sub> | reak level |                   | 130 MHz to 1 GHz            | 9                                          |      |  |

|                  |            |                   | EMI Level                   | 2                                          | -    |  |

| Table # | 54. EMI | characteristics |

|---------|---------|-----------------|

|---------|---------|-----------------|

### 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Symbol                | Ratings                                                     | Conditions                                                     | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|----------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)          | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/JEDEC JS-001  | 2     | 2000                            | v    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge<br>voltage (charge device<br>model) | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/ESD STM5.3.1. | C4    | 500                             |      |

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 56. Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +125$ °C conforming to JESD78A | II level A |

#### **SPI characteristics**

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                            | Conditions                                                  | Min     | Тур   | Max               | Unit |

|----------------------------------------------|--------------------------------------|-------------------------------------------------------------|---------|-------|-------------------|------|

|                                              |                                      | Master mode                                                 |         |       | 16                |      |

|                                              |                                      | Slave mode<br>receiver                                      | -       | -     | 16                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode<br>Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 12 <sup>(2)</sup> | MHz  |

|                                              |                                      | Slave mode<br>Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                                  | 30      | 50    | 70                | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI<br>presc = 2                                | 4*Tpclk | -     | -                 |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI<br>presc = 2                                | 2*Tpclk | -     | -                 |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                                 | Tpclk-2 | Tpclk | Tpclk+<br>2       |      |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                                 | 0       | -     | -                 |      |

| t <sub>su(SI)</sub>                          |                                      | Slave mode                                                  | 3       | -     | -                 |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                                 | 7       | -     | -                 |      |

| t <sub>h(SI)</sub>                           | Data input noid time                 | Slave mode                                                  | 3.5     | -     | -                 | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                                  | 15      | -     | 36                |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                                  | 10      | -     | 30                |      |

| +                                            |                                      | Slave mode<br>1.65 V <v<sub>DD&lt;3.6 V</v<sub>             | -       | 18    | 41                |      |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode<br>2.7 V <v<sub>DD&lt;3.6 V</v<sub>              | -       | 18    | 25                |      |

| t <sub>v(MO)</sub>                           | ]                                    | Master mode                                                 | -       | 4     | 7                 |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                                                  | 10      | -     | -                 |      |

| t <sub>h(MO)</sub>                           |                                      | Master mode                                                 | 0       | -     | -                 |      |

| Table 72. SPI characteristics | s in voltage Range 1 <sup>(1)</sup> |

|-------------------------------|-------------------------------------|

|-------------------------------|-------------------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

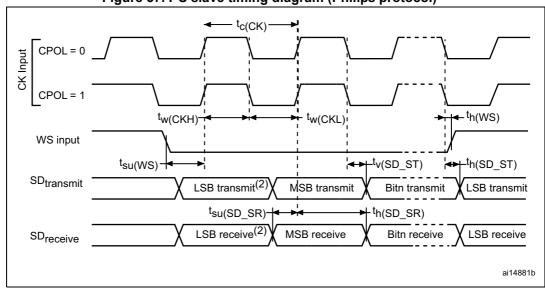

Figure 37. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels:  $0.3 \times V_{DD}$  and  $0.7 \times V_{DD}$ .

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

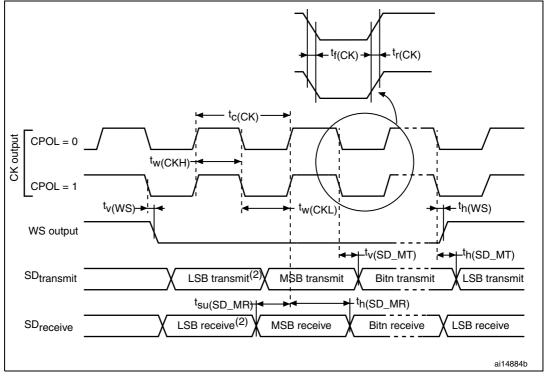

#### Figure 38. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| Е      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |

| Table 76. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

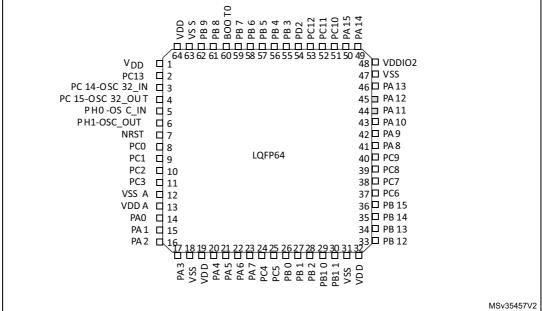

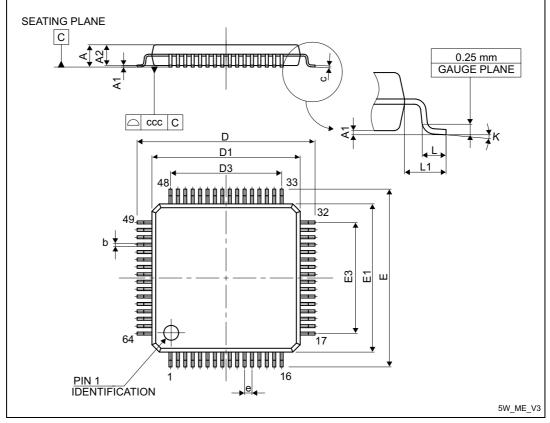

## 7.3 LQFP64 package information

Figure 44. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 79. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat |  |  |

|-------------------------------------------------------------|--|--|

| package mechanical data                                     |  |  |

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах   | Min                   | Тур    | Мах    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

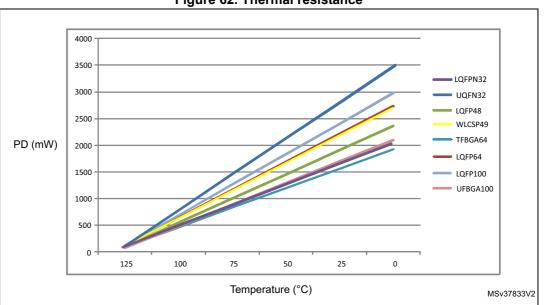

### 7.9.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 02-Sep-2015 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 26-Oct-2015 | 2        | Changed confidentiality level to public.<br>Updated datasheet status to "production data".<br>Modified ultra-low-power platform features on cover page.<br>In <i>Table 15: STM32L071xxx pin definition</i> :<br>– changed pin name to VDDIO2 for the following pins:<br>UFQFPN32 pin 24, LQFP48 pin 36, LQFP64 pin 48, UFBGA64<br>pin E5, WLCSP49 pin A1, LQFP100 pin 75 and UFBGA100 pin<br>G11.<br>– Added note related to UFQFPN32.<br>In <i>Section 6: Electrical characteristics</i> , updated notes related to<br>values guaranteed by characterization.<br>Updated  ΔV <sub>SS</sub>   definition to include V <sub>REF-</sub> in <i>Table 22: Voltage</i><br><i>characteristics</i> .<br>Updated f <sub>TRIG</sub> and V <sub>AIN</sub> maximum value, added V <sub>REF+</sub> and V <sub>REF-</sub><br>in <i>Table 62: ADC characteristics</i> .<br>Added Section : Device marking for LQFP100.<br>Updated Figure 42: UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm<br>pitch, ultra fine pitch ball grid array package outline and Table 76:<br>LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package<br>mechanical data.<br>Added Section : Device marking for LQFP100, Section : Device<br>marking for LQFP64, Section : Device marking for TFBGA64 and<br>Section : Device marking for WLCSP49.<br>Updated Figure 55: LQFP48 marking example (package top<br>view). |  |

### Table 89. Document revision history