Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 23                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 3K x 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

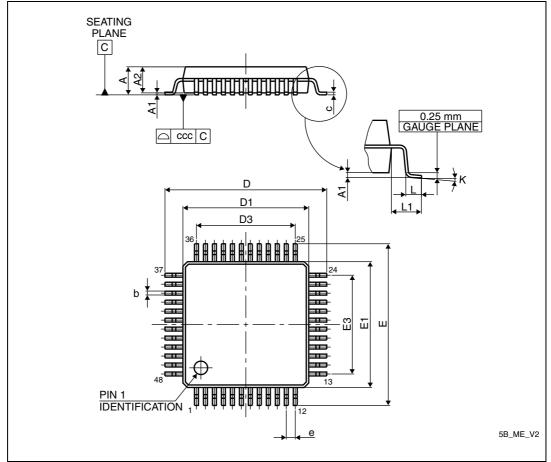

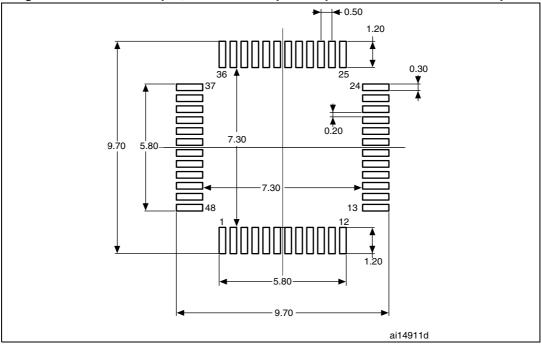

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l071k8u3 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.1 Device overview

| Table 2. Ultra-low- | power STM32L071xx | device features ar | d peripheral counts |

|---------------------|-------------------|--------------------|---------------------|

|                     |                   |                    |                     |

| Perip                              | heral               | eral STM32L O71VZ |                                                                             |                       |                        |                    |                        | STM32L<br>071RZ      |                        |                                               |                       |                      |  |

|------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|------------------------|--------------------|------------------------|----------------------|------------------------|-----------------------------------------------|-----------------------|----------------------|--|

| Flash (Kbyt                        | es)                 |                                                                                                                     | 64 Kbytes                                                                   |                       |                        | 128 Kb             | ytes                   |                      | 192 Kbytes             |                                               |                       |                      |  |

| Data EEPRO                         | OM (Kbytes)         |                                                                                                                     | 3 Kbytes                                                                    |                       |                        |                    |                        | 6 Ki                 | oytes                  |                                               |                       |                      |  |

| RAM (Kbyte                         | s)                  |                                                                                                                     |                                                                             |                       |                        |                    | 20 Kbytes              |                      |                        |                                               |                       |                      |  |

|                                    | General-<br>purpose |                                                                                                                     | 4                                                                           |                       |                        |                    |                        |                      |                        |                                               |                       |                      |  |

| Timers                             | Basic               |                                                                                                                     |                                                                             |                       |                        |                    | 2                      |                      |                        |                                               |                       |                      |  |

|                                    | LPTIMER             |                                                                                                                     |                                                                             |                       |                        |                    | 1                      |                      |                        |                                               |                       |                      |  |

| RTC/SYST<br>/WW                    |                     |                                                                                                                     |                                                                             |                       |                        |                    | 1/1/1/1                |                      |                        |                                               |                       |                      |  |

|                                    | SPI/I2S             | 4(3) <sup>(1)</sup> /0 6(4) <sup>(2)</sup> /1                                                                       |                                                                             |                       | 4(3) <sup>(1)</sup> /0 |                    | 6(4) <sup>(2)</sup> /1 |                      | 4(3) <sup>(1)</sup> /0 | 4(3) <sup>(1)</sup> /0 6(4) <sup>(2)</sup> /1 |                       |                      |  |

| Com.                               | l <sup>2</sup> C    | 2 3                                                                                                                 |                                                                             |                       | 2                      |                    | 3                      |                      | 2                      | 3                                             |                       |                      |  |

| nterfaces                          | USART               | 3 4                                                                                                                 |                                                                             |                       | 3                      |                    | 4                      |                      | 3                      | 4                                             |                       |                      |  |

|                                    | LPUART              |                                                                                                                     |                                                                             |                       |                        |                    | 1                      |                      |                        |                                               |                       |                      |  |

| GPIOs                              |                     | 23                                                                                                                  | 37                                                                          | 84                    | 25 <sup>(3)</sup>      | 40 <sup>(4)</sup>  | 84                     | 51 <sup>(5)</sup>    | 25 <sup>(3)</sup>      | 40 <sup>(4)</sup>                             | 84                    | 51 <sup>(5)</sup>    |  |

| Clocks:<br>HSE/LSE/H               | SI/MSI/LSI          | 1/1/1/1/1                                                                                                           |                                                                             |                       |                        |                    |                        |                      |                        |                                               |                       |                      |  |

| 12-bit synch<br>ADC<br>Number of o |                     | 1<br>10                                                                                                             |                                                                             |                       |                        |                    |                        |                      | 1<br>16                | 1<br>16 <sup>(5)</sup>                        |                       |                      |  |

| Comparator                         | s                   |                                                                                                                     |                                                                             |                       |                        |                    | 2                      |                      |                        |                                               |                       |                      |  |

| Max. CPU fr                        | equency             |                                                                                                                     |                                                                             |                       |                        |                    | 32 MHz                 |                      |                        |                                               |                       |                      |  |

| Operating v                        | oltage              |                                                                                                                     | 1.8 V to                                                                    | o 3.6 V (dov          | vn to 1.65 V           | at power-do        | wn) with B0            | OR option 1          | 1.65 to 3.6 V          | / without BOF                                 | R option              |                      |  |

| Operating<br>temperature           | es                  |                                                                                                                     | Ambient temperature: -40 to +125 °C<br>Junction temperature: -40 to +130 °C |                       |                        |                    |                        |                      |                        |                                               |                       |                      |  |

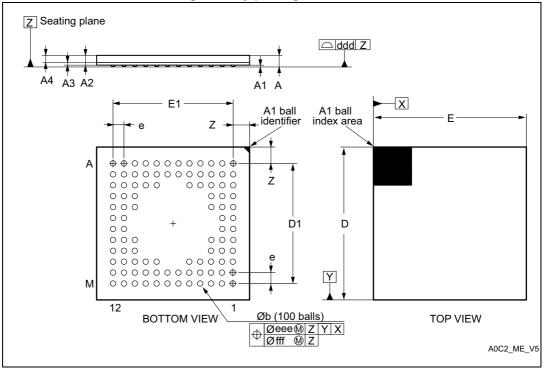

| Packages                           |                     | UFQFPN<br>32                                                                                                        | LQFP48                                                                      | LQFP/<br>UFBGA<br>100 | UFQFPN/<br>LQFP32      | LQFP48,<br>WLCSP49 | LQFP/<br>UFBGA<br>100  | LQFP/<br>TFBGA<br>64 | UFQFPN/<br>LQFP32      | LQFP48,<br>WLCSP49                            | LQFP/<br>UFBGA<br>100 | LQFP/<br>TFBGA<br>64 |  |

1. 3 SPI interfaces are USARTs operating in SPI master mode.

2. 4 SPI interfaces are USARTs operating in SPI master mode.

3. UFQFPN32 has 2 GPIOs less than LQFP32.

4. LQFP48 has three GPIOs less than WLCSP49.

5. TFBGA64 has one GPIO, one ADC input less than LQFP64.

| Table 3. Functionalities de | pending on the or | perating power sup | ply range (continued) |

|-----------------------------|-------------------|--------------------|-----------------------|

|                             |                   |                    |                       |

| Operating power supply         | Functionalities depending on the operating power supply range |                                  |                      |  |  |  |  |  |

|--------------------------------|---------------------------------------------------------------|----------------------------------|----------------------|--|--|--|--|--|

| range                          | ADC operation                                                 | Dynamic voltage<br>scaling range | I/O operation        |  |  |  |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V | Conversion time up<br>to 1.14 Msps                            | Range 1, range 2 or range 3      | Full speed operation |  |  |  |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V | Conversion time up<br>to 1.14 Msps                            | Range 1, range 2 or<br>range 3   | Full speed operation |  |  |  |  |  |

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.</li>

| Table 4. CPU frequency range | depending on d | ynamic voltage scaling |

|------------------------------|----------------|------------------------|

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

# Table 5. Functionalities depending on the working mode(from Run/active down to standby) (1)(2)

|                                           |            |       | Low-         | Low-           |     | Stop                 | S | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|-----|----------------------|---|----------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |     | Wakeup<br>capability |   | Wakeup<br>capability |

| CPU                                       | Y          |       | Y            |                |     |                      |   |                      |

| Flash memory                              | 0          | 0     | 0            | 0              |     |                      |   |                      |

| RAM                                       | Y          | Y     | Y            | Y              | Y   |                      |   |                      |

| Backup registers                          | Y          | Y     | Y            | Y              | Y   |                      | Y |                      |

| EEPROM                                    | 0          | 0     | 0            | 0              |     |                      |   |                      |

| Brown-out reset<br>(BOR)                  | 0          | 0     | 0            | 0              | 0   | Ο                    | 0 | 0                    |

| DMA                                       | 0          | 0     | 0            | 0              |     |                      |   |                      |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | 0     | 0            | Ο              | 0   | 0                    | - |                      |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y     | Y            | Y              | Y   | Y                    | Y | Y                    |

| High Speed<br>Internal (HSI)              | 0          | 0     |              |                | (3) |                      |   |                      |

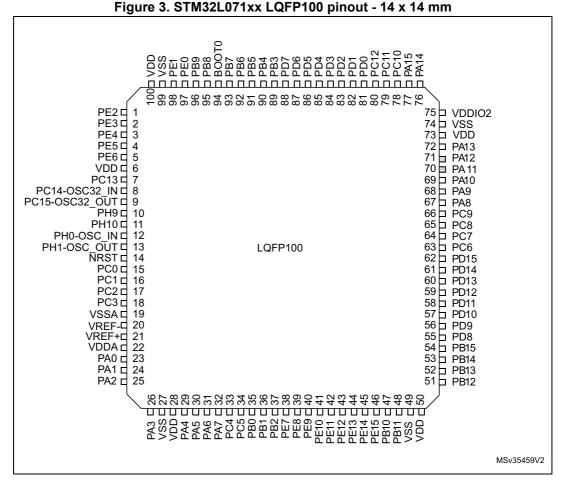

## 4 Pin descriptions

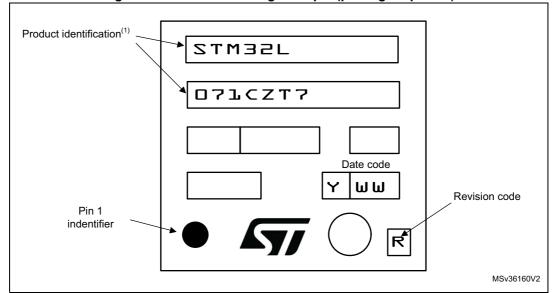

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

|        |                         |        | Pin n  | umbo    | er      |         |         |                                       | -        |               |      |                                                                     |                                           |

|--------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|---------------|------|---------------------------------------------------------------------|-------------------------------------------|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                 | Additional functions                      |

| -      | -                       | -      | 11     | -       | -       | 18      | K2      | PC3                                   | I/O      | FT            | -    | LPTIM1_ETR,<br>SPI2_MOSI/I2S2_SD                                    | ADC_IN13                                  |

| -      | 4                       | 8      | 12     | F1      | -       | 19      | J1      | VSSA                                  | S        |               | -    | -                                                                   | -                                         |

| -      | -                       | -      | -      | -       | -       | 20      | K1      | VREF-                                 | S        |               | -    | -                                                                   | -                                         |

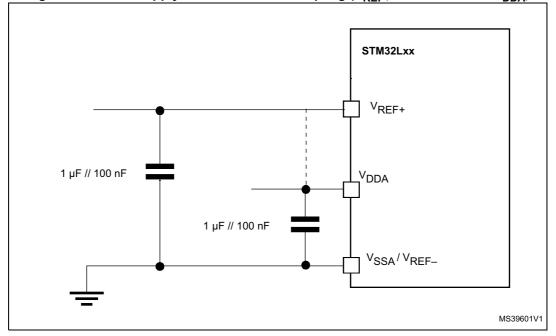

| -      | -                       | I      | -      | G1      | E6      | 21      | L1      | VREF+                                 | S        |               | -    | -                                                                   | -                                         |

| 5      | 5                       | 9      | 13     | H1      | F7      | 22      | M1      | VDDA                                  | S        |               | -    | -                                                                   | -                                         |

| 6      | 6                       | 10     | 14     | G2      | E5      | 23      | L2      | PA0                                   | I/O      | ТТа           | -    | TIM2_CH1,<br>USART2_CTS,<br>TIM2_ETR,<br>USART4_TX,<br>COMP1_OUT    | COMP1_INM,<br>ADC_IN0,<br>RTC_TAMP2/WKUP1 |

| 7      | 7                       | 11     | 15     | H2      | E4      | 24      | M2      | PA1                                   | I/O      | FT            | -    | EVENTOUT,<br>TIM2_CH2,<br>USART2_RTS_DE,<br>TIM21_ETR,<br>USART4_RX | COMP1_INP,<br>ADC_IN1                     |

| 8      | 8                       | 12     | 16     | F3      | F6      | 25      | K3      | PA2                                   | I/O      | FT            | -    | TIM21_CH1,<br>TIM2_CH3,<br>USART2_TX,<br>LPUART1_TX,<br>COMP2_OUT   | COMP2_INM,<br>ADC_IN2                     |

| 9      | 9                       | 13     | 17     | G3      | G7      | 26      | L3      | PA3                                   | I/O      | FT            | -    | TIM21_CH2,<br>TIM2_CH4,<br>USART2_RX,<br>LPUART1_RX                 | COMP2_INP,<br>ADC_IN3                     |

| -      | -                       | I      | 18     | C2      | -       | 27      | D3      | VSS                                   | s        | -             | -    | -                                                                   | -                                         |

| -      | -                       | I      | 19     | D2      | -       | 28      | H3      | VDD                                   | S        | -             | -    | -                                                                   | -                                         |

| 10     | 10                      | 14     | 20     | H3      | F5      | 29      | М3      | PA4                                   | I/O      | тс            | -    | SPI1_NSS,<br>USART2_CK,<br>TIM22_ETR                                | COMP1_INM,<br>COMP2_INM,<br>ADC_IN4       |

| 11     | 11                      | 15     | 21     | F4      | G6      | 30      | K4      | PA5                                   | I/O      | тс            | -    | SPI1_SCK, TIM2_ETR,<br>TIM2_CH1                                     | COMP1_INM,<br>COMP2_INM,<br>ADC_IN5       |

|        |                         | I      | Pin n  | umbe    | ər      |         |         |                                       |          |               |      |                                                                              |                      |

|--------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|---------------|------|------------------------------------------------------------------------------|----------------------|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                          | Additional functions |

| -      | -                       | -      | 39     | E8      | -       | 65      | E10     | PC8                                   | I/O      | FT            | -    | TIM22_ETR, TIM3_CH3                                                          | -                    |

| -      | -                       | -      | 40     | D8      | -       | 66      | D12     | PC9                                   | I/O      | FTf           | -    | TIM21_ETR,<br>TIM3_CH4, I2C3_SDA                                             | -                    |

| 18     | 18                      | 29     | 41     | D7      | D1      | 67      | D11     | PA8                                   | I/O      | FTf           | -    | MCO, EVENTOUT,<br>USART1_CK,<br>I2C3_SCL                                     | -                    |

| 19     | 19                      | 30     | 42     | C7      | E2      | 68      | D10     | PA9                                   | I/O      | FTf           | -    | MCO, USART1_TX,<br>I2C1_SCL, I2C3_SMBA                                       | -                    |

| 20     | 20                      | 31     | 43     | C6      | C1      | 69      | C12     | PA10                                  | I/O      | FTf           | -    | USART1_RX,<br>I2C1_SDA                                                       | -                    |

| 21     | 21                      | 32     | 44     | C8      | D2      | 70      | B12     | PA11                                  | I/O      | FT            | -    | SPI1_MISO,<br>EVENTOUT,<br>USART1_CTS,<br>COMP1_OUT                          | -                    |

| 22     | 22                      | 33     | 45     | B8      | B1      | 71      | A12     | PA12                                  | I/O      | FT            | -    | SPI1_MOSI,<br>EVENTOUT,<br>USART1_RTS_DE,<br>COMP2_OUT                       | -                    |

| 23     | 23                      | 34     | 46     | A8      | C2      | 72      | A11     | PA13                                  | I/O      | FT            | I    | SWDIO, LPUART1_RX                                                            | -                    |

| -      | -                       | 1      | -      | -       | -       | 73      | C11     | VDD                                   | S        |               | I    | -                                                                            | -                    |

| -      | -                       | 35     | 47     | D5      | -       | 74      | F11     | VSS                                   | S        |               | -    | -                                                                            | -                    |

| -      | 24                      | 36     | 48     | E5      | A1      | 75      | G11     | VDDIO2                                | S        |               | -    | -                                                                            | -                    |

| 24     | 25                      | 37     | 49     | A7      | B2      | 76      | A10     | PA14                                  | I/O      | FT            | -    | SWCLK, USART2_TX,<br>LPUART1_TX                                              | -                    |

| 25     | -                       | 38     | 50     | A6      | A2      | 77      | A9      | PA15                                  | I/O      | FT            | -    | SPI1_NSS, TIM2_ETR,<br>EVENTOUT,<br>USART2_RX,<br>TIM2_CH1,<br>USART4_RTS_DE | -                    |

| -      | -                       | -      | 51     | B7      | -       | 78      | B11     | PC10                                  | I/O      | FT            | -    | LPUART1_TX,<br>USART4_TX                                                     | -                    |

| -      | -                       | -      | 52     | B6      | -       | 79      | C10     | PC11                                  | I/O      | FT            | -    | LPUART1_RX,<br>USART4_RX                                                     | -                    |

| -      | -                       | -      | 53     | C5      | -       | 80      | B10     | PC12                                  | I/O      | FT            | -    | USART5_TX,<br>USART4_CK                                                      | -                    |

Table 15. STM32L071xxx pin definition (continued)

| Pin number |                         |        |        |         | -       |         |         |                                       |          |               |      |                                                                                                             |                      |

|------------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|---------------|------|-------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP32     | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                                                         | Additional functions |

| -          | -                       | -      | -      | -       | -       | 81      | C9      | PD0                                   | I/O      | FT            | -    | TIM21_CH1,<br>SPI2_NSS/I2S2_WS                                                                              | -                    |

| -          | -                       | -      | -      | -       | -       | 82      | B9      | PD1                                   | I/O      | FT            | -    | SPI2_SCK/I2S2_CK                                                                                            | -                    |

| -          | -                       | -      | 54     | В5      | -       | 83      | C8      | PD2                                   | I/O      | FT            | -    | LPUART1_RTS_DE,<br>TIM3_ETR,<br>USART5_RX                                                                   | -                    |

| -          | -                       | -      | -      | -       | -       | 84      | B8      | PD3                                   | I/O      | FT            | -    | USART2_CTS,<br>SPI2_MISO/I2S2_MCK                                                                           | -                    |

| -          | -                       | -      | -      | -       | -       | 85      | B7      | PD4                                   | I/O      | FT            | -    | USART2_RTS_DE,<br>SPI2_MOSI/I2S2_SD                                                                         | -                    |

| -          | -                       | -      | -      | -       | -       | 86      | A6      | PD5                                   | I/O      | FT            | -    | USART2_TX                                                                                                   | -                    |

| -          | -                       | -      | -      | -       | -       | 87      | B6      | PD6                                   | I/O      | FT            | -    | USART2_RX                                                                                                   | -                    |

| -          | -                       | -      | -      | -       | -       | 88      | A5      | PD7                                   | I/O      | FT            | -    | USART2_CK,<br>TIM21_CH2                                                                                     | -                    |

| 26         | -                       | 39     | 55     | A5      | A3      | 89      | A8      | PB3                                   | I/O      | FT            | -    | SPI1_SCK, TIM2_CH2,<br>EVENTOUT,<br>USART1_RTS_DE,<br>USART5_TX                                             | COMP2_INM            |

| 27         | 26                      | 40     | 56     | A4      | В3      | 90      | A7      | PB4                                   | I/O      | FTf           | -    | SPI1_MISO,<br>TIM3_CH1,<br>TIM22_CH1,<br>USART1_CTS,<br>USART5_RX,<br>I2C3_SDA                              | COMP2_INP            |

| 28         | 27                      | 41     | 57     | C4      | A4      | 91      | C5      | PB5                                   | I/O      | FT            | -    | SPI1_MOSI,<br>LPTIM1_IN1,<br>I2C1_SMBA,<br>TIM3_CH2/TIM22_CH2,<br>USART1_CK,<br>USART5_CK/USART5_<br>RTS_DE | COMP2_INP            |

| 29         | 28                      | 42     | 58     | D3      | В4      | 92      | B5      | PB6                                   | I/O      | FTf           | -    | USART1_TX,<br>I2C1_SCL,<br>LPTIM1_ETR,                                                                      | COMP2_INP            |

|        |                         |        | Pin n  | umb     | er      |         |         |                                       |                   |               |          |                                                      |                           |

|--------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|-------------------|---------------|----------|------------------------------------------------------|---------------------------|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type          | I/O structure | Note     | Alternate functions                                  | Additional functions      |

| 30     | 29                      | 43     | 59     | C3      | C3      | 93      | B4      | PB7                                   | I/O               | FTf           | -        | USART1_RX,<br>I2C1_SDA,<br>LPTIM1_IN2,<br>USART4_CTS | COMP2_INP,<br>VREF_PVD_IN |

| 31     | 30                      | 44     | 60     | B4      | A5      | 94      | A4      | BOOT0                                 | Ι                 |               | -        | -                                                    | -                         |

| -      | -                       | 45     | 61     | B3      | B5      | 95      | A3      | PB8                                   | I/O               | FTf           | -        | I2C1_SCL                                             | -                         |

| -      | -                       | 46     | 62     | A3      | A6      | 96      | В3      | PB9                                   | I/O               | FTf           | -        | EVENTOUT,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS           | -                         |

| -      | -                       | -      | -      | -       | -       | 97      | C3      | PE0                                   | I/O FT - EVENTOUT |               | -        |                                                      |                           |

| -      | -                       | -      | -      | -       | -       | 98      | A2      | PE1                                   | I/O FT - EVENTOUT |               | EVENTOUT | -                                                    |                           |

| 32     | 31                      | 47     | 63     | D4      | -       | 99      | D3      | VSS                                   | S                 |               | -        |                                                      |                           |

| -      | 32                      | 48     | 64     | E4      | A7      | 100     | C4      | VDD                                   | S                 |               | -        | -                                                    | -                         |

| Table 15. STM32L071xxx | pin definition ( | continued) |

|------------------------|------------------|------------|

|------------------------|------------------|------------|

1. UFQFPN32 pinout differs from other STM32 devices except STM32L07xxx and STM32L8xxx.

| 48              |      |      |                                                                                           |                                 | Table 18. Alter                                                             | nate functior     | ns port C                                          |                                              |                                                             |                                   |

|-----------------|------|------|-------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------|-------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|-----------------------------------|

| 48/136          |      |      | AF0                                                                                       | AF1                             | AF2                                                                         | AF3               | AF4                                                | AF5                                          | AF6                                                         | AF7                               |

|                 |      | Port | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/<br>LPTIM1/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2C1/<br>TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/<br>LPTIM1/TIM2/3<br>/EVENTOUT/SYS_AF | I2C1/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2<br>/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/E<br>VENTOUT | I2C3/LPUART1/<br>COMP1/2/<br>TIM3 |

|                 |      | PC0  | LPTIM1_IN1                                                                                |                                 | EVENTOUT                                                                    |                   |                                                    |                                              | LPUART1_RX                                                  | I2C3_SCL                          |

|                 |      | PC1  | LPTIM1_OUT                                                                                |                                 | EVENTOUT                                                                    |                   |                                                    |                                              | LPUART1_TX                                                  | I2C3_SDA                          |

|                 |      | PC2  | LPTIM1_IN2                                                                                |                                 | SPI2_MISO/<br>I2S2_MCK                                                      |                   |                                                    |                                              |                                                             |                                   |

| _               |      | PC3  | LPTIM1_ETR                                                                                |                                 | SPI2_MOSI/<br>I2S2_SD                                                       |                   |                                                    |                                              |                                                             |                                   |

| DocID027101 Rev |      | PC4  | EVENTOUT                                                                                  |                                 | LPUART1_TX                                                                  |                   |                                                    |                                              |                                                             |                                   |

| 0027            |      | PC5  |                                                                                           |                                 | LPUART1_RX                                                                  |                   |                                                    |                                              |                                                             |                                   |

| 7101            | U    | PC6  | TIM22_CH1                                                                                 |                                 | TIM3_CH1                                                                    |                   |                                                    |                                              |                                                             |                                   |

| Re              | Port | PC7  | TIM22_CH2                                                                                 |                                 | TIM3_CH2                                                                    |                   |                                                    |                                              |                                                             |                                   |

| ×<br>د          | _    | PC8  | TIM22_ETR                                                                                 |                                 | TIM3_CH3                                                                    |                   |                                                    |                                              |                                                             |                                   |

|                 |      | PC9  | TIM21_ETR                                                                                 |                                 | TIM3_CH4                                                                    |                   |                                                    |                                              |                                                             | I2C3_SDA                          |

|                 |      | PC10 | LPUART1_TX                                                                                |                                 |                                                                             |                   |                                                    |                                              | USART4_TX                                                   |                                   |

|                 |      | PC11 | LPUART1_RX                                                                                |                                 |                                                                             |                   |                                                    |                                              | USART4_RX                                                   |                                   |

|                 |      | PC12 |                                                                                           |                                 | USART5_TX                                                                   |                   |                                                    |                                              | USART4_CK                                                   |                                   |

|                 |      | PC13 |                                                                                           |                                 |                                                                             |                   |                                                    |                                              |                                                             |                                   |

|                 |      | PC14 |                                                                                           |                                 |                                                                             |                   |                                                    |                                              |                                                             |                                   |

|                 |      | PC15 |                                                                                           |                                 |                                                                             |                   |                                                    |                                              |                                                             |                                   |

5

| ו ה |        |      |                                                                                           |                                 |                                                                                 | Iternate func     | -                                                  |                                              |                                                             |                              |  |

|-----|--------|------|-------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------|-------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|------------------------------|--|

|     |        |      | AF0                                                                                       | AF1                             | AF2                                                                             | AF3               | AF4                                                | AF5                                          | AF6                                                         | AF7                          |  |

|     | Port   |      | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/<br>LPTIM1/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2C1/<br>TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/<br>LPTIM1/TIM2/3<br>/EVENTOUT/<br>SYS_AF | I2C1/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2<br>/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/E<br>VENTOUT | I2C3/LPUART1<br>COMP1/2/TIM3 |  |

|     |        | PD0  | TIM21_CH1                                                                                 | SPI2_NSS/I2S2_WS                | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD1  | -                                                                                         | SPI2_SCK/I2S2_CK                | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD2  | LPUART1_RTS_<br>DE                                                                        |                                 | TIM3_ETR                                                                        | -                 | -                                                  | -                                            | USART5_RX                                                   | -                            |  |

|     |        | PD3  | USART2_CTS                                                                                |                                 | SPI2_MISO/<br>I2S2_MCK                                                          | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD4  | USART2_RTS_D<br>E                                                                         | SPI2_MOSI/I2S2_SD               | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD5  | USART2_TX                                                                                 | -                               | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD6  | USART2_RX                                                                                 | -                               | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     | Port D | PD7  | USART2_CK                                                                                 | TIM21_CH2                       | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     | -      | PD8  | LPUART1_TX                                                                                |                                 | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD9  | LPUART1_RX                                                                                |                                 | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD10 | -                                                                                         |                                 | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD11 | LPUART1_CTS                                                                               |                                 | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD12 | LPUART1_RTS_<br>DE                                                                        |                                 | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD13 | -                                                                                         |                                 | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD14 | -                                                                                         |                                 | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

|     |        | PD15 |                                                                                           |                                 | -                                                                               | -                 | -                                                  | -                                            | -                                                           | -                            |  |

49/136

STM32L071xx

Pin descriptions

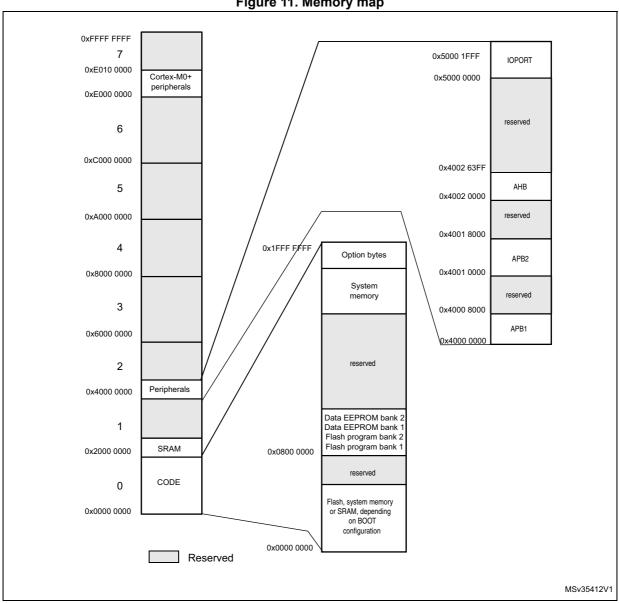

#### Memory mapping 5

Figure 11. Memory map

1. Refer to the STM32L071xx reference manual for details on the Flash memory organization for each memory size.

| Symbol                            | Parameter                                   | Condition                                                         |                                       | f <sub>HCLK</sub><br>(MHz) | Тур  | Max <sup>(1)</sup> | Unit     |  |

|-----------------------------------|---------------------------------------------|-------------------------------------------------------------------|---------------------------------------|----------------------------|------|--------------------|----------|--|

|                                   |                                             |                                                                   | Range3,                               | 1                          | 175  | 230                |          |  |

|                                   |                                             |                                                                   | Vcore=1.2 V                           | 2                          | 315  | 360                | μA       |  |

|                                   |                                             |                                                                   | VOS[1:0]=11                           | 4                          | 570  | 630                |          |  |

|                                   |                                             | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                        | Range2,                               | 4                          | 0,71 | 0,78               |          |  |

|                                   |                                             | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | Vcore=1.5 V<br>VOS[1:0]=10            | 8                          | 1,35 | 1,6                | mΑ<br>μΑ |  |

|                                   |                                             | 16 MHz (PLL ON) <sup>(2)</sup>                                    |                                       | 16                         | 2,7  | 3                  |          |  |

|                                   |                                             |                                                                   | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 8                          | 1,7  | 1,9                |          |  |

| I (Dup                            | Supply current in Run<br>mode code executed |                                                                   |                                       | 16                         | 3,2  | 3,7                |          |  |

| I <sub>DD</sub> (Run<br>from RAM) | from RAM, Flash                             |                                                                   |                                       | 32                         | 6,65 | 7,1                |          |  |

|                                   | memory switched off                         |                                                                   | Range3,                               | 0,065                      | 38   | 98                 |          |  |

|                                   |                                             | MSI clock                                                         | Vcore=1.2 V                           | 0,524                      | 105  | 160                |          |  |

|                                   |                                             |                                                                   | VOS[1:0]=11                           | 4,2                        | 615  | 710                |          |  |

|                                   |                                             | HSI clock source                                                  | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16                         | 2,85 | 3                  | mA       |  |

|                                   |                                             | (16 MHz)                                                          | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32                         | 6,85 | 7,3                |          |  |

### Table 31. Current consumption in Run mode, code with data processing running from RAM

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

# Table 32. Current consumption in Run mode vs code type,code with data processing running from RAM<sup>(1)</sup>

| Symbol                       | Parameter                       |                                                                                 | Conditions                                           |           | f <sub>HCLK</sub> | Тур  | Unit |

|------------------------------|---------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------|-----------|-------------------|------|------|

|                              |                                 | 6 6 mm 4m                                                                       |                                                      | Dhrystone |                   | 570  |      |

|                              |                                 |                                                                                 | Range 3,<br>V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 | CoreMark  | 4 MHz             | 670  |      |

|                              | Supply current in               |                                                                                 |                                                      | Fibonacci |                   | 410  | mA   |

| I <sub>DD</sub> (Run<br>from | Run mode, code<br>executed from | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,                  |                                                      | while(1)  |                   | 375  |      |

| RAM)                         | RAM, Flash<br>memory switched   | f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above<br>16 MHz (PLL on) <sup>(2)</sup> |                                                      | Dhrystone |                   | 6,65 |      |

|                              | off                             |                                                                                 | Range 1,<br>V <sub>CORE</sub> =1.8 V,                | CoreMark  | - 32 MHz          | 6,95 |      |

|                              |                                 |                                                                                 | VOS[1:0]=01                                          | Fibonacci |                   | 5,9  |      |

|                              |                                 |                                                                                 |                                                      | while(1)  |                   | 5,2  |      |

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

### Table 39. Peripheral current consumption in Run or Sleep mode<sup>(1)</sup>

|      |                     | Typical                                               | consumption, V                                        | / <sub>DD</sub> = 3.0 V, T <sub>A</sub> =             | 25 °C                         |                                |  |

|------|---------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|--------------------------------|--|

| Per  | ipheral             | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                           |  |

|      | CRS                 | 2.5                                                   | 2                                                     | 2                                                     | 2                             |                                |  |

|      | I2C1                | 11                                                    | 9.5                                                   | 7.5                                                   | 9                             |                                |  |

|      | I2C3                | 11                                                    | 9                                                     | 7                                                     | 9                             |                                |  |

|      | LPTIM1              | 10                                                    | 8.5                                                   | 6.5                                                   | 8                             |                                |  |

|      | LPUART1             | 8                                                     | 6.5                                                   | 5.5                                                   | 6                             |                                |  |

|      | SPI2                | 9                                                     | 4.5                                                   | 3.5                                                   | 4                             |                                |  |

|      | USART2              | 14.5                                                  | 12                                                    | 9.5                                                   | 11                            |                                |  |

|      | USART4              | 5                                                     | 4                                                     | 3                                                     | 5                             | µA/MHz<br>(f <sub>HCLK</sub> ) |  |

| APB1 | USART5              | 5                                                     | 4                                                     | 3                                                     | 5                             |                                |  |

|      | TIM2                | 10.5                                                  | 8.5                                                   | 7                                                     | 9                             |                                |  |

|      | TIM3                | 12                                                    | 10                                                    | 8                                                     | 11                            |                                |  |

|      | TIM6                | 3.5                                                   | 3                                                     | 2.5                                                   | 2                             |                                |  |

|      | TIM7                | 3.5                                                   | 3                                                     | 2.5                                                   | 2                             |                                |  |

|      | WWDG                | 3                                                     | 2                                                     | 2                                                     | 2                             |                                |  |

|      | ADC1 <sup>(2)</sup> | 5.5                                                   | 5                                                     | 3.5                                                   | 4                             |                                |  |

|      | SPI1                | 4                                                     | 3                                                     | 3                                                     | 2.5                           |                                |  |

|      | USART1              | 14.5                                                  | 11.5                                                  | 9.5                                                   | 12                            |                                |  |

| APB2 | TIM21               | 7.5                                                   | 6                                                     | 5                                                     | 5.5                           | µA/MHz                         |  |

| AFDZ | TIM22               | 7                                                     | 6                                                     | 5                                                     | 6                             | (f <sub>HCLK</sub> )           |  |

|      | FIREWALL            | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |  |

|      | DBGMCU              | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |  |

|      | SYSCFG              | 2.5                                                   | 2                                                     | 2                                                     | 1.5                           |                                |  |

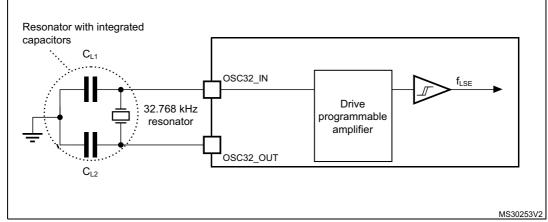

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 45*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                | Conditions <sup>(2)</sup>                          | Min <sup>(2)</sup> | Тур    | Max  | Unit |

|-------------------------------------|--------------------------|----------------------------------------------------|--------------------|--------|------|------|

| f <sub>LSE</sub>                    | LSE oscillator frequency |                                                    | -                  | 32.768 | -    | kHz  |

|                                     |                          | LSEDRV[1:0]=00<br>lower driving capability         | -                  | -      | 0.5  | μΑ/V |

| 6                                   | Maximum critical crystal | LSEDRV[1:0]= 01<br>medium low driving capability   | -                  | -      | 0.75 |      |

| G <sub>m</sub>                      | transconductance         | LSEDRV[1:0] = 10<br>medium high driving capability | -                  | -      | 1.7  | μΑνν |

|                                     |                          | LSEDRV[1:0]=11<br>higher driving capability        | -                  | -      | 2.7  | 2.7  |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time             | V <sub>DD</sub> is stabilized                      | -                  | 2      | -    | S    |

| Table 45. | LSE | oscillator | characteristics <sup>(1)</sup> |

|-----------|-----|------------|--------------------------------|

|           |     |            |                                |

1. Guaranteed by design.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. Guaranteed by characterization results. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

# *Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

DocID027101 Rev 3

## 6.3.8 PLL characteristics

The parameters given in *Table 49* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

| Symbol                 | Parameter                               |     | Unit                       |       |      |  |

|------------------------|-----------------------------------------|-----|----------------------------|-------|------|--|

| Symbol                 | Farameter                               | Min | lin Typ Max <sup>(1)</sup> |       | Unit |  |

| £                      | PLL input clock <sup>(2)</sup>          | 2   | -                          | 24    | MHz  |  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle              | 45  | -                          | 55    | %    |  |

| f <sub>PLL_OUT</sub>   | PLL output clock                        | 2   | -                          | 32    | MHz  |  |

| t <sub>LOCK</sub>      | PLL input = 16 MHz<br>PLL VCO = 96 MHz  | -   | 115                        | 160   | μs   |  |

| Jitter                 | Cycle-to-cycle jitter                   | -   |                            | ± 600 | ps   |  |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub> | -   | 220                        | 450   |      |  |

| I <sub>DD</sub> (PLL)  | Current consumption on V <sub>DD</sub>  | -   | 120                        | 150   | μA   |  |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

### 6.3.9 Memory characteristics

#### **RAM** memory

Table 50. RAM and hardware registers

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

### Flash memory and data EEPROM

#### Table 51. Flash memory and data EEPROM characteristics

| Symbol          | Parameter                                 | Conditions  | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |

|-----------------|-------------------------------------------|-------------|------|------|--------------------|------|--|

| V <sub>DD</sub> | Operating voltage<br>Read / Write / Erase | -           | 1.65 | -    | 3.6                | V    |  |

| +               | Programming time for word or half-page    | Erasing     | -    | 3.28 | 3.94               | - ms |  |

| ٩prog           |                                           | Programming | -    | 3.28 | 3.94               | 1115 |  |

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 53*. They are based on the EMS levels and classes defined in application note AN1709.

| Syn             | nbol | Parameter                                                                                                                         | Conditions                                                                                                     | Level/<br>Class |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FE</sub> | SD   | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| V <sub>EF</sub> | ТВ   | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP100, $T_A = +25$ °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4          | 4A              |

#### Table 53. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

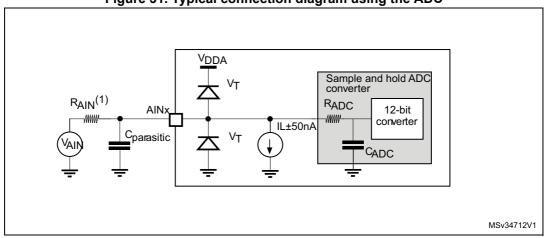

### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The simplified formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| T <sub>s</sub><br>(cycles) | t <sub>S</sub><br>(µs) | R <sub>AIN</sub> max for<br>fast channels<br>(kΩ) | ${\sf R}_{\sf AIN}$ max for standard channels (k $\Omega$ ) |                            |                            |                            |                             |                                                            |                                                           |