Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 50                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 6К х 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 15x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-TFBGA                                                              |

| Supplier Device Package    | 64-TFBGA (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l071rbh6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 3.15.1                     | I2C bus                                                           | 0         |  |  |  |  |  |  |  |

|---|--------|----------------------------|-------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

|   |        | 3.15.2                     | Universal synchronous/asynchronous receiver transmitter (USART) 3 | 1         |  |  |  |  |  |  |  |

|   |        | 3.15.3                     | Low-power universal asynchronous receiver transmitter (LPUART) 3  | 1         |  |  |  |  |  |  |  |

|   |        | 3.15.4                     | Serial peripheral interface (SPI)/Inter-integrated sound (I2S)    | 2         |  |  |  |  |  |  |  |

|   | 3.16   | Cyclic re                  | edundancy check (CRC) calculation unit                            | 2         |  |  |  |  |  |  |  |

|   | 3.17   | Serial w                   | ire debug port (SW-DP) 3                                          | 2         |  |  |  |  |  |  |  |

| 4 | Pin de | escripti                   | ons                                                               | 3         |  |  |  |  |  |  |  |

| 5 | Memo   | ory map                    | ping                                                              | 2         |  |  |  |  |  |  |  |

| 6 | Electr | Electrical characteristics |                                                                   |           |  |  |  |  |  |  |  |

|   | 6.1    | Parame                     | ter conditions                                                    | 3         |  |  |  |  |  |  |  |

|   |        | 6.1.1                      | Minimum and maximum values                                        | 3         |  |  |  |  |  |  |  |

|   |        | 6.1.2                      | Typical values                                                    | 3         |  |  |  |  |  |  |  |

|   |        | 6.1.3                      | Typical curves                                                    | 3         |  |  |  |  |  |  |  |

|   |        | 6.1.4                      | Loading capacitor                                                 | 3         |  |  |  |  |  |  |  |

|   |        | 6.1.5                      | Pin input voltage                                                 | 3         |  |  |  |  |  |  |  |

|   |        | 6.1.6                      | Power supply scheme                                               | 4         |  |  |  |  |  |  |  |

|   |        | 6.1.7                      | Current consumption measurement5                                  | 4         |  |  |  |  |  |  |  |

|   | 6.2    | Absolute                   | e maximum ratings                                                 | 5         |  |  |  |  |  |  |  |

|   | 6.3    | Operatir                   | ng conditions                                                     | 7         |  |  |  |  |  |  |  |

|   |        | 6.3.1                      | General operating conditions                                      | 57        |  |  |  |  |  |  |  |

|   |        | 6.3.2                      | Embedded reset and power control block characteristics            | 9         |  |  |  |  |  |  |  |

|   |        | 6.3.3                      | Embedded internal reference voltage6                              | 0         |  |  |  |  |  |  |  |

|   |        | 6.3.4                      | Supply current characteristics                                    | <b>;1</b> |  |  |  |  |  |  |  |

|   |        | 6.3.5                      | Wakeup time from low-power mode                                   | 3         |  |  |  |  |  |  |  |

|   |        | 6.3.6                      | External clock source characteristics                             | 5         |  |  |  |  |  |  |  |

|   |        | 6.3.7                      | Internal clock source characteristics7                            | '9        |  |  |  |  |  |  |  |

|   |        | 6.3.8                      | PLL characteristics                                               | 2         |  |  |  |  |  |  |  |

|   |        | 6.3.9                      | Memory characteristics                                            | 2         |  |  |  |  |  |  |  |

|   |        | 6.3.10                     | EMC characteristics                                               | 3         |  |  |  |  |  |  |  |

|   |        | 6.3.11                     | Electrical sensitivity characteristics                            | 6         |  |  |  |  |  |  |  |

|   |        | 6.3.12                     | I/O current injection characteristics                             | 7         |  |  |  |  |  |  |  |

|   |        | 6.3.13                     | I/O port characteristics                                          | 8         |  |  |  |  |  |  |  |

|   |        | 6.3.14                     | NRST pin characteristics9                                         | 2         |  |  |  |  |  |  |  |

|   |        | 6.3.15                     | 12-bit ADC characteristics9                                       | 3         |  |  |  |  |  |  |  |

|   |        |                            |                                                                   |           |  |  |  |  |  |  |  |

DocID027101 Rev 3

# 2.1 Device overview

| Table 2. Ultra-low- | power STM32L071xx | device features ar | d peripheral counts |

|---------------------|-------------------|--------------------|---------------------|

|                     |                   |                    |                     |

| Peripheral                         |                     | STM32L<br>071K8                                                             | STM32L<br>071C8 | STM32L<br>071V8       | STM32L<br>071KB        | STM32L<br>071CB        | STM32L<br>071VB        | STM32L<br>071RB        | STM32L<br>071KZ   | STM32L<br>071CZ        | STM32L<br>071VZ       | STM32L<br>071RZ        |  |

|------------------------------------|---------------------|-----------------------------------------------------------------------------|-----------------|-----------------------|------------------------|------------------------|------------------------|------------------------|-------------------|------------------------|-----------------------|------------------------|--|

| Flash (Kbyt                        | es)                 |                                                                             | 64 Kbytes       |                       |                        | 128 Kb                 | ytes                   |                        | 192 Kbytes        |                        |                       |                        |  |

| Data EEPRO                         | OM (Kbytes)         |                                                                             | 3 Kbytes        |                       |                        |                        |                        | 6 Ki                   | oytes             |                        |                       |                        |  |

| RAM (Kbyte                         | s)                  |                                                                             |                 |                       |                        |                        | 20 Kbytes              |                        |                   |                        |                       |                        |  |

|                                    | General-<br>purpose |                                                                             | 4               |                       |                        |                        |                        |                        |                   |                        |                       |                        |  |

| Timers                             | Basic               |                                                                             | 2               |                       |                        |                        |                        |                        |                   |                        |                       |                        |  |

|                                    | LPTIMER             |                                                                             | 1               |                       |                        |                        |                        |                        |                   |                        |                       |                        |  |

| RTC/SYST<br>/WW                    |                     |                                                                             |                 |                       |                        |                        | 1/1/1/1                |                        |                   |                        |                       |                        |  |

|                                    | SPI/I2S             | 4(3) <sup>(1)</sup> /0 6(4) <sup>(2)</sup> /1                               |                 |                       | 4(3) <sup>(1)</sup> /0 |                        | 6(4) <sup>(2)</sup> /1 |                        |                   | 6(4) <sup>(2)</sup> /1 |                       |                        |  |

| Com.                               | l <sup>2</sup> C    | 2                                                                           | 2 3             |                       |                        | 3                      |                        |                        | 2                 | 3                      |                       |                        |  |

| interfaces                         | USART               | 3                                                                           | 3 4             |                       |                        | 4                      |                        |                        | 3                 | 4                      |                       |                        |  |

|                                    | LPUART              |                                                                             |                 |                       |                        |                        | 1                      |                        |                   |                        |                       |                        |  |

| GPIOs                              |                     | 23                                                                          | 37              | 84                    | 25 <sup>(3)</sup>      | 40 <sup>(4)</sup>      | 84                     | 51 <sup>(5)</sup>      | 25 <sup>(3)</sup> | 40 <sup>(4)</sup>      | 84                    | 51 <sup>(5)</sup>      |  |

| Clocks:<br>HSE/LSE/H               | SI/MSI/LSI          | 1/1/1/1/1                                                                   |                 |                       |                        |                        |                        |                        |                   |                        |                       |                        |  |

| 12-bit synch<br>ADC<br>Number of o |                     | 1<br>10                                                                     | 1<br>13         | 1<br>16               | 1<br>10                | 1<br>13 <sup>(4)</sup> | 1<br>16                | 1<br>16 <sup>(5)</sup> | 1<br>10           | 1<br>13 <sup>(4)</sup> | 1<br>16               | 1<br>16 <sup>(5)</sup> |  |

| Comparator                         | s                   |                                                                             |                 |                       |                        |                        | 2                      |                        |                   |                        |                       |                        |  |

| Max. CPU fr                        | equency             |                                                                             |                 |                       |                        |                        | 32 MHz                 |                        |                   |                        |                       |                        |  |

| Operating v                        | oltage              |                                                                             | 1.8 V to        | o 3.6 V (dov          | vn to 1.65 V           | at power-do            | wn) with B0            | OR option 1            | 1.65 to 3.6 V     | / without BOF          | R option              |                        |  |

| Operating<br>temperature           | es                  | Ambient temperature: -40 to +125 °C<br>Junction temperature: -40 to +130 °C |                 |                       |                        |                        |                        |                        |                   |                        |                       |                        |  |

| Packages                           |                     | UFQFPN<br>32                                                                | LQFP48          | LQFP/<br>UFBGA<br>100 | UFQFPN/<br>LQFP32      | LQFP48,<br>WLCSP49     | LQFP/<br>UFBGA<br>100  | LQFP/<br>TFBGA<br>64   | UFQFPN/<br>LQFP32 | LQFP48,<br>WLCSP49     | LQFP/<br>UFBGA<br>100 | LQFP/<br>TFBGA<br>64   |  |

1. 3 SPI interfaces are USARTs operating in SPI master mode.

2. 4 SPI interfaces are USARTs operating in SPI master mode.

3. UFQFPN32 has 2 GPIOs less than LQFP32.

4. LQFP48 has three GPIOs less than WLCSP49.

5. TFBGA64 has one GPIO, one ADC input less than LQFP64.

# 3 Functional overview

## 3.1 Low-power modes

The ultra-low-power STM32L071xx support dynamic voltage scaling to optimize its power consumption in Run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply.

There are three power consumption ranges:

- Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), with the CPU running at up to 32 MHz

- Range 2 (full V<sub>DD</sub> range), with a maximum CPU frequency of 16 MHz

- Range 3 (full V<sub>DD</sub> range), with a maximum CPU frequency limited to 4.2 MHz

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs. Sleep mode power consumption at 16 MHz is about 1 mA with all peripherals off.

#### Low-power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the lowspeed clock (max 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In Lowpower run mode, the clock frequency and the number of enabled peripherals are both limited.

Low-power sleep mode

This mode is achieved by entering Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In Low-power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the Run mode with the regulator on.

#### Stop mode with RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSE crystal and HSI RC oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The device can be woken up from Stop mode by any of the EXTI line, in  $3.5 \,\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on), it can be the RTC alarm/tamper/timestamp/wakeup events, the USART/I2C/LPUART/LPTIMER wakeup events.

### 3.8 Memories

The STM32L071xx devices have the following features:

- 20 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 64, 128 or 192 Kbytes of embedded Flash program memory

- 6 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 8 Kbytes of system memory

Flash program and data EEPROM are divided into two banks. This allows writing in one bank while running code or reading data from the other bank.

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the non-volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

# 3.9 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1(PA4, PA5, PA6, PA7) or SPI2 (PB12, PB13, PB14, PB15), I2C1 (PB6, PB7) or I2C2 (PB10, PB11), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

|        | Pin number              |        |        |         |         |         | -       |                                       |          |               |      |                                                                     |                                           |

|--------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|---------------|------|---------------------------------------------------------------------|-------------------------------------------|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                 | Additional functions                      |

| -      | -                       | -      | 11     | -       | -       | 18      | K2      | PC3                                   | I/O      | FT            | -    | LPTIM1_ETR,<br>SPI2_MOSI/I2S2_SD                                    | ADC_IN13                                  |

| -      | 4                       | 8      | 12     | F1      | -       | 19      | J1      | VSSA                                  | S        |               | -    | -                                                                   | -                                         |

| -      | -                       | -      | -      | -       | -       | 20      | K1      | VREF-                                 | S        |               | -    | -                                                                   | -                                         |

| -      | -                       | I      | -      | G1      | E6      | 21      | L1      | VREF+                                 | S        |               | -    | -                                                                   | -                                         |

| 5      | 5                       | 9      | 13     | H1      | F7      | 22      | M1      | VDDA                                  | S        |               | -    | -                                                                   | -                                         |

| 6      | 6                       | 10     | 14     | G2      | E5      | 23      | L2      | PA0                                   | I/O      | ТТа           | -    | TIM2_CH1,<br>USART2_CTS,<br>TIM2_ETR,<br>USART4_TX,<br>COMP1_OUT    | COMP1_INM,<br>ADC_IN0,<br>RTC_TAMP2/WKUP1 |

| 7      | 7                       | 11     | 15     | H2      | E4      | 24      | M2      | PA1                                   | I/O      | FT            | -    | EVENTOUT,<br>TIM2_CH2,<br>USART2_RTS_DE,<br>TIM21_ETR,<br>USART4_RX | COMP1_INP,<br>ADC_IN1                     |

| 8      | 8                       | 12     | 16     | F3      | F6      | 25      | K3      | PA2                                   | I/O      | FT            | -    | TIM21_CH1,<br>TIM2_CH3,<br>USART2_TX,<br>LPUART1_TX,<br>COMP2_OUT   | COMP2_INM,<br>ADC_IN2                     |

| 9      | 9                       | 13     | 17     | G3      | G7      | 26      | L3      | PA3                                   | I/O      | FT            | -    | TIM21_CH2,<br>TIM2_CH4,<br>USART2_RX,<br>LPUART1_RX                 | COMP2_INP,<br>ADC_IN3                     |

| -      | -                       | I      | 18     | C2      | -       | 27      | D3      | VSS                                   | s        | -             | -    | -                                                                   | -                                         |

| -      | -                       | I      | 19     | D2      | -       | 28      | H3      | VDD                                   | S        | -             | -    | -                                                                   | -                                         |

| 10     | 10                      | 14     | 20     | H3      | F5      | 29      | М3      | PA4                                   | I/O      | тс            | -    | SPI1_NSS,<br>USART2_CK,<br>TIM22_ETR                                | COMP1_INM,<br>COMP2_INM,<br>ADC_IN4       |

| 11     | 11                      | 15     | 21     | F4      | G6      | 30      | K4      | PA5                                   | I/O      | тс            | -    | SPI1_SCK, TIM2_ETR,<br>TIM2_CH1                                     | COMP1_INM,<br>COMP2_INM,<br>ADC_IN5       |

| Pin number |                         |        |        |         |         |         |         |                                       |          |               |      |                                                                                 |                      |

|------------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|---------------|------|---------------------------------------------------------------------------------|----------------------|

| LQFP32     | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                             | Additional functions |

| 12         | 12                      | 16     | 22     | G4      | G5      | 31      | L4      | PA6                                   | I/O      | FT            | _    | SPI1_MISO,<br>TIM3_CH1,<br>LPUART1_CTS,<br>TIM22_CH1,<br>EVENTOUT,<br>COMP1_OUT | ADC_IN6              |

| 13         | 13                      | 17     | 23     | H4      | F4      | 32      | M4      | PA7                                   | I/O      | FT            | -    | SPI1_MOSI,<br>TIM3_CH2,<br>TIM22_CH2,<br>EVENTOUT,<br>COMP2_OUT                 | ADC_IN7              |

| -          | -                       | -      | 24     | H5      | -       | 33      | K5      | PC4                                   | I/O      | FT            | -    | EVENTOUT,<br>LPUART1_TX                                                         | ADC_IN14             |

| -          | -                       | -      | 25     | H6      | -       | 34      | L5      | PC5                                   | I/O      | FT            | -    | LPUART1_RX                                                                      | ADC_IN15             |

| 14         | 14                      | 18     | 26     | F5      | G4      | 35      | M5      | PB0                                   | I/O      | FT            | -    | EVENTOUT, TIM3_CH3                                                              | ADC_IN8,<br>VREF_OUT |

| 15         | 15                      | 19     | 27     | G5      | D3      | 36      | M6      | PB1                                   | I/O      | FT            | -    | TIM3_CH4,<br>LPUART1_RTS_DE                                                     | ADC_IN9,<br>VREF_OUT |

| -          | -                       | 20     | 28     | G6      | E3      | 37      | L6      | PB2                                   | I/O      | FT            | -    | LPTIM1_OUT,<br>I2C3_SMBA                                                        | -                    |

| -          | -                       | I      | -      | -       | -       | 38      | M7      | PE7                                   | I/O      | FT            | I    | USART5_CK/USART5_<br>RTS_DE                                                     | -                    |

| -          | -                       | -      | -      | -       | -       | 39      | L7      | PE8                                   | I/O      | FT            | -    | USART4_TX                                                                       | -                    |

| -          | -                       | -      | -      | -       | -       | 40      | M8      | PE9                                   | I/O      | FT            | -    | TIM2_CH1, TIM2_ETR,<br>USART4_RX                                                | -                    |

| -          | -                       | -      | -      | -       | -       | 41      | L8      | PE10                                  | I/O      | FT            | -    | TIM2_CH2,<br>USART5_TX                                                          | -                    |

| -          | -                       | -      | -      | -       | -       | 42      | М9      | PE11                                  | I/O      | FT            | -    | TIM2_CH3,<br>USART5_RX                                                          | -                    |

| -          | -                       | -      | -      | -       | -       | 43      | L9      | PE12                                  | I/O      | FT            | -    | TIM2_CH4, SPI1_NSS                                                              | -                    |

| -          | -                       | -      | -      | -       | -       | 44      | M10     | PE13                                  | I/O      | FT            | -    | SPI1_SCK                                                                        | -                    |

| -          | -                       | -      | -      | -       | -       | 45      | M11     | PE14                                  | I/O      | FT            | -    | SPI1_MISO                                                                       | -                    |

| -          | -                       | -      | -      | -       | -       | 46      | M12     | PE15                                  | I/O      | FT            | -    | SPI1_MOSI                                                                       | -                    |

Table 15. STM32L071xxx pin definition (continued)

|        |                         |        | Pin n  | umb     | er      |         |         |                                       |          |                                   |   |                                                      |                           |  |

|--------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|-----------------------------------|---|------------------------------------------------------|---------------------------|--|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | Pin type<br>I/O structure<br>Note |   | Alternate functions                                  | Additional functions      |  |

| 30     | 29                      | 43     | 59     | C3      | C3      | 93      | B4      | PB7                                   | I/O      | FTf                               | - | USART1_RX,<br>I2C1_SDA,<br>LPTIM1_IN2,<br>USART4_CTS | COMP2_INP,<br>VREF_PVD_IN |  |

| 31     | 30                      | 44     | 60     | B4      | A5      | 94      | A4      | BOOT0                                 | Ι        |                                   | - | -                                                    | -                         |  |

| -      | -                       | 45     | 61     | B3      | B5      | 95      | A3      | PB8                                   | I/O      | FTf                               | - | I2C1_SCL                                             | -                         |  |

| -      | -                       | 46     | 62     | A3      | A6      | 96      | В3      | PB9                                   | I/O      | FTf                               | - | EVENTOUT,<br>I2C1_SDA,<br>SPI2_NSS/I2S2_WS           | -                         |  |

| -      | -                       | -      | -      | -       | -       | 97      | C3      | PE0                                   | I/O      | FT                                | - | EVENTOUT                                             | -                         |  |

| -      | -                       | -      | -      | -       | -       | 98      | A2      | PE1                                   | I/O      | FT                                | I | EVENTOUT                                             | -                         |  |

| 32     | 31                      | 47     | 63     | D4      | -       | 99      | D3      | VSS                                   | S        |                                   | - | -                                                    | -                         |  |

| -      | 32                      | 48     | 64     | E4      | A7      | 100     | C4      | VDD                                   | S        |                                   | - | -                                                    | -                         |  |

| Table 15. STM32L071xxx | pin definition ( | continued) |

|------------------------|------------------|------------|

|------------------------|------------------|------------|

1. UFQFPN32 pinout differs from other STM32 devices except STM32L07xxx and STM32L8xxx.

### 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in *Table 25*.

| Symbol                          | Parameter                      | Conditions                                          | Min  | Тур                                    | Мах      | Unit |  |

|---------------------------------|--------------------------------|-----------------------------------------------------|------|----------------------------------------|----------|------|--|

|                                 |                                | BOR detector enabled                                | 0    | -                                      | $\infty$ |      |  |

| <b>↓</b> (1)                    | V <sub>DD</sub> rise time rate | BOR detector disabled                               | 0    | -                                      | 1000     |      |  |

| t <sub>VDD</sub> <sup>(1)</sup> |                                | 20                                                  | -    | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | µs/V     |      |  |

|                                 | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0    | -                                      | 1000     |      |  |

| <b>T</b> (1)                    | Deast temperization            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2                                      | 3.3      |      |  |

| RSTTEMPO <sup>(1)</sup>         | Reset temporization            | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7                                    | 1.6      | ms   |  |

|                                 | Power on/power down reset      | Falling edge                                        | 1    | 1.5                                    | 1.65     |      |  |

| V <sub>POR/PDR</sub>            | threshold                      | Rising edge                                         | 1.3  | 1.5                                    | 1.65     |      |  |

|                                 |                                | Falling edge                                        | 1.67 | 1.7                                    | 1.74     |      |  |

| V <sub>BOR0</sub>               | Brown-out reset threshold 0    | Rising edge                                         | 1.69 | 1.76                                   | 1.8      |      |  |

|                                 |                                | Falling edge                                        | 1.87 | 1.93                                   | 1.97     |      |  |

| V <sub>BOR1</sub>               | Brown-out reset threshold 1    | Rising edge                                         | 1.96 | 2.03                                   | 2.07     |      |  |

| V <sub>BOR2</sub>               |                                | Falling edge                                        | 2.22 | 2.30                                   | 2.35     |      |  |

|                                 | Brown-out reset threshold 2    | Rising edge                                         | 2.31 | 2.41                                   | 2.44     |      |  |

| V                               |                                | Falling edge                                        | 2.45 | 2.55                                   | 2.6      | 2.6  |  |

| V <sub>BOR3</sub>               | Brown-out reset threshold 3    | Rising edge                                         |      | 2.66                                   | 2.7      |      |  |

|                                 |                                | Falling edge 2.6                                    |      | 2.8                                    | 2.85     |      |  |

| V <sub>BOR4</sub>               | Brown-out reset threshold 4    | Rising edge                                         | 2.78 | 2.9                                    | 2.95     | .,   |  |

|                                 | Programmable voltage detector  | Falling edge                                        | 1.8  | 1.85                                   | 1.88     | V    |  |

| V <sub>PVD0</sub>               | threshold 0                    | Rising edge                                         | 1.88 | 1.94                                   | 1.99     |      |  |

|                                 |                                | Falling edge                                        | 1.98 | 2.04                                   | 2.09     |      |  |

| V <sub>PVD1</sub>               | PVD threshold 1                | Rising edge                                         | 2.08 | 2.14                                   | 2.18     |      |  |

|                                 |                                | Falling edge                                        | 2.20 | 2.24                                   | 2.28     |      |  |

| V <sub>PVD2</sub>               | PVD threshold 2                | Rising edge                                         | 2.28 | 2.34                                   | 2.38     |      |  |

|                                 |                                | Falling edge                                        | 2.39 | 2.44                                   | 2.48     |      |  |

| V <sub>PVD3</sub>               | PVD threshold 3                | Rising edge                                         | 2.47 | 2.54                                   | 2.58     | -    |  |

|                                 |                                | Falling edge                                        | 2.57 | 2.64                                   | 2.69     |      |  |

| V <sub>PVD4</sub>               | PVD threshold 4                | Rising edge                                         | 2.68 | 2.74                                   | 2.79     |      |  |

|                                 |                                | Falling edge                                        | 2.77 | 2.83                                   | 2.88     |      |  |

| V <sub>PVD5</sub>               | PVD threshold 5                | Rising edge                                         | 2.87 | 2.94                                   | 2.99     |      |  |

#### Table 26. Embedded reset and power control block characteristics

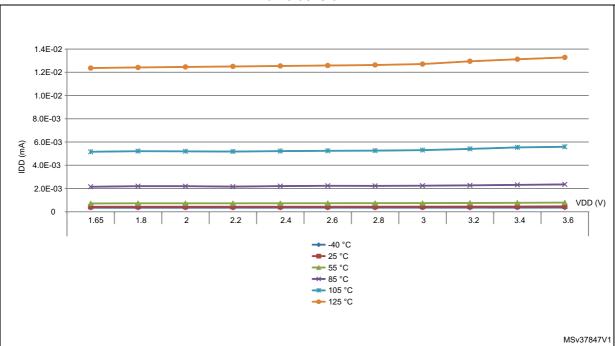

Figure 20.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/85/105/125 °C, Stop mode with RTC disabled, all clocks off

| Symbol          | Parameter                 | Conditi                                 | Тур                                        | Max <sup>(1)</sup> | Unit |             |

|-----------------|---------------------------|-----------------------------------------|--------------------------------------------|--------------------|------|-------------|

|                 |                           |                                         | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 0,855              | 1,70 |             |

|                 |                           |                                         | T <sub>A</sub> = 55 °C                     | -                  | 2,90 |             |

|                 |                           | Independent watchdog<br>and LSI enabled | T <sub>A</sub> = 85 °C                     | -                  | 3,30 |             |

|                 |                           |                                         | T <sub>A</sub> = 105 °C                    | -                  | 4,10 | - μA<br>- μ |

| I <sub>DD</sub> | Supply current in Standby |                                         | T <sub>A</sub> = 125 °C                    | -                  | 8,50 |             |

| (Standby)       | mode                      |                                         | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 0,29               | 0,60 |             |

|                 |                           |                                         | T <sub>A</sub> = 55 °C                     | 0,32               | 1,20 |             |

|                 |                           | Independent watchdog<br>and LSI off     | T <sub>A</sub> = 85 °C                     | 0,5                | 2,30 |             |

|                 |                           |                                         | T <sub>A</sub> = 105 °C                    | 0,94               | 3,00 |             |

|                 |                           |                                         | T <sub>A</sub> = 125 °C                    | 2,6                | 7,00 |             |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified

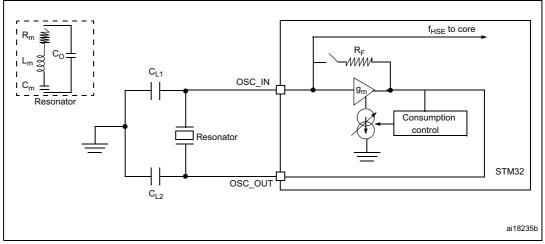

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 25 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 44*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                      | Parameter                                 | Conditions             | Min | Тур | Мах | Unit     |  |

|-----------------------------|-------------------------------------------|------------------------|-----|-----|-----|----------|--|

| f <sub>OSC_IN</sub>         | Oscillator frequency                      | -                      | 1   |     | 25  | MHz      |  |

| R <sub>F</sub>              | Feedback resistor                         | -                      | -   | 200 | -   | kΩ       |  |

| G <sub>m</sub>              | Maximum critical crystal transconductance | Startup                | -   | -   | 700 | μΑ<br>/V |  |

| t <sub>SU(HSE)</sub><br>(2) | Startup time                              | $V_{DD}$ is stabilized | -   | 2   | -   | ms       |  |

Table 44. HSE oscillator characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Guaranteed by characterization results. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 23*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

| Symbol                                | Parameter                          | Condition                                    | Тур  | Мах                                                 | Unit |

|---------------------------------------|------------------------------------|----------------------------------------------|------|-----------------------------------------------------|------|

|                                       |                                    | MSI range 0                                  | 0.75 | -                                                   |      |

|                                       |                                    | MSI range 1                                  | 1    | -                                                   |      |

|                                       |                                    | MSI range 2                                  | 1.5  | -                                                   |      |

| I <sub>DD(MSI)</sub> <sup>(2)</sup>   | MSI oscillator power consumption   | MSI range 3                                  | 2.5  | -                                                   | μA   |

|                                       |                                    | MSI range 4                                  | 4.5  | -                                                   |      |

|                                       |                                    | MSI range 5                                  | 8    | -                                                   |      |

|                                       |                                    | MSI range 6                                  | 15   | -                                                   |      |

| t <sub>SU(MSI)</sub>                  |                                    | MSI range 0                                  | 30   | -                                                   |      |

|                                       |                                    | MSI range 1                                  | 20   | -                                                   |      |

|                                       |                                    | MSI range 2                                  | 15   | -                                                   |      |

|                                       |                                    | MSI range 3                                  | 10   | -                                                   |      |

|                                       | MSI oscillator startup time        | MSI range 4                                  | 6    | 6     -       5     -       3.5     -       5     - | μs   |

|                                       |                                    | MSI range 5                                  | 5    |                                                     |      |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2     | 3.5  |                                                     |      |

|                                       |                                    | MSI range 6,<br>Voltage range 3              | 5    |                                                     |      |

|                                       |                                    | MSI range 0                                  | -    | 40                                                  | -    |

|                                       |                                    | MSI range 1                                  | -    | 20                                                  |      |

|                                       |                                    | MSI range 2                                  | -    | 10                                                  |      |

|                                       |                                    | MSI range 3                                  | -    | 4                                                   |      |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> | MSI oscillator stabilization time  | MSI range 4 -                                | 2.5  | μs                                                  |      |

| •STAB(MSI)                            |                                    | MSI range 5                                  | -    | 2                                                   | μο   |

|                                       |                                    | MSI range 6,<br>Voltage range 1 - 2<br>and 2 |      | 2                                                   |      |

|                                       |                                    | MSI range 3,<br>Voltage range 3              | -    | 3                                                   |      |

| former                                | MSI oscillator frequency overshoot | Any range to range 5                         | -    | 4                                                   | MHz  |

| f <sub>OVER(MSI)</sub>                |                                    | Any range to range 6                         | -    | 6                                                   |      |

Table 48. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

| Symbol          | Parameter                                                                      | Conditions                                      | Min | Тур | Max <sup>(1)</sup> | Unit |

|-----------------|--------------------------------------------------------------------------------|-------------------------------------------------|-----|-----|--------------------|------|

|                 | Average current during<br>the whole programming /<br>erase operation           |                                                 | -   | 500 | 700                | μA   |

| I <sub>DD</sub> | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -   | 1.5 | 2.5                | mA   |

Table 51. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

| Symbol                          | Parameter                                                                      | Conditions                       | Value              | Unit    |

|---------------------------------|--------------------------------------------------------------------------------|----------------------------------|--------------------|---------|

| Symbol                          | Parameter                                                                      | Conditions                       | Min <sup>(1)</sup> | Unit    |

|                                 | Cycling (erase / write)<br>Program memory                                      | T₄ = -40°C to 105 °C             | 10                 |         |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>EEPROM data memory                                  |                                  | 100                | kcycles |

| INCYC <sup>®</sup>              | Cycling (erase / write)<br>Program memory                                      | T <sub>A</sub> = -40°C to 125 °C | 0.2                | REYCIES |

|                                 | Cycling (erase / write)<br>EEPROM data memory                                  | TA = -40 C to 125 C              | 2                  |         |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C  | -Т <sub>вет</sub> = +85 °С       | 30                 |         |

|                                 | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$ | TRET - 105 C                     | 30                 |         |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C | -T <sub>RFT</sub> = +105 °C      |                    |         |

| <sup>I</sup> RET <sup>1</sup>   | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 105 \degree C$ | TRET - FIUS C                    | 10                 | years   |

|                                 | Data retention (program memory) after<br>200 cycles at T <sub>A</sub> = 125 °C | -T <sub>RET</sub> = +125 °C      | 10                 |         |

|                                 | Data retention (EEPROM data memory) after 2 kcycles at $T_A$ = 125 °C          | RET - TIZS C                     |                    |         |

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

## 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

| Symbol                                       | Parameter                            | Conditions                | Min     | Тур   | Max              | Unit |

|----------------------------------------------|--------------------------------------|---------------------------|---------|-------|------------------|------|

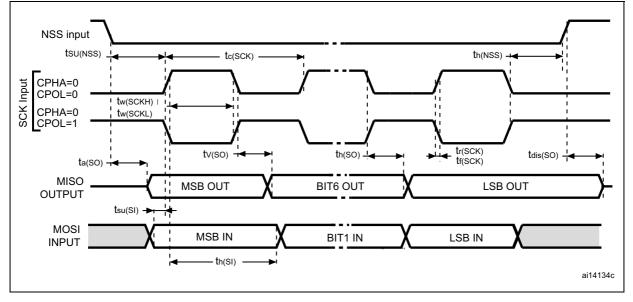

| f <sub>SCK</sub>                             | SDI alook froguonov                  | Master mode               |         |       | 2                | MHz  |

| 1/t <sub>c(SCK)</sub>                        | SPI clock frequency                  | Slave mode                | -       | -     | 2 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | - Slave mode              |         | 50    | 70               | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2 | 4*Tpclk | -     | -                |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2 | 2*Tpclk | -     | -                |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode               | Tpclk-2 | Tpclk | Tpclk+2          |      |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode               | 1.5     | -     | -                |      |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                | 6       | -     | -                |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode               | 13.5    | -     | -                |      |

| t <sub>h(SI)</sub>                           | Data input noid time                 | Slave mode                | 16      | -     | -                | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                | 30      | -     | 70               |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                | 40      | -     | 80               |      |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode                | -       | 30    | 70               |      |

| t <sub>v(MO)</sub>                           |                                      | Master mode               | -       | 7     | 9                |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                | 25      | -     | -                |      |

| t <sub>h(MO)</sub>                           | Data output hold time                | Master mode               | 8       | -     | -                |      |

| Table 74. SPI characteristics in | voltage Range 3 <sup>(1)</sup> |

|----------------------------------|--------------------------------|

|----------------------------------|--------------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

Figure 34. SPI timing diagram - slave mode and CPHA = 0

104/136

DocID027101 Rev 3

### **I2S** characteristics

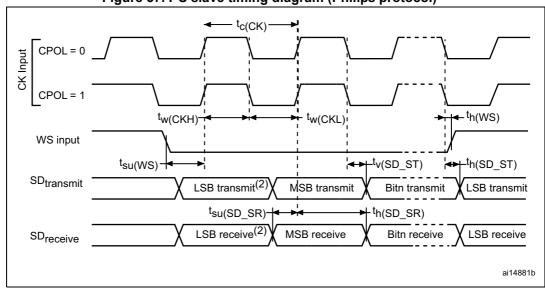

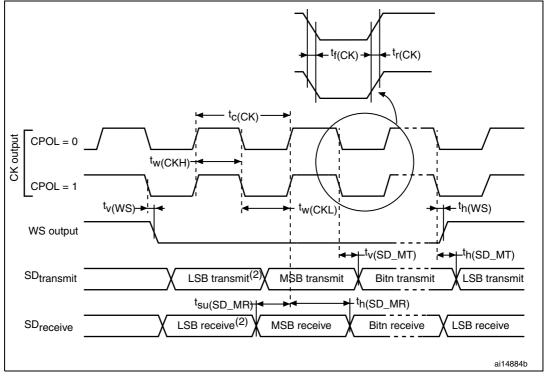

| Symbol                 | Parameter                      | Conditions                             | Min      | Max                   | Unit  |

|------------------------|--------------------------------|----------------------------------------|----------|-----------------------|-------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                      | 256 x 8K | 256xFs <sup>(2)</sup> | MHz   |

| 4                      | 125 alook froguopov            | Master data: 32 bits                   | -        | 64xFs                 | MHz   |

| f <sub>CK</sub>        | I2S clock frequency            | Slave data: 32 bits                    | -        | 64xFs                 | IVITZ |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                         | 30       | 70                    | %     |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                            | -        | 15                    |       |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                            | 11       | -                     |       |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode                             | 6        | -                     |       |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode                             | 2        | -                     |       |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                        | 0        | -                     |       |

| t <sub>su(SD_SR)</sub> | Data input setup time          | Slave receiver                         | 6.5      | -                     | ns    |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                        | 18       | -                     | 115   |

| t <sub>h(SD_SR)</sub>  | Data Input noid time           | Slave receiver                         | 15.5     | -                     |       |

| t <sub>v(SD_ST)</sub>  | Data output valid time         | Slave transmitter (after enable edge)  | -        | 77                    |       |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge) | -        | 8                     |       |

| t <sub>h(SD_ST)</sub>  | Data output hold time          | Slave transmitter (after enable edge)  | 18       | -                     |       |

| t <sub>h(SD_MT)</sub>  | Data output hold time          | Master transmitter (after enable edge) | 1.5      | -                     |       |

### Table 75. I2S characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. 256xFs maximum value is equal to the maximum clock frequency.

Note: Refer to the I2S section of the product reference manual for more details about the sampling frequency (Fs),  $f_{MCK}$ ,  $f_{CK}$  and  $D_{CK}$  values. These values reflect only the digital peripheral behavior, source clock precision might slightly change them. DCK depends mainly on the ODD bit value, digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max of (I2SDIV+ODD)/(2\*I2SDIV+ODD). Fs max is supported for each mode/condition.

Figure 37. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels:  $0.3 \times V_{DD}$  and  $0.7 \times V_{DD}$ .

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

### Figure 38. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| Cumhal |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol | Min    | Тур         | Мах    | Min    | Min Typ               |        |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| D3     | -      | 12.000      | -      | -      | 0.4724                | -      |

| Е      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| E3     | -      | 12.000      | -      | -      | 0.4724                | -      |

| е      | -      | 0.500       | -      | -      | 0.0197                | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |

| L1     | -      | 1.000       | -      | -      | 0.0394                | -      |

| k      | 0.0°   | 3.5°        | 7.0°   | 0.0°   | 3.5°                  | 7.0°   |

| CCC    | -      | -           | 0.080  | -      | -                     | 0.0031 |

| Table 76. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

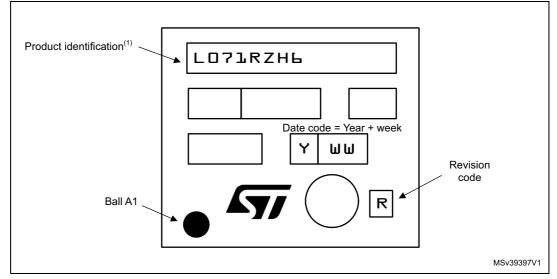

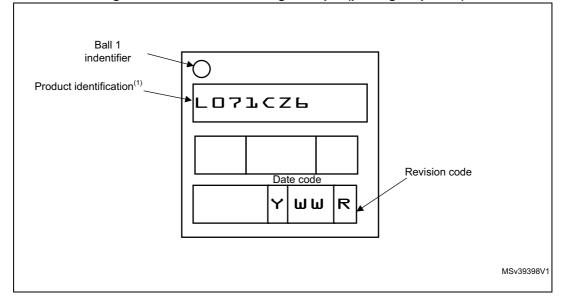

### **Device marking for TFBGA64**

The following figure gives an example of topside marking versus ball A 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Dimension      | Recommended values                             |  |  |  |

|----------------|------------------------------------------------|--|--|--|

| Pitch          | 0.4                                            |  |  |  |

| Dpad           | 260 μm max. (circular)                         |  |  |  |

|                | 220 µm recommended                             |  |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)          |  |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed. |  |  |  |

Table 83. WLCSP49 recommended PCB design rules (0.4 mm pitch)

#### **Device marking for WLCSP49**

The following figure gives an example of topside marking versus ball A 1 position identifier location.

Figure 52. WLCSP49 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 7.9 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                       | Value | Unit |

|---------------|---------------------------------------------------------------------------------|-------|------|

|               | Thermal resistance junction-ambient<br>UFQFPN32 - 5 x 5 mm / 0.5 mm pitch       | 36    |      |

|               | Thermal resistance junction-ambient<br>LQFP32 - 7 x 7 mm / 0.8 mm pitch         | 60    |      |

|               | Thermal resistance junction-ambient<br>LQFP48 - 7 x 7 mm / 0.5 mm pitch         | 54    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>WLCSP49 - 0.4 mm pitch                   | 48    | °C/W |

| JA            | <b>Thermal resistance junction-ambient</b><br>TFBGA64 - 5 x 5 mm / 0.5 mm pitch | 64    | 0,11 |

|               | Thermal resistance junction-ambient<br>LQFP64 - 10 x 10 mm / 0.5 mm pitch       | 46    |      |

|               | Thermal resistance junction-ambient<br>LQFP100 - 14 x 14 mm / 0.5 mm pitch      | 41    |      |

|               | Thermal resistance junction-ambient<br>UFBGA100 - 7 x 7 mm / 0.5 mm pitch       | 57    |      |

| Table 87. | Thermal | characteristics |

|-----------|---------|-----------------|

|           |         |                 |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID027101 Rev 3