Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 192KB (192K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 6K x 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l071rzt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

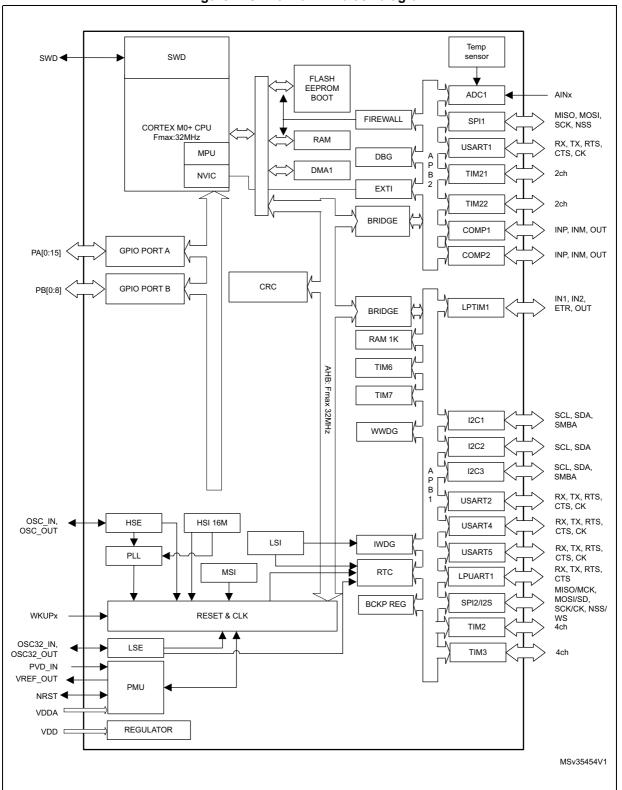

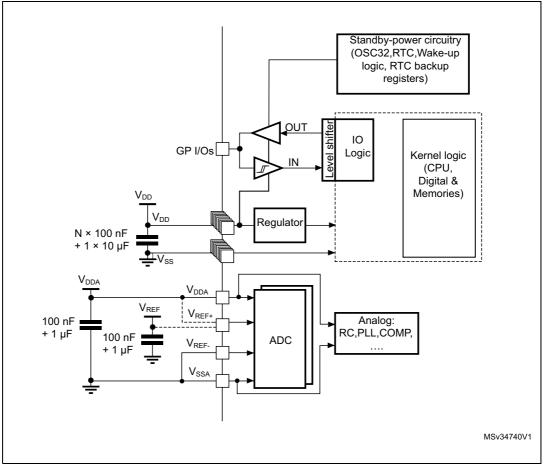

Figure 1. STM32L071xx block diagram

DocID027101 Rev 3

#### • Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USART/I2C/LPUART/LPTIMER wakeup events.

#### Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE crystal and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

#### Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

| One setting new or our plu                     | Functionalities depending on the operating power supply range |                                  |                            |  |  |  |

|------------------------------------------------|---------------------------------------------------------------|----------------------------------|----------------------------|--|--|--|

| Operating power supply<br>range                | ADC operation                                                 | Dynamic voltage<br>scaling range | I/O operation              |  |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | ADC only,<br>conversion time up<br>to 570 ksps                | Range 2 or<br>range 3            | Degraded speed performance |  |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time up<br>to 1.14 Msps               | Range 1, range 2 or<br>range 3   | Degraded speed performance |  |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | Conversion time up<br>to 1.14 Msps                            | Range1, range 2 or<br>range 3    | Degraded speed performance |  |  |  |

#### Table 3. Functionalities depending on the operating power supply range

|                               |            |         | Low-         | Low-           |                  | Stop                 | Standby |                      |

|-------------------------------|------------|---------|--------------|----------------|------------------|----------------------|---------|----------------------|

| IPs                           | Run/Active | Sleep   | power<br>run | power<br>sleep |                  | Wakeup<br>capability |         | Wakeup<br>capability |

| High Speed<br>External (HSE)  | 0          | 0       | 0            | 0              |                  |                      |         |                      |

| Low Speed Internal<br>(LSI)   | 0          | 0       | 0            | 0              | 0                |                      | 0       |                      |

| Low Speed<br>External (LSE)   | 0          | 0       | 0            | 0              | 0                |                      | 0       |                      |

| Multi-Speed<br>Internal (MSI) | 0          | 0       | Y            | Y              |                  |                      |         |                      |

| Inter-Connect<br>Controller   | Y          | Y       | Y            | Y              | Y                |                      |         |                      |

| RTC                           | 0          | 0       | 0            | 0              | 0                | 0                    | 0       |                      |

| RTC Tamper                    | 0          | 0       | 0            | 0              | 0                | 0                    | 0       | 0                    |

| Auto WakeUp<br>(AWU)          | 0          | 0       | 0            | 0              | 0                | 0                    | 0       | 0                    |

| USART                         | 0          | 0       | 0            | 0              | O <sup>(4)</sup> | 0                    |         |                      |

| LPUART                        | 0          | 0       | 0            | 0              | O <sup>(4)</sup> | 0                    |         |                      |

| SPI                           | 0          | 0       | 0            | 0              |                  |                      |         |                      |

| 12C                           | 0          | 0       | 0            | 0              | O <sup>(5)</sup> | 0                    |         |                      |

| ADC                           | 0          | 0       |              |                |                  |                      |         |                      |

| Temperature<br>sensor         | 0          | 0       | 0            | 0              | 0                |                      |         |                      |

| Comparators                   | 0          | 0       | 0            | 0              | 0                | 0                    |         |                      |

| 16-bit timers                 | 0          | 0       | 0            | 0              |                  |                      |         |                      |

| LPTIMER                       | 0          | 0       | 0            | 0              | 0                | 0                    |         |                      |

| IWDG                          | 0          | 0       | 0            | 0              | 0                | 0                    | 0       | 0                    |

| WWDG                          | 0          | 0       | 0            | 0              |                  |                      |         |                      |

| SysTick Timer                 | 0          | 0       | 0            | 0              |                  |                      |         |                      |

| GPIOs                         | 0          | 0       | 0            | 0              | 0                | 0                    |         | 2 pins               |

| Wakeup time to<br>Run mode    | 0 µs       | 0.36 µs | 3 µs         | 32 µs          |                  |                      |         | 50 µs                |

Table 5. Functionalities depending on the working mode (from Run/active down to standby) (continued)<sup>(1)(2)</sup>

internal reference voltage (V<sub>REFINT</sub>) in Stop mode. The device remains in reset mode when V<sub>DD</sub> is below a specified threshold, V<sub>POR/PDR</sub> or V<sub>BOR</sub>, without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

#### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

### 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

#### Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

• Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

• System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 1-25 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLLMultispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

#### Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the real-time clock:

#### 3.15.2 Universal synchronous/asynchronous receiver transmitter (USART)

The four USART interfaces (USART1, USART2, USART4 and USART5) are able to communicate at speeds of up to 4 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 and USART2 also support SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability, auto baud rate feature and has a clock domain independent from the CPU clock, allowing to wake up the MCU from Stop mode using baudrates up to 42 Kbaud.

All USART interfaces can be served by the DMA controller.

Table 12 for the supported modes and features of USART interfaces.

| USART modes/features <sup>(1)</sup>         | USART1 and USART2 | USART4 and USART5 |

|---------------------------------------------|-------------------|-------------------|

| Hardware flow control for modem             | Х                 | Х                 |

| Continuous communication using DMA          | Х                 | Х                 |

| Multiprocessor communication                | Х                 | Х                 |

| Synchronous mode <sup>(2)</sup>             | Х                 | Х                 |

| Smartcard mode                              | Х                 | -                 |

| Single-wire half-duplex communication       | Х                 | Х                 |

| IrDA SIR ENDEC block                        | Х                 | -                 |

| LIN mode                                    | Х                 | -                 |

| Dual clock domain and wakeup from Stop mode | Х                 | -                 |

| Receiver timeout interrupt                  | Х                 | -                 |

| Modbus communication                        | Х                 | -                 |

| Auto baud rate detection (4 modes)          | Х                 | -                 |

| Driver Enable                               | Х                 | Х                 |

Table 12. USART implementation

1. X = supported.

2. This mode allows using the USART as an SPI master.

#### 3.15.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock. It can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

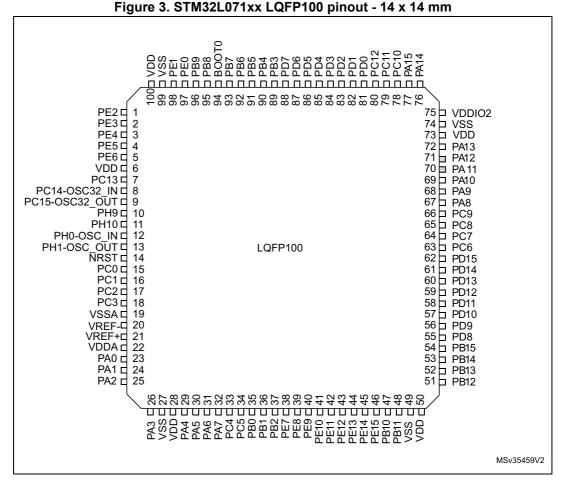

## 4 Pin descriptions

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

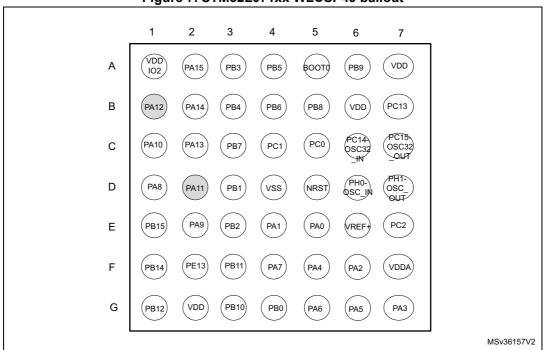

Figure 7. STM32L071xx WLCSP49 ballout

1. The above figure shows the package top view.

2. I/O supplied by VDDIO2.

|        |                         | I      | Pin n  | umb     | er      |         |         |                                       |          |               |      |                                                                           |                      |

|--------|-------------------------|--------|--------|---------|---------|---------|---------|---------------------------------------|----------|---------------|------|---------------------------------------------------------------------------|----------------------|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                       | Additional functions |

| -      | -                       | 21     | 29     | G7      | G3      | 47      | L10     | PB10                                  | I/O      | FT            | -    | TIM2_CH3,<br>LPUART1_TX,<br>SPI2_SCK, I2C2_SCL,<br>LPUART1_RX             | -                    |

| -      | -                       | 22     | 30     | H7      | F3      | 48      | L11     | PB11                                  | I/O      | FT            | -    | EVENTOUT,<br>TIM2_CH4,<br>LPUART1_RX,<br>I2C2_SDA,<br>LPUART1_TX          | -                    |

| 16     | 16                      | 23     | 31     | D6      | D4      | 49      | F12     | VSS                                   | S        |               | -    | -                                                                         | -                    |

| 17     | 17                      | 24     | 32     | E6      | G2      | 50      | G12     | VDD                                   | S        |               | -    | -                                                                         | -                    |

| -      | -                       | 25     | 33     | H8      | G1      | 51      | L12     | PB12                                  | I/O      | FT            | -    | SPI2_NSS/I2S2_WS,<br>LPUART1_RTS_DE,<br>I2C2_SMBA,<br>EVENTOUT            | -                    |

| -      | -                       | 26     | 34     | G8      | F2      | 52      | K12     | PB13                                  | I/O      | FTf           | -    | SPI2_SCK/I2S2_CK,<br>MCO, LPUART1_CTS,<br>I2C2_SCL, TIM21_CH1             | -                    |

| -      | -                       | 27     | 35     | F8      | F1      | 53      | K11     | PB14                                  | I/O      | FTf           | -    | SPI2_MISO/I2S2_MCK,<br>RTC_OUT,<br>LPUART1_RTS_DE,<br>I2C2_SDA, TIM21_CH2 | -                    |

| -      | -                       | 28     | 36     | F7      | E1      | 54      | K10     | PB15                                  | I/O      | FT            | -    | SPI2_MOSI/I2S2_SD,<br>RTC_REFIN                                           | -                    |

| -      | -                       | -      | -      | -       | -       | 55      | K9      | PD8                                   | I/O      | FT            | -    | LPUART1_TX                                                                | -                    |

| -      | -                       | -      | -      | -       | -       | 56      | K8      | PD9                                   | I/O      | FT            | -    | LPUART1_RX                                                                | -                    |

| -      | -                       | -      | -      | -       | -       | 57      | J12     | PD10                                  | I/O      | FT            | -    |                                                                           | -                    |

| -      | -                       | -      | -      | -       | -       | 58      | J11     | PD11                                  | I/O      | FT            | -    | LPUART1_CTS                                                               | -                    |

| -      | -                       | -      | -      | -       | -       | 59      | J10     | PD12                                  | I/O      | FT            | -    | LPUART1_RTS_DE                                                            | -                    |

| -      | -                       | -      | -      | -       | -       | 60      | H12     | PD13                                  | I/O      | FT            | -    |                                                                           | -                    |

| -      | -                       | -      | -      | -       | -       | 61      | H11     | PD14                                  | I/O      | FT            | -    |                                                                           | -                    |

| -      | -                       | -      | -      | -       | -       | 62      | H10     | PD15                                  | I/O      | FT            | -    |                                                                           | -                    |

| -      | -                       | -      | 37     | F6      | -       | 63      | E12     | PC6                                   | I/O      | FT            | -    | TIM22_CH1, TIM3_CH1                                                       | -                    |

| -      | -                       | -      | 38     | E7      | -       | 64      | E11     | PC7                                   | I/O      | FT            | -    | TIM22_CH2, TIM3_CH2                                                       | -                    |

| Table 15. STM32L071xxx pin definition (continued) |

|---------------------------------------------------|

|---------------------------------------------------|

## 6 Electrical characteristics

### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

### 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.6 V (for the 1.65 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

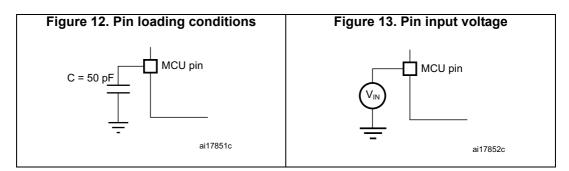

#### 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 12*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 13*.

#### Power supply scheme 6.1.6

Figure 14. Power supply scheme

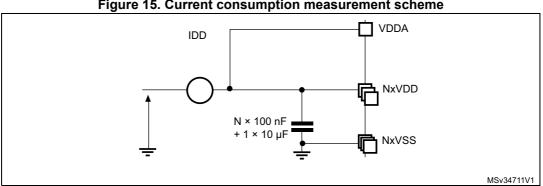

#### 6.1.7 **Current consumption measurement**

## Figure 15. Current consumption measurement scheme

| Symbol                | Parameter                                                        | Conditio                                        | on                                    | f <sub>HCLK</sub><br>(MHz) | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------------|------------------------------------------------------------------|-------------------------------------------------|---------------------------------------|----------------------------|------|--------------------|------|

|                       |                                                                  |                                                 | Range3,                               | 1                          | 190  | 250                |      |

|                       |                                                                  |                                                 | Vcore=1.2 V                           | 2                          | 345  | 380                | μA   |

|                       |                                                                  |                                                 | VOS[1:0]=11                           | 4                          | 650  | 670                |      |

|                       |                                                                  | f <sub>HSE</sub> = f <sub>HCLK</sub> up to      | Range2,                               | 4                          | 0,8  | 0,86               |      |

|                       |                                                                  | 16MHz included,<br>$f_{HSE} = f_{HCLK}/2$ above | Vcore=1.5 V                           | 8                          | 1,55 | 1,7                | μA   |

| I <sub>DD</sub> (Run  | Supply current in Run<br>mode code executed<br>from Flash memory | 16 MHz (PLL ON) <sup>(2)</sup>                  | VOS[1:0]=10                           | 16                         | 2,95 | 3,1                |      |

|                       |                                                                  |                                                 | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 8                          | 1,9  | 2,1                |      |

|                       |                                                                  |                                                 |                                       | 16                         | 3,55 | 3,8                |      |

| from Flash<br>memory) |                                                                  |                                                 |                                       | 32                         | 6,65 | 7,2                |      |

| memory)               |                                                                  | MSI clock source                                | Range3,<br>Vcore=1.2 V                | 0,065                      | 39   | 130                |      |

|                       |                                                                  |                                                 |                                       | 0,524                      | 115  | 210                |      |

|                       |                                                                  |                                                 | VOS[1:0]=11                           | 4,2                        | 700  | 770                |      |

|                       |                                                                  | HSI clock source                                | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16                         | 2,9  | 3,2                |      |

|                       |                                                                  | (16MHz)                                         | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32                         | 7,15 | 7,4                | mA   |

# Table 29. Current consumption in Run mode, code with data processing running fromFlash memory

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

# Table 30. Current consumption in Run mode vs code type,code with data processing running from Flash memory

| Symbol                                           | Parameter                                             |                                                                                                                                                                          | Conditions                            |                             | f <sub>HCLK</sub> | Тур  | Unit |

|--------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|-------------------|------|------|

|                                                  |                                                       |                                                                                                                                                                          |                                       | Dhrystone                   |                   | 650  |      |

| I <sub>DD</sub> c<br>(Run F<br>from c<br>Flash e |                                                       |                                                                                                                                                                          |                                       | CoreMark                    |                   | 655  |      |

|                                                  |                                                       |                                                                                                                                                                          | Range 3,<br>V <sub>CORE</sub> =1.2 V, | Fibonacci                   | 4 MHz             | 485  | μA   |

|                                                  | Supply<br>current in<br>Run mode,<br>code<br>executed | ply<br>ent in<br>mode,<br>e<br>cuted<br>n Flash<br>nory<br>$f_{HSE} = f_{HCLK}$ up to<br>16 MHz included, $f_{HSE} = f_{HCLK}/2$ above 16<br>MHz (PLL on) <sup>(1)</sup> | VOS[1:0]=11                           | while(1)                    |                   | 385  |      |

|                                                  |                                                       |                                                                                                                                                                          |                                       | while(1), 1WS, prefetch off |                   | 375  |      |

|                                                  |                                                       |                                                                                                                                                                          | Range 1,<br>V <sub>CORE</sub> =1.8 V, | Dhrystone                   |                   | 6,65 |      |

| memory)                                          | memory                                                |                                                                                                                                                                          |                                       | CoreMark                    | 1                 | 6,9  | mA   |

|                                                  |                                                       |                                                                                                                                                                          |                                       | Fibonacci                   | 32 MHz            | 6,75 |      |

|                                                  |                                                       |                                                                                                                                                                          | VOS[1:0]=01                           | while(1)                    |                   | 5,8  |      |

|                                                  |                                                       |                                                                                                                                                                          |                                       | while(1), prefetch off      |                   | 5,5  |      |

1. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol          | Parameter                              | Condition                                                                                                                                        | -                                     | f <sub>HCLK</sub> (MHz) | Тур  | Max <sup>(1)</sup> | Unit    |

|-----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------|------|--------------------|---------|

|                 |                                        |                                                                                                                                                  | Range3,                               | 1                       | 43,5 | 110                |         |

|                 |                                        |                                                                                                                                                  | Vcore=1.2 V                           | 2                       | 72   | 140                | I       |

|                 |                                        |                                                                                                                                                  | VOS[1:0]=11                           | 4                       | 130  | 200                |         |

|                 |                                        | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                                                                                                       | Range2,                               | 4                       | 160  | 220                |         |

|                 |                                        | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above                                                                                | Vcore=1.5 V                           | 8                       | 305  | 380                |         |

|                 |                                        | 16 MHz (PLL ON) <sup>(2)</sup>                                                                                                                   | VOS[1:0]=10                           | 16                      | 590  | 690                |         |

|                 |                                        |                                                                                                                                                  | Range1,                               | 8                       | 370  | 460                |         |

|                 | Supply current in<br>Sleep mode, Flash |                                                                                                                                                  | Vcore=1.8 V                           | 16                      | 715  | 840                |         |

|                 | memory switched                        |                                                                                                                                                  | VOS[1:0]=01                           | 32                      | 1650 | 2000               |         |

|                 | OFF                                    |                                                                                                                                                  | Range3,                               | 0,065                   | 18   | 93                 |         |

|                 |                                        | MSI clock                                                                                                                                        | Vcore=1.2 V                           | 0,524                   | 31,5 | 110                |         |

|                 |                                        |                                                                                                                                                  | VOS[1:0]=11                           | 4,2                     | 140  | 230                |         |

|                 |                                        | HSI clock source<br>(16 MHz)                                                                                                                     | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16                      | 665  | 850                |         |

| I <sub>DD</sub> |                                        |                                                                                                                                                  | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32                      | 1750 | 2100               |         |

| (Sleep)         |                                        | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above<br>16 MHz (PLL ON) <sup>(2)</sup> | Range3,<br>Vcore=1.2 V<br>VOS[1:0]=11 | 1                       | 57,5 | 130                | μA<br>- |

|                 |                                        |                                                                                                                                                  |                                       | 2                       | 84   | 160                |         |

|                 |                                        |                                                                                                                                                  |                                       | 4                       | 150  | 220                |         |

|                 |                                        |                                                                                                                                                  | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 4                       | 170  | 240                |         |

|                 |                                        |                                                                                                                                                  |                                       | 8                       | 315  | 400                |         |

|                 |                                        |                                                                                                                                                  |                                       | 16                      | 605  | 710                |         |

|                 |                                        |                                                                                                                                                  | Range1,                               | 8                       | 380  | 470                |         |

|                 | Supply current in                      |                                                                                                                                                  | Vcore=1.8 V                           | 16                      | 730  | 860                |         |

|                 | Sleep mode, Flash<br>memory switched   |                                                                                                                                                  | VOS[1:0]=01                           | 32                      | 1650 | 2000               |         |

|                 | ON                                     |                                                                                                                                                  | Range3,                               | 0,065                   | 29,5 | 110                |         |

|                 |                                        | MSI clock                                                                                                                                        | Vcore=1.2 V                           | 0,524                   | 44,5 | 120                |         |

|                 |                                        |                                                                                                                                                  | VOS[1:0]=11                           | 4,2                     | 150  | 240                |         |

|                 |                                        | HSI clock source                                                                                                                                 | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16                      | 680  | 930                |         |

|                 |                                        | (16MHz)                                                                                                                                          | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32                      | 1750 | 2200               |         |

| Table 33. Current consumption in Sleep mode |

|---------------------------------------------|

|---------------------------------------------|

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol                     | Devinhevel                   | Typical consum         | ption, T <sub>A</sub> = 25 °C | Unit   |

|----------------------------|------------------------------|------------------------|-------------------------------|--------|

| Symbol                     | Peripheral                   | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V        | – Unit |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                    | 1.2                           |        |

| I <sub>REFINT</sub>        | -                            | -                      | 1.7                           |        |

| -                          | LSE Low drive <sup>(2)</sup> | 0.11                   | 0,13                          |        |

| -                          | LSI                          | 0.27                   | 0.31                          |        |

| -                          | IWDG                         | 0.2                    | 0.3                           |        |

| -                          | LPTIM1, Input 100 Hz         | 0.01                   | 0,01                          | μA     |

| -                          | LPTIM1, Input 1 MHz          | 11                     | 12                            |        |

| -                          | LPUART1                      | -                      | 0,5                           |        |

| -                          | RTC                          | 0.16                   | 0,3                           |        |

| Table 40. Peripheral current | consumption in | Stop and Standby | / mode <sup>(1)</sup> |

|------------------------------|----------------|------------------|-----------------------|

|                              |                |                  |                       |

1. LPTIM, LPUART peripherals can operate in Stop mode but not in Standby mode.

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

### 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

| Symbol               | Parameter Conditions              |                                                          | Тур | Max | Unit               |

|----------------------|-----------------------------------|----------------------------------------------------------|-----|-----|--------------------|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode            | f <sub>HCLK</sub> = 32 MHz                               | 7   | 8   |                    |

| twusleep             | Wakeup from Low-power sleep mode, | f <sub>HCLK</sub> = 262 kHz<br>Flash memory enabled      | 7   | 8   | Number<br>of clock |

| LP                   | f <sub>HCLK</sub> = 262 kHz       | f <sub>HCLK</sub> = 262 kHz<br>Flash memory switched OFF | 9   | 10  | cycles             |

| Table 41. | Low-power | mode | wakeup | timinas |

|-----------|-----------|------|--------|---------|

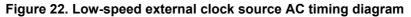

#### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 25*.

| Symbol                                     | Parameter Conditions Min Typ            |                                  | Max                | Unit   |                    |     |

|--------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|-----|

| f <sub>LSE_ext</sub>                       | User external clock source<br>frequency |                                  | 1                  | 32.768 | 1000               | kHz |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v   |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v   |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns  |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115 |

| C <sub>IN(LSE)</sub>                       | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF  |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                              | -                                | 45                 | -      | 55                 | %   |

| ١L                                         | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA  |

Table 43. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production

### 6.3.7 Internal clock source characteristics

The parameters given in *Table 46* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

#### High-speed internal 16 MHz (HSI16) RC oscillator

| Symbol                                | Parameter                                           | Conditions Mi                                                                        |                   | Тур                 | Max   | Unit |

|---------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------|-------------------|---------------------|-------|------|

| f <sub>HSI16</sub>                    | Frequency                                           | V <sub>DD</sub> = 3.0 V                                                              | -                 | 16                  | -     | MHz  |

| TRIM <sup>(1)(2)</sup>                | HSI16 user-                                         | Trimming code is not a multiple of 16                                                | -                 | $\pm0.4$            | 0.7   | %    |

| TRIM                                  | trimmed resolution                                  | Trimming code is a multiple of 16                                                    | -                 | -                   | ± 1.5 | %    |

|                                       |                                                     | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                                     | -1 <sup>(3)</sup> | -1 <sup>(3)</sup> - |       | %    |

|                                       |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = 0 to 55 °C                                                | -1.5              | -                   | 1.5   | %    |

| ACC                                   | Accuracy of the factory-calibrated HSI16 oscillator | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                                              |                   | -                   | 2     | %    |

| ACC <sub>HSI16</sub>                  |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 85 °C                                              |                   | -                   | 2     | %    |

|                                       |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                                             |                   | -                   | 2     | %    |

|                                       |                                                     | $V_{DDA} = 1.65 V \text{ to } 3.6 V$<br>$T_A = -40 \text{ to } 125 ^{\circ}\text{C}$ | -5.45             | -                   | 3.25  | %    |

| t <sub>SU(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>startup time                    | -                                                                                    | -                 | 3.7                 | 6     | μs   |

| I <sub>DD(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>power consumption               | -                                                                                    | -                 | 100                 | 140   | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

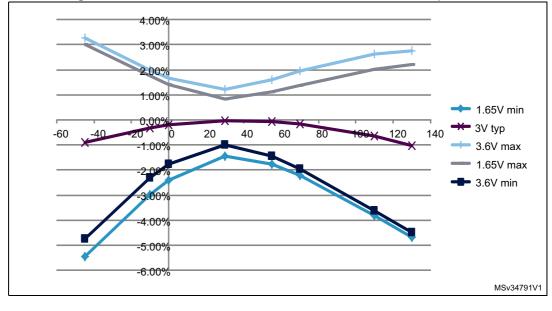

Figure 25. HSI16 minimum and maximum value versus temperature

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 28* and *Table 60*, respectively.

Unless otherwise specified, the parameters given in *Table 60* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 25*.

| OSPEEDRx[1:0]<br>bit value <sup>(1)</sup> | Symbol                  | Parameter                                                                              | Conditions                                                | Min | Max <sup>(2)</sup>                                                                                                                                                                          | Unit    |  |

|-------------------------------------------|-------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

|                                           | f                       | Maximum frequency <sup>(3)</sup>                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 400                                                                                                                                                                                         |         |  |

| 00                                        | f <sub>max(IO)out</sub> | Maximum nequency (*)                                                                   | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 100                                                                                                                                                                                         | KIIZ    |  |

| 00                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                                              | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 125                                                                                                                                                                                         | 200     |  |

|                                           | t <sub>r(IO)out</sub>   |                                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 320                                                                                                                                                                                         | 115     |  |

|                                           | f                       | Maximum frequency <sup>(3)</sup>                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 2                                                                                                                                                                                           | MНт     |  |

| 01                                        | f <sub>max(IO)out</sub> |                                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 400 kHz   100 kHz   125 ns   320 ms   30 ms   30 ms   30 ms   10 ms   10 ms   11 ms   10 ns   10 ns   30 ms   30 ms |         |  |

| 01                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                                              | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 30                                                                                                                                                                                          | 200     |  |

|                                           | t <sub>r(IO)out</sub>   |                                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 65                                                                                                                                                                                          | 115     |  |

|                                           | E                       | Maximum frequency <sup>(3)</sup>                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 10                                                                                                                                                                                          |         |  |

| 10                                        | F <sub>max(IO)out</sub> |                                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               |     |                                                                                                                                                                                             |         |  |

| 10                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                                              | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 13                                                                                                                                                                                          | <b></b> |  |

|                                           | t <sub>r(IO)out</sub>   |                                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 28                                                                                                                                                                                          | 115     |  |

|                                           | E                       | Maximum frequency <sup>(3)</sup> $C_L = 30 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6$ | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 35                                                                                                                                                                                          |         |  |

| 11                                        | F <sub>max(IO)out</sub> |                                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               |     | 10                                                                                                                                                                                          |         |  |

| 11                                        | t <sub>f(IO)out</sub>   | Output rise and fall time                                                              | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 6                                                                                                                                                                                           | 20      |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise and fall time                                                              | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 17                                                                                                                                                                                          | ns      |  |

|                                           | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                                       |                                                           | -   | 1                                                                                                                                                                                           | MHz     |  |

|                                           | t <sub>f(IO)out</sub>   | Output fall time                                                                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.5 V to 3.6 V  |     | 10                                                                                                                                                                                          | 20      |  |

| Fm+                                       | t <sub>r(IO)out</sub>   | Output rise time                                                                       |                                                           | -   | 30                                                                                                                                                                                          | ns      |  |

| configuration <sup>(4)</sup>              | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                                       |                                                           | -   | 350                                                                                                                                                                                         | KHz     |  |

|                                           | t <sub>f(IO)out</sub>   | Output fall time                                                                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 3.6 V |     | 15                                                                                                                                                                                          |         |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise time                                                                       |                                                           | -   | 60                                                                                                                                                                                          | 115     |  |

| -                                         | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller                  | -                                                         | 8   | -                                                                                                                                                                                           | ns      |  |

Table 60. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the line reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. The maximum frequency is defined in *Figure 28*.

4. When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the line reference manual for a detailed description of Fm+ I/O configuration.

DocID027101 Rev 3

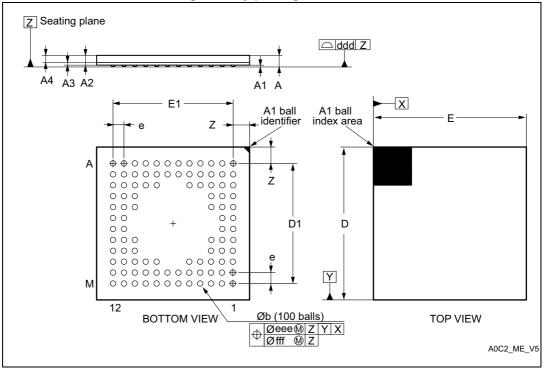

## 7.2 UFBGA100 package information

Figure 42. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

# Table 77. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package mechanical data

| Symbol |       | millimeters | llimeters inches <sup>(1)</sup> |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|---------------------------------|--------|-----------------------|--------|--|

| Symbol | Min.  | Тур.        | Max.                            | Min.   | Тур.                  | Max.   |  |

| А      | -     | -           | 0.600                           | -      | -                     | 0.0236 |  |

| A1     | -     | -           | 0.110                           | -      | -                     | 0.0043 |  |

| A2     | -     | 0.450       | -                               | -      | 0.0177                | -      |  |

| A3     | -     | 0.130       | -                               | -      | 0.0051                | 0.0094 |  |

| A4     | -     | 0.320       | -                               | -      | 0.0126                | -      |  |

| b      | 0.240 | 0.290       | 0.340                           | 0.0094 | 0.0114                | 0.0134 |  |

| D      | 6.850 | 7.000       | 7.150                           | 0.2697 | 0.2756                | 0.2815 |  |

| D1     | -     | 5.500       | -                               | -      | 0.2165                | -      |  |

| E      | 6.850 | 7.000       | 7.150                           | 0.2697 | 0.2756                | 0.2815 |  |

| E1     | -     | 5.500       | -                               | -      | 0.2165                | -      |  |

| е      | -     | 0.500       | -                               | -      | 0.0197                | -      |  |

| Z      | -     | 0.750       | -                               | -      | 0.0295                | -      |  |

| package mechanical data |       |             |       |        |        |        |  |

|-------------------------|-------|-------------|-------|--------|--------|--------|--|

| Symbol                  |       | millimeters |       |        |        |        |  |

| Symbol                  | Min   | Тур         | Мах   | Min    | Тур    | Max    |  |

| А                       | 0.525 | 0.555       | 0.585 | 0.0207 | 0.0219 | 0.0230 |  |

| A1                      | -     | 0.175       | -     | -      | 0.0069 | -      |  |

| A2                      | -     | 0.380       | -     | -      | 0.0150 | -      |  |

| A3 <sup>(2)</sup>       | -     | 0.025       | -     | -      | 0.0010 | -      |  |

| b <sup>(3)</sup>        | 0.220 | 0.250       | 0.280 | 0.0087 | 0.0098 | 0.0110 |  |

| D                       | 3.259 | 3.294       | 3.329 | 0.1283 | 0.1297 | 0.1311 |  |

| E                       | 3.223 | 3.258       | 3.293 | 0.1269 | 0.1283 | 0.1296 |  |

| е                       | -     | 0.400       | -     | -      | 0.0157 | -      |  |

| e1                      | -     | 2.400       | -     | -      | 0.0945 | -      |  |

| e2                      | -     | 2.400       | -     | -      | 0.0945 | -      |  |

| F                       | -     | 0.447       | -     | -      | 0.0176 | -      |  |

| G                       | -     | 0.429       | -     | -      | 0.0169 | -      |  |

| aaa                     | -     | -           | 0.100 | -      | -      | 0.0039 |  |

| bbb                     | -     | -           | 0.100 | -      | -      | 0.0039 |  |

| CCC                     | -     | -           | 0.100 | -      | -      | 0.0039 |  |

| ddd                     | -     | -           | 0.050 | -      | -      | 0.0020 |  |

| eee                     | -     | -           | 0.050 | -      | -      | 0.0020 |  |

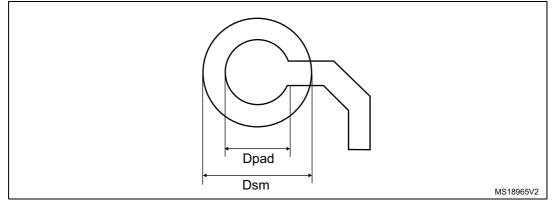

# Table 82. WLCSP49 - 49-pin, 3.294 x 3.258 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

# Figure 51. WLCSP49 - 49-pin, 3.294 x 3.258 mm, 0.4 mm pitch wafer level chip scale recommended footprint

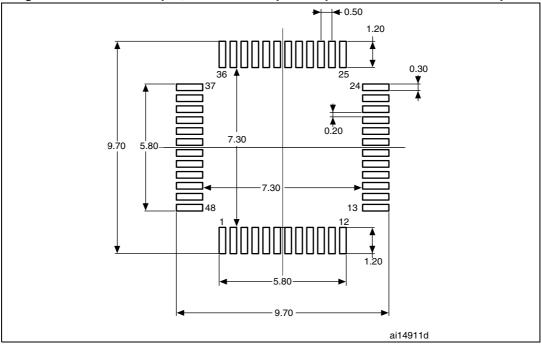

#### Figure 54. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

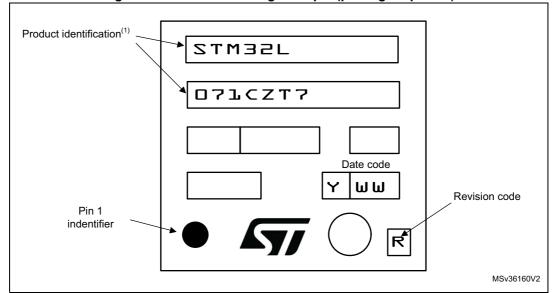

#### **Device marking for LQFP48**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Figure 55. LQFP48 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

DocID027101 Rev 3

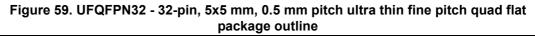

# 7.8 UFQFPN32 package information

<sup>1.</sup> Drawing is not to scale.