Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27k40-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

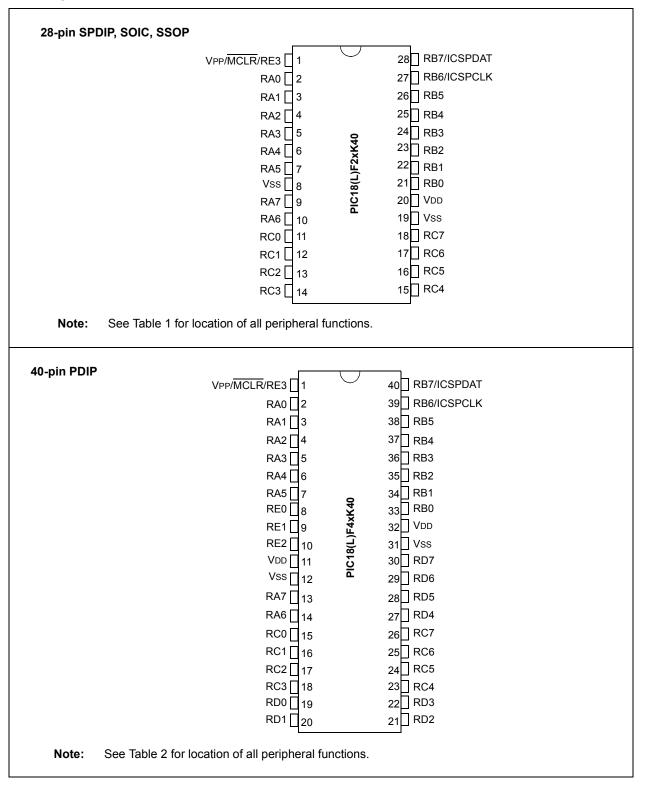

# **Pin Diagrams**

# Pin Allocation Tables

#### TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F27K40)

| I/O <sup>(2)</sup> | 28-Pin SPDIP, SOIC, SSOP | 28-Pin QFN | AD   | Reference                              | Comparator       | Timers               | CCP | CWG                 | ZCD   | Interrupt                    | EUSART                 | WSQ                   | MSSP                                         | Pull-up | Basic          |

|--------------------|--------------------------|------------|------|----------------------------------------|------------------|----------------------|-----|---------------------|-------|------------------------------|------------------------|-----------------------|----------------------------------------------|---------|----------------|

| RA0                | 2                        | 27         | ANA0 | _                                      | C1IN0-<br>C2IN0- | -                    | —   |                     |       | IOCA0                        | —                      | _                     | _                                            | Y       | —              |

| RA1                | 3                        | 28         | ANA1 |                                        | C1IN1-<br>C2IN1- |                      | —   |                     |       | IOCA1                        | —                      | _                     | _                                            | Y       | —              |

| RA2                | 4                        | 1          | ANA2 | DAC1OUT1<br>Vref- (DAC)<br>Vref- (ADC) | C1IN0+<br>C2IN0+ | _                    | —   | —                   | Ι     | IOCA2                        | _                      |                       | —                                            | Y       | _              |

| RA3                | 5                        | 2          | ANA3 | VREF+ (DAC)<br>VREF+ (ADC)             | C1IN1+           | _                    | —   | _                   | _     | IOCA3                        | —                      | MDCIN1 <sup>(1)</sup> | _                                            | Y       | —              |

| RA4                | 6                        | 3          | ANA4 | _                                      | _                | T0CKI <sup>(1)</sup> | _   | _                   | _     | IOCA4                        | _                      | MDCIN2 <sup>(1)</sup> | _                                            | Y       | _              |

| RA5                | 7                        | 4          | ANA5 | _                                      | _                | _                    | _   | _                   | _     | IOCA5                        | _                      | MDMIN <sup>(1)</sup>  | SS1 <sup>(1)</sup>                           | Y       | _              |

| RA6                | 10                       | 7          | ANA6 | —                                      | —                | _                    | —   | _                   | _     | IOCA6                        | —                      | —                     | _                                            | Y       | CLKOUT<br>OSC2 |

| RA7                | 9                        | 6          | ANA7 | _                                      | —                | _                    | —   | _                   | _     | IOCA7                        | —                      | —                     | _                                            | Y       | OSC1<br>CLKIN  |

| RB0                | 21                       | 18         | ANB0 | —                                      | C2IN1+           | _                    | —   | CWG1 <sup>(1)</sup> | ZCDIN | IOCB0<br>INT0 <sup>(1)</sup> | —                      | —                     | <u>SS2</u> (1)                               | Y       | —              |

| RB1                | 22                       | 19         | ANB1 | _                                      | C1IN3-<br>C2IN3- | _                    | —   | _                   | _     | IOCB1<br>INT1 <sup>(1)</sup> | —                      | _                     | SCK2 <sup>(1)</sup><br>SCL2 <sup>(3,4)</sup> | Y       | —              |

| RB2                | 23                       | 20         | ANB2 | _                                      | —                | _                    | —   | _                   | _     | IOCB2<br>INT2 <sup>(1)</sup> | —                      | —                     | SDI2 <sup>(1)</sup><br>SDA2 <sup>(3,4)</sup> | Y       | —              |

| RB3                | 24                       | 21         | ANB3 | _                                      | C1IN2-<br>C2IN2- | —                    | —   | _                   | _     | IOCB3                        | —                      | _                     | _                                            | Y       | —              |

| RB4                | 25                       | 22         | ANB4 | _                                      | —                | T5G <sup>(1)</sup>   | —   | -                   | _     | IOCB4                        | —                      | _                     | _                                            | Y       | —              |

| RB5                | 26                       | 23         | ANB5 | _                                      | _                | T1G <sup>(1)</sup>   | _   | _                   | -     | IOCB5                        | _                      | _                     | _                                            | Y       | _              |

| RB6                | 27                       | 24         | ANB6 | _                                      |                  | —                    | _   |                     | -     | IOCB6                        | CK2 <sup>(1)</sup>     |                       |                                              | Y       | ICSPCLK        |

| RB7                | 28                       | 25         | ANB7 | DAC1OUT2                               | _                | T6AIN <sup>(1)</sup> | _   |                     | _     | IOCB7                        | RX2/DT2 <sup>(1)</sup> |                       | _                                            | Y       | ICSPDAT        |

PIC18(L)F27/47K40

**Note 1:** Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

2: All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for 1<sup>2</sup>C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the 1<sup>2</sup>C specific or SMBus input buffer thresholds.

# 1.4 Register and Bit naming conventions

#### 1.4.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

#### 1.4.2 BIT NAMES

There are two variants for bit names:

- Short name: Bit function abbreviation

- Long name: Peripheral abbreviation + short name

#### 1.4.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is *RegisterName*bits.*ShortName*. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

#### 1.4.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

## 1.4.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

COG1CON0bits.MD = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

Example 1:

MOVLW ~(1<<G1MD1) ANDWF COG1CON0,F MOVLW 1<<G1MD2 | 1<<G1MD0 IORWF COG1CON0,F

#### Example 2:

| BSF | COG1CON0,G1MD2 |

|-----|----------------|

| BCF | COG1CON0,G1MD1 |

| BSF | COG1CON0,G1MD0 |

# 1.4.3 REGISTER AND BIT NAMING EXCEPTIONS

#### 1.4.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

#### 1.4.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

#### REGISTER 3-5: CONFIGURATION WORD 3L (30 0004h): WINDOWED WATCHDOG TIMER

| U-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|-------|-------|-------|-------|-------|------------|-------|-------|

|       | WDTE  | <1:0> |       |       | WDTCPS<4:0 | >     |       |

| bit 7 |       |       |       |       |            |       | bit 0 |

|       |       |       |       |       |            |       |       |

#### Legend: P = Peadable bit W = W

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, rea | d as '1'           |

|-----------------------------|------------------|----------------------------|--------------------|

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 7 Unimplemented: Read as '1'

bit 6-5 **WDTE<1:0>:** WDT Operating Mode bits

- 11 = WDT enabled regardless of Sleep; SEN bit in WDTCON0 is ignored

- 10 = WDT enabled while Sleep = 0, suspended when Sleep = 1; SEN bit in WDTCON0 is ignored

- 01 = WDT enabled/disabled by SEN bit in WDTCON0

- 00 = WDT disabled, SEN bit in WDTCON0 is ignored

#### bit 4-0 WDTCPS<4:0>: WDT Period Select bits

|           |           |               | Software Control |                                    |           |

|-----------|-----------|---------------|------------------|------------------------------------|-----------|

| WDTCPS    | Value     | Divider Ratio |                  | Typical Time Out<br>(Fɪʌ = 31 kHz) | of WDTPS? |

| 11111     | 01011     | 1:65536       | 2 <sup>16</sup>  | 2s                                 | Yes       |

| 10011     | 10011     |               | -                |                                    |           |

| <br>11110 | <br>11110 | 1:32          | 2 <sup>5</sup>   | 1 ms                               | No        |

| 10010     | 10010     | 1:8388608     | 2 <sup>23</sup>  | 256s                               |           |

| 10001     | 10001     | 1:4194304     | 2 <sup>22</sup>  | 128s                               |           |

| 10000     | 10000     | 1:2097152     | 2 <sup>21</sup>  | 64s                                |           |

| 01111     | 01111     | 1:1048576     | 2 <sup>20</sup>  | 32s                                |           |

| 01110     | 01110     | 1:524299      | 2 <sup>19</sup>  | 16s                                |           |

| 01101     | 01101     | 1:262144      | 2 <sup>18</sup>  | 8s                                 |           |

| 01100     | 01100     | 1:131072      | 2 <sup>17</sup>  | 4s                                 |           |

| 01011     | 01011     | 1:65536       | 2 <sup>16</sup>  | 2s                                 |           |

| 01010     | 01010     | 1:32768       | 2 <sup>15</sup>  | 1s                                 |           |

| 01001     | 01001     | 1:16384       | 2 <sup>14</sup>  | 512 ms                             | No        |

| 01000     | 01000     | 1:8192        | 2 <sup>13</sup>  | 256 ms                             |           |

| 00111     | 00111     | 1:4096        | 2 <sup>12</sup>  | 128 ms                             |           |

| 00110     | 00110     | 1:2048        | 2 <sup>11</sup>  | 64 ms                              |           |

| 00101     | 00101     | 1:1024        | 2 <sup>10</sup>  | 32 ms                              |           |

| 00100     | 00100     | 1:512         | 2 <sup>9</sup>   | 16 ms                              | ]         |

| 00011     | 00011     | 1:256         | 2 <sup>8</sup>   | 8 ms                               | ]         |

| 00010     | 00010     | 1:128         | 2 <sup>7</sup>   | 4 ms                               |           |

| 00001     | 00001     | 1:64          | 2 <sup>6</sup>   | 2 ms                               | ]         |

| 00000     | 00000     | 1:32          | 2 <sup>5</sup>   | 1 ms                               |           |

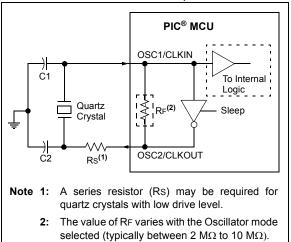

#### FIGURE 4-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

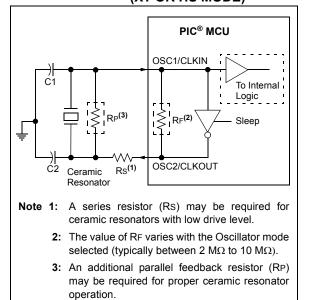

#### FIGURE 4-4: CERAMIC RESONATOR OPERATION (XT OR HS MODE)

# 4.3.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR), or a wake-up from Sleep. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

# 4.3.1.4 4x PLL

The oscillator module contains a 4x PLL that can be used with the external clock sources to provide a system clock source. The input frequency for the PLL must fall within specifications. See the PLL Clock Timing Specifications in Table 37-9.

The PLL can be enabled for use by one of two methods:

- 1. Program the RSTOSC bits in the Configuration Word 1 to 010 (enable EXTOSC with 4x PLL).

- 2. Write the NOSC bits in the OSCCON1 register to 010 (enable EXTOSC with 4x PLL).

# 8.13 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON0 registers are updated to indicate the cause of the Reset. Table 8-3 shows the Reset conditions of these registers.

| Condition                          | Program<br>Counter    | STATUS<br>Register <sup>(2,3)</sup> | PCON0<br>Register |

|------------------------------------|-----------------------|-------------------------------------|-------------------|

| Power-on Reset                     | 0                     | -110 0000                           | 0011 110x         |

| Brown-out Reset                    | 0                     | -110 0000                           | 0011 11u0         |

| MCLR Reset during normal operation | 0                     | -uuu uuuu                           | uuuu Ouuu         |

| MCLR Reset during Sleep            | 0                     | -10u uuuu                           | uuuu Ouuu         |

| WDT Time-out Reset                 | 0                     | -0uu uuuu                           | սսս0 սսսս         |

| WDT Wake-up from Sleep             | PC + 2                | -00u uuuu                           | uuuu uuuu         |

| WWDT Window Violation Reset        | 0                     | -uuu uuuu                           | uu0u uuuu         |

| Interrupt Wake-up from Sleep       | PC + 2 <sup>(1)</sup> | -10u 0uuu                           | uuuu uuuu         |

| RESET Instruction Executed         | 0                     | -uuu uuuu                           | uuuu u0uu         |

| Stack Overflow Reset (STVREN = 1)  | 0                     | -uuu uuuu                           | luuu uuuu         |

| Stack Underflow Reset (STVREN = 1) | 0                     | -uuu uuuu                           | uluu uuuu         |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit (GIE) is set the return address is pushed on the stack and PC is loaded with the corresponding interrupt vector (depending on source, high or low priority) after execution of PC + 2.

2: If a Status bit is not implemented, that bit will be read as '0'.

3: Status bits Z, C, DC are reset by POR/BOR (Register 10-2).

# 13.2 Register Definitions: CRC and Scanner Control

Long bit name prefixes for the CRC and Scanner peripherals are shown in Table 13-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

#### TABLE 13-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CRC        | CRC             |

#### REGISTER 13-1: CRCCON0: CRC CONTROL REGISTER 0

| R/W-0/0 | R/W-0/0 | R-0  | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R-0   |

|---------|---------|------|---------|-----|-----|---------|-------|

| EN      | GO      | BUSY | ACCM    | —   | _   | SHIFTM  | FULL  |

| bit 7   |         |      |         |     |     |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <ul> <li>EN: CRC Enable bit</li> <li>1 = CRC module is released from Reset</li> <li>0 = CRC is disabled and consumes no operating current</li> </ul> |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | GO: CRC Start bit<br>1 = Start CRC serial shifter<br>0 = CRC serial shifter turned off                                                               |

| bit 5   | <b>BUSY:</b> CRC Busy bit<br>1 = Shifting in progress or pending<br>0 = All valid bits in shifter have been shifted into accumulator and EMPTY = 1   |

| bit 4   | ACCM: Accumulator Mode bit<br>1 = Data is augmented with zeros<br>0 = Data is not augmented with zeros                                               |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                           |

| bit 1   | SHIFTM: Shift Mode bit<br>1 = Shift right (LSb)<br>0 = Shift left (MSb)                                                                              |

| bit 0   | <b>FULL:</b> Data Path Full Indicator bit<br>1 = CRCDATH/L registers are full<br>0 = CRCDATH/L registers have shifted their data into the shifter    |

# REGISTER 13-2: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|---------|---------|---------|---------|-----------|---------|---------|---------|--|--|

|         | DLEN    | <3:0>   |         | PLEN<3:0> |         |         |         |  |  |

| bit 7   |         |         |         |           |         |         | bit 0   |  |  |

| Legend:                                                                                                       |         |                            |                                                       |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|---------|----------------------------|-------------------------------------------------------|--|--|--|--|

| R = Readab                                                                                                    | le bit  | W = Writable bit           | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is un                                                                                                 | changed | x = Bit is unknown         | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is se                                                                                               | et      | '0' = Bit is cleared       |                                                       |  |  |  |  |

| bit 7-4 <b>DLEN&lt;3:0&gt;:</b> Data Length bits<br>Denotes the length of the data word -1 (See Example 13-1) |         |                            |                                                       |  |  |  |  |

| bit 3-0                                                                                                       | PLEN<3: | D>: Polynomial Length bits |                                                       |  |  |  |  |

Denotes the length of the polynomial -1 (See Example 13-1)

| U-0                                                                                                                   | U-0                                                                                                                   | U-0              | U-0           | U-0              | R/W-0/0          | R/W-0/0         | R/W-0/0 |  |  |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------------|------------------|-----------------|---------|--|--|

|                                                                                                                       |                                                                                                                       | —                | _             | —                | TMR5GIF          | TMR3GIF         | TMR1GIF |  |  |

| bit 7                                                                                                                 |                                                                                                                       |                  |               |                  |                  |                 | bit 0   |  |  |

|                                                                                                                       |                                                                                                                       |                  |               |                  |                  |                 |         |  |  |

| Legend:                                                                                                               |                                                                                                                       |                  |               |                  |                  |                 |         |  |  |

| R = Readable                                                                                                          | bit                                                                                                                   | W = Writable     | bit           | U = Unimplei     | mented bit, read | as '0'          |         |  |  |

| -n = Value at F                                                                                                       | POR                                                                                                                   | '1' = Bit is set |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |

|                                                                                                                       |                                                                                                                       |                  |               |                  |                  |                 |         |  |  |

| bit 7-3                                                                                                               | Unimplemen                                                                                                            | ted: Read as '   | 0'            |                  |                  |                 |         |  |  |

| bit 2                                                                                                                 | TMR5GIF: TN                                                                                                           | /IR5 Gate Inter  | rupt Flag bit |                  |                  |                 |         |  |  |

|                                                                                                                       | 0                                                                                                                     | e interrupt occ  | •             | e cleared in so  | oftware)         |                 |         |  |  |

|                                                                                                                       | 0 = NO TWR5                                                                                                           | gate occurred    |               |                  |                  |                 |         |  |  |

| bit 1                                                                                                                 |                                                                                                                       | /IR3 Gate Inter  |               |                  | <i>a</i> )       |                 |         |  |  |

|                                                                                                                       | <ul> <li>1 = TMR3 gate interrupt occurred (must be cleared in software)</li> <li>0 = No TMR3 gate occurred</li> </ul> |                  |               |                  |                  |                 |         |  |  |

| bit 0                                                                                                                 | TMR1GIF: TN                                                                                                           | /IR1 Gate Inter  | rupt Flag bit |                  |                  |                 |         |  |  |

| <ul> <li>1 = TMR1 gate interrupt occurred (must be cleared in software)</li> <li>0 = No TMR1 gate occurred</li> </ul> |                                                                                                                       |                  |               |                  |                  |                 |         |  |  |

|                                                                                                                       |                                                                                                                       |                  |               |                  |                  |                 |         |  |  |

# REGISTER 14-7: PIR5: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 5

# 14.9 INTn Pin Interrupts

PIC18(L)F2x/4xK40 devices have three external interrupt sources which can be assigned to any pin on PORTA and PORTB using PPS. The external interrupt sources are edge-triggered. If the corresponding INTxEDG bit in the INTCON0 register is set (= 1), the interrupt is triggered by a rising edge. It the bit is clear, the trigger is on the falling edge.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from Idle or Sleep modes if bit INTxE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE/GIEH, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority is determined by the value contained in the interrupt priority bits, INT0IP, INT1IP and INT2IP of the IPR0 register.

### 14.10 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE of the PIE0 register. Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP of the IPR0 register. See **Section 18.0 "Timer0 Module"** for further details on the Timer0 module.

# 14.11 Interrupt-on-Change

An input change on any port pins that support IOC sets Flag bit, IOCIF of the PIR0 register. The interrupt can be enabled/disabled by setting/clearing the enable bit, IOCIE of the PIE0 register. Pins must also be individually enabled in the IOCxP and IOCxN register. IOCIF is a read-only bit and the flag can be cleared by clearing the corresponding IOCxF registers. For more information refer to **Section 16.0 "Interrupt-on-Change"**.

# 14.12 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see **Section 10.2.2 "Fast Register Stack"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 14-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| EXAMPL | E 14-1: SAVING STATUS, | , WREG AND BSR REGISTERS IN RAM |  |

|--------|------------------------|---------------------------------|--|

| MOVWF  | W_TEMP                 | ; W_TEMP is in virtual bank     |  |

| MOVFF  | STATUS, STATUS_TEMP    | ; STATUS_TEMP located anywhere  |  |

| MOVFF  | BSR, BSR_TEMP          | ; BSR_TEMP located anywhere     |  |

| ;      |                        |                                 |  |

| ; USER | ISR CODE               |                                 |  |

| ;      |                        |                                 |  |

| MOVFF  | BSR_TEMP, BSR          | ; Restore BSR                   |  |

| MOVF   | W_TEMP, W              | ; Restore WREG                  |  |

| MOVFF  | STATUS_TEMP, STATUS    | ; Restore STATUS                |  |

|        |                        |                                 |  |

# EXAMPLE 14-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

# 15.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 17.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over digital outputs and force the digital output driver into a high-impedance state.

The pin function priorities are as follows:

- 1. Configuration bits

- 2. Analog outputs (disable the input buffers)

- 3. Analog inputs

- 4. Port inputs and outputs from PPS

# 15.2 PORTx Registers

In this section the generic names such as PORTx, LATx, TRISx, etc. can be associated with PORTA, PORTB, PORTC and PORTD. For availability of PORTD refer to Table 15-1. The functionality of PORTE is different compared to other ports and is explained in a separate section.

#### 15.2.1 DATA REGISTER

PORTx is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISx (Register 15-2). Setting a TRISx bit ('1') will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISx bit ('0') will make the corresponding PORTx pin an output (i.e., it enables output driver and puts the contents of the output latch on the selected pin). Example 15-1 shows how to initialize PORTx.

Reading the PORTx register (Register 15-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATx).

The PORT data latch LATx (Register 15-3) holds the output port data and contains the latest value of a LATx or PORTx write.

#### EXAMPLE 15-1: INITIALIZING PORTA

| ; initia | ports are in | illustrates<br>ORTA register. The<br>itialized in the same |

|----------|--------------|------------------------------------------------------------|

| BANKSEL  | PORTA        | ;                                                          |

| CLRF     | PORTA        | ;Init PORTA                                                |

| BANKSEL  | LATA         | ;Data Latch                                                |

| CLRF     | LATA         | ;                                                          |

| BANKSEL  | ANSELA       | ;                                                          |

| CLRF     | ANSELA       | ;digital I/O                                               |

|          |              |                                                            |

# MOVWF TRISA ;and set RA<2:0> as ;outputs

B'11111000' ;Set RA<7:3> as inputs

# 15.2.2 DIRECTION CONTROL

BANKSEL TRISA

MOVLW

The TRISx register (Register 15-2) controls the PORTx pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISx register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 15.2.3 ANALOG CONTROL

The ANSELx register (Register 15-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELx bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELx bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELx bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

# 15.2.4 OPEN-DRAIN CONTROL

The ODCONx register (Register 15-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONx bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONx bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

**Note:** It is not necessary to set open-drain control when using the pin for I<sup>2</sup>C; the I<sup>2</sup>C module controls the pin and makes the pin open-drain.

#### 20.5.5 SOFTWARE START ONE-SHOT MODE

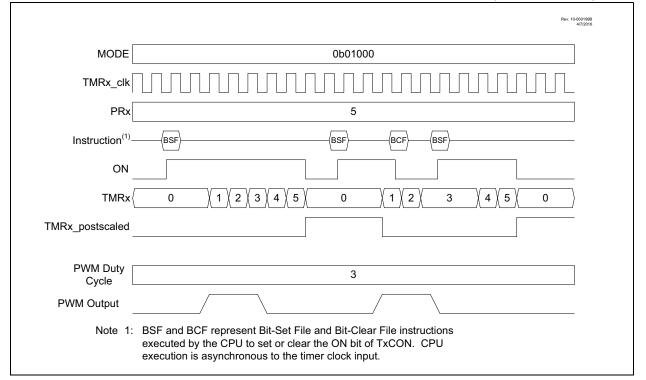

In One-Shot mode the timer resets and the ON bit is cleared when the timer value matches the PRx period value. The ON bit must be set by software to start another timer cycle. Setting MODE<4:0> = 01000 selects One-Shot mode which is illustrated in Figure 20-8. In the example, ON is controlled by BSF and BCF instructions. In the first case, a BSF instruction sets ON and the counter runs to completion and clears ON. In the second case, a BSF instruction starts the cycle, BCF/BSF instructions turn the counter off and on during the cycle, and then it runs to completion.

When One-Shot mode is used in conjunction with the CCP PWM operation the PWM pulse drive starts concurrent with setting the ON bit. Clearing the ON bit while the PWM drive is active will extend the PWM drive. The PWM drive will terminate when the timer value matches the CCPRx pulse width value. The PWM drive will remain off until software sets the ON bit to start another cycle. If software clears the ON bit after the CCPRx match but before the PRx match then the PWM drive will be extended by the length of time the ON bit remains cleared. Another timing cycle can only be initiated by setting the ON bit after it has been cleared by a PRx period count match.

FIGURE 20-8: SOFTWARE START ONE-SHOT MODE TIMING DIAGRAM (MODE = 01000)

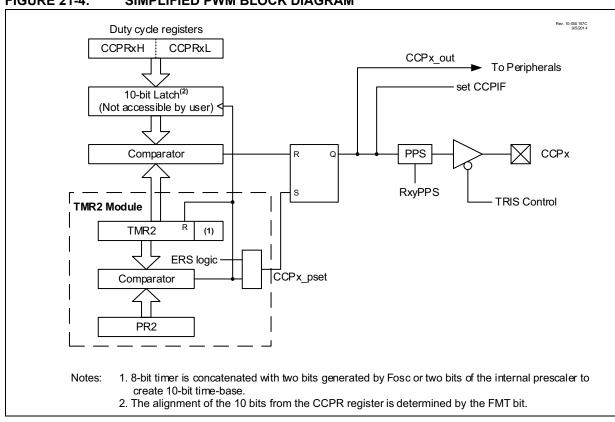

#### FIGURE 21-4: SIMPLIFIED PWM BLOCK DIAGRAM

# PIC18(L)F27/47K40

| R/W-0/0          | R/W-0/0                                                                              | R/W-0/0                             | R/W-0/0         | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------|-------------------------------------|-----------------|---------------------|---------------------|---------------------|---------------------|--|--|--|--|

| OVRD             | OVRC                                                                                 | OVRB                                | OVRA            | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |  |  |  |  |

| bit 7            |                                                                                      |                                     |                 |                     |                     |                     | bit 0               |  |  |  |  |

| Legend:          |                                                                                      |                                     |                 |                     |                     |                     |                     |  |  |  |  |

| R = Readable     | bit                                                                                  | W = Writable                        | bit             | U = Unimpler        | mented bit, read    | l as '0'            |                     |  |  |  |  |

| u = Bit is unch  | nanged                                                                               | x = Bit is unki                     | nown            | -n/n = Value a      | at POR and BO       | R/Value at all c    | other Resets        |  |  |  |  |

| '1' = Bit is set |                                                                                      | '0' = Bit is cle                    | ared            | q = Value dep       | pends on condit     | ion                 |                     |  |  |  |  |

| bit 7            | OVED: Stoo                                                                           | ring Data D bit                     |                 |                     |                     |                     |                     |  |  |  |  |

| bit 6            |                                                                                      | ring Data C bit                     |                 |                     |                     |                     |                     |  |  |  |  |

| bit 5            |                                                                                      | ring Data B bit                     |                 |                     |                     |                     |                     |  |  |  |  |

| bit 4            |                                                                                      | ring Data A bit                     |                 |                     |                     |                     |                     |  |  |  |  |

| bit 3            |                                                                                      | ring Enable bit [                   | )(2)            |                     |                     |                     |                     |  |  |  |  |

| Sit O            |                                                                                      | output has the                      |                 | ut waveform wi      | ith polarity contr  | ol from POLD        | bit                 |  |  |  |  |

|                  |                                                                                      | output is assign                    |                 |                     | . ,                 |                     |                     |  |  |  |  |

| bit 2            | STRC: Steer                                                                          | STRC: Steering Enable bit $C^{(2)}$ |                 |                     |                     |                     |                     |  |  |  |  |

|                  | 1 = CWG1C output has the CWG data input waveform with polarity control from POLC bit |                                     |                 |                     |                     |                     |                     |  |  |  |  |

|                  |                                                                                      | output is assign                    |                 | f OVRC bit          |                     |                     |                     |  |  |  |  |

| bit 1            | STRB: Steer                                                                          | ring Enable bit E                   | 3(2)            |                     |                     |                     |                     |  |  |  |  |

|                  |                                                                                      | output has the                      | •               |                     | th polarity contr   | ol from POLB        | oit                 |  |  |  |  |

|                  |                                                                                      | output is assigr                    |                 | OVRB bit            |                     |                     |                     |  |  |  |  |

| bit 0            |                                                                                      | ring Enable bit A                   |                 |                     |                     |                     |                     |  |  |  |  |

|                  | 1 = CWG1A output has the CWG data input waveform with polarity control from POLA bit |                                     |                 |                     |                     |                     |                     |  |  |  |  |

|                  | 0 = CWG1A                                                                            | output is assigr                    | ned to value of | OVRA bit            |                     |                     |                     |  |  |  |  |

| Note 1: The      | e bits in this reg                                                                   | gister apply only                   | when MODE       | <2:0> = 00x (R      | Register 24-1, St   | teering modes)      |                     |  |  |  |  |

|                  |                                                                                      |                                     |                 |                     |                     |                     |                     |  |  |  |  |

**2:** This bit is double-buffered when MODE < 2:0 > = 0.01.

# 26.9.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSPxCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 26.9.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSPxSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPxBUF with data to transfer to the master. If the SEN bit of SSPxCON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPxBUF was read before the ninth falling edge of SCL.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPxBUF was loaded before the ninth falling edge of SCL. It is now always cleared for read requests.

#### 26.9.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSPxADD.

**Note:** Previous versions of the module did not stretch the clock if the second address byte did not match.

# 26.9.6.3 Byte NACKing

When the AHEN bit of SSPxCON3 is set; CKP is cleared by hardware after the eighth falling edge of SCL for a received matching address byte. When the DHEN bit of SSPxCON3 is set; CKP is cleared after the eighth falling edge of SCL for received data.

Stretching after the eighth falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

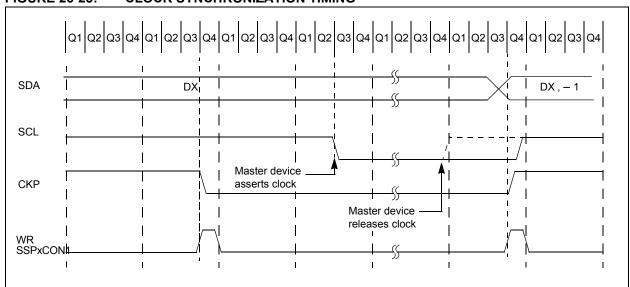

# 26.9.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 26-23).

FIGURE 26-23: CLOCK SYNCHRONIZATION TIMING

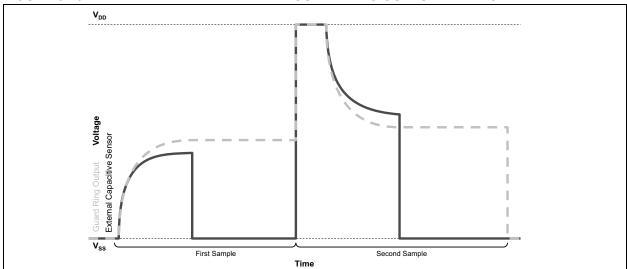

FIGURE 31-9: DIFFERENTIAL CVD WITH GUARD RING OUTPUT WAVEFORM

| Precharge<br>Time                                           | Acquisition/<br>Sharing Time                      | ı<br>                                                                                                  |                  |         | (Tradi | Co<br>tional |              | on Tin<br>of AD |      | nversi | on)     |       |       |

|-------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------|---------|--------|--------------|--------------|-----------------|------|--------|---------|-------|-------|

| 1-255 TINST<br>(TPRE)                                       | 1-255 TINST<br>(TACQ)                             | <br>,TCY - TAE                                                                                         | TAD1             | TAD2    | TAD3   | Tad4         | Tad5         | Tad6            | TAD7 | TAD8   | TAD9    | TAD10 | Tad11 |

|                                                             |                                                   | <b>Ì</b> ↑ _ 4                                                                                         |                  | b9      | b8     | b7           | b6           | b5              | b4   | b3     | b2      | b1    | b0    |

| External and Internal<br>Channels are<br>charged/discharged | External and Internal<br>Channels share<br>charge | I<br>Conversion starts<br>Holding capacitor Сно∟р is disconnected from analog input (typically 100 ns) |                  |         |        |              |              |                 |      |        |         |       |       |

| If ADPRE ≠ 0                                                | If ADACQ ≠ 0                                      | If ADPR                                                                                                | $\mathbf{Q} = 0$ |         |        |              |              |                 |      |        | is load | ed    | 1     |

| et GO/DONE bit                                              |                                                   | (Traditio                                                                                              | nal Op           | eration | Start) |              | ADI <u>F</u> | <u>bit is</u> s |      |        | 13 1000 | cu,   |       |

# 31.4.5 ADDITIONAL SAMPLE AND HOLD CAPACITANCE

Additional capacitance can be added in parallel with the internal sample and hold capacitor (CHOLD) by using the ADCAP register. This register selects a digitally programmable capacitance which is added to the ADC conversion bus, increasing the effective internal capacitance of the sample and hold capacitor in the ADC module. This is used to improve the match between internal and external capacitance for a better sensing performance. The additional capacitance does not affect analog performance of the ADC because it is not connected during conversion. See Figure 31-11.

# 32.0 COMPARATOR MODULE

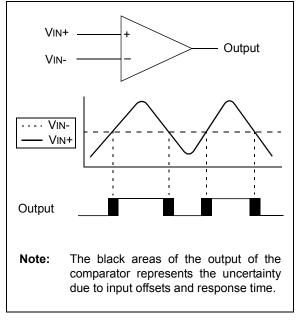

**Note:** The PIC18(L)F27/47K40 devices have two comparators. Therefore, all information in this section refers to both C1 and C2.

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution.

The analog comparator module includes the following features:

- Programmable input selection

- Programmable output polarity

- Rising/falling output edge interrupts

- Wake-up from Sleep

- CWG Auto-shutdown source

- Selectable voltage reference

- ADC Auto-trigger

- TMR1/3/5 Gate

- TMR2/4/6 Reset

- CCP Capture Mode Input

- DSM Modulator Source

- Input and Window signal to Signal Measurement

Timer

# 32.1 Comparator Overview

A single comparator is shown in Figure 32-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

# 32.11 CWG1 Auto-Shutdown Source

The output of the comparator module can be used as an auto-shutdown source for the CWG1 module. When the output of the comparator is active and the corresponding WGASxE is enabled, the CWG operation will be suspended immediately (see Section 24.10.1.2 "External Input Source").

# 32.12 ADC Auto-Trigger Source

The output of the comparator module can be used to trigger an ADC conversion. When the ADACT register is set to trigger on a comparator output, an ADC conversion will trigger when the Comparator output goes high.

# 32.13 TMR2/4/6 Reset

The output of the comparator module can be used to reset Timer2. When the TxERS register is appropriately set, the timer will reset when the Comparator output goes high.

# 32.14 Operation in Sleep Mode

The comparator module can operate during Sleep. The comparator clock source is based on the Timer1 clock source. If the Timer1 clock source is either the system clock (FOSC) or the instruction clock (FOSC/4), Timer1 will not operate during Sleep, and synchronized comparator outputs will not operate.

A comparator interrupt will wake the device from Sleep. The CxIE bits of the PIE2 register must be set to enable comparator interrupts.

# PIC18(L)F27/47K40

| MO\   | Index                                 | ed                                                                                                                                                                                            |                                                                                                                                           |                                                                                                                                    |                      |

|-------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Synta | ax:                                   | MOVSS [z                                                                                                                                                                                      | z <sub>s</sub> ], [z <sub>d</sub> ]                                                                                                       |                                                                                                                                    |                      |

| Oper  | ands:                                 | $0 \le z_s \le 127$                                                                                                                                                                           | 7                                                                                                                                         |                                                                                                                                    |                      |

|       |                                       | $0 \le z_d \le 12$                                                                                                                                                                            | 7                                                                                                                                         |                                                                                                                                    |                      |

| Oper  | ation:                                | ((FSR2) + z                                                                                                                                                                                   | $(FS) \rightarrow ((FS))$                                                                                                                 | SR2) +                                                                                                                             | z <sub>d</sub> )     |

| Statu | s Affected:                           | None                                                                                                                                                                                          |                                                                                                                                           |                                                                                                                                    |                      |

|       | ding:<br>ord (source)<br>vord (dest.) | 1110<br>1111                                                                                                                                                                                  | 1011<br>xxxx                                                                                                                              | lzzz<br>xzzz                                                                                                                       | s                    |

| Desc  | ription                               | ne destina<br>of the source<br>offsets 'z <sub>s</sub><br>y, to the va<br>n be loca<br>yte data m<br>Fh).<br>instruction<br>J, TOSH of<br>register.<br>ant source<br>addressin<br>ned will be | ition re<br>rce and<br>ned by<br>alue of<br>ted an<br>nemory<br>on canr<br>or TOS<br>e addres<br>g regis<br>e 00h. I<br>addres<br>g regis | FSR2. Both<br>ywhere in<br>y space<br>not use the<br>L as the<br>ess points to<br>ster, the<br>lf the<br>as points to<br>ster, the |                      |

| Word  | ls:                                   | 2                                                                                                                                                                                             |                                                                                                                                           |                                                                                                                                    |                      |

| Cycle | es:                                   | 2                                                                                                                                                                                             |                                                                                                                                           |                                                                                                                                    |                      |

| QC    | ycle Activity:                        |                                                                                                                                                                                               |                                                                                                                                           |                                                                                                                                    |                      |

|       | Q1                                    | Q2                                                                                                                                                                                            | Q3                                                                                                                                        | <u> </u>                                                                                                                           | Q4                   |

|       | Decode                                | Determine                                                                                                                                                                                     | Determ                                                                                                                                    | -                                                                                                                                  | Read                 |

|       |                                       | source addr                                                                                                                                                                                   | source a                                                                                                                                  |                                                                                                                                    | source reg           |

|       | Decode                                | Determine<br>dest addr                                                                                                                                                                        | Determ<br>dest ac                                                                                                                         | -                                                                                                                                  | Write<br>to dest reg |

| Example:                               | MOVSS   | [05h], | [06h] |

|----------------------------------------|---------|--------|-------|

| Before Instruction<br>FSR2<br>Contents | on<br>= | 80h    |       |

| of 85h<br>Contents                     | =       | 33h    |       |

| of 86h                                 | =       | 11h    |       |

| After Instruction<br>FSR2<br>Contents  | =       | 80h    |       |

| of 85h<br>Contents                     | =       | 33h    |       |

| of 86h                                 | =       | 33h    |       |

| PUSHL            | Store Liter                                              | al at F             | SR         | 2, Decr               | eme  | ent FSR2              |

|------------------|----------------------------------------------------------|---------------------|------------|-----------------------|------|-----------------------|

| Syntax:          | PUSHL k                                                  |                     |            |                       |      |                       |

| Operands:        | $0 \leq k \leq 255$                                      |                     |            |                       |      |                       |

| Operation:       | $k \rightarrow (FSR2)$<br>FSR2 – 1 –                     |                     | 2          |                       |      |                       |

| Status Affected: | None                                                     |                     |            |                       |      |                       |

| Encoding:        | 1111                                                     | 101                 | 0          | kkkk                  |      | kkkk                  |

|                  | memory ad<br>is decremen<br>This instruc<br>onto a softw | nted by<br>tion all | 1 a<br>ows | after the of users to | oper | ration.               |

| Words:           | 1                                                        |                     |            |                       |      |                       |

| Cycles:          | 1                                                        |                     |            |                       |      |                       |

| Q Cycle Activity | /:                                                       |                     |            |                       |      |                       |

| Q1               | Q2                                                       |                     | (          | Q3                    |      | Q4                    |

| Decode           | Read '                                                   | K'                  |            |                       |      | Vrite to<br>stination |

| Example:         | PUSHL                                                    | 08h                 |            |                       |      |                       |

|                  | ruction<br>H:FSR2L<br>pry (01ECh)                        |                     | =          | 01ECh<br>00h          |      |                       |

| After Instru     | ction                                                    |                     |            |                       |      |                       |

01EBh 08h

=

FSR2H:FSR2L Memory (01ECh)

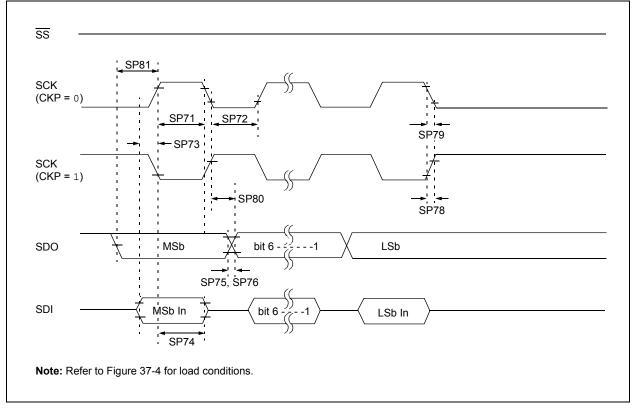

FIGURE 37-17: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

$\ensuremath{\textcircled{\sc 0}}$  2016-2017, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-1640-1