Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27k40-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address           | Name       | Bit 7  | Bit 6   | Bit 5 | Bit 4         | Bit 3          | Bit 2        | Bit 1  | Bit 0     | <u>Value on</u><br>POR, BOR |

|-------------------|------------|--------|---------|-------|---------------|----------------|--------------|--------|-----------|-----------------------------|

| EB1h              | CWGINPPS   | _      | —       | _     |               | CWGINPPS<4:0>  |              |        |           |                             |

| EB0h              | CCP2PPS    | _      | —       | _     |               |                | CCP2PPS<4:0  | >      |           | 10001                       |

| EAFh              | CCP1PPS    | _      | _       | _     |               |                | CCP1PPS<4:0  | >      |           | 10010                       |

| EAEh              | ADACTPPS   | _      | —       | _     |               | /              | ADACTPPS<4:( | )>     |           | 01100                       |

| EADh              | T6INPPS    | _      | _       | _     |               |                | T6INPPS<4:0> | •      |           | 01111                       |

| EACh              | T4INPPS    | _      | —       | _     |               |                | T4INPPS<4:0> | •      |           | 10101                       |

| EABh              | T2INPPS    | _      | —       | _     |               |                | T2INPPS<4:0> | •      |           | 10011                       |

| EAAh              | T5GPPS     | _      | —       | _     |               |                | T5GPPS<4:0>  |        |           | 01100                       |

| EA9h              | T5CKIPPS   | _      | —       | _     |               |                | T5CKIPPS<4:0 | >      |           | 10010                       |

| EA8h              | T3GPPS     | _      | —       | _     |               |                | T3GPPS<4:0>  |        |           | 10000                       |

| EA7h              | T3CKIPPS   | _      | —       | _     |               |                | T3CKIPPS<4:0 | >      |           | 10000                       |

| EA6h              | T1GPPS     | _      | —       | _     |               |                | T1GPPS<4:0>  |        |           | 01101                       |

| EA5h              | T1CKIPPS   | _      | —       | _     |               |                | T1CKIPPS<4:0 | >      |           | 10000                       |

| EA4h              | TOCKIPPS   | _      | —       | _     |               |                | T0CKIPPS<4:0 | >      |           | 00100                       |

| EA3h              | INT2PPS    | _      | —       | _     |               |                | INT2PPS<4:0> | •      |           | 01010                       |

| EA2h              | INT1PPS    | _      | —       | _     |               |                | INT1PPS<4:0> | •      |           | 01001                       |

| EA1h              | INTOPPS    | _      | —       | _     |               |                | INT0PPS<4:0> | •      |           | 01000                       |

| EA0h              | PPSLOCK    | _      | —       | _     | —             | —              | —            | —      | PPSLOCKED | 0                           |

| E9Fh              | BAUD2CON   | ABDOVF | RCIDL   | _     | SCKP          | BRG16          | _            | WUE    | ABDEN     | 01-00-00                    |

| E9Eh              | TX2STA     | CSRC   | TX9     | TXEN  | SYNC          | SENDB          | BRGH         | TRMT   | TX9D      | 00000010                    |

| E9Dh              | RC2STA     | SPEN   | RX9     | SREN  | CREN          | ADDEN          | FERR         | OERR   | RX9D      | 00000000                    |

| E9Ch              | SP2BRGH    |        |         | EUSA  | RT2 Baud Rat  | e Generator, H | igh Byte     |        |           | 00000000                    |

| E9Bh              | SP2BRGL    |        |         | EUSA  | ART2 Baud Rat | e Generator, L | ow Byte      |        |           | 00000000                    |

| E9Ah              | TX2REG     |        |         |       | EUSART2 Tra   | ansmit Registe | r            |        |           | 00000000                    |

| E99h              | RC2REG     |        |         |       | EUSART2 Re    | eceive Registe | r            |        |           | 00000000                    |

| E98h              | SSP2CON3   | ACKTIM | PCIE    | SCIE  | BOEN          | SDAHT          | SBCDE        | AHEN   | DHEN      | 00000000                    |

| E97h              | SSP2CON2   | GCEN   | ACKSTAT | ACKDT | ACKEN         | RCEN           | PEN          | RSEN   | SEN       | 00000000                    |

| E96h              | SSP2CON1   | WCOL   | SSPOV   | SSPEN | CKP           |                | SSPN         | 1<3:0> |           | 00000000                    |

| E95h              | SSP2STAT   | SMP    | CKE     | D/A   | Р             | S              | R/W          | UA     | BF        | 00000000                    |

| E94h              | SSP2MSK    |        |         |       | MSP           | <7:0>          |              |        |           | 11111111                    |

| E93h              | SSP2ADD    |        |         |       | ADE           | )<7:0>         |              |        |           | 00000000                    |

| E92h              | SSP2BUF    |        |         |       | BUF           | <7:0>          |              |        |           | xxxxxxxx                    |

| E91h              | SSP2SSPPS  | _      | —       | —     |               | :              | SSPSSPPS<4:( | )>     |           | 00101                       |

| E90h              | SSP2DATPPS | —      | —       | —     |               | S              | SPDATPPS<4:  | 0>     |           | 10100                       |

| E8Fh              | SSP2CLKPPS | —      | —       | —     |               | S              | SPCLKPPS<4:  | 0>     |           | 10011                       |

| E8Eh              | TX2PPS     | —      | —       | —     |               |                | TXPPS<4:0>   |        |           | 10110                       |

| E8Dh              | RX2PPS     | _      | —       | —     |               |                | RXPPS<4:0>   |        |           | 10111                       |

| E8Ch<br>-<br>E7Eh | _          |        |         |       | Unimpl        | emented        |              |        |           | _                           |

## TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F27/47K40 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F27K40 (28-pin variants).

# 13.2 Register Definitions: CRC and Scanner Control

Long bit name prefixes for the CRC and Scanner peripherals are shown in Table 13-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

#### TABLE 13-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CRC        | CRC             |

### REGISTER 13-1: CRCCON0: CRC CONTROL REGISTER 0

| R/W-0/0 | R/W-0/0 | R-0  | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R-0   |

|---------|---------|------|---------|-----|-----|---------|-------|

| EN      | GO      | BUSY | ACCM    | —   | _   | SHIFTM  | FULL  |

| bit 7   |         |      |         |     |     |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <ul> <li>EN: CRC Enable bit</li> <li>1 = CRC module is released from Reset</li> <li>0 = CRC is disabled and consumes no operating current</li> </ul> |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | GO: CRC Start bit<br>1 = Start CRC serial shifter<br>0 = CRC serial shifter turned off                                                               |

| bit 5   | <b>BUSY:</b> CRC Busy bit<br>1 = Shifting in progress or pending<br>0 = All valid bits in shifter have been shifted into accumulator and EMPTY = 1   |

| bit 4   | ACCM: Accumulator Mode bit<br>1 = Data is augmented with zeros<br>0 = Data is not augmented with zeros                                               |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                           |

| bit 1   | SHIFTM: Shift Mode bit<br>1 = Shift right (LSb)<br>0 = Shift left (MSb)                                                                              |

| bit 0   | <b>FULL:</b> Data Path Full Indicator bit<br>1 = CRCDATH/L registers are full<br>0 = CRCDATH/L registers have shifted their data into the shifter    |

# REGISTER 13-2: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|---------|---------|---------|---------|-----------|---------|---------|---------|--|

|         | DLEN    | <3:0>   |         | PLEN<3:0> |         |         |         |  |

| bit 7   |         |         |         |           |         |         | bit 0   |  |

| Legend:         |         |                                                                    |                                                       |

|-----------------|---------|--------------------------------------------------------------------|-------------------------------------------------------|

| R = Readab      | le bit  | W = Writable bit                                                   | U = Unimplemented bit, read as '0'                    |

| u = Bit is un   | changed | x = Bit is unknown                                                 | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is se | et      | '0' = Bit is cleared                                               |                                                       |

| bit 7-4         |         | <b>0&gt;:</b> Data Length bits<br>he length of the data word -1 (S | ee Example 13-1)                                      |

| bit 3-0         | PLEN<3: | D>: Polynomial Length bits                                         |                                                       |

Denotes the length of the polynomial -1 (See Example 13-1)

# 14.4 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable and priority bits.

# 14.5 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Request Flag registers (PIR0, PIR1, PIR2, PIR3, PIR4, PIR5, PIR6 and PIR7).

# 14.6 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Enable registers (PIE0, PIE1, PIE2, PIE3, PIE4, PIE5, PIE6 and PIE7). When IPEN = 0, the PEIE/GIEL bit must be set to enable any of these peripheral interrupts.

# 14.7 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are eight Peripheral Interrupt Priority registers (IPR0, IPR1, IPR2, IPR3, IPR4 and IPR5, IPR6 and IPR7). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

# PIC18(L)F27/47K40

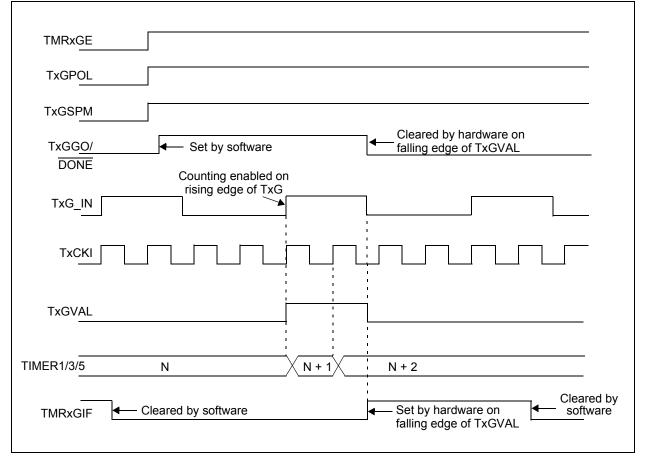

| FIGURE 19-5: | TIMER1/3/5 GATE TOGGLE MODE                                                                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                                                                                                                          |

| TMRxGE       |                                                                                                                                          |

| TxGPOL       |                                                                                                                                          |

| TxGTM        |                                                                                                                                          |

| TxTxG_IN     |                                                                                                                                          |

| ТхСКІ        |                                                                                                                                          |

| TxGVAL       |                                                                                                                                          |

| TIMER1/3/5   | $N \qquad \qquad$ |

|              |                                                                                                                                          |

# FIGURE 19-6: TIMER1/3/5 GATE SINGLE-PULSE MODE

| R/W-0/0        | ) R/W-0/0                                                   | R/W-0/0                                                   | R/W-0/0                           | R/W-0/0                                                           | R/W-0/0          | R/W-0/0          | R/W-0/0         |

|----------------|-------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------|------------------|------------------|-----------------|

| PSYNC          | CPOL                                                        | CSYNC                                                     |                                   |                                                                   | MODE<4:0>        |                  |                 |

| bit 7          |                                                             |                                                           |                                   |                                                                   |                  |                  | bit 0           |

|                |                                                             |                                                           |                                   |                                                                   |                  |                  |                 |

| Legend:        |                                                             |                                                           |                                   |                                                                   |                  |                  |                 |

| R = Reada      | ible bit                                                    | W = Writable                                              | bit                               | U = Unimpler                                                      | nented bit, read | 1 as '0'         |                 |

| u = Bit is u   | nchanged                                                    | x = Bit is unkr                                           | nown                              | -n/n = Value a                                                    | at POR and BO    | R/Value at all o | other Resets    |

| '1' = Bit is s | set                                                         | '0' = Bit is cle                                          | ared                              |                                                                   |                  |                  |                 |

| bit 7          | 1 = TMRx P                                                  | rescaler Output                                           | is synchroniz                     | n Enable bit <sup>(1, 2</sup><br>ed to Fosc/4<br>onized to Fosc/4 |                  |                  |                 |

| bit 6          | 1 = Falling e<br>0 = Rising e                               | rx Clock Polarit<br>dge of input clo<br>dge of input clo  | ock clocks time<br>ck clocks time | er/prescaler<br>r/prescaler                                       |                  |                  |                 |

| bit 5          | 1 = ON regis                                                | erx Clock Sync<br>ster bit is synch<br>ster bit is not sy | ronized to TM                     |                                                                   | t                |                  |                 |

| bit 4-0        |                                                             | Timerx Contro                                             |                                   | ion bits <sup>(6, 7)</sup>                                        |                  |                  |                 |

|                | Setting this bit er<br>When this bit is '<br>CKPOL should n | 1', Timer2 cann                                           | ot operate in S                   |                                                                   | lata value.      |                  |                 |

| 3.<br>4:       |                                                             | •                                                         |                                   | hen the ON is e                                                   | nahled or disa   | hled             |                 |

|                | When this bit is se                                         | 0                                                         | •                                 |                                                                   |                  |                  | e ON bit is set |

|                | Unless otherwise<br>affecting the value                     | e indicated, all                                          | •                                 |                                                                   | •                |                  |                 |

| -              | When TMRx = P                                               |                                                           |                                   |                                                                   | £ 11             |                  |                 |

# REGISTER 20-2: TxHLT: TIMERx HARDWARE LIMIT CONTROL REGISTER

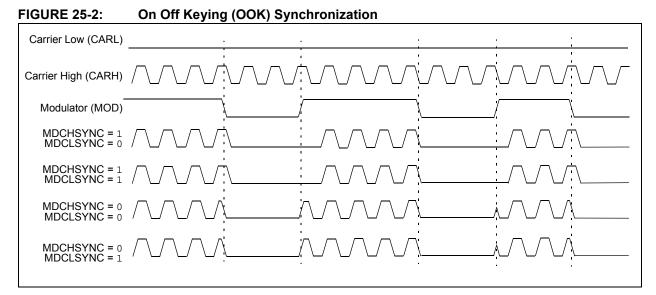

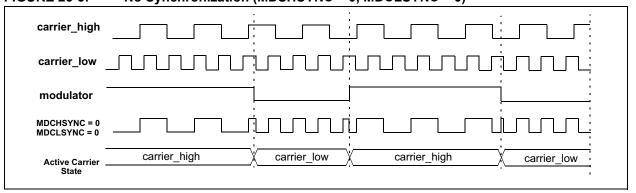

# FIGURE 25-3: No Synchronization (MDSHSYNC = 0, MDCLSYNC = 0)

FIGURE 25-4: Carrier High Synchronization (MDSHSYNC = 1, MDCLSYNC = 0)

| carrier_high                 |                                                                       |

|------------------------------|-----------------------------------------------------------------------|

| carrier_low                  |                                                                       |

| modulator                    |                                                                       |

| MDCHSYNC = 1<br>MDCLSYNC = 0 |                                                                       |

| Active Carrier<br>State      | carrier_high /_both\carrier_low \ / carrier_high / both \ carrier_low |

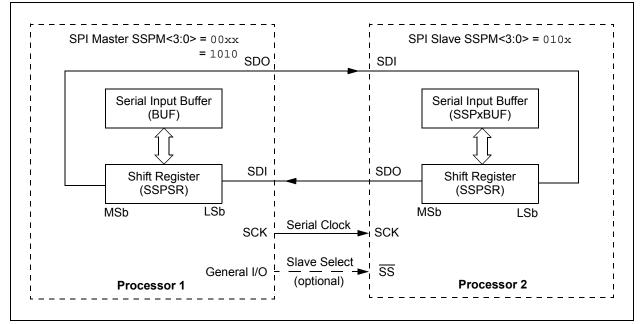

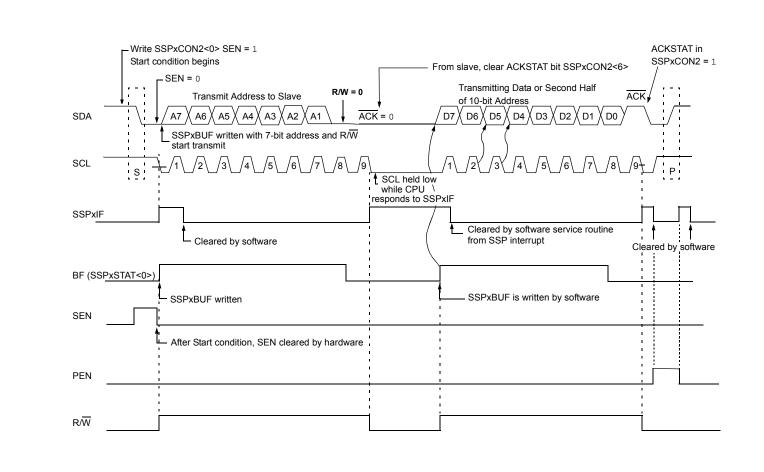

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various Status conditions.

#### FIGURE 26-3: SPI MASTER/SLAVE CONNECTION

| R/W-0            | R/W-0 | R/W-0               | R/W-0 | R/W-0          | R/W-0            | R/W-0          | R/W-0        |

|------------------|-------|---------------------|-------|----------------|------------------|----------------|--------------|

|                  |       |                     | ADD   | )<7:0>         |                  |                |              |

| bit 7            |       |                     |       |                |                  |                | bit 0        |

|                  |       |                     |       |                |                  |                |              |

| Legend:          |       |                     |       |                |                  |                |              |

| R = Readable b   | it    | W = Writable bit    | :     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is uncha | nged  | x = Bit is unknow   | wn    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |       | '0' = Bit is cleare | ed    |                |                  |                |              |

# **REGISTER 26-11:** SSPxADD: MSSP ADDRESS REGISTER (I<sup>2</sup>C MASTER MODE)

# Master mode: |<sup>2</sup>C mode

| bit 7-0 | Baud Rate Clock Divider bits <sup>(1)</sup>             |

|---------|---------------------------------------------------------|

|         | SCK/SCL pin clock period = ((SSPxADD<7:0> + 1) *4)/Fosc |

#### 10-Bit Slave mode – Most Significant Address Byte:

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a don't care. Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to, '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<9:8>: Two Most Significant bits of 10-bit Address

- bit 0 Not used: Unused in this mode. Bit state is a don't care.

### 10-Bit Slave mode – Least Significant Address Byte:

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit Address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a don't care.

**Note 1:** Values of 0x00, 0x01 and 0x02 are not valid for SSPxADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

#### REGISTER 26-12: SSPxMSK: MSSPx ADDRESS MASK REGISTER

| R/W-1   | R/W-1    | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|----------|-------|-------|-------|-------|-------|-------|

|         | MSK<7:1> |       |       |       |       |       |       |

| bit 7   |          |       |       |       |       |       | bit 0 |

|         |          |       |       |       |       |       |       |

| Legend: |          |       |       |       |       |       |       |

| W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|-------------------------------------------------------|

| x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '0' = Bit is cleared |                                                       |

|                      |                                                       |

|                      | x = Bit is unknown                                    |

| bit 7-1 | MSK<7:1>: Mask bits                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = The received address bit n is compared to SSPxADDn to detect I<sup>2</sup>C address match</li> <li>0 = The received address bit n is not used to detect I<sup>2</sup>C address match</li> </ul>                                                                                                                                                                                                  |

| bit 0   | <b>MSK0:</b> Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address<br>I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):<br>1 = The received address bit 0 is compared to SSPxADD0 to detect I <sup>2</sup> C address match<br>0 = The received address bit 0 is not used to detect I <sup>2</sup> C address match<br>I <sup>2</sup> C Slave mode, 7-bit address, the bit is ignored. |

PIC18(L)F27/47K40

| U-0              | U-0   | U-0               | R/W-0/0 | R/W-0/0        | R/W-0/0           | R/W-0/0           | R/W-0/0   |

|------------------|-------|-------------------|---------|----------------|-------------------|-------------------|-----------|

| —                | —     | —                 |         |                | DAC1R<4:0>        |                   |           |

| bit 7            |       |                   |         |                |                   |                   | bit 0     |

|                  |       |                   |         |                |                   |                   |           |

| Legend:          |       |                   |         |                |                   |                   |           |

| R = Readable b   | bit   | W = Writable      | bit     | U = Unimplem   | ented bit, read a | as 'O'            |           |

| u = Bit is uncha | inged | x = Bit is unkr   | nown    | -n/n = Value a | t POR and BOR     | /Value at all oth | er Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared    |                |                   |                   |           |

## REGISTER 30-2: DAC1CON1: DAC DATA REGISTER

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **DAC1R<4:0>:** Data Input Register for DAC bits

#### TABLE 30-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name     | Bit 7 | Bit 6  | Bit 5 | Bit 4      | Bit 3                  | Bit 2 | Bit 1  | Bit 0 | Register<br>on page |

|----------|-------|--------|-------|------------|------------------------|-------|--------|-------|---------------------|

| DAC1CON0 | EN    | —      | OE1   | OE2        | PSS•                   | <1:0> | —      | NSS   | 428                 |

| DAC1CON1 | —     | —      | _     | DAC1R<4:0> |                        | 429   |        |       |                     |

| FVRCON   | FVREN | FVRRDY | TSEN  | TSRNG      | CDAFVR<1:0> ADFVR<1:0> |       | ۲<1:0> | 423   |                     |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

#### **REGISTER 31-19:** ADRESL: ADC RESULT REGISTER LOW, ADFM = 1

|                  |         |                   |         | •              |                  |                |              |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|                  |         |                   | ADRE    | S<7:0>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | mented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits. Lower eight bits of 10-bit conversion result.

## REGISTER 31-20: ADPREVH: ADC PREVIOUS RESULT REGISTER

| R-x          | R-x | R-x | R-x | R-x | R-x | R-x | R-x   |

|--------------|-----|-----|-----|-----|-----|-----|-------|

| ADPREV<15:8> |     |     |     |     |     |     |       |

| bit 7        |     |     |     |     |     |     | bit 0 |

|              |     |     |     |     |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADPREV<15:8>: Previous ADC Results bits If ADPSIS = 1: Upper byte of ADFLTR at the start of current ADC conversion If ADPSIS = 0: Upper bits of ADRES at the start of current ADC conversion<sup>(1)</sup>

**Note 1:** If ADPSIS = 0, ADPREVH and ADPREVL are formatted the same way as ADRES is, depending on the ADFM bit.

| U-0          | U-0         | U-0              | U-0            | U-0                                     | R/W-0/0   | R/W-0/0  | R/W-0/0 |

|--------------|-------------|------------------|----------------|-----------------------------------------|-----------|----------|---------|

| _            | _           | _                | _              | _                                       |           | PCH<2:0> |         |

| bit 7        |             |                  |                |                                         |           |          | bit 0   |

|              |             |                  |                |                                         |           |          |         |

| Legend:      |             |                  |                |                                         |           |          |         |

| R = Readal   | ble bit     | W = Writable     | bit            | U = Unimplemented bit, read as '0'      |           |          |         |

| -n = Value a | at POR      | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |           |          |         |

| L:1 7 0      |             |                  | ~ 1            |                                         |           |          |         |

| bit 7-3      | Unimplemen  | ted: Read as '   | ).             |                                         |           |          |         |

| bit 2-0      | PCH<2:0>: ( | Comparator Non   | -Inverting Inp | out Channel Se                          | lect bits |          |         |

## **REGISTER 32-4: CMxPCH: COMPARATOR x NON-INVERTING CHANNEL SELECT REGISTER**

| 111 | = | AVss |

|-----|---|------|

110 = FVR Buffer2

101 = DAC\_Output

100 = CxPCH not connected

011 = CxPCH not connected

- 010 = CxPCH not connected

- 001 = CxIN1+

- 000 = CxIN0+

## **REGISTER 32-5: CMOUT: COMPARATOR OUTPUT REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | _   | —   | —   | MC2OUT | MC1OUT |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 1 MC2OUT: Mirror copy of C2OUT bit

| bit 0 | MC10UT: Mirror copy of C10UT bit |

|-------|----------------------------------|

|-------|----------------------------------|

| Name    | Bit 7    | Bit 6     | Bit 5 | Bit 4 | Bit 3                   | Bit 2    | Bit 1   | Bit 0   | Reset<br>Values<br>on page |  |

|---------|----------|-----------|-------|-------|-------------------------|----------|---------|---------|----------------------------|--|

| CMxCON0 | EN       | OUT       | -     | POL   | —                       | —        | HYS     | SYNC    | 468                        |  |

| CMxCON1 | _        | _         | _     | _     | _                       | _        | CxINTP  | CxINTN  | 469                        |  |

| CMxNCH  | _        | _         | _     | _     | —                       |          |         | 469     |                            |  |

| CMxPCH  | _        | _         | _     | _     | —                       | PCH<2:0> |         |         | 470                        |  |

| CMOUT   | _        | —         | _     | _     | —                       | _        | MC2OUT  | MC1OUT  | 470                        |  |

| FVRCON  | FVREN    | FVRRDY    | TSEN  | TSRNG | CDAFV                   | ′R<1:0>  | ADFVI   | R<1:0>  | 423                        |  |

| INTCON  | GIE/GIEH | PEIE/GIEL | IPEN  | _     | —                       | INT2EDG  | INT1EDG | INT0EDG | 170                        |  |

| PIR2    | HLVDIF   | ZCDIF     | _     | _     | —                       | —        | C2IF    | C1IF    | 173                        |  |

| PIE2    | HLVDIE   | ZCDIE     | _     | _     | —                       | —        | C2IE    | C1IE    | 181                        |  |

| IPR2    | HLVDIP   | ZCDIP     | _     | _     | —                       | _        | C2IP    | C1IP    | 189                        |  |

| PMD2    | _        | DACMD     | ADCMD | —     | – – CMP2MD CMP1MD ZCDMD |          |         |         |                            |  |

| RxyPPS  | _        | _         |       |       | RxyPPS<4:0>             |          |         |         |                            |  |

## TABLE 32-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

# PIC18(L)F27/47K40

| BCF                                  | Bit Clear f                                                                                                                                                                                                                                                                                                                                                                                  | BN                                                                                      | Branch if Negative                                                                                                                                                                                                                                                                                    |                                                        |                 |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------|--|--|

| Syntax:                              | BCF f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                | Syntax:                                                                                 | BN n                                                                                                                                                                                                                                                                                                  |                                                        |                 |  |  |

| Operands:                            | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                           | Operands:<br>Operation:                                                                 | -128 ≤ n ≤ 1<br>if NEGATIV<br>(PC) + 2 + 2                                                                                                                                                                                                                                                            |                                                        |                 |  |  |

| Operation:                           | $0 \rightarrow f \le b >$                                                                                                                                                                                                                                                                                                                                                                    | Status Affected:                                                                        | None                                                                                                                                                                                                                                                                                                  |                                                        |                 |  |  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                                                                         | Encoding:                                                                               | 1110                                                                                                                                                                                                                                                                                                  | 0110 nn:                                               | nn nnnn         |  |  |

| Encoding:<br>Description:            | 1001bbbaffffffffBit 'b' in register 'f' is cleared.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select theGPR bank.If 'a' is '0' and the extended instructionset is enabled, this instruction operatesin Indexed Literal Offset Addressingmode whenever $f \le 95$ (5Fh). See Section 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal | Description:<br>Words:<br>Cycles:                                                       | If the NEGATIVE bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction.<br>1<br>1(2) |                                                        |                 |  |  |

| Words:                               | eral Offset Mode" for details.                                                                                                                                                                                                                                                                                                                                                               | Q Cycle Activity:<br>If Jump:                                                           |                                                                                                                                                                                                                                                                                                       |                                                        |                 |  |  |

| Cycles:                              | 1                                                                                                                                                                                                                                                                                                                                                                                            | Q1                                                                                      | Q2                                                                                                                                                                                                                                                                                                    | Q3                                                     | Q4              |  |  |

| Q Cycle Activity:                    |                                                                                                                                                                                                                                                                                                                                                                                              | Decode                                                                                  | Read literal<br>'n'                                                                                                                                                                                                                                                                                   | Process<br>Data                                        | Write to PC     |  |  |

| Q1<br>Decode                         | Q2 Q3 Q4<br>Read Process Write<br>register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                             | No<br>operation<br>If No Jump:                                                          | No<br>operation                                                                                                                                                                                                                                                                                       | No<br>operation                                        | No<br>operation |  |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                              | Q1                                                                                      | Q2                                                                                                                                                                                                                                                                                                    | Q3                                                     | Q4              |  |  |

| Example:<br>Before Instruc<br>FLAG_R |                                                                                                                                                                                                                                                                                                                                                                                              | Decode                                                                                  | Read literal<br>'n'                                                                                                                                                                                                                                                                                   | Process<br>Data                                        | No<br>operation |  |  |

| After Instructio<br>FLAG_R           |                                                                                                                                                                                                                                                                                                                                                                                              | Example:<br>Before Instruct<br>PC<br>After Instructio<br>If NEGA<br>PC<br>If NEGA<br>PC | = ad<br>on<br>TIVE = 1;<br>= ad<br>TIVE = 0;                                                                                                                                                                                                                                                          | BN Jump<br>dress (HERE)<br>dress (Jump)<br>dress (HERE |                 |  |  |

# PIC18(L)F27/47K40

| RCA   | LL             | Relative C                                                                                                | Relative Call                                                                                                                                                                                                                                                                                                                                          |      |            |   |  |  |

|-------|----------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|---|--|--|

| Synta | ax:            | RCALL n                                                                                                   | RCALL n                                                                                                                                                                                                                                                                                                                                                |      |            |   |  |  |

| Oper  | ands:          | -1024 ≤ n ≤                                                                                               | 1023                                                                                                                                                                                                                                                                                                                                                   |      |            |   |  |  |

| Oper  | ation:         | $(PC) + 2 \rightarrow (PC) + 2 + 2$                                                                       |                                                                                                                                                                                                                                                                                                                                                        | ;    |            |   |  |  |

| Statu | s Affected:    | None                                                                                                      |                                                                                                                                                                                                                                                                                                                                                        |      |            |   |  |  |

| Enco  | ding:          | 1101                                                                                                      | 1nnn                                                                                                                                                                                                                                                                                                                                                   | nnnn | nnn        | ı |  |  |

| Desc  | ription:       | from the cui<br>address (PC<br>stack. Then<br>number '2n'<br>have increm<br>instruction, '<br>PC + 2 + 2r | Subroutine call with a jump up to 1K<br>from the current location. First, return<br>address (PC + 2) is pushed onto the<br>stack. Then, add the 2's complement<br>number '2n' to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>2-cycle instruction. |      |            |   |  |  |

| Word  | ls:            | 1                                                                                                         |                                                                                                                                                                                                                                                                                                                                                        |      |            |   |  |  |

| Cycle | es:            | 2                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                      |      |            |   |  |  |

| QC    | ycle Activity: |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                        |      |            |   |  |  |

|       | Q1             | Q2                                                                                                        | Q3                                                                                                                                                                                                                                                                                                                                                     | 3    | Q4         |   |  |  |

|       | Decode         | Read literal<br>'n'<br>PUSH PC to<br>stack                                                                | Proce<br>Dat                                                                                                                                                                                                                                                                                                                                           |      | Write to P | С |  |  |

|       | No             | No                                                                                                        | No                                                                                                                                                                                                                                                                                                                                                     |      | No         |   |  |  |

|       | operation      | operation                                                                                                 | opera                                                                                                                                                                                                                                                                                                                                                  | tion | operation  | 1 |  |  |

Example: HERE RCALL Jump

Before Instruction

PC = Address (HERE)

After Instruction

PC = Address (Jump) TOS = Address (HERE + 2)

| RES   | ET             | Reset |                                                                      |           |    |          |  |  |  |

|-------|----------------|-------|----------------------------------------------------------------------|-----------|----|----------|--|--|--|

| Synta | ax:            | RESET | RESET                                                                |           |    |          |  |  |  |

| Oper  | ands:          | None  |                                                                      |           |    |          |  |  |  |

| Oper  | ation:         |       | Reset all registers and flags that are affected by a MCLR Reset.     |           |    |          |  |  |  |

| Statu | s Affected:    | All   | All                                                                  |           |    |          |  |  |  |

| Enco  | ding:          | 0000  | 0000                                                                 | 0000 1111 |    | 1111     |  |  |  |

| Desc  | ription:       |       | This instruction provides a way to execute a MCLR Reset by software. |           |    |          |  |  |  |

| Word  | ls:            | 1     | 1                                                                    |           |    |          |  |  |  |

| Cycle | es:            | 1     | 1                                                                    |           |    |          |  |  |  |

| QC    | ycle Activity: |       |                                                                      |           |    |          |  |  |  |

|       | Q1             | Q2    | Q3                                                                   | Q3        |    | Q4       |  |  |  |

|       | Decode         | Start | No                                                                   |           | No |          |  |  |  |

|       |                | Reset | opera                                                                | tion      | op | peration |  |  |  |

Example:

After Instruction

| Registers = | Reset Value |

|-------------|-------------|

| Flags* =    | Reset Value |

RESET

© 2016-2017 Microchip Technology Inc.

| Standard Operating Conditions (unless otherwise stated) |                    |                                             |            |          |        |       |                                                                                                                 |

|---------------------------------------------------------|--------------------|---------------------------------------------|------------|----------|--------|-------|-----------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                            | Sym.               | Characteristic                              | Min.       | Тур†     | Max.   | Units | Conditions                                                                                                      |

| Data EE                                                 | PROM Me            | mory Specifications                         |            | •        |        |       | •                                                                                                               |

| MEM20                                                   | ED                 | DataEE Byte Endurance                       | 100k       | _        | _      | E/W   | $-40^\circ C \leq T_A \leq +85^\circ C$                                                                         |

| MEM21                                                   | T <sub>D_RET</sub> | Characteristic Retention                    | _          | 40       | _      | Year  | Provided no other specifications are violated                                                                   |

| MEM22                                                   | N <sub>D_REF</sub> | Total Erase/Write Cycles before Refresh     | 1M<br>500k | 10M<br>— | _      | E/W   | $\begin{array}{l} -40^{\circ}C \leq TA \leq +60^{\circ}C \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \end{array}$ |

| MEM23                                                   | V <sub>D_RW</sub>  | VDD for Read or Erase/Write operation       | VDDMIN     | _        | VDDMAX | V     |                                                                                                                 |

| MEM24                                                   | T <sub>D_BEW</sub> | Byte Erase and Write Cycle Time             | _          | 4.0      | 5.0    | ms    |                                                                                                                 |

| Program                                                 | n Flash Me         | emory Specifications                        |            |          | •      |       | •                                                                                                               |

| MEM30                                                   | E <sub>P</sub>     | Flash Memory Cell Endurance                 | 10k        | _        | _      | E/W   | -40°C ≤ TA ≤ +85°C<br>(Note 1)                                                                                  |

| MEM32                                                   | T <sub>P_RET</sub> | Characteristic Retention                    | _          | 40       | _      | Year  | Provided no other specifications are violated                                                                   |

| MEM33                                                   | V <sub>P_RD</sub>  | VDD for Read operation                      | VDDMIN     | _        | VDDMAX | V     |                                                                                                                 |

| MEM34                                                   | V <sub>P_REW</sub> | VDD for Row Erase or Write operation        | VDDMIN     | _        | VDDMAX | V     |                                                                                                                 |

| MEM35                                                   | T <sub>P_REW</sub> | Self-Timed Row Erase or Self-Timed<br>Write | _          | 2.0      | 2.5    | ms    |                                                                                                                 |

# TABLE 37-5: MEMORY PROGRAMMING SPECIFICATIONS

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Flash Memory Cell Endurance for the Flash memory is defined as: One Row Erase operation and one Self-Timed Write.

| Standard Operating Conditions (unless otherwise stated) |                       |                                                                       |              |      |      |       |                                  |  |

|---------------------------------------------------------|-----------------------|-----------------------------------------------------------------------|--------------|------|------|-------|----------------------------------|--|

| Param<br>No.                                            | Symbol                | Characteristic                                                        | Min.         | Тур† | Max. | Units | Conditions                       |  |

| SP70*                                                   | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | 2.25*Tcy     | —    | _    | ns    |                                  |  |

| SP71*                                                   | TscH                  | SCK input high time (Slave mode)                                      | Tcy + 20     |      | _    | ns    |                                  |  |

| SP72*                                                   | TscL                  | SCK input low time (Slave mode)                                       | Tcy + 20     | _    | _    | ns    |                                  |  |

| SP73*                                                   | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to SCK edge                              | 100          | —    | —    | ns    |                                  |  |

| SP74*                                                   | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               | 100          | —    | —    | ns    |                                  |  |

| SP75*                                                   | TDOR                  | SDO data output rise time                                             |              | 10   | 25   | ns    | $3.0V \le V\text{DD} \le 5.5V$   |  |

|                                                         |                       |                                                                       |              | 25   | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |  |

| SP76*                                                   | TDOF                  | SDO data output fall time                                             |              | 10   | 25   | ns    |                                  |  |

| SP77*                                                   | TssH2doZ              | SS↑ to SDO output high-impedance                                      | 10           |      | 50   | ns    |                                  |  |

| SP78*                                                   | TscR                  | SCK output rise time                                                  | _            | 10   | 25   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |  |

|                                                         |                       | (Master mode)                                                         |              | 25   | 50   | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |  |

| SP79*                                                   | TSCF                  | SCK output fall time (Master mode)                                    |              | 10   | 25   | ns    |                                  |  |

| SP80*                                                   | TscH2doV,             | SDO data output valid after SCK edge                                  |              |      | 50   | ns    | $3.0V \leq V\text{DD} \leq 5.5V$ |  |

|                                                         | TscL2DoV              |                                                                       |              |      | 145  | ns    | $1.8V \leq V\text{DD} \leq 5.5V$ |  |

| SP81*                                                   | TDOV2scH,<br>TDOV2scL | SDO data output setup to SCK edge                                     | 1 Tcy        | —    | —    | ns    |                                  |  |

| SP82*                                                   | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edge            |              | _    | 50   | ns    |                                  |  |

| SP83*                                                   | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   | 1.5 Tcy + 40 | —    | —    | ns    |                                  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

# 38.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

Graphs and tables are not available at this time.

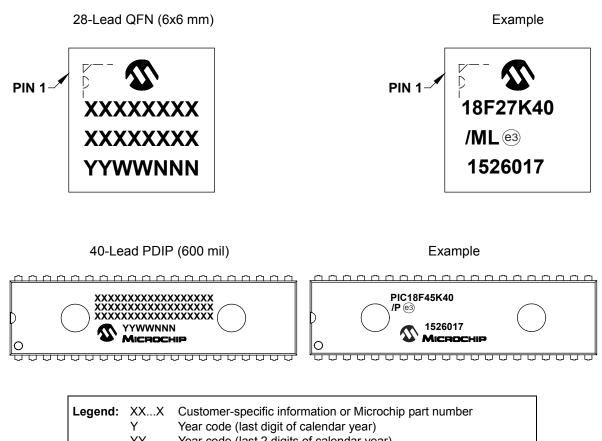

# Package Marking Information (Continued)

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>©3<br>*                                                                                                                                                                      | Customer-specific information or Microchip part number<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                                                      |

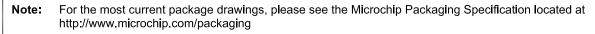

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

Microchip Technology Drawing C04-105C Sheet 1 of 2