#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27k40-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                 | Bit 7  | Bit 6                | Bit 5      | Bit 4  | Bit 3      | Bit 2   | Bit 1       | Bit 0                    | Register on<br>Page |  |

|----------------------|--------|----------------------|------------|--------|------------|---------|-------------|--------------------------|---------------------|--|

| INTCON               | GIE    | PEIE                 | —          | —      | —          | —       | —           | INTEDG                   | 170                 |  |

| PIE0                 | _      | —                    | TMR0IE     | IOCIE  | —          | INT2IE  | INT1IE      | INTOIE                   | 179                 |  |

| PIE1                 | OSCFIE | CSWIE                | —          | —      | —          | —       | ADTIE       | ADIE                     | 180                 |  |

| PIE2                 | HLVDIE | ZCDIE                | —          | —      | —          | —       | C2IE        | C1IE                     | 181                 |  |

| PIE3                 | RC2IE  | TX2IE                | RC1IE      | TX1IE  | BCL2IE     | SSP2IE  | BCL1IE      | SSP1IE                   | 182                 |  |

| PIE4                 | —      | —                    | TMR6IE     | TMR5IE | TMR4IE     | TMR3IE  | TMR2IE      | TMR1IE                   | 183                 |  |

| PIE5                 | _      | _                    | _          | _      | _          | TMR5GIE | TMR3GIE     | TMR1GIE                  | 184                 |  |

| PIE6                 | _      | —                    | —          | —      | —          | —       | CCP2IE      | CCP1IE                   | 185                 |  |

| PIE7                 | SCANIE | CRCIE                | NVMIE      | —      | —          | —       | —           | CWG1IE                   | 186                 |  |

| PIR0                 | _      | _                    | TMR0IF     | IOCIF  | —          | INT2IF  | INT1IF      | INT0IF                   | 171                 |  |

| PIR1                 | OSCFIF | CSWIF                | —          | —      | —          | —       | ADTIF       | ADIF                     | 172                 |  |

| PIR2                 | HLVDIF | ZCDIF <sup>(1)</sup> | _          | _      | _          | _       | C2IF        | C1IF                     | 173                 |  |

| PIR3                 | RC2IF  | TX2IF                | RC1IF      | TX1IF  | BCL2IF     | SSP2IF  | BCL1IF      | SSP1IF                   | 174                 |  |

| PIR4                 | _      | —                    | TMR6IF     | TMR5IF | TMR4IF     | TMR3IF  | TMR2IF      | TMR1IF                   | 174                 |  |

| IOCAP                | _      | —                    | IOCAP5     | IOCAP4 | IOCAP3     | IOCAP2  | IOCAP1      | IOCAP0                   | 211                 |  |

| IOCAN                | _      | —                    | IOCAN5     | IOCAN4 | IOCAN3     | IOCAN2  | IOCAN1      | IOCAN0                   | 211                 |  |

| IOCAF                | _      | —                    | IOCAF5     | IOCAF4 | IOCAF3     | IOCAF2  | IOCAF1      | IOCAF0                   | 211                 |  |

| IOCCP <sup>(1)</sup> | _      | —                    | IOCCP5     | IOCCP4 | IOCCP3     | IOCCP2  | IOCCP1      | IOCCP0                   | 211                 |  |

| IOCCN <sup>(1)</sup> | _      | —                    | IOCCN5     | IOCCN4 | IOCCN3     | IOCCN2  | IOCCN1      | IOCCN0                   | 211                 |  |

| IOCCF <sup>(1)</sup> | _      | —                    | IOCCF5     | IOCCF4 | IOCCF3     | IOCCF2  | IOCCF1      | IOCCF0                   | 211                 |  |

| STATUS               | _      | —                    | —          | TO     | PD         | Z       | DC          | С                        | 118                 |  |

| VREGCON              | _      | —                    | _          | —      | —          | —       | VREGPM      | Reserved                 | 64                  |  |

| CPUDOZE              | IDLEN  | DOZEN                | ROI        | DOE    | —          |         | DOZE<2:0>   |                          | 65                  |  |

| WDTCON0              | —      | —                    |            |        | WDTPS<4:0> |         |             | SEN                      | 85                  |  |

| WDTCON1              | _      |                      | WDTPS<2:0> |        | _          |         | WINDOW<2:0> | WDTPS<2:0> — WINDOW<2:0> |                     |  |

TABLE 6-1:

SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

#### 10.4.5 STATUS REGISTER

The STATUS register, shown in Register 10-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the STATUS register is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu').

It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in **Section 35.0 "Instruction Set Summary"** and Table 35-3.

Note: The <u>C</u> and <u>DC</u> bits operate as the borrow and digit borrow bits, respectively, in subtraction.

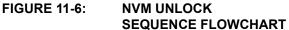

#### 11.1.4 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- Write of PFM write latches to PFM memory

- Write of PFM write latches to User IDs

- Write to Data EEPROM Memory

- · Write to Configuration Words

The unlock sequence consists of the following steps and must be completed in order:

- Write 55h to NVMCON2

- Write AAh to NMVCON2

- · Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

| BCF     | INTCON, GIE                                              | ; Recommended so sequence is not interrupted                     |

|---------|----------------------------------------------------------|------------------------------------------------------------------|

| BANKSEL | NVMCON1                                                  |                                                                  |

| BSF     | NVMCON1, WREN                                            | ; Enable write/erase                                             |

| MOVLW   | 55h                                                      | ; Load 55h                                                       |

|         |                                                          |                                                                  |

| MOVWF   | NVMCON2                                                  | ; Step 1: Load 55h into NVMCON2                                  |

| MOVLW   | AAh                                                      | ; Step 2: Load W with AAh                                        |

| MOVWF   | NVMCON2                                                  | ; Step 3: Load AAh into NVMCON2                                  |

| BSF     | INTCON1,WR                                               | ; Step 4: Set WR bit to begin write/erase                        |

|         |                                                          |                                                                  |

| BSF     | INTCON, GIE                                              | ; Re-enable interrupts                                           |

|         |                                                          |                                                                  |

| Note 1: | Sequence begins when NVMCO                               | N2 is written; steps 1-4 must occur in the cycle-accurate order  |

|         | shown. If the timing of the steps 1 will not take place. | to 4 is corrupted by an interrupt or a debugger Halt, the action |

| 2:      | Opcodes shown are illustrative; a                        | any instruction that has the indicated effect may be used.       |

|         | -                                                        |                                                                  |

|         |                                                          |                                                                  |

#### EXAMPLE 11-2: NVM UNLOCK SEQUENCE

### 11.3 Data EEPROM Memory

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, which is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Four SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- NVMCON1

- NVMCON2

- NVMDAT

- NVMADRL

- NVMADRH

The data EEPROM allows byte read and write. When interfacing to the data memory block, NVMDAT holds the 8-bit data for read/write and the NVMADRH:NVMADRL register pair hold the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an internal programming timer; it will vary with voltage and temperature as well as from chip-to-chip. Please refer to the Data EEPROM Memory parameters in **Section 37.0 "Electrical Specifications"** for limits.

#### 11.3.1 NVMADRL AND NVMADRH REGISTERS

The NVMADRH:NVMADRL registers are used to address the data EEPROM for read and write operations.

#### 11.3.2 NVMCON1 AND NVMCON2 REGISTERS

Access to the data EEPROM is controlled by two registers: NVMCON1 and NVMCON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The NVMCON1 register (Register 11-1) is the control register for data and program memory access. Control bits NVMREG<1:0> determine if the access will be to program, Data EEPROM Memory or the User IDs, Configuration bits, Revision ID and Device ID.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

The WR control bit initiates write operations. The bit can be set but not cleared by software. It is cleared only by hardware at the completion of the write operation.

The NVMIF interrupt flag bit of the PIR7 register is set when the write is complete. It must be cleared by software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (NVMREG<1:0> = 0x10). Program memory is read using table read instructions. See **Section 11.1.1 "Table Reads and Table Writes"** regarding table reads.

#### REGISTER 13-9: CRCXORH: CRC XOR HIGH BYTE REGISTER

| R/W-x/x         | R/W-x/x  | R/W-x/x            | R/W-x/x | R/W-x/x                                    | R/W-x/x          | R/W-x/x  | R/W-x/x      |

|-----------------|----------|--------------------|---------|--------------------------------------------|------------------|----------|--------------|

| r////x          | r///-x/x | r///-x/x           | r////x  | K/ VV-X/ X                                 | K/ VV-X/X        | r///*//X | FX/ V V-X/ X |

|                 |          |                    | X<1     | 5:8>                                       |                  |          |              |

| bit 7           |          |                    |         |                                            |                  |          | bit 0        |

|                 |          |                    |         |                                            |                  |          |              |

| Legend:         |          |                    |         |                                            |                  |          |              |

| R = Readable    | bit      | W = Writable       | bit     | U = Unimpler                               | nented bit, read | l as '0' |              |

| u = Bit is unch | anged    | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all o |                  |          | ther Resets  |

bit 7-0 X<15:8>: XOR of Polynomial Term XN Enable bits

#### REGISTER 13-10: CRCXORL: CRC XOR LOW BYTE REGISTER

'0' = Bit is cleared

| R/W-x/x | U-1   |

|---------|---------|---------|---------|---------|---------|---------|-------|

|         |         |         | X<7:1>  |         |         |         |       |

| bit 7   |         |         |         |         |         |         | bit 0 |

|         |         |         |         |         |         |         |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 X<7:1>: XOR of Polynomial Term XN Enable bits

bit 0 Unimplemented: Read as '1'

'1' = Bit is set

#### 18.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the T016BIT bit of the T0CON register.

#### 18.1.1 16-BIT MODE

The register pair TMR0H:TMR0L, increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

### 18.1.1.1 Timer0 Reads and Writes in 16-Bit Mode

In 16-bit mode, to avoid rollover between reading high and low registers, the TMR0H register is a buffered copy of the actual high byte of Timer0, which is neither directly readable nor writable (see Figure 18-1). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte was valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### 18.1.2 8-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

In 8-bit mode, the value of TMR0L is compared to that of the Period buffer, a copy of TMR0H, on each clock cycle. When the two values match, the following events happen:

- TMR0\_out goes high for one prescaled clock period

- TMR0L is reset

- The contents of TMR0H are copied to the period buffer

In 8-bit mode, the TMR0L and TMR0H registers are both directly readable and writable. The TMR0L register is cleared on any device Reset, while the TMR0H register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- Any device Reset Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or

- Brown-out Reset (BOR)

#### 18.1.3 COUNTER MODE

In Counter mode, the prescaler is normally disabled by setting the T0CKPS bits of the T0CON1 register to '0000'. Each rising edge of the clock input (or the output of the prescaler if the prescaler is used) increments the counter by '1'.

#### 18.1.4 TIMER MODE

In Timer mode, the Timer0 module will increment every instruction cycle as long as there is a valid clock signal and the T0CKPS bits of the T0CON1 register (Register 18-2) are set to '0000'. When a prescaler is added, the timer will increment at the rate based on the prescaler value.

#### 18.1.5 ASYNCHRONOUS MODE

When the TOASYNC bit of the TOCON1 register is set (TOASYNC = '1'), the counter increments with each rising edge of the input source (or output of the prescaler, if used). Asynchronous mode allows the counter to continue operation during Sleep mode provided that the clock also continues to operate during Sleep.

#### 18.1.6 SYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is clear (T0ASYNC = 0), the counter clock is synchronized to the system clock (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

#### 18.2 Clock Source Selection

The T0CS<2:0> bits of the T0CON1 register are used to select the clock source for Timer0. Register 18-2 displays the clock source selections.

#### 18.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, Timer0 operates as a timer and will increment on multiples of the clock source, as determined by the Timer0 prescaler.

#### 18.2.2 EXTERNAL CLOCK SOURCE

When an external clock source is selected, Timer0 can operate as either a timer or a counter. Timer0 will increment on multiples of the rising edge of the external clock source, as determined by the Timer0 prescaler.

#### REGISTER 21-3: CCPxCAP: CAPTURE INPUT SELECTION MULTIPLEXER REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/x | R/W-0/x |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | _   | _   |     | CTS<    | <1:0>   |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-2 Unimplemented: Read as '0'

bit 1-0 CTS<1:0>: Capture Trigger Input Selection bits

| CTS<1:0> | Connection              |                         |  |  |  |

|----------|-------------------------|-------------------------|--|--|--|

| 013<1.02 | CCP1                    | CCP2                    |  |  |  |

| 11       |                         | IOC_Interrupt           |  |  |  |

| 10       |                         | CMP2_output             |  |  |  |

| 01       |                         | CMP1_output             |  |  |  |

| 00       | Pin selected by CCP1PPS | Pin selected by CCP2PPS |  |  |  |

#### REGISTER 21-4: CCPRxL: CCPx REGISTER LOW BYTE

| R/W-x/x    | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|------------|---------|---------|---------|---------|---------|---------|---------|

| CCPRx<7:0> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-0 | MODE = Capture Mode:                           |

|---------|------------------------------------------------|

|         | CCPRxL<7:0>: LSB of captured TMR1 value        |

|         | MODE = Compare Mode:                           |

|         | CCPRxL<7:0>: LSB compared to TMR1 value        |

|         | MODE = PWM Mode && FMT = 0:                    |

|         | CCPRxL<7:0>: CCPW<7:0> - Pulse-Width LS 8 bits |

|         | MODE = PWM Mode && FMT = 1:                    |

|         | CCPRxL<7:6>: CCPW<1:0> - Pulse-Width LS 2 bits |

|         | CCPRxL<5:0>: Not used                          |

© 2016-2017 Microchip Technology Inc.

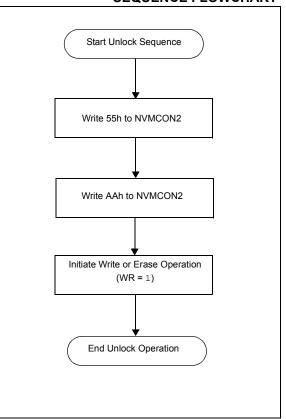

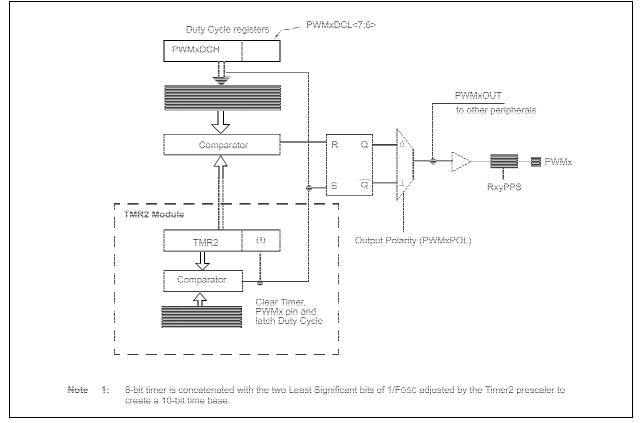

### 22.0 PULSE-WIDTH MODULATION (PWM)

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PRx

- TxCON

- PWMxDCH

- PWMxDCL

- PWMxCON

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin. Each PWM module can select the timer source that controls the module. Each module has an independent timer selection which can be accessed using the CCPTMRS register (Register 21-2). Please note that the PWM mode operation is described with respect to TMR2 in the following sections.

Figure 22-1 shows a simplified block diagram of PWM operation.

Figure 22-2 shows a typical waveform of the PWM signal.

### FIGURE 22-1: SIMPLIFIED PWM BLOCK DIAGRAM

FIGURE 22-2:

PWM OUTPUT

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 22.1.9 "Setup for PWM Operation using PWMx Pins".

| Name      | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3        | Bit 2      | Bit 1 | Bit 0  | Register<br>on Page |

|-----------|-------|-------|-------|--------|--------------|------------|-------|--------|---------------------|

| MDCON0    | EN    | _     | OUT   | OPOL   | —            | —          | —     | BIT    | 325                 |

| MDCON1    | —     |       | CHPOL | CHSYNC | _            | _          | CLPOL | CLSYNC | 326                 |

| MDCARH    | _     | —     | —     | _      | — — CHS<2:0> |            |       |        | 327                 |

| MDCARL    | —     | _     | _     | _      | CLS<2:0>     |            |       |        | 327                 |

| MDSRC     | _     | —     | —     | _      | — SRCS<3:0>  |            |       |        | 328                 |

| MDCARLPPS | _     | —     | —     |        | С            | ARLPPS<4:( | )>    |        | 216                 |

| MDCARHPPS | —     |       |       |        | С            | ARHPPS<4:  | )>    |        | 216                 |

| MDSRCPPS  | —     |       | _     |        | 5            | SRCPPS<4:0 | >     |        | 216                 |

| RxyPPS    | _     |       |       |        |              | RxyPPS<4:0 | >     |        | 218                 |

| PMD5      | _     | _     | _     |        | _            | _          | _     | DSMMD  | 73                  |

#### TABLE 25-4: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MODE

Legend: — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

© 2016-2017 Microchip Technology Inc

|        |                                     | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                   |            |                             |                    |            |                             |                |            |                             |

|--------|-------------------------------------|------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz Fosc = 20.000 MHz |                                                      |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |                |            |                             |

| RATE   | Actual<br>Rate                      | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                               | 0.00                                                 | 26666                       | 300.0             | 0.00       | 16665                       | 300.0              | 0.00       | 15359                       | 300.0          | 0.00       | 9215                        |

| 1200   | 1200                                | 0.00                                                 | 6666                        | 1200              | -0.01      | 4166                        | 1200               | 0.00       | 3839                        | 1200           | 0.00       | 2303                        |

| 2400   | 2400                                | 0.01                                                 | 3332                        | 2400              | 0.02       | 2082                        | 2400               | 0.00       | 1919                        | 2400           | 0.00       | 1151                        |

| 9600   | 9604                                | 0.04                                                 | 832                         | 9597              | -0.03      | 520                         | 9600               | 0.00       | 479                         | 9600           | 0.00       | 287                         |

| 10417  | 10417                               | 0.00                                                 | 767                         | 10417             | 0.00       | 479                         | 10425              | 0.08       | 441                         | 10433          | 0.16       | 264                         |

| 19.2k  | 19.18k                              | -0.08                                                | 416                         | 19.23k            | 0.16       | 259                         | 19.20k             | 0.00       | 239                         | 19.20k         | 0.00       | 143                         |

| 57.6k  | 57.55k                              | -0.08                                                | 138                         | 57.47k            | -0.22      | 86                          | 57.60k             | 0.00       | 79                          | 57.60k         | 0.00       | 47                          |

| 115.2k | 115.9k                              | 0.64                                                 | 68                          | 116.3k            | 0.94       | 42                          | 115.2k             | 0.00       | 39                          | 115.2k         | 0.00       | 23                          |

### TABLE 27-5: SAMPLE BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                     |            |                             |                   |            |                             |                  |            |                             |

|--------|----------------|------------------------------------------------------|-----------------------------|---------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000                                            | ) MHz                       | Hz Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate      | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00                                                 | 6666                        | 300.0               | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200           | -0.02                                                | 1666                        | 1200                | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1202             | 0.16       | 207                         |

| 2400   | 2401           | 0.04                                                 | 832                         | 2398                | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 103                         |

| 9600   | 9615           | 0.16                                                 | 207                         | 9615                | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 25                          |

| 10417  | 10417          | 0                                                    | 191                         | 10417               | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k         | 0.16                                                 | 103                         | 19.23k              | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 57.14k         | -0.79                                                | 34                          | 58.82k              | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | _                | _          | _                           |

| 115.2k | 117.6k         | 2.12                                                 | 16                          | 111.1k              | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | _                | —          | —                           |

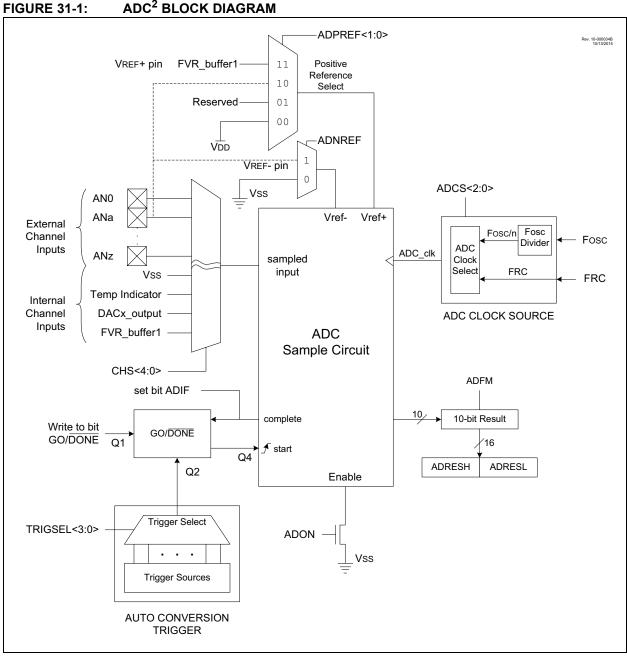

ADC<sup>2</sup> BLOCK DIAGRAM

| U-0                                     | U-0                                                             | U-0                                          | R/W-0/0          | R/W-0/0       | R/W-0/0            | R/W-0/0 | R/W-0/0 |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------|----------------------------------------------|------------------|---------------|--------------------|---------|---------|--|--|--|

| —                                       | —                                                               | —                                            |                  |               | ADACT<4:0>         |         |         |  |  |  |

| oit 7                                   |                                                                 |                                              |                  |               |                    |         | bit     |  |  |  |

|                                         |                                                                 |                                              |                  |               |                    |         |         |  |  |  |

| Legend:                                 |                                                                 |                                              |                  |               |                    |         |         |  |  |  |

| R = Readab                              | le bit                                                          | W = Writable b                               | oit              | U = Unimpleme | ented bit, read as | s 'O'   |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                                                                 | own                                          | -n/n = Value at  | POR and BOR/  | /alue at all other | Resets  |         |  |  |  |

| '1' = Bit is set '0' = Bit is cleared   |                                                                 | red                                          |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 |                                              |                  |               |                    |         |         |  |  |  |

| bit 7-5                                 | Unimpleme                                                       | Unimplemented: Read as '0'                   |                  |               |                    |         |         |  |  |  |

| bit 4-0                                 | ADACT<4:0                                                       | >: Auto-Conversio                            | n Trigger Select | Bits          |                    |         |         |  |  |  |

|                                         |                                                                 | oftware write to ADF                         |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 | served, do not use                           |                  |               |                    |         |         |  |  |  |

|                                         | 11101 = Software read of ADRESH                                 |                                              |                  |               |                    |         |         |  |  |  |

|                                         | 11100 = Software read of ADERRH<br>11011 = Reserved, do not use |                                              |                  |               |                    |         |         |  |  |  |

|                                         | 11011 <b>- Re</b>                                               | served, do not use                           |                  |               |                    |         |         |  |  |  |

|                                         | •                                                               |                                              |                  |               |                    |         |         |  |  |  |

|                                         | •                                                               |                                              |                  |               |                    |         |         |  |  |  |

|                                         | 10000 <b>= Re</b>                                               | eserved, do not use                          |                  |               |                    |         |         |  |  |  |

|                                         | 01111 = Int                                                     | errupt-on-change I                           | nterrupt Flag    |               |                    |         |         |  |  |  |

|                                         | 01110 <b>= C2</b>                                               | —                                            |                  |               |                    |         |         |  |  |  |

|                                         | 01101 <b>= C1</b>                                               | —                                            |                  |               |                    |         |         |  |  |  |

|                                         | 01100 = PV                                                      |                                              |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 | 01011 = PWM3_out                             |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 | 01010 = CCP2_trigger<br>01001 = CCP1 trigger |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 | /R6_postscaled                               |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 | /R5_overflow                                 |                  |               |                    |         |         |  |  |  |

| 00110 = TMR4_postscaled                 |                                                                 |                                              |                  |               |                    |         |         |  |  |  |

|                                         | 00101 = TMR3_overflow                                           |                                              |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 | IR2_postscaled                               |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 | IR1_overflow                                 |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 | IR0_overflow                                 |                  |               |                    |         |         |  |  |  |

|                                         |                                                                 | n selected by ADA(<br>ternal Trigger Disa    |                  |               |                    |         |         |  |  |  |

|                                         | 00000 <b>- EX</b>                                               | liemai myyei Disa                            | lieu             |               |                    |         |         |  |  |  |

#### REGISTER 31-32: ADACT: ADC AUTO CONVERSION TRIGGER CONTROL REGISTER

| BRA   | BRA Unconditional Branch                               |                                                                                                                                                                                                               |                                          |             |  |  |  |  |

|-------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------|--|--|--|--|

| Synta | ax:                                                    | BRA n                                                                                                                                                                                                         |                                          |             |  |  |  |  |

| Oper  | ands:                                                  | $-1024 \le n \le 1023$                                                                                                                                                                                        |                                          |             |  |  |  |  |

| Oper  | ation:                                                 | (PC) + 2 + 2n                                                                                                                                                                                                 | $\rightarrow$ PC                         |             |  |  |  |  |

| Statu | s Affected:                                            | None                                                                                                                                                                                                          |                                          |             |  |  |  |  |

| Enco  | ding:                                                  | 1101 (                                                                                                                                                                                                        | )nnn nnni                                | n nnnn      |  |  |  |  |

| Desc  | ription:                                               | Add the 2's complement number '2n' to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction, the<br>new address will be PC + 2 + 2n. This<br>instruction is a 2-cycle instruction. |                                          |             |  |  |  |  |

| Word  | ls:                                                    | 1                                                                                                                                                                                                             |                                          |             |  |  |  |  |

| Cycle | es:                                                    | 2                                                                                                                                                                                                             |                                          |             |  |  |  |  |

| QC    | ycle Activity:                                         |                                                                                                                                                                                                               |                                          |             |  |  |  |  |

|       | Q1                                                     | Q2                                                                                                                                                                                                            | Q3                                       | Q4          |  |  |  |  |

|       | Decode                                                 | Read literal<br>'n'                                                                                                                                                                                           | Process<br>Data                          | Write to PC |  |  |  |  |

|       | No                                                     | No                                                                                                                                                                                                            | No                                       | No          |  |  |  |  |

|       | operation                                              | operation                                                                                                                                                                                                     | operation                                | operation   |  |  |  |  |

|       | nple:<br>Before Instruc<br>PC<br>After Instructi<br>PC | = ad                                                                                                                                                                                                          | BRA Jump<br>dress (HERE)<br>dress (Jump) |             |  |  |  |  |

| BSF                                                                         | Bit Set f                                                                                                                                                                                                                                                                                                                                                                                                                         |                           |      |                     |  |  |  |  |  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|---------------------|--|--|--|--|--|

| Syntax:                                                                     | BSF f, b {                                                                                                                                                                                                                                                                                                                                                                                                                        | ,a}                       |      |                     |  |  |  |  |  |

| Operands:                                                                   | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                |                           |      |                     |  |  |  |  |  |

| Operation:                                                                  | $1 \rightarrow f \le b >$                                                                                                                                                                                                                                                                                                                                                                                                         | $1 \rightarrow f \le b >$ |      |                     |  |  |  |  |  |

| Status Affected:                                                            | None                                                                                                                                                                                                                                                                                                                                                                                                                              | None                      |      |                     |  |  |  |  |  |

| Encoding:                                                                   | 1000                                                                                                                                                                                                                                                                                                                                                                                                                              | bbba f:                   | Eff  | ffff                |  |  |  |  |  |

| Description:                                                                | Bit 'b' in register 'f' is set.<br>If 'a' is '0', the Access Bank is selecte<br>If 'a' is '1', the BSR is used to select th<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See See<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Li<br>eral Offset Mode" for details. |                           |      |                     |  |  |  |  |  |

| Words:                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           |      |                     |  |  |  |  |  |

| Cycles:                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           |      |                     |  |  |  |  |  |

| Q Cycle Activity:                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |      |                     |  |  |  |  |  |

| Q1                                                                          | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                | Q3                        |      | Q4                  |  |  |  |  |  |

| Decode                                                                      | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                              | Process<br>Data           | re   | Write<br>gister 'f' |  |  |  |  |  |

| Example:                                                                    | BSF F                                                                                                                                                                                                                                                                                                                                                                                                                             | LAG_REG,                  | 7, 1 |                     |  |  |  |  |  |

| Before Instruction<br>FLAG_REG = 0Ah<br>After Instruction<br>FLAG_REG = 8Ah |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |      |                     |  |  |  |  |  |

|                                                   | Complem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |            |                        |  |  |  |  |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------|------------------------|--|--|--|--|

| Syntax:                                           | COMF f {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | {,d {,a}}                         |            |                        |  |  |  |  |

| Operands:                                         | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | d ∈ [0,1]                         |            |                        |  |  |  |  |

| Operation:                                        | $(\overline{f}) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $(\overline{f}) \rightarrow dest$ |            |                        |  |  |  |  |

| Status Affected:                                  | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                   |            |                        |  |  |  |  |

| Encoding:                                         | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11da                              | ffff       | ffff                   |  |  |  |  |

|                                                   | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |                                   |            |                        |  |  |  |  |

| Words:                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mode                              | or actails |                        |  |  |  |  |

| Cycles:                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |            |                        |  |  |  |  |

| Q Cycle Activity:                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   |            |                        |  |  |  |  |

| Q1                                                | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Q3                                |            | Q4                     |  |  |  |  |

| Decode                                            | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Proce<br>Data                     |            | Write to<br>estination |  |  |  |  |

| Example:                                          | COMF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REG,                              | 0, 0       |                        |  |  |  |  |

| Before Instruct<br>REG<br>After Instructio<br>REG | = 13h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |            |                        |  |  |  |  |

| CPFSEQ                     | Compare                  | f with W, sk                                                             | ip if f = W     |  |  |  |  |  |

|----------------------------|--------------------------|--------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Syntax:                    | CPFSEQ                   | f {,a}                                                                   |                 |  |  |  |  |  |

| Operands:                  | 0 ≤ f ≤ 255<br>a ∈ [0,1] |                                                                          |                 |  |  |  |  |  |

| Operation:                 |                          | (f) – (W),                                                               |                 |  |  |  |  |  |

|                            | skip if $(f) = (f)$      | skip if (f) = (W)                                                        |                 |  |  |  |  |  |

|                            | . –                      | comparison)                                                              |                 |  |  |  |  |  |

| Status Affected:           | None                     |                                                                          |                 |  |  |  |  |  |

| Encoding:                  | 0110                     | 001a fff                                                                 |                 |  |  |  |  |  |

| Description:               |                          | Compares the contents of data memory                                     |                 |  |  |  |  |  |

|                            |                          | location 'f' to the contents of W by performing an unsigned subtraction. |                 |  |  |  |  |  |

|                            |                          | en the fetched                                                           |                 |  |  |  |  |  |

|                            |                          | nd a NOP is ex<br>king this a 2-c                                        |                 |  |  |  |  |  |

|                            | instruction.             |                                                                          | yolo            |  |  |  |  |  |

|                            |                          | he Access Bar                                                            |                 |  |  |  |  |  |

|                            | GPR bank.                | he BSR is used                                                           | d to select the |  |  |  |  |  |

|                            |                          | nd the extende                                                           | ed instruction  |  |  |  |  |  |

|                            |                          | ed, this instruc                                                         |                 |  |  |  |  |  |

|                            |                          | Literal Offset A<br>ever f ≤ 95 (5F                                      |                 |  |  |  |  |  |

|                            |                          | "Byte-Oriente                                                            |                 |  |  |  |  |  |

|                            | Oriented In              | Oriented Instructions in Indexed Literal Offset Mode" for details.       |                 |  |  |  |  |  |

|                            |                          | Mode" for det                                                            | ails.           |  |  |  |  |  |

| Words:                     | 1                        |                                                                          |                 |  |  |  |  |  |

| Cycles:                    | 1(2)<br>Note: 3 cv       | cles if skip an                                                          | d followed      |  |  |  |  |  |

|                            |                          | a 2-word instru                                                          |                 |  |  |  |  |  |

| Q Cycle Activity:          |                          |                                                                          |                 |  |  |  |  |  |

| Q1                         | Q2                       | Q3                                                                       | Q4              |  |  |  |  |  |

| Decode                     | Read                     | Process                                                                  | No              |  |  |  |  |  |

| lf skip:                   | register 'f'             | Data                                                                     | operation       |  |  |  |  |  |

| Q1                         | Q2                       | Q3                                                                       | Q4              |  |  |  |  |  |

| No                         | No                       | No                                                                       | No              |  |  |  |  |  |

| operation                  | operation                | operation                                                                | operation       |  |  |  |  |  |

| If skip and followed<br>Q1 | •                        | Q3                                                                       | Q4              |  |  |  |  |  |

| No                         | No                       | No                                                                       | No              |  |  |  |  |  |

| operation                  | operation                | operation                                                                | operation       |  |  |  |  |  |

| No<br>operation            | No<br>operation          | No<br>operation                                                          | No<br>operation |  |  |  |  |  |

| L .                        | operation                | operation                                                                | operation       |  |  |  |  |  |

| Example:                   | HERE                     | CPFSEQ REG                                                               | , 0             |  |  |  |  |  |

|                            | NEQUAL<br>EQUAL          | :                                                                        |                 |  |  |  |  |  |

| Before Instruc             |                          |                                                                          |                 |  |  |  |  |  |

| PC Addre                   |                          | RE                                                                       |                 |  |  |  |  |  |

| W                          | = ?                      | = ?                                                                      |                 |  |  |  |  |  |

| REG<br>After Instructic    | = ?                      |                                                                          |                 |  |  |  |  |  |

| If REG                     | = W;                     |                                                                          |                 |  |  |  |  |  |

| PC                         |                          | dress (EQUAI                                                             | L)              |  |  |  |  |  |

| If REG                     | ≠ W;                     |                                                                          |                 |  |  |  |  |  |

| PC                         | = Ad                     | dress (NEQUA                                                             | AL)             |  |  |  |  |  |

| DECF          | sz                    | Decremer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nt f, skip if O                  | )                       | DCFSNZ           | Decrement f, skip if not 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |