## Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 64MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.6K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f47k40-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|               | <u></u>                          |                                                             |             |                  | 301             |                 |       |

|---------------|----------------------------------|-------------------------------------------------------------|-------------|------------------|-----------------|-----------------|-------|

| R/W-1         | R/W-1                            | R/W-1                                                       | U-1         | U-1              | U-1             | R/W-1           | R/W-1 |

| BOF           | REN<1:0>                         | LPBOREN                                                     | _           | _                | _               | PWRTE           | MCLRE |

| bit 7         |                                  |                                                             |             |                  |                 |                 | bit C |

|               |                                  |                                                             |             |                  |                 |                 |       |

| Legend:       |                                  |                                                             |             |                  |                 |                 |       |

| R = Readabl   | e bit                            | W = Writable b                                              | it          | U = Unimple      | mented bit, rea | ad as '1'       |       |

| -n = Value fo | r blank device                   | '1' = Bit is set                                            |             | '0' = Bit is cle | eared           | x = Bit is unki | nown  |

|               |                                  |                                                             |             |                  |                 |                 |       |

| bit 7-6       |                                  | Brown-out Reserved, Brown-out Reserved, Brown-out Reserved. |             |                  | v BORV bit      |                 |       |

|               |                                  | out Reset enabled                                           | •           |                  | ,               |                 |       |

|               |                                  | out Reset enabled                                           |             | 0.               | n Sleep; SBOF   | REN is ignored  |       |

|               |                                  | out Reset enabled                                           |             | to SBOREN        |                 |                 |       |

| =             |                                  | out Reset disable                                           | -           |                  |                 |                 |       |

| bit 5         |                                  | Low-Power BOR E<br>ower Brown-out Re                        |             | blod             |                 |                 |       |

|               |                                  | ower Brown-out Re                                           |             |                  |                 |                 |       |

| bit 4-2       |                                  | nted: Read as '1'                                           |             |                  |                 |                 |       |

| bit 1         | PWRTE: Pov                       | wer-up Timer Enal                                           | ole bit     |                  |                 |                 |       |

|               | 1 = PWRT                         | disabled                                                    |             |                  |                 |                 |       |

|               | 0 = PWRT                         | enabled                                                     |             |                  |                 |                 |       |

| bit 0         |                                  | ster Clear (MCLR)                                           | Enable bit  | t                |                 |                 |       |

|               | <u>If LVP = 1</u>                |                                                             |             |                  |                 |                 |       |

|               | •                                | unction is MCLR                                             |             |                  |                 |                 |       |

|               | $\frac{\text{If LVP} = 0}{1000}$ | <u>-</u> · · <del> </del>                                   |             |                  |                 |                 |       |

|               |                                  | R pin is MCLR                                               |             | <i>c</i>         |                 |                 |       |

|               | 0 = MCL                          | R pin function is p                                         | ort defined | function         |                 |                 |       |

|               |                                  |                                                             |             |                  |                 |                 |       |

#### REGISTER 3-3: Configuration Word 2L (30 0002h): Supervisor

# PIC18(L)F27/47K40

| U-0             | U-0                 | R/W-0/0                                                                 | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|-----------------|---------------------|-------------------------------------------------------------------------|---------|----------------|------------------|----------------|--------------|

| _               | _                   |                                                                         |         | HFTU           | N<5:0>           |                |              |

| bit 7           |                     |                                                                         |         |                |                  |                | bit 0        |

| Legend:         |                     |                                                                         |         |                |                  |                |              |

| R = Readable    | e bit               | W = Writable                                                            | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unc  | hanged              | x = Bit is unkr                                                         | nown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is se | t                   | '0' = Bit is clea                                                       | ared    |                |                  |                |              |

| bit 5-0         | 01 1111 =<br>•<br>• | D>: HFINTOSC F<br>Maximum freque<br>Center frequenc<br>(default value). | ency    | -              | g at the calibra | ted frequency  |              |

## 5.1 Clock Source

The input to the reference clock output can be selected using the CLKRCLK register.

#### 5.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (EN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

## 5.2 Programmable Clock Divider

The module takes the clock input and divides it based on the value of the DIV<2:0> bits of the CLKRCON register (Register 5-1).

The following configurations can be made based on the DIV<2:0> bits:

- · Base Fosc value

- Fosc divided by 2

- Fosc divided by 4

- Fosc divided by 8

- Fosc divided by 16

- · Fosc divided by 32

- Fosc divided by 64

- Fosc divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the DIV<2:0> bits should only be changed when the module is disabled (EN = 0).

## 5.3 Selectable Duty Cycle

The DC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the DC<1:0> bits should only be changed when the module is disabled (EN = 0).

Note: The DC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

## 5.4 Operation in Sleep Mode

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal. No change should occur in the module from entering or exiting from Sleep.

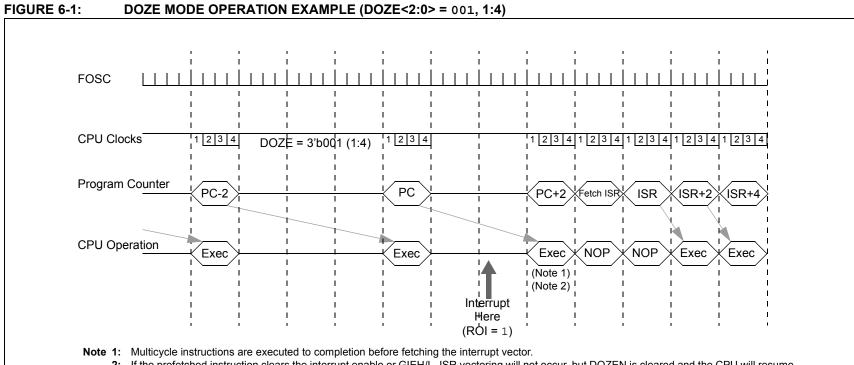

2: If the prefetched instruction clears the interrupt enable or GIEH/L, ISR vectoring will not occur, but DOZEN is cleared and the CPU will resume execution at full speed.

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit         1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore)         0 = Device clock operating         bit 6       CSWIF: Clock-Switch Interrupt Flag bit( <sup>1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt Has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                | R/W-0/0    | ) R/W-0/0            | U-0                   | U-0           | U-0              | U-0              | R/W-0/0          | R/W-0/0         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------|-----------------------|---------------|------------------|------------------|------------------|-----------------|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit       1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore)         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Threshold interrupt Has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Threshold interrupt Has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Interrupt Flag bit         1 = ANC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software) | OSCFIF     | CSWIF <sup>(1)</sup> | —                     | _             | _                | _                | ADTIF            | ADIF            |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit       1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore)         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                  | bit 7      | ·                    |                       |               |                  |                  |                  | bit 0           |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit       1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore)         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold interrupt Flag bit         1 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                  |            |                      |                       |               |                  |                  |                  |                 |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit       1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwork)         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                            | Legend:    |                      |                       |               |                  |                  |                  |                 |

| bit 7       OSCFIF: Oscillator Fail Interrupt Flag bit         1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwork)         0 = Device clock operating         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                            | R = Reada  | ble bit              | W = Writable b        | it            | U = Unimpler     | mented bit, read | d as '0'         |                 |

| <ul> <li>1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore) = Device clock operating</li> <li>bit 6</li> <li>CSWIF: Clock-Switch Interrupt Flag bit<sup>(1)</sup></li> <li>1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started</li> <li>bit 5-2</li> <li>Unimplemented: Read as '0'</li> <li>bit 1</li> <li>ADTIF: ADC Threshold Interrupt Flag bit</li> <li>1 = ADC Threshold interrupt has occurred (must be cleared by software)</li> <li>0 = ADC Threshold event is not complete or has not been started</li> <li>bit 0</li> <li>ADIF: ADC Interrupt Flag bit</li> <li>1 = An A/D conversion completed (must be cleared by software)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -n = Value | at POR               | '1' = Bit is set      |               | '0' = Bit is cle | ared             | x = Bit is unkr  | nown            |

| <ul> <li>1 = Device oscillator failed, clock input has changed to HFINTOSC (must be cleared by softwore) = Device clock operating</li> <li>bit 6</li> <li>CSWIF: Clock-Switch Interrupt Flag bit<sup>(1)</sup></li> <li>1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started</li> <li>bit 5-2</li> <li>Unimplemented: Read as '0'</li> <li>bit 1</li> <li>ADTIF: ADC Threshold Interrupt Flag bit</li> <li>1 = ADC Threshold interrupt has occurred (must be cleared by software)</li> <li>0 = ADC Threshold event is not complete or has not been started</li> <li>bit 0</li> <li>ADIF: ADC Interrupt Flag bit</li> <li>1 = An A/D conversion completed (must be cleared by software)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                      |                       |               |                  |                  |                  |                 |

| 0 = Device clock operating         bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7      | OSCFIF: Osc          | cillator Fail Interro | upt Flag bit  |                  |                  |                  |                 |

| bit 6       CSWIF: Clock-Switch Interrupt Flag bit <sup>(1)</sup> 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold Interrupt Has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | 1 = Device o         | scillator failed, c   | lock input ha | s changed to I   | HFINTOSC (mu     | ist be cleared b | y software)     |

| 1 = New oscillator is ready for switch (must be cleared by software) (see Figure 4-6 and Figure 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold Interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                      |                       |               |                  |                  |                  |                 |

| 0 = New oscillator is not ready for switch or has not been started         bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 6      |                      | -                     | -             |                  |                  |                  |                 |

| bit 5-2       Unimplemented: Read as '0'         bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                      |                       |               |                  |                  | e Figure 4-6 ar  | nd Figure 4-7)  |

| bit 1       ADTIF: ADC Threshold Interrupt Flag bit         1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                      |                       | •             | or has not bee   | n started        |                  |                 |

| 1 = ADC Threshold interrupt has occurred (must be cleared by software)         0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 5-2    | Unimplemen           | ited: Read as '0'     |               |                  |                  |                  |                 |

| 0 = ADC Threshold event is not complete or has not been started         bit 0       ADIF: ADC Interrupt Flag bit         1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 1      |                      |                       |               |                  |                  |                  |                 |

| bit 0 ADIF: ADC Interrupt Flag bit<br>1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                      |                       |               | •                | •                | e)               |                 |

| 1 = An A/D conversion completed (must be cleared by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                      |                       | not complete  | or has not bee   | en started       |                  |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 0      |                      |                       |               |                  |                  |                  |                 |

| 0 = 1  ne A/D conversion is not complete or has not been started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                      | •                     | •             | -                | ,                |                  |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | 0 = 1  ne A/D        | conversion is not     | complete or   | r nas not been   | started          |                  |                 |

| Note 1: The CSWIF interrupt will not wake the system from Sleep. The system will sleep until another i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Note 1:    | The CSWIF inter      | rupt will not wak     | e the systen  | n from Sleep.    | The system wil   | I sleep until an | other interrupt |

## REGISTER 14-3: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

**Note 1:** The CSWIF interrupt will not wake the system from Sleep. The system will sleep until another interrupt causes the wake-up.

| R/W-0/0       | R/W-0/0                     | R/W-0/0              | R-/W0/0           | R/W-0/0           | R/W-0/0 | R/W-0/0         | R/W-0/0 |

|---------------|-----------------------------|----------------------|-------------------|-------------------|---------|-----------------|---------|

| RC2IE         | TX2IE                       | RC1IE                | TX1IE             | BCL2IE            | SSP2IE  | BCL1IE          | SSP1IE  |

| bit 7         |                             | ·                    |                   |                   |         | ·               | bit (   |

| • • • • • •   |                             |                      |                   |                   |         |                 |         |

| Legend:       |                             |                      |                   |                   |         |                 |         |

| R = Readable  |                             | W = Writable         |                   | U = Unimplen      |         |                 |         |

| -n = Value at | POR                         | '1' = Bit is set     |                   | '0' = Bit is clea | ared    | x = Bit is unkr | IOWN    |

| bit 7         | RC2IE: EUS                  | ART2 Receive         | Interrupt Enab    | le bit            |         |                 |         |

|               | 1 = Enabled<br>0 = Disabled |                      |                   |                   |         |                 |         |

| bit 6         |                             | ART2 Transmit        | Interrupt Enab    | le bit            |         |                 |         |

|               | 1 = Enabled<br>0 = Disabled | 1                    |                   |                   |         |                 |         |

| bit 5         | RC1IE: EUS                  | ART1 Receive         | Interrupt Enab    | le bit            |         |                 |         |

|               | 1 = Enabled<br>0 = Disabled | ł                    |                   |                   |         |                 |         |

| bit 4         |                             | ART1 Transmit        | Interrupt Enab    | ole bit           |         |                 |         |

|               | 1 = Enabled<br>0 = Disabled |                      |                   |                   |         |                 |         |

| bit 3         | BCL2IE: MS                  | SP2 Bus Collisi      | on Interrupt E    | nable bit         |         |                 |         |

|               | 1 = Enabled                 |                      |                   |                   |         |                 |         |

| <b>h</b> # 0  | 0 = Disabled                |                      |                   | unt Enchla bit    |         |                 |         |

| bit 2         | 1 = Enabled                 | chronous Seria       | II Port 2 Intern  | upt Enable bit    |         |                 |         |

|               | 0 = Disabled                |                      |                   |                   |         |                 |         |

| bit 1         | BCL1IE: MS                  | SP1 Bus Collisi      | on Interrupt E    | nable bit         |         |                 |         |

|               | 1 = Enabled<br>0 = Disabled |                      |                   |                   |         |                 |         |

| bit 0         |                             | '<br>Ichronous Seria | Il Port 1 Interru | upt Enable bit    |         |                 |         |

|               | 1 = Enabled                 |                      |                   |                   |         |                 |         |

|               | 0 = Disabled                | 1                    |                   |                   |         |                 |         |

## REGISTER 14-13: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| R/W-0/0                                               | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0         | R/W-0/0          | R/W-0/0  | R/W-0/0 |  |  |

|-------------------------------------------------------|---------|-------------------|---------|-----------------|------------------|----------|---------|--|--|

| WPUx7                                                 | WPUx6   | WPUx5             | WPUx4   | WPUx3           | WPUx2            | WPUx1    | WPUx0   |  |  |

| bit 7                                                 |         |                   |         | -               |                  |          | bit 0   |  |  |

|                                                       |         |                   |         |                 |                  |          |         |  |  |

| Legend:                                               |         |                   |         |                 |                  |          |         |  |  |

| R = Readable                                          | bit     | W = Writable      | bit     | U = Unimpler    | nented bit, read | d as '0' |         |  |  |

| '1' = Bit is set                                      |         | '0' = Bit is clea | ared    | x = Bit is unkr | nown             |          |         |  |  |

| -n/n = Value at POR and BOR/Value at all other Resets |         |                   |         |                 |                  |          |         |  |  |

|                                                       |         |                   |         |                 |                  |          |         |  |  |

#### REGISTER 15-5: WPUx: WEAK PULL-UP REGISTER

bit 7-0

WPUx<7:0>: Weak Pull-up PORTx Control bits

1 = Weak Pull-up enabled

0 = Weak Pull-up disabled

|      | Dev        | /ice          |       |       |       |       |                      |       |       |       |

|------|------------|---------------|-------|-------|-------|-------|----------------------|-------|-------|-------|

| Name | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

| WPUA | Х          | Х             | WPUA7 | WPUA6 | WPUA5 | WPUA4 | WPUA3                | WPUA2 | WPUA1 | WPUA0 |

| WPUB | Х          | Х             | WPUB7 | WPUB6 | WPUB5 | WPUB4 | WPUB3                | WPUB2 | WPUB1 | WPUB0 |

| WPUC | Х          | Х             | WPUC7 | WPUC6 | WPUC5 | WPUC4 | WPUC3                | WPUC2 | WPUC1 | WPUC0 |

| WPUD | Х          |               | _     | _     | _     | _     | —                    | _     | _     | _     |

|      |            | Х             | WPUD7 | WPUD6 | WPUD5 | WPUD4 | WPUD3                | WPUD2 | WPUD1 | WPUD0 |

| WPUE | Х          |               | —     | _     | —     | _     | WPUE3 <sup>(1)</sup> | _     | _     | _     |

|      |            | Х             | _     | _     | _     | _     | WPUE3 <sup>(1)</sup> | WPUE2 | WPUE1 | WPUE0 |

#### TABLE 15-6: WEAK PULL-UP PORT REGISTERS

Note 1: If MCLRE = 1, the weak pull-up in RE3 is always enabled; bit WPUE3 is not affected.

| Name   | Bit 7  | Bit 6 | Bit 5         | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0   | Register<br>on page |

|--------|--------|-------|---------------|--------|-------|--------|---------|---------|---------------------|

| PIE2   | HLVDIE | ZCDIE | _             | _      | _     | —      | C2IE    | C1IE    | 181                 |

| PIR2   | HLVDIF | ZCDIF | _             | _      | _     | —      | C2IF    | C1IF    | 173                 |

| IPR2   | HLVDIP | ZCDIP |               |        |       | —      | C2IP    | C1IP    | 189                 |

| ZCDCON | ZCDSEN | _     | ZCDOUT        | ZCDPOL | _     | _      | ZCDINTP | ZCDINTN | 294                 |

| PMD2   | _      | DACMD | <b>ADC</b> MD | _      | _     | CMP2MD | CMP1MD  | ZCDMD   | 70                  |

#### TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### TABLE 23-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit 15/7 | Bit 14/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|----------|----------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 15:8 | XINST    | _        | DEBUG    | STVREN   | PPS1WAY  | ZCD      | BORV1   | BORV0   | 24                  |

|         | 7:0  | BOREN1   | BOREN0   | LPBOREN  | _        | _        | _        | PWRTE   | MCLRE   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

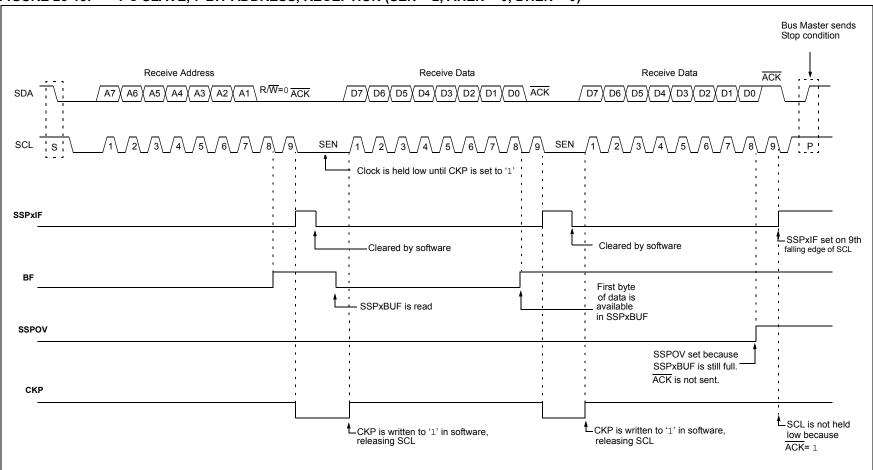

## FIGURE 26-15: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 0, DHEN = 0)

PIC18(L)F27/47K40

## 27.3 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 4.3.2.3 "Internal Oscillator Frequency Adjustment"** for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 27.4.1 "Auto-Baud Detect"**). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

## 27.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDxCON register selects 16-bit mode.

The SPxBRGH, SPxBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXxSTA register and the BRG16 bit of the BAUDxCON register. In Synchronous mode, the BRGH bit is ignored.

Table 27-3 contains the formulas for determining the baud rate. Example 27-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 27-5. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPxBRGH, SPxBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

## EXAMPLE 27-1: CALCULATING BAUD RATE ERROR

For a device with FOSC of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate =  $\frac{Fosc}{64([SPxBRGH:SPxBRGL] + 1)}$

Solving for SPxBRGH:SPxBRGL:

$SPBRGH:SPBRGL = \frac{Fosc}{Desired Baud Rate} - 1$   $= \frac{16000000}{9600} - 1$  = [25.042] = 25Calculated Baud Rate =  $\frac{16000000}{64(25+1)}$  = 9615Error =  $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$   $= \frac{(9615 - 9600)}{9600} = 0.16\%$

## 28.3 Register Definitions: FVR Control

| R/W-0/0          | R-q/q                                     | R/W-0/0                                                                                | R/W-0/0                                                    | R/W-0/0                              | R/W-0/0          | R/W-0/0 | R/W-0/0      |

|------------------|-------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------|------------------|---------|--------------|

| FVREN            | FVRRDY <sup>(1)</sup>                     | TSEN <sup>(3)</sup>                                                                    | TSRNG <sup>(3)</sup>                                       | CDAF                                 | VR<1:0>          | ADFV    | R<1:0>       |

| bit 7            | ·                                         |                                                                                        | •                                                          |                                      |                  |         | bit          |

|                  |                                           |                                                                                        |                                                            |                                      |                  |         |              |

| Legend:          |                                           |                                                                                        |                                                            |                                      |                  |         |              |

| R = Readable     |                                           | W = Writable                                                                           |                                                            | •                                    | mented bit, read |         |              |

| u = Bit is unc   | hanged                                    | x = Bit is unk                                                                         | nown                                                       |                                      | at POR and BO    |         | other Resets |

| '1' = Bit is set | t                                         | '0' = Bit is cle                                                                       | ared                                                       | q = Value dep                        | pends on condit  | ion     |              |

| bit 7            | 1 Fixed Vo                                | d Voltage Refe<br>Itage Referenc<br>Itage Referenc                                     | e is enabled                                               | bit                                  |                  |         |              |

| bit 6            | 1 = Fixed Vo                              | ed Voltage Re<br>Itage Referenc<br>Itage Referenc                                      | e output is rea                                            | -                                    | enabled          |         |              |

| bit 5            | 1 = Tempera                               | erature Indicato<br>ture Indicator i<br>ture Indicator i                               | s enabled                                                  | )                                    |                  |         |              |

| bit 4            | 1 = VOUT = V                              | perature Indica<br>/DD - 4VT (Higł<br>/DD - 2VT (Low                                   | n Range)                                                   | lection bit <sup>(3)</sup>           |                  |         |              |

| bit 3-2          | 11 = Compar<br>10 = Compar<br>01 = Compar | D>: Comparato<br>ator FVR Buffe<br>ator FVR Buffe<br>ator FVR Buffe<br>ator FVR Buffe  | er Gain is 4x, (4<br>er Gain is 2x, (2<br>er Gain is 1x, ( | 2.048V) <sup>(2)</sup>               | bits             |         |              |

| bit 1-0          | 11 = ADC FV<br>10 = ADC FV<br>01 = ADC FV | : ADC FVR Bu<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer Gain<br>'R Buffer is off | is 4x, (4.096V<br>is 2x, (2.048V                           | ) <sup>(2)</sup><br>) <sup>(2)</sup> |                  |         |              |

|                  | /RRDY is always                           |                                                                                        | cannot exceed                                              | Vdd.                                 |                  |         |              |

| REGISTER 28-1. | FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER |

|----------------|--------------------------------------------------|

| REGISTER 20-1. | FURGON. FIXED VOLTAGE REFERENCE CONTROL REGISTER |

2: Fixed Voltage Reference output cannot exceed VDD.

3: See Section 29.0 "Temperature Indicator Module" for additional information.

| _        |       | -      |       |       |       |         |           |        |                     |

|----------|-------|--------|-------|-------|-------|---------|-----------|--------|---------------------|

| Name     | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1     | Bit 0  | Register<br>on page |

| FVRCON   | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R<1:0> | ADFV      | R<1:0> | 423                 |

| ADCON0   | ADON  | ADCONT | _     | ADCS  |       | ADFM    | _         | ADGO   | 448                 |

| CMxNCH   | _     | —      | _     | —     |       |         | CxNCH<2:0 | >      | 469                 |

| CMxPCH   | —     | —      | _     | —     | _     |         | CxPCH<2:0 | >      | 470                 |

| DAC1CON1 |       |        | _     |       |       | DAC1R<4 | :0>       |        | 429                 |

## TABLE 28-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the Fixed Voltage Reference.

#### 31.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| The ADIF bit is set at the completion of |

|------------------------------------------|

| every conversion, regardless of whether  |

| or not the ADC interrupt is enabled.     |

|                                          |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

#### 31.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bits of the ADCON0 register controls the output format.

Figure 31-3 shows the two output formats.

#### FIGURE 31-3: 10-BIT ADC CONVERSION RESULT FORMAT

# PIC18(L)F27/47K40

| CLRF                                                                            | Clear f                                                              |                                     |                       | CLRWDT                                      | Clear Wat                              | chdog Time     | er            |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|-----------------------|---------------------------------------------|----------------------------------------|----------------|---------------|

| Syntax:                                                                         | CLRF f {,a}                                                          |                                     |                       | Syntax:                                     | CLRWDT                                 |                |               |

| Operands:                                                                       | $0 \leq f \leq 255$                                                  |                                     |                       | Operands:                                   | None                                   |                |               |

|                                                                                 | a ∈ [0,1]                                                            |                                     |                       | Operation:                                  | $000h \rightarrow WE$                  | DT,            |               |

| Operation:                                                                      | $\begin{array}{l} 000h \rightarrow f \\ 1 \rightarrow Z \end{array}$ |                                     |                       |                                             | $1 \rightarrow \overline{\text{TO}}$ , | OT postscaler, |               |

| Status Affected:                                                                | Z                                                                    |                                     |                       |                                             | $1 \rightarrow PD$                     |                |               |

| Encoding:                                                                       | 0110                                                                 | 101a fff:                           | f ffff                | Status Affected:                            | TO, PD                                 |                |               |

| Description:                                                                    | Clears the co                                                        | ontents of the                      | specified             | Encoding:                                   | 0000                                   |                | 00 0100       |

| register.<br>If 'a' is '0', the Acces<br>If 'a' is '1', the BSR is<br>GPR bank. |                                                                      | e BSR is used                       |                       |                                             | Watchdog 1                             | e WDT. Status  | esets the pos |

|                                                                                 |                                                                      | d the extended                      |                       | Words:                                      | 1                                      |                |               |

|                                                                                 |                                                                      | d, this instruct<br>teral Offset Ac | •                     | Cycles:                                     | 1                                      |                |               |

|                                                                                 | mode whene                                                           | ver f ≤ 95 (5F                      | h). See <b>Sec-</b>   | Q Cycle Activity:                           |                                        |                |               |

|                                                                                 |                                                                      | Byte-Oriente<br>tructions in I      |                       | Q1                                          | Q2                                     | Q3             | Q4            |

|                                                                                 |                                                                      | <b>Node</b> " for deta              |                       | Decode                                      | No                                     | Process        | No            |

| Words:                                                                          | 1                                                                    |                                     |                       |                                             | operation                              | Data           | operation     |

| Cycles:                                                                         | 1                                                                    |                                     |                       | Example:                                    | CLRWDT                                 |                |               |

| Q Cycle Activity:                                                               |                                                                      |                                     |                       | Before Instruc                              |                                        |                |               |

| Q1                                                                              | Q2                                                                   | Q3                                  | Q4                    | WDT Co                                      |                                        | ?              |               |

| Decode                                                                          | Read<br>register 'f'                                                 | Process<br>Data                     | Write<br>register 'f' | After Instructi<br>WDT Co<br><u>WD</u> T Po | unter =                                | 00h<br>0       |               |

| Example:                                                                        | CLRF                                                                 | FLAG REG,                           | 1                     | TO<br>PD                                    | =                                      | 1<br>1         |               |

| Before Instruc<br>FLAG_RI                                                       | tion<br>EG = 5Ah                                                     |                                     |                       |                                             |                                        |                |               |

| After Instructic<br>FLAG_RI                                                     |                                                                      |                                     |                       |                                             |                                        |                |               |

## PIC18(L)F27/47K40

| NEGF             | Negate f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | NEGF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Operands:        | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Status Affected: | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Encoding:        | 0110 110a ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                  | Location 'f' is negated using two's<br>complement. The result is placed in the<br>data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| O Cycle Activity |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| NOF       | •              | No Operation |                               |            |    |              |  |  |

|-----------|----------------|--------------|-------------------------------|------------|----|--------------|--|--|

| Synta     | ax:            | NOP          | NOP                           |            |    |              |  |  |

| Oper      | ands:          | None         | None                          |            |    |              |  |  |

| Oper      | ation:         | No operati   | on                            |            |    |              |  |  |

| Statu     | s Affected:    | None         |                               |            |    |              |  |  |

| Encoding: |                | 0000<br>1111 | 0000<br>xxxx                  | 000<br>xxx | -  | 0000<br>xxxx |  |  |

| Desc      | ription:       | No operati   | on.                           |            |    |              |  |  |

| Word      | ls:            | 1            |                               |            |    |              |  |  |