Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6К х 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

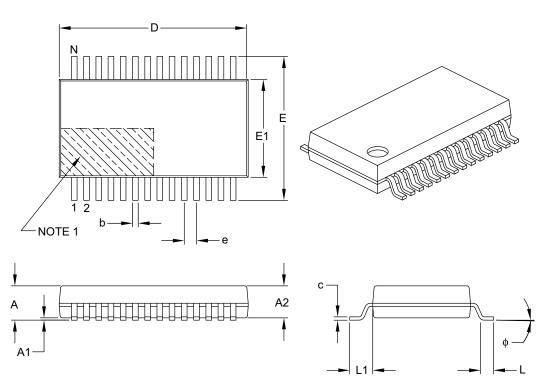

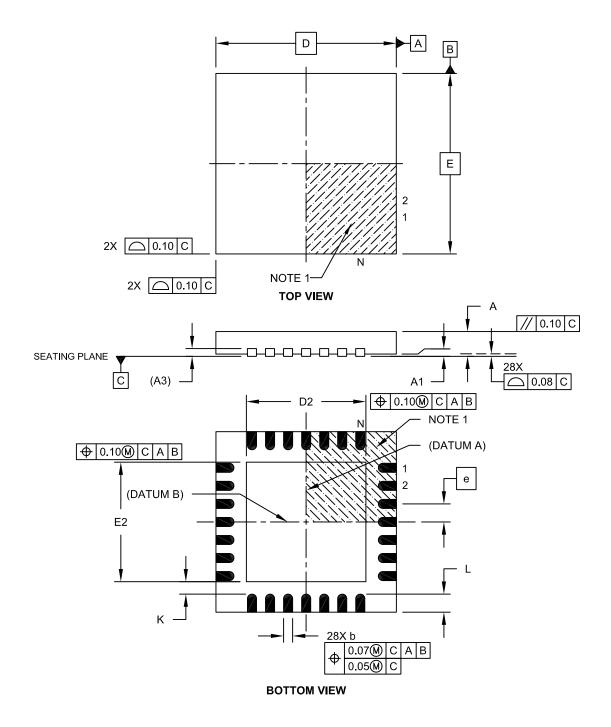

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f47k40-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 7.0 PERIPHERAL MODULE DISABLE (PMD)

Sleep, Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume some amount of power. There may be cases where the application needs what these modes do not provide: the ability to allocate limited power resources to the CPU while eliminating power consumption from the peripherals.

The PIC18(L)F2x/4xK40 family addresses this requirement by allowing peripheral modules to be selectively enabled or disabled, placing them into the lowest possible power mode.

For legacy reasons, all modules are ON by default following any Reset.

# 7.1 Disabling a Module

Disabling a module has the following effects:

- All clock and control inputs to the module are suspended; there are no logic transitions, and the module will not function.

- The module is held in Reset.

- · Any SFR becomes "unimplemented"

- Writing is disabled

- Reading returns 00h

- I/O functionality is prioritized as per Section 15.1, I/O Priorities

- All associated Input Selection registers are also disabled

# 7.2 Enabling a Module

When the PMD register bit is cleared, the module is re-enabled and will be in its Reset state (Power-on Reset). SFR data will reflect the POR Reset values.

Depending on the module, it may take up to one full instruction cycle for the module to become active. There should be no interaction with the module (e.g., writing to registers) for at least one instruction after it has been re-enabled.

# 7.3 Effects of a Reset

Following any Reset, each control bit is set to '0', enabling all modules.

# 7.4 System Clock Disable

Setting SYSCMD (PMD0, Register 7-1) disables the system clock (Fosc) distribution network to the peripherals. Not all peripherals make use of SYSCLK, so not all peripherals are affected. Refer to the specific peripheral description to see if it will be affected by this bit.

#### **Register Definitions: Windowed Watchdog Timer Control** 9.1

| U-0                                   | U-0                    | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>                                                                      | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W-0/0    |  |  |

|---------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|------------|--|--|

| _                                     | -                      |                                                                                                             |                                        | WDTPS<4:0>                             |                                        |                                        | SEN        |  |  |

| pit 7                                 | ·                      |                                                                                                             |                                        |                                        |                                        |                                        | bit        |  |  |

| _egend:                               |                        |                                                                                                             |                                        |                                        |                                        |                                        |            |  |  |

| R = Readat                            | ole bit                | W = Writable b                                                                                              | bit                                    | U = Unimplem                           | nented bit, read                       | as '0'                                 |            |  |  |

| u = Bit is ur                         | nchanged               | x = Bit is unkno                                                                                            | own                                    | -n/n = Value a                         | t POR and BO                           | R/Value at all oth                     | ner Resets |  |  |

| '1' = Bit is set '0' = Bit is cleared |                        | red                                                                                                         | q = Value dep                          | ends on condit                         | ion                                    |                                        |            |  |  |

| bit 7-6                               | Unimpleme              | ented: Read as '0                                                                                           | 3                                      |                                        |                                        |                                        |            |  |  |

| oit 5-1                               | WDTPS<4:               | 0>: Watchdog Tin                                                                                            | ner Prescale S                         | elect bits <sup>(1)</sup>              |                                        |                                        |            |  |  |

|                                       | Bit Value =            | Prescale Rate                                                                                               |                                        |                                        |                                        |                                        |            |  |  |

|                                       | 11111 <b>= F</b>       | Reserved. Results                                                                                           | in minimum in                          | terval (1:32)                          |                                        |                                        |            |  |  |

|                                       | •                      |                                                                                                             |                                        |                                        |                                        |                                        |            |  |  |

|                                       | •                      |                                                                                                             |                                        |                                        |                                        |                                        |            |  |  |

|                                       | •<br>10011 = F         | Reserved. Results                                                                                           | in minimum in                          | terval (1·32)                          |                                        |                                        |            |  |  |

|                                       | 10011 1                |                                                                                                             |                                        | (1.02)                                 |                                        |                                        |            |  |  |

| 10010 =                               |                        | 1:8388608 (2 <sup>23</sup> ) (Interval 256s nominal)                                                        |                                        |                                        |                                        |                                        |            |  |  |

|                                       | 10001 <b>= 1</b>       | 1:4194304 (2 <sup>22</sup> ) (Interval 128s nominal)<br>1:2097152 (2 <sup>21</sup> ) (Interval 64s nominal) |                                        |                                        |                                        |                                        |            |  |  |

|                                       | 10000 = 1              | 1:2097152 (2 <sup>-1</sup> ) (Interval 64s nominal)                                                         |                                        |                                        |                                        |                                        |            |  |  |

|                                       | 01111 = 1              | :1048576 (2 <sup>20</sup> ) (Interval 32s nominal)<br>:524288 (2 <sup>19</sup> ) (Interval 16s nominal)     |                                        |                                        |                                        |                                        |            |  |  |

|                                       | 01110 = 1<br>01101 = 1 | 1:262144 (2 <sup>18</sup> ) (Interval 8s nominal)                                                           |                                        |                                        |                                        |                                        |            |  |  |

|                                       | 01100 = 1              | 1:131072 (2 <sup>17</sup> ) (Interval 4s nominal)                                                           |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | 1:65536 (Interval 2s nominal) (Reset value)                                                                 |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | 1:32768 (Interval 1s nominal)                                                                               |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | 1:16384 (Interval 512 ms nominal)                                                                           |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | 1:8192 (Interval 256 ms nominal)                                                                            |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | = 1:4096 (Interval 128 ms nominal)<br>= 1:2048 (Interval 64 ms nominal)                                     |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | :1024 (Interval 32                                                                                          |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | :512 (Interval 16)                                                                                          |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | :256 (Interval 8 m                                                                                          |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | 1:128 (Interval 4 ms nominal)                                                                               |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | :64 (Interval 2 ms                                                                                          | ,                                      |                                        |                                        |                                        |            |  |  |

|                                       |                        | :32 (Interval 1 ms                                                                                          |                                        |                                        |                                        |                                        |            |  |  |

| oit O                                 |                        | are Enable/Disab                                                                                            | le for Watchdo                         | g Timer bit                            |                                        |                                        |            |  |  |

|                                       |                        | $\frac{\text{WDTE}<1:0>=1:x}{\text{WDTE}<1:0>=1:x}$                                                         |                                        |                                        |                                        |                                        |            |  |  |

|                                       |                        | This bit is ignored.<br>f WDTE<1:0> = 01:                                                                   |                                        |                                        |                                        |                                        |            |  |  |

|                                       | 1 = WDT is             |                                                                                                             |                                        |                                        |                                        |                                        |            |  |  |

|                                       | 0 = WDT is             |                                                                                                             |                                        |                                        |                                        |                                        |            |  |  |

|                                       | If WDTE<1              |                                                                                                             |                                        |                                        |                                        |                                        |            |  |  |

|                                       | This bit is ig         |                                                                                                             |                                        |                                        |                                        |                                        |            |  |  |

#### WINTCOND, WATCHING TIMED CONTROL DEGISTED A DECISTED 0 1.

- - 2: When WDTCPS <4:0> in CONFIG3L = 11111, the Reset value of WDTPS<4:0> is 01011. Otherwise, the Reset value of WDTPS<4:0> is equal to WDTCPS<4:0> in CONFIG3L.

- 3: When WDTCPS <4:0> in CONFIG3L  $\neq$  11111, these bits are read-only.

| U-0                  | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | U-0          | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> |

|----------------------|----------------------------------------|----------------------------------------|----------------------------------------|--------------|----------------------------------------|----------------------------------------|----------------------------------------|

| -                    |                                        | WDTCS<2:0>                             |                                        | -            |                                        | WINDOW<2:0>                            |                                        |

| bit 7                |                                        |                                        |                                        | •            |                                        |                                        | bit 0                                  |

|                      |                                        |                                        |                                        |              |                                        |                                        |                                        |

| Legend:              |                                        |                                        |                                        |              |                                        |                                        |                                        |

| R = Readable bit     |                                        | W = Writable                           | e bit                                  | U = Unimple  | mented bit, read                       | as '0'                                 |                                        |

| u = Bit is unchanged |                                        | x = Bit is unk                         | nown                                   | -n/n = Value | at POR and BO                          | R/Value at all othe                    | er Resets                              |

q = Value depends on condition

#### REGISTER 9-2: WDTCON1: WATCHDOG TIMER CONTROL REGISTER 1

| bit 7 | <b>Unimplemented:</b> Read as '0' |

|-------|-----------------------------------|

'1' = Bit is set

bit 6-4 WDTCS<2:0>: Watchdog Timer Clock Select bits

'0' = Bit is cleared

111 = Reserved

•

•

- 010 = Reserved

- 001 = MFINTOSC 31.25 kHz

- 000 = LFINTOSC 31 kHz

- bit 3 Unimplemented: Read as '0'

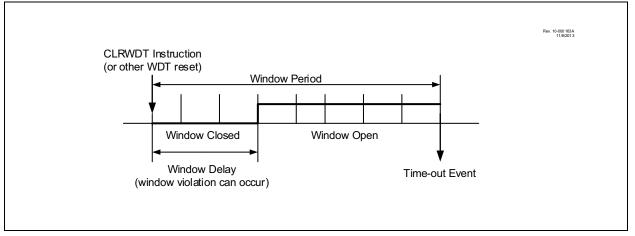

- bit 2-0 WINDOW<2:0>: Watchdog Timer Window Select bits

| WINDOW<2:0> | Window delay<br>Percent of time | Window opening<br>Percent of time |

|-------------|---------------------------------|-----------------------------------|

| 111         | N/A                             | 100                               |

| 110         | 12.5                            | 87.5                              |

| 101         | 25                              | 75                                |

| 100         | 37.5                            | 62.5                              |

| 011         | 50                              | 50                                |

| 010         | 62.5                            | 37.5                              |

| 001         | 75                              | 25                                |

| 000         | 87.5                            | 12.5                              |

- Note 1: If WDTCCS <2:0> in CONFIG3H = 111, the Reset value of WDTCS<2:0> is 000.

- 2: The Reset value of WINDOW<2:0> is determined by the value of WDTCWS<2:0> in the CONFIG3H register.

- **3:** If WDTCCS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

- 4: If WDTCWS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

# 9.7 Operation During Sleep

When the device enters Sleep, the WWDT is cleared. If the WWDT is enabled during Sleep, the WWDT resumes counting. When the device exits Sleep, the WWDT is cleared again.

The WWDT remains clear until the Oscillator Start-up Timer (OST) completes, if enabled. See **Section 4.3.1.3 "Oscillator Start-up Timer (OST)**" for more information on the OST.

When a WWDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON0 register can also be used. See **Section 10.0 "Memory Organization"** for more information.

#### TABLE 9-2: WWDT CLEARING CONDITIONS

| Conditions                                              | WWDT                         |

|---------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                          |                              |

| WDTE<1:0> = 01 and SEN = 0                              |                              |

| WDTE<1:0> = 10 and enter Sleep                          | Cleared                      |

| CLRWDT Command                                          | Cleared                      |

| Oscillator Fail Detected                                |                              |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |

#### FIGURE 9-2: WINDOW PERIOD AND DELAY

© 2016-2017 Microchip Technology Inc.

#### 10.3.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as either two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of two and the LSb will always read '0' (see Section 10.1.1 "Program Counter").

Figure 10-3 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 10-3 shows how the instruction GOTO 0006h is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 35.0 "Instruction Set Summary" provides further details of the instruction set.

# 10.3.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LFSR. In all cases, the second word of the instruction always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed and used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 10-4 shows how this works.

Note: See Section 10.8 "PIC18 Instruction Execution and the Extended Instruction Set" for information on two-word instructions in the extended instruction set.

## FIGURE 10-3: INSTRUCTIONS IN PROGRAM MEMORY

|                |            |                    | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|---------|---------|---------------------------|

|                | Program N  | lemory             |         |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |         |         | 000002h                   |

|                |            |                    |         |         | 000004h                   |

|                |            |                    |         |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h              | EFh     | 03h     | 00000Ah                   |

|                |            |                    | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456          | h C1h   | 23h     | 00000Eh                   |

|                |            |                    | F4h     | 56h     | 000010h                   |

|                |            |                    |         |         | 000012h                   |

|                |            |                    |         |         | 000014h                   |

#### EXAMPLE 10-4: TWO-WORD INSTRUCTIONS

| CASE 1:             |             |           |                            |

|---------------------|-------------|-----------|----------------------------|

| Object Code         | Source Code |           |                            |

| 0110 0110 0000 0000 | TSTFSZ REG  | 1 ;       | ; is RAM location 0?       |

| 1100 0001 0010 0011 | MOVFF REG   | 1, REG2 ; | ; No, skip this word       |

| 1111 0100 0101 0110 |             | ;         | Execute this word as a NOP |

| 0010 0100 0000 0000 | ADDWF REG   | 3;        | continue code              |

| CASE 2:             |             |           |                            |

| Object Code         | Source Code |           |                            |

| 0110 0110 0000 0000 | TSTFSZ REG  | 1 ;       | ; is RAM location 0?       |

| 1100 0001 0010 0011 | MOVFF REG   | 1, REG2 ; | Yes, execute this word     |

| 1111 0100 0101 0110 |             | ;         | ; 2nd word of instruction  |

| 0010 0100 0000 0000 | ADDWF REG   | 3;        | continue code              |

#### 11.1.5 ERASING PROGRAM FLASH MEMORY

The minimum erase block is 32 or 64 words (refer to Table 11-3). Only through the use of an external programmer, or through ICSP™ control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

For example, when initiating an erase sequence from a microcontroller with erase row size of 32 words, a block of 32 words (64 bytes) of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The NVMCON1 register commands the erase operation. The NVMREG<1:0> bits must be set to point to the Program Flash Memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

The NVM unlock sequence described in **Section 11.1.4 "NVM Unlock Sequence**" should be used to guard against accidental writes. This is sometimes referred to as a long write.

A long write is necessary for erasing the internal Flash. Instruction execution is halted during the long write cycle. The long write is terminated by the internal programming timer.

# 11.1.5.1 Program Flash Memory Erase Sequence

The sequence of events for erasing a block of internal program memory is:

- 1. NVMREG bits of the NVMCON1 register point to PFM

- 2. Set the FREE and WREN bits of the NVMCON1 register

- 3. Perform the unlock sequence as described in Section 11.1.4 "NVM Unlock Sequence"

If the PFM address is write-protected, the WR bit will be cleared and the erase operation will not take place, WRERR is signaled in this scenario.

The operation erases the memory row indicated by masking the LSBs of the current TBLPTR.

While erasing PFM, CPU operation is suspended and it resumes when the operation is complete. Upon completion the WR bit is cleared in hardware, the NVMIF is set and an interrupt will occur if the NVMIE bit is also set.

Write latch data is not affected by erase operations and WREN will remain unchanged.

Note 1: If a write or erase operation is terminated by an unexpected event, WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

- 2: WRERR is set if WR is written to '1' while TBLPTR points to a write-protected address.

- **3:** WRERR is set if WR is written to '1' while TBLPTR points to an invalid address location (Table 10-2 and Table 11-1).

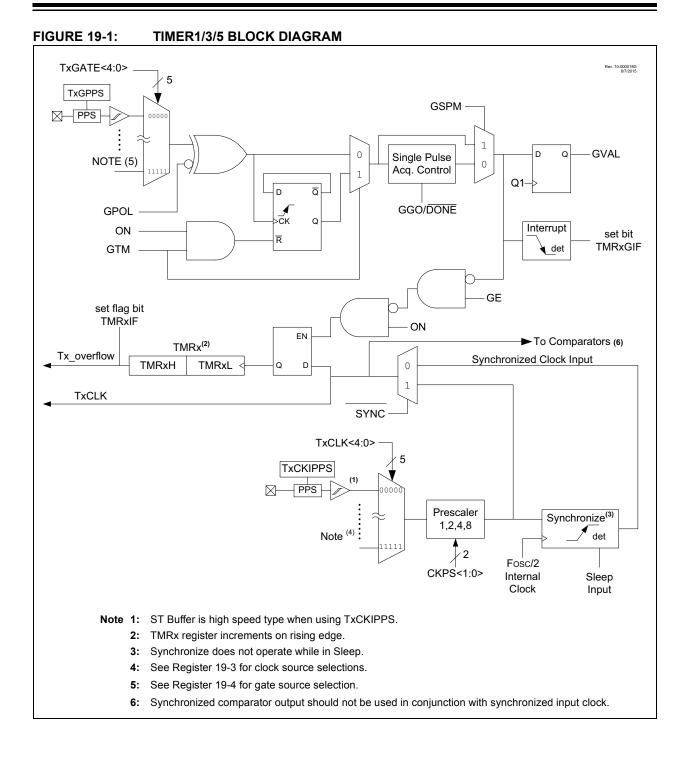

## 19.9 Timer1/3/5 Interrupt

The Timer1/3/5 register pair (TMRxH:TMRxL) increments to FFFFh and rolls over to 0000h. When Timer1/3/5 rolls over, the Timer1/3/5 interrupt flag bit of the PIR4 register is set. To enable the interrupt-on-rollover, you must set these bits:

- TMRxON bit of the TxCON register

- TMRxIE bits of the PIE4 register

- PEIE/GIEL bit of the INTCON register

- · GIE/GIEH bit of the INTCON register

The interrupt is cleared by clearing the TMRxIF bit in the Interrupt Service Routine.

For more information on selecting high or low priority status for the Timer1/3/5 Overflow Interrupt, see **Section 14.0 "Interrupts"**.

Note: The TMRxH:TMRxL register pair and the TMRxIF bit should be cleared before enabling interrupts.

## 19.10 Timer1/3/5 Operation During Sleep

Timer1/3/5 can only operate during Sleep when set up in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMRxON bit of the TxCON register must be set

- TMRxIE bit of the PIE4 register must be set

- PEIE/GIEL bit of the INTCON register must be set

- TxSYNC bit of the TxCON register must be set

- Configure the TMRxCLK register for using secondary oscillator as the clock source

- Enable the SOSCEN bit of the OSCEN register (Register 4-7)

The device will wake-up on an overflow and execute the next instruction. If the GIE/GIEH bit of the INTCON register is set, the device will call the Interrupt Service Routine.

The secondary oscillator will continue to operate in Sleep regardless of the  $\overline{\text{TxSYNC}}$  bit setting.

#### 19.11 CCP Capture/Compare Time Base

The CCP modules use the TMRxH:TMRxL register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMRxH:TMRxL register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value in the CCPRxH:CCPRxL register pair matches the value in the TMRxH:TMRxL register pair. This event can be a Special Event Trigger.

For more information, see Section 21.0 "Capture/Compare/PWM Module".

## 19.12 CCP Special Event Trigger

When any of the CCP's are configured to trigger a special event, the trigger will clear the TMRxH:TMRxL register pair. This special event does not cause a Timer1/3/5 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1/3/5.

Timer1/3/5 should be synchronized and FOSC/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1/3/5 can cause a Special Event Trigger to be missed.

In the event that a write to TMRxH or TMRxL coincides with a Special Event Trigger from the CCP, the write will take precedence.

© -2017 Microchip Technology Inc.

# PIC18(L)F27/47K40

| SHUTDOWN<br>bit 7<br>Legend:<br>R = Readable bit | REN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LSBD            | )<1:0>      | LSAC          |                 |             |             |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|---------------|-----------------|-------------|-------------|

| Legend:                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |             | 20/10         | <1:0>           | —           | —           |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |             |               |                 |             | bit C       |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |             |               |                 |             |             |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | W = Writable    | bit         | II = Unimplem | ented bit, read | as '0'      |             |

| u = Bit is unchang                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | x = Bit is unk  |             |               | t POR and BOF   |             | thar Resets |

| '1' = Bit is set                                 | geu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0' = Bit is cle |             |               | set/cleared by  |             |             |

| q = Value depend                                 | ls on condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 | areu        |               | sercleared by   | naruware    |             |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |             |               |                 |             |             |

| bit 7<br>bit 6                                   | <pre>SHUTDOWN: Auto-Shutdown Event Status bit<sup>(1,2)</sup> 1 = An auto-shutdown state is in effect 0 = No auto-shutdown event has occurred</pre>                                                                                                                                                                                                                                                                                                                                                       |                 |             |               |                 |             |             |

| טונס                                             | REN: Auto-Restart Enable bit<br>1 = Auto-restart is enabled<br>0 = Auto-restart is disabled                                                                                                                                                                                                                                                                                                                                                                                                               |                 |             |               |                 |             |             |

| bit 5-4                                          | <ul> <li>LSBD&lt;1:0&gt;: CWG1B and CWG1D Auto-Shutdown State Control bits</li> <li>11 = A logic '1' is placed on CWG1B/D when an auto-shutdown event occurs.</li> <li>10 = A logic '0' is placed on CWG1B/D when an auto-shutdown event occurs.</li> <li>01 = Pin is tri-stated on CWG1B/D when an auto-shutdown event occurs.</li> <li>00 = The inactive state of the pin, including polarity, is placed on CWG1B/D after the require dead-band interval when an auto-shutdown event occurs.</li> </ul> |                 |             |               |                 |             | he required |

| bit 3-2                                          | LSAC<1:0>: CWG1A and CWG1C Auto-Shutdown State Control bits<br>11 = A logic '1' is placed on CWG1A/C when an auto-shutdown event occurs.<br>10 = A logic '0' is placed on CWG1A/C when an auto-shutdown event occurs.<br>01 = Pin is tri-stated on CWG1A/C when an auto-shutdown event occurs.<br>00 = The inactive state of the pin, including polarity, is placed on CWG1A/C after the requir<br>dead-band interval when an auto-shutdown event occurs.                                                 |                 |             |               |                 | he required |             |

| bit 1-0                                          | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ted: Read as    | <b>'</b> 0' |               |                 |             |             |

2: The outputs will remain in auto-shutdown state until the next rising edge of the CWG data input after this bit is cleared.

| Name       | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1     | Bit 0  | Register<br>on Page |

|------------|----------|---------|---------|---------|-------|-------|-----------|--------|---------------------|

| CWG1CON0   | EN       | LD      | —       | —       | —     |       | MODE<2:0> | •      | 315                 |

| CWG1CON1   | _        | —       | IN      | _       | POLD  | POLC  | POLB      | POLA   | 316                 |

| CWG1CLKCON | _        | —       | _       | _       | _     | —     | —         | CS     | 317                 |

| CWG1ISM    | —        | —       | —       | —       |       |       | ISM<2:0>  |        | 317                 |

| CWG1STR    | OVRD     | OVRC    | OVRB    | OVRA    | STRD  | STRC  | STRB      | STRA   | 318                 |

| CWG1AS0    | SHUTDOWN | REN     | LSBD    | <1:0>   | LSAC  |       |           | 319    |                     |

| CWG1AS1    | _        | —       | AS5E    | AS4E    | AS3E  | AS2E  | AS1E      | AS0E   | 320                 |

| CWG1DBR    | _        | —       |         |         | DBR<  | <5:0> |           |        | 321                 |

| CWG1DBF    | _        | —       |         |         | DBF<  | :5:0> |           |        | 321                 |

| PIE7       | SCANIE   | CRCIE   | NVMIE   | _       | _     | _     |           | CWG1IE | 186                 |

| PIR7       | SCANIF   | CRCIF   | NVMIF   | _       | _     | _     | _         | CWG1IF | 178                 |

| IPR7       | SCANIP   | CRCIP   | NVMIP   | _       | _     | _     | —         | CWG1IP | 194                 |

| PMD4       | UART2MD  | UART1MD | MSSP2MD | MSSP1MD |       | _     | —         | CWG1MD | 72                  |

#### TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH CWG

Legend: -= unimplemented locations read as '0'. Shaded cells are not used by CWG.

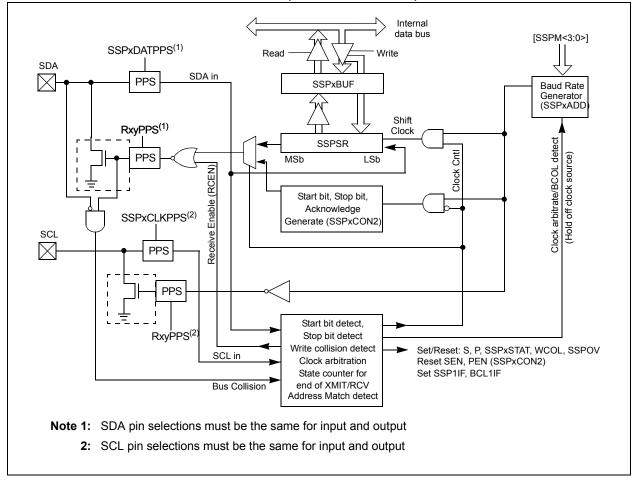

controlled through addressing. Figure 26-9 is a block diagram of the I<sup>2</sup>C interface module in Master mode.

Figure 26-10 is a diagram of the  $I^2C$  interface module

in Slave mode.

# 26.6 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit (I<sup>2</sup>C) bus is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is

FIGURE 26-9: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

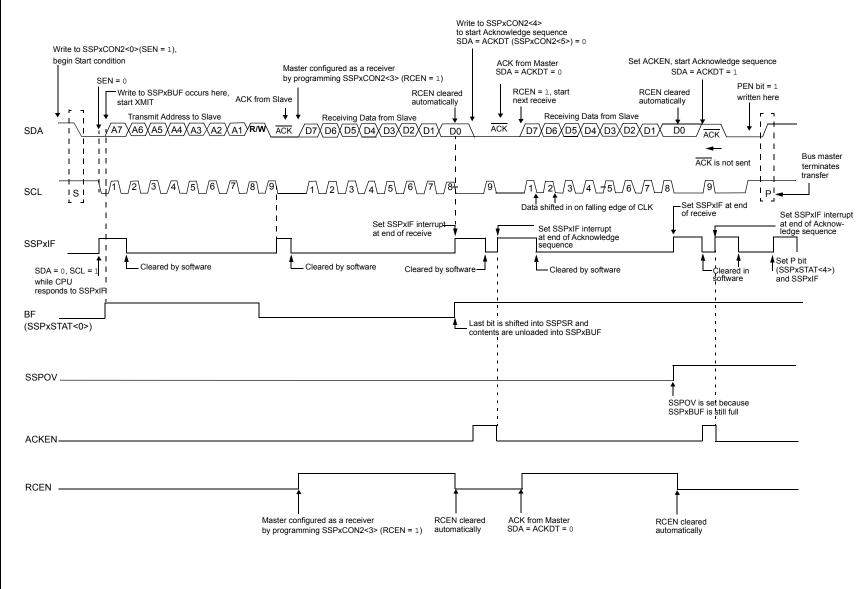

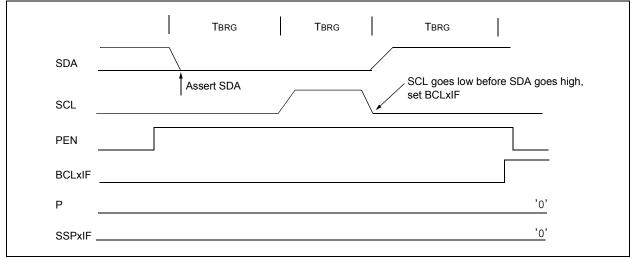

#### 26.10.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 26-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 26-39).

#### FIGURE 26-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 26-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# 28.3 Register Definitions: FVR Control

| R/W-0/0          | R-q/q                                                                                                                                                                                                                                                                                           | R/W-0/0                                            | R/W-0/0              | R/W-0/0       | R/W-0/0          | R/W-0/0 | R/W-0/0      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|---------------|------------------|---------|--------------|--|

| FVREN            | FVRRDY <sup>(1)</sup>                                                                                                                                                                                                                                                                           | TSEN <sup>(3)</sup>                                | TSRNG <sup>(3)</sup> | CDAF          | VR<1:0>          | ADFV    | R<1:0>       |  |

| bit 7            | ·                                                                                                                                                                                                                                                                                               |                                                    | •                    |               |                  |         | bit          |  |

|                  |                                                                                                                                                                                                                                                                                                 |                                                    |                      |               |                  |         |              |  |

| Legend:          |                                                                                                                                                                                                                                                                                                 |                                                    |                      |               |                  |         |              |  |

| R = Readable     |                                                                                                                                                                                                                                                                                                 | W = Writable                                       |                      | •             | mented bit, read |         |              |  |

| u = Bit is unc   | hanged                                                                                                                                                                                                                                                                                          | x = Bit is unk                                     | nown                 |               | at POR and BO    |         | other Resets |  |

| '1' = Bit is set | t                                                                                                                                                                                                                                                                                               | '0' = Bit is cle                                   | ared                 | q = Value dep | pends on condit  | ion     |              |  |

| bit 7            | 1 Fixed Vo                                                                                                                                                                                                                                                                                      | d Voltage Refe<br>Itage Referenc<br>Itage Referenc | e is enabled         | bit           |                  |         |              |  |

| bit 6            | <b>FVRRDY:</b> Fixed Voltage Reference Ready Flag bit <sup>(1)</sup><br>1 = Fixed Voltage Reference output is ready for use<br>0 = Fixed Voltage Reference output is not ready or not enabled                                                                                                   |                                                    |                      |               |                  |         |              |  |

| bit 5            | <b>TSEN:</b> Temperature Indicator Enable bit <sup>(3)</sup><br>1 = Temperature Indicator is enabled<br>0 = Temperature Indicator is disabled                                                                                                                                                   |                                                    |                      |               |                  |         |              |  |

| bit 4            | <b>TSRNG:</b> Temperature Indicator Range Selection bit <sup>(3)</sup><br>1 = VOUT = VDD - 4VT (High Range)<br>0 = VOUT = VDD - 2VT (Low Range)                                                                                                                                                 |                                                    |                      |               |                  |         |              |  |

| bit 3-2          | <b>CDAFVR&lt;1:0&gt;:</b> Comparator FVR Buffer Gain Selection bits<br>11 = Comparator FVR Buffer Gain is 4x, (4.096V) <sup>(2)</sup><br>10 = Comparator FVR Buffer Gain is 2x, (2.048V) <sup>(2)</sup><br>01 = Comparator FVR Buffer Gain is 1x, (1.024V)<br>00 = Comparator FVR Buffer is off |                                                    |                      |               |                  |         |              |  |

| bit 1-0          | <b>ADFVR&lt;1:0&gt;:</b> ADC FVR Buffer Gain Selection bit<br>11 = ADC FVR Buffer Gain is 4x, $(4.096V)^{(2)}$<br>10 = ADC FVR Buffer Gain is 2x, $(2.048V)^{(2)}$<br>01 = ADC FVR Buffer Gain is 1x, $(1.024V)$<br>00 = ADC FVR Buffer is off                                                  |                                                    |                      |               |                  |         |              |  |

|                  | VRRDY is always '1'.                                                                                                                                                                                                                                                                            |                                                    |                      |               |                  |         |              |  |

| REGISTER 28-1. | FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER |

|----------------|--------------------------------------------------|

| REGISTER 20-1. | FURGON. FIXED VOLTAGE REFERENCE CONTROL REGISTER |

2: Fixed Voltage Reference output cannot exceed VDD.

3: See Section 29.0 "Temperature Indicator Module" for additional information.

| _        |       | -      |       |       |       |            |           |        |                     |

|----------|-------|--------|-------|-------|-------|------------|-----------|--------|---------------------|

| Name     | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1     | Bit 0  | Register<br>on page |

| FVRCON   | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R<1:0>    | ADFV      | R<1:0> | 423                 |

| ADCON0   | ADON  | ADCONT | _     | ADCS  |       | ADFM       | _         | ADGO   | 448                 |

| CMxNCH   | _     | —      | _     | —     |       |            | CxNCH<2:0 | >      | 469                 |

| CMxPCH   | _     | —      | _     | —     |       | CxPCH<2:0> |           | 470    |                     |

| DAC1CON1 |       |        | _     |       |       | DAC1R<4    | :0>       |        | 429                 |

### TABLE 28-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the Fixed Voltage Reference.

#### 31.4.1 CVD OPERATION

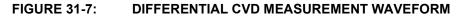

A CVD operation begins with the ADC's internal and hold capacitor sample (С<sub>НОГD</sub>) being disconnected from the path which connects it to the external capacitive sensor node. While disconnected, CHOLD is precharged to VDD or Vss, while the path to the sensor node is also discharged to VDD or VSS. Typically, this node is discharged to the level opposite that of CHOLD. When the precharge phase is complete, the VDD/VSS bias paths for the two nodes are shut off and CHOLD and the path to the external sensor node are re-connected, at which time the acquisition phase of the CVD operation begins. During acquisition, a capacitive voltage divider is formed between the precharged CHOLD and sensor nodes, which results in a final voltage level setting on CHOLD which is determined by the capacitances and precharge levels of the two nodes. After acquisition, the ADC converts the voltage level on CHOLD. This process is then repeated with the selected precharge levels for both the CHOLD and the inverted sensor nodes. Figure 31-7 shows the waveform for two inverted CVD measurements, which is known as differential CVD measurement.

| Field           | Description                                                                                                                                                     |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| a               | RAM access bit<br>a = 0: RAM location in Access RAM (BSR register is ignored)<br>a = 1: RAM bank is specified by BSR register                                   |  |  |  |  |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                             |  |  |  |  |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                      |  |  |  |  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                                  |  |  |  |  |

| d               | Destination select bit<br>d = 0: store result in WREG<br>d = 1: store result in file register f                                                                 |  |  |  |  |

| dest            | Destination: either the WREG register or the specified register file location.                                                                                  |  |  |  |  |

| f               | 8-bit Register file address (00h to FFh) or 2-bit FSR designator (0h to 3h).                                                                                    |  |  |  |  |

| fs              | 12-bit Register file address (000h to FFFh). This is the source address.                                                                                        |  |  |  |  |

| fd              | 12-bit Register file address (000h to FFFh). This is the destination address.                                                                                   |  |  |  |  |

| GIE             | Global Interrupt Enable bit.                                                                                                                                    |  |  |  |  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                                       |  |  |  |  |

| label           | Label name.                                                                                                                                                     |  |  |  |  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions:                     |  |  |  |  |

| *               | No change to register (such as TBLPTR with table reads and writes)                                                                                              |  |  |  |  |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                                             |  |  |  |  |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for CALL/BRANCH and RETURN instructions.                    |  |  |  |  |

| PC              | Program Counter.                                                                                                                                                |  |  |  |  |

| PCL             | Program Counter Low Byte.                                                                                                                                       |  |  |  |  |

| PCH             | Program Counter High Byte.                                                                                                                                      |  |  |  |  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                                |  |  |  |  |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                               |  |  |  |  |

| PD              | Power-down bit.                                                                                                                                                 |  |  |  |  |

| PRODH           | Product of Multiply High Byte.                                                                                                                                  |  |  |  |  |

| PRODL           | Product of Multiply Low Byte.                                                                                                                                   |  |  |  |  |

| S               | Fast Call/Return mode select bit<br>s = 0: do not update into/from shadow registers<br>s = 1: certain registers loaded into/from shadow registers (Fast mode)   |  |  |  |  |

| TBLPTR          | 21-bit Table Pointer (points to a Program Memory location).                                                                                                     |  |  |  |  |

| TABLAT          | 8-bit Table Latch.                                                                                                                                              |  |  |  |  |

| TO              | Time-out bit.                                                                                                                                                   |  |  |  |  |

| TOS             | Top-of-Stack.                                                                                                                                                   |  |  |  |  |

| u               | Unused or unchanged.                                                                                                                                            |  |  |  |  |

| WDT             | Watchdog Timer.                                                                                                                                                 |  |  |  |  |

| WREG            | Working register (accumulator).                                                                                                                                 |  |  |  |  |

| x               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |  |  |  |  |

| Zs              | 7-bit offset value for indirect addressing of register files (source).                                                                                          |  |  |  |  |

| z <sub>d</sub>  | 7-bit offset value for indirect addressing of register files (destination).                                                                                     |  |  |  |  |

| { }             | Optional argument.                                                                                                                                              |  |  |  |  |

| [text]          | Indicates an indexed address.                                                                                                                                   |  |  |  |  |

| (text)          | The contents of text.                                                                                                                                           |  |  |  |  |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer $expr$ .                                                                                               |  |  |  |  |

| $\rightarrow$   | Assigned to.                                                                                                                                                    |  |  |  |  |

| < >             | Register bit field.                                                                                                                                             |  |  |  |  |

|                 |                                                                                                                                                                 |  |  |  |  |

| ∈               | In the set of.                                                                                                                                                  |  |  |  |  |

TABLE 35-1: OPCODE FIELD DESCRIPTIONS

# PIC18(L)F27/47K40

| if ZERO bit                                                                                                           | 27                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| if ZERO bit                                                                                                           | 27                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                                                                                                                       |                                                                                                                                                                                                                                                                       | $-128 \le n \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                                                                                                       | if ZERO bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| None                                                                                                                  | None                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 1110                                                                                                                  | 1110 0000 nnnn nnnn                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| will branch.<br>The 2's com<br>added to the<br>have increm<br>instruction,<br>PC + 2 + 2r                             | The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |