Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f47k40t-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Allocation Tables**

TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F27K40)

| IADEL              |                          |            |      | ION IABLE (I                           | ( – ,            | ,                    |     |                     |       |                              |                        |                       |                                              |         |                |

|--------------------|--------------------------|------------|------|----------------------------------------|------------------|----------------------|-----|---------------------|-------|------------------------------|------------------------|-----------------------|----------------------------------------------|---------|----------------|

| I/O <sup>(2)</sup> | 28-Pin SPDIP, SOIC, SSOP | 28-Pin QFN | A/D  | Reference                              | Comparator       | Timers               | doo | cwe                 | ZCD   | Interrupt                    | EUSART                 | DSM                   | MSSP                                         | Pull-up | Basic          |

| RA0                | 2                        | 27         | ANA0 | _                                      | C1IN0-<br>C2IN0- |                      | -   | _                   | _     | IOCA0                        | _                      | _                     | _                                            | Y       | _              |

| RA1                | 3                        | 28         | ANA1 | _                                      | C1IN1-<br>C2IN1- | -                    | _   | _                   | _     | IOCA1                        | _                      | _                     | _                                            | Y       | _              |

| RA2                | 4                        | 1          | ANA2 | DAC1OUT1<br>VREF- (DAC)<br>VREF- (ADC) | C1IN0+<br>C2IN0+ | 1                    | -   | -                   | _     | IOCA2                        | -                      | -                     | -                                            | Y       | _              |

| RA3                | 5                        | 2          | ANA3 | VREF+ (DAC)<br>VREF+ (ADC)             | C1IN1+           | _                    | _   | _                   | _     | IOCA3                        | _                      | MDCIN1 <sup>(1)</sup> | _                                            | Υ       | _              |

| RA4                | 6                        | 3          | ANA4 | _                                      | _                | T0CKI <sup>(1)</sup> | _   | _                   | _     | IOCA4                        | _                      | MDCIN2 <sup>(1)</sup> | _                                            | Υ       | _              |

| RA5                | 7                        | 4          | ANA5 | _                                      | _                | _                    | _   | _                   | _     | IOCA5                        | _                      | MDMIN <sup>(1)</sup>  | SS1 <sup>(1)</sup>                           | Υ       | _              |

| RA6                | 10                       | 7          | ANA6 | _                                      | _                | _                    | _   | _                   | _     | IOCA6                        | _                      | _                     | _                                            | Y       | CLKOUT<br>OSC2 |

| RA7                | 9                        | 6          | ANA7 | _                                      | _                | -                    | _   | _                   | _     | IOCA7                        | _                      | _                     | _                                            | Y       | OSC1<br>CLKIN  |

| RB0                | 21                       | 18         | ANB0 | _                                      | C2IN1+           | 1                    | _   | CWG1 <sup>(1)</sup> | ZCDIN | IOCB0<br>INT0 <sup>(1)</sup> | _                      | _                     | SS2 <sup>(1)</sup>                           | Y       | _              |

| RB1                | 22                       | 19         | ANB1 | _                                      | C1IN3-<br>C2IN3- | _                    | _   | _                   | _     | IOCB1<br>INT1 <sup>(1)</sup> | _                      | _                     | SCK2 <sup>(1)</sup><br>SCL2 <sup>(3,4)</sup> | Y       | _              |

| RB2                | 23                       | 20         | ANB2 | _                                      | _                | _                    | _   | _                   | _     | IOCB2<br>INT2 <sup>(1)</sup> | _                      | _                     | SDI2 <sup>(1)</sup><br>SDA2 <sup>(3,4)</sup> | Y       | _              |

| RB3                | 24                       | 21         | ANB3 | _                                      | C1IN2-<br>C2IN2- | _                    |     | _                   | _     | IOCB3                        | _                      | _                     | _                                            | Υ       | _              |

| RB4                | 25                       | 22         | ANB4 | _                                      | _                | T5G <sup>(1)</sup>   | _   | _                   | _     | IOCB4                        | _                      | _                     | _                                            | Υ       | _              |

| RB5                | 26                       | 23         | ANB5 | _                                      | _                | T1G <sup>(1)</sup>   |     | _                   | _     | IOCB5                        | _                      | _                     |                                              | Υ       | _              |

| RB6                | 27                       | 24         | ANB6 | _                                      | _                | _                    | _   | _                   | _     | IOCB6                        | CK2 <sup>(1)</sup>     | _                     | _                                            | Υ       | ICSPCLK        |

| RB7                | 28                       | 25         | ANB7 | DAC1OUT2                               | _                | T6AIN <sup>(1)</sup> | -   | _                   | _     | IOCB7                        | RX2/DT2 <sup>(1)</sup> | _                     |                                              | Υ       | ICSPDAT        |

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers (Register 17-1).

<sup>2:</sup> All pin outputs default to PORT latch data. Any pin can be selected as a peripheral digital output with the PPS output selection registers.

<sup>3:</sup> These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

<sup>4:</sup> These pins are configured for I<sup>2</sup>C logic levels; The SCLx/SDAx signals may be assigned to any of these pins. PPS assignments to the other pins (e.g., RB1) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

## REGISTER 4-5: OSCFRQ: HFINTOSC FREQUENCY SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-q/q    | R/W-q/q | R/W-q/q | R/W-q/q |

|-------|-----|-----|-----|------------|---------|---------|---------|

| _     | _   | _   | _   | HFFRQ<3:0> |         |         |         |

| bit 7 |     |     |     |            |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedq = Reset value is determined by hardware

bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 **HFFRQ<3:0>:** HFINTOSC Frequency Selection bits

| HFFRQ<3:0>            | Nominal Freq (MHz) |  |  |  |  |  |

|-----------------------|--------------------|--|--|--|--|--|

| 1001                  |                    |  |  |  |  |  |

| 1010                  |                    |  |  |  |  |  |

| 1111                  |                    |  |  |  |  |  |

| 1110                  | Reserved           |  |  |  |  |  |

| 1101                  |                    |  |  |  |  |  |

| 1100                  |                    |  |  |  |  |  |

| 1011                  |                    |  |  |  |  |  |

| 1000(3)               | 64                 |  |  |  |  |  |

| 0111                  | 48                 |  |  |  |  |  |

| 0110                  | 32                 |  |  |  |  |  |

| 0101 <sup>(4)</sup>   | 16                 |  |  |  |  |  |

| 0100                  | 12                 |  |  |  |  |  |

| 0011                  | 8                  |  |  |  |  |  |

| 0010 <sup>(1,2)</sup> | 4                  |  |  |  |  |  |

| 0001                  | 2                  |  |  |  |  |  |

| 0000                  | 1                  |  |  |  |  |  |

Note 1: Refer to Table 4-1 for more information.

## REGISTER 5-2: CLKRCLK: CLOCK REFERENCE CLOCK SELECTION MUX

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | _   | _   | _   | _   |         | CLK<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 CLK<2:0>: CLKR Clock Selection bits

111 = Unimplemented

110 = Unimplemented

101 = Unimplemented

100 = SOSC

011 = MFINTOSC (500 kHz)

010 = LFINTOSC (31 kHz)

001 = HFINTOSC

000 = FOSC

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK REFERENCE OUTPUT

| Name    | Bit 7  | Bit 6 | Bit 5  | Bit 4 | Bit 3       | Bit 2    | Bit 1    | Bit 0 | Register on Page |          |  |  |

|---------|--------|-------|--------|-------|-------------|----------|----------|-------|------------------|----------|--|--|

| CLKRCON | EN     | -     | _      | DC<   | DC<1:0>     |          | DIV<2:0> |       |                  | DIV<2:0> |  |  |

| CLKRCLK | _      | _     | _      | _     | _           | CLK<2:0> |          |       | 57               |          |  |  |

| PMD0    | SYSCMD | FVRMD | HLVDMD | CRCMD | SCANMD      | NVMMD    | CLKRMD   | IOCMD | 68               |          |  |  |

| RxyPPS  | _      |       | _      |       | RxyPPS<4:0> |          |          |       |                  |          |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the CLKR module.

## REGISTER 6-2: CPUDOZE: DOZE AND IDLE REGISTER

| R/W-0/u | R/W/HC/HS-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|---------------|---------|---------|-----|---------|-----------|---------|

| IDLEN   | DOZEN         | ROI     | DOE     | _   |         | DOZE<2:0> |         |

| bit 7   |               |         |         |     |         |           | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

| bit 7   | IDLEN: Idle Enable bit  1 = A SLEEP instruction inhibits the CPU clock, but not the peripheral clock(s)  0 = A SLEEP instruction places the device into full Sleep mode                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | DOZEN: Doze Enable bit <sup>(1,2)</sup> 1 = The CPU executes instruction cycles according to DOZE setting  0 = The CPU executes all instruction cycles (fastest, highest power operation)                                    |

| bit 5   | <ul> <li>ROI: Recover-On-Interrupt bit</li> <li>1 = Entering the Interrupt Service Routine (ISR) makes DOZEN = 0 bit, bringing the CPU to full-speed operation</li> <li>0 = Interrupt entry does not change DOZEN</li> </ul> |

| bit 4   | <b>DOE</b> : Doze-On-Exit bit  1 = Executing RETFIE makes DOZEN = 1, bringing the CPU to reduced speed operation  0 = RETFIE does not change DOZEN                                                                           |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                   |

| bit 2-0 | DOZE<2:0>: Ratio of CPU Instruction Cycles to Peripheral Instruction Cycles  111 =1:256  110 =1:128  101 =1:64  100 =1:32  011 =1:16  010 =1:8  001 =1:4  000 =1:2                                                           |

- **Note 1:** When ROI = 1 or DOE = 1, DOZEN is changed by hardware interrupt entry and/or exit.

- 2: Entering ICD overrides DOZEN, returning the CPU to full execution speed; this bit is not affected.

## REGISTER 9-5: WDTTMR: WDT TIMER REGISTER (READ-ONLY)

| R-0/0 | R-0/0       | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0   |

|-------|-------------|-------|-------|-------|-------|-------|---------|

|       | WDTTMR<4:0> |       |       |       |       | PSCNT | <17:16> |

| bit 7 |             |       |       |       |       |       | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

# bit 7-3 WDTTMR<4:0>: Watchdog Window Value bits

| MINDOM | WDT Win     | Onen Bereent |              |

|--------|-------------|--------------|--------------|

| WINDOW | Closed      | Open         | Open Percent |

| 111    | N/A         | 00000-11111  | 100          |

| 110    | 00000-00011 | 00100-11111  | 87.5         |

| 101    | 00000-00111 | 01000-11111  | 75           |

| 100    | 00000-01011 | 01100-11111  | 62.5         |

| 011    | 00000-01111 | 10000-11111  | 50           |

| 010    | 00000-10011 | 10100-11111  | 37.5         |

| 001    | 00000-10111 | 11000-11111  | 25           |

| 000    | 00000-11011 | 11100-11111  | 12.5         |

bit 2 STATE: WDT Armed Status bit

1 = WDT is armed 0 = WDT is not armed

bit 1-0 **PSCNT<17:16>:** Prescale Select Upper Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F27/47K40 DEVICES (CONTINUED)

| Address | Name     | Bit 7           | Bit 6              | Bit 5            | Bit 4             | Bit 3           | Bit 2      | Bit 1  | Bit 0    | Value on<br>POR, BOR |  |

|---------|----------|-----------------|--------------------|------------------|-------------------|-----------------|------------|--------|----------|----------------------|--|

| FC1h    | TMR5L    | Holding Registe | er for the Least   | Significant Byte | e of the 16-bit T | MR5 Register    |            |        |          | 00000000             |  |

| FC0h    | T2RST    | _               | _                  | _                | _                 |                 | RSEL       | .<3:0> |          | 0000                 |  |

| FBFh    | T2CLKCON | _               | _                  | _                | _                 |                 | 0000       |        |          |                      |  |

| FBEh    | T2HLT    | PSYNC           | CPOL               | CSYNC            |                   | •               | MODE<4:0>  |        |          | 00000000             |  |

| FBDh    | T2CON    | ON              |                    | CKPS<2:0>        |                   |                 | OUTP       | S<3:0> |          | 00000000             |  |

| FBCh    | T2PR     | TMR2 Period R   | Register           |                  |                   | •               |            |        |          | 11111111             |  |

| FBBh    | T2TMR    | Holding Registe | er for the 8-bit T | MR2 Register     |                   |                 |            |        |          | 00000000             |  |

| FBAh    | T4RST    | _               | RSEL<3:0>          |                  |                   |                 |            | 0000   |          |                      |  |

| FB9h    | T4CLKCON | _               | _                  | _                | _                 |                 | CS<        | :3:0>  |          | 0000                 |  |

| FB8h    | T4HLT    | PSYNC           | CPOL               | CSYNC            |                   |                 | MODE<4:0>  |        |          | 00000000             |  |

| FB7h    | T4CON    | ON              |                    | CKPS<2:0>        |                   |                 | OUTP       | S<3:0> |          | 00000000             |  |

| FB6h    | T4PR     | TMR4 Period R   | Register           |                  |                   | •               |            |        |          | 11111111             |  |

| FB5h    | T4TMR    | Holding Registe | er for the 8-bit T | MR4 Register     |                   |                 |            |        |          | 00000000             |  |

| FB4h    | T6RST    | _               | _                  | _                | _                 |                 | RSEL       | .<3:0> |          | 0000                 |  |

| FB3h    | T6CLKCON | _               | _                  | _                | _                 |                 | CS<        | :3:0>  |          | 0000                 |  |

| FB2h    | T6HLT    | PSYNC           | CPOL               | CSYNC            |                   | •               | MODE<4:0>  |        |          | 00000000             |  |

| FB1h    | T6CON    | ON              |                    | CKPS<2:0>        |                   |                 | OUTPS<3:0> |        |          |                      |  |

| FB0h    | T6PR     | TMR6 Period R   | Register           |                  |                   | •               |            |        |          | 11111111             |  |

| FAFh    | T6TMR    | Holding Registe | er for the 8-bit T | MR6 Register     |                   |                 |            |        |          | 00000000             |  |

| FAEh    | CCPTMRS  | P4TSEL          | _<1:0>             | P3TSE            | EL<1:0>           | C2TSE           | EL<1:0>    | C1TS   | SEL<1:0> | 01010101             |  |

| FADh    | CCP1CAP  | _               | _                  | _                | _                 | _               | _          | CTS    | S<1:0>   | 00                   |  |

| FACh    | CCP1CON  | EN              | _                  | OUT              | FMT               |                 | MODE       | E<3:0> |          | 0-000000             |  |

| FABh    | CCPR1H   | Capture/Compa   | are/PWM Regis      | ster 1 (MSB)     |                   |                 |            |        |          | xxxxxxxx             |  |

| FAAh    | CCPR1L   | Capture/Compa   | are/PWM Regis      | ster 1 (LSB)     |                   |                 |            |        |          | xxxxxxxx             |  |

| FA9h    | CCP2CAP  | _               | _                  | _                | _                 | _               | _          | CTS    | S<1:0>   | 00                   |  |

| FA8h    | CCP2CON  | EN              | _                  | OUT              | FMT               |                 | MODE       | <3:0>  |          | 0-000000             |  |

| FA7h    | CCPR2H   | Capture/Compa   | are/PWM Regis      | ster 2 (MSB)     |                   | •               |            |        |          | xxxxxxx              |  |

| FA6h    | CCPR2L   | Capture/Compa   | are/PWM Regis      | ster 2 (LSB)     |                   |                 |            |        |          | xxxxxxxx             |  |

| FA5h    | PWM3CON  | EN              | _                  | OUT              | POL               | _               | _          | _      | _        | 0-00                 |  |

| FA4h    | PWM3DCH  |                 |                    |                  | DC                | <7:0>           |            |        |          | xxxxxxxx             |  |

| FA3h    | PWM3DCL  | DC<             | 9:8>               | _                | _                 | _               | _          | _      | _        | xx                   |  |

| FA2h    | PWM4CON  | EN              | _                  | OUT              | POL               | _               | _          | _      | _        | 0-00                 |  |

| FA1h    | PWM4DCH  |                 |                    |                  | DC                | 7:0>            |            |        |          | xxxxxxxx             |  |

| FA0h    | PWM4DCL  | DC<9            | 9:8>               | _                | _                 | _               | _          | _      | _        | xx                   |  |

| F9Fh    | BAUD1CON | ABDOVF          | RCIDL              | _                | SCKP              | BRG16           | _          | WUE    | ABDEN    | 01-00-00             |  |

| F9Eh    | TX1STA   | CSRC            | TX9                | TXEN             | SYNC              | SENDB           | BRGH       | TRMT   | TX9D     | 00000010             |  |

| F9Dh    | RC1STA   | SPEN            | RX9                | SREN             | CREN              | ADDEN           | FERR       | OERR   | RX9D     | 00000000             |  |

| F9Ch    | SP1BRGH  |                 |                    | EUSA             | RT1 Baud Rat      | e Generator, Hi | igh Byte   |        | •        | 00000000             |  |

$\textbf{Legend:} \qquad x = \text{unknown}, \ u = \text{unchanged}, \\ \textbf{—} = \text{unimplemented}, \ q = \text{value depends on condition}$

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F27K40 (28-pin variants).

## 11.1.2 CONTROL REGISTERS

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the following registers:

- NVMCON1 register

- NVMCON2 register

- · TABLAT register

- · TBLPTR registers

# 11.1.2.1 NVMCON1 and NVMCON2 Registers

The NVMCON1 register (Register 11-1) is the control register for memory accesses. The NVMCON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading NVMCON2 will read all '0's.

The NVMREG<1:0> control bits determine if the access will be to Data EEPROM Memory locations. PFM locations or User IDs, Configuration bits, Rev ID and Device ID. When NVMREG<1:0> = 00, any subsequent operations will operate on the Data EEPROM Memory. When NVMREG<1:0> = 10, any subsequent operations will operate on the program memory. When NVMREG<1:0> = x1, any subsequent operations will operate on the Configuration bits, User IDs, Rev ID and Device ID.

The FREE bit allows the program memory erase operation. When the FREE bit is set, an erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled. This bit is applicable only to the PFM and not to data EEPROM.

When set, the WREN bit will allow a program/erase operation. The WREN bit is cleared on power-up.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is successfully complete.

The WR control bit initiates erase/write cycle operation when the NVMREG<1:0> bits point to the Data EEPROM Memory location, and it initiates a write operation when the NVMREG<1:0> bits point to the PFM location. The WR bit cannot be cleared by firmware; it can only be set by firmware. Then the WR bit is cleared by hardware at the completion of the write operation.

The NVMIF Interrupt Flag bit of the PIR7 register is set when the write is complete. The NVMIF flag stays set until cleared by firmware.

#### 11.1.2.2 TABLAT – Table Latch Register

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 11.1.2.3 TBLPTR – Table Pointer Register

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22<sup>nd</sup> bit allows access to the Device ID, the User ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations on the TBLPTR affect only the low-order 21 bits.

#### 11.1.2.4 Table Pointer Boundaries

TBLPTR is used in reads, writes and erases of the Program Flash Memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory directly into the TABLAT register.

When a TBLWT is executed the byte in the TABLAT register is written, not to Flash memory but, to a holding register in preparation for a program memory write. The holding registers constitute a write block which varies depending on the device (see Table 11-3). The 3, 4, or 5 LSbs of the TBLPTRL register determine which specific address within the holding register block is written to. The MSBs of the Table Pointer have no effect during TBLWT operations.

When a program memory write is executed the entire holding register block is written to the Flash memory at the address determined by the MSbs of the TBLPTR. The 3, 4, or 5 LSBs are ignored during Flash memory writes. For more detail, see **Section 11.1.6** "Writing to **Program Flash Memory**".

Figure 11-3 describes the relevant boundaries of TBLPTR based on Program Flash Memory operations.

#### REGISTER 13-14: SCANLADRL: SCAN LOW ADDRESS LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0                | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|------------------------|---------|---------|---------|

|         |         |         | LADR<   | 7:0> <sup>(1, 2)</sup> |         |         |         |

| bit 7   |         |         |         |                        |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-0 LADR<7:0>: Scan Start/Current Address bits<sup>(1, 2)</sup>

Least Significant bits of the current address to be fetched from, value increments on each fetch of memory

**Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 13-15: SCANHADRU: SCAN HIGH ADDRESS UPPER BYTE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | HADR    | <21:16> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 HADR<21:16>: Scan End Address bits<sup>(1, 2)</sup>

Upper bits of the address at the end of the designated scan

**Note 1:** Registers SCANHADRU/H/L form a 22-bit value but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

## REGISTER 15-7: SLRCONX: SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRx7   | SLRx6   | SLRx5   | SLRx4   | SLRx3   | SLRx2   | SLRx1   | SLRx0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set 0' = Bit is cleared x = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0 **SLRx<7:0>**: Slew Rate Control on Pins Rx<7:0>, respectively

1 = Port pin slew rate is limited0 = Port pin slews at maximum rate

## TABLE 15-8: SLEW RATE CONTROL REGISTERS

|         | Device     |               |       |       |       |       |       |       |       |       |

|---------|------------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name    | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| SLRCONA | Х          | Х             | SLRA7 | SLRA6 | SLRA5 | SLRA4 | SLRA3 | SLRA2 | SLRA1 | SLRA0 |

| SLRCONB | Х          | Х             | SLRB7 | SLRB6 | SLRB5 | SLRB4 | SLRB3 | SLRB2 | SLRB1 | SLRB0 |

| SLRCONC | Х          | Х             | SLRC7 | SLRC6 | SLRC5 | SLRC4 | SLRC3 | SLRC2 | SLRC1 | SLRC0 |

| SLRCOND | Х          |               | _     | _     | _     | _     | _     | _     | _     | _     |

|         |            | Х             | SLRD7 | SLRD6 | SLRD5 | SLRD4 | SLRD3 | SLRD2 | SLRD1 | SLRD0 |

| SLRCONE | Х          |               | _     | _     | _     | _     | _     | _     | _     | _     |

|         |            | Х             | _     | _     | _     | _     | _     | SLRE2 | SLRE1 | SLRE0 |

#### REGISTER 15-8: INLVLx: INPUT LEVEL CONTROL REGISTER

| R/W-1/1 | R/W-1/1  | R/W-1/1 | R/W-1/1  | R/W-1/1  | R/W-1/1  | R/W-1/1  | R/W-1/1 |

|---------|----------|---------|----------|----------|----------|----------|---------|

| INLVLx7 | INLVLx6  | INLVLx5 | INLVLx4  | INLVLx3  | INLVLx2  | INLVLx1  | INLVLx0 |

| bit 7   | IINLVLXO | INLVLXS | IINLVLX4 | IINLVLXS | IINLVLXZ | IINLVLXI |         |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'1' = Bit is set 0' = Bit is cleared 0' = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0 **INLVLx<7:0>**: Input Level Select on Pins Rx<7:0>, respectively

1 = ST input used for port reads and interrupt-on-change

0 = TTL input used for port reads and interrupt-on-change

## TABLE 15-9: INPUT LEVEL PORT REGISTERS

|        | Dev        | /ice          |         |         |         |                        |                        |                        |                        |                        |

|--------|------------|---------------|---------|---------|---------|------------------------|------------------------|------------------------|------------------------|------------------------|

| Name   | 28<br>Pins | 40/44<br>Pins | Bit 7   | Bit 6   | Bit 5   | Bit 4                  | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0                  |

| INLVLA | Х          | Х             | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4                | INLVLA3                | INLVLA2                | INLVLA1                | INLVLA0                |

| INLVLB | Χ          | Х             | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4                | INLVLB3                | INLVLB2 <sup>(1)</sup> | INLVLB1 <sup>(1)</sup> | INLVLB0                |

| INLVLC | Χ          | Х             | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 <sup>(1)</sup> | INLVLC3 <sup>(1)</sup> | INLVLC2                | INLVLC1                | INLVLC0                |

| INLVLD | Χ          |               |         | -       | _       | _                      | _                      | _                      | -                      | _                      |

|        |            | Х             | INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4                | INLVLD3                | INLVLD2                | INLVLD1 <sup>(1)</sup> | INLVLD0 <sup>(1)</sup> |

| INLVLE | Χ          |               |         |         | 1       | 1                      | INLVLE3                | _                      |                        | 1                      |

|        |            | Х             |         | 1       | 1       | 1                      | INLVLE3                | INLVLE2                | INLVLE1                | INLVLE0                |

**Note 1:** Pins read the I<sup>2</sup>C ST inputs when MSSP inputs select these pins, and I<sup>2</sup>C mode is enabled.

REGISTER 17-2: RxyPPS: PIN Rxy OUTPUT SOURCE SELECTION REGISTER

| U-0   | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u     | R/W-0/u | R/W-0/u |  |

|-------|-----|-----|---------|---------|-------------|---------|---------|--|

| _     | _   | _   |         |         | RxyPPS<4:0> | •       |         |  |

| bit 7 |     |     | bi      |         |             |         |         |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 RxyPPS<4:0>: Pin Rxy Output Source Selection bits<sup>(1)</sup>

| D DDO 44.05 | Bin Danie Outroot Occurs |      |        | Devi | ce Cor | nfigura | tion   |      |   |

|-------------|--------------------------|------|--------|------|--------|---------|--------|------|---|

| RxyPPS<4:0> | Pin Rxy Output Source    | PIC1 | 8(L)F2 | 7K40 |        | PIC1    | 8(L)F4 | 7K40 |   |

| 5'b1 0111   | ADGRDB                   | Α    | _      | С    | Α      | _       | С      | _    | _ |

| 5'b1 0110   | ADGRDA                   | Α    | _      | С    | Α      | _       | С      | _    | _ |

| 5'b1 0101   | DSM                      | Α    | _      | С    | Α      | _       | _      | D    | _ |

| 5'b1 0100   | CLKR                     | _    | В      | С    | _      | В       | С      | _    | _ |

| 5'b1 0011   | TMR0                     | _    | В      | С    | _      | В       | С      | _    | _ |

| 5'b1 0010   | MSSP2 (SDO/SDA)          | _    | В      | С    | _      | В       | _      | D    | _ |

| 5'b1 0001   | MSSP2 (SCK/SCL)          | _    | В      | С    | _      | В       | _      | D    | _ |

| 5'b1 0000   | MSSP1 (SDO/SDA)          | _    | В      | С    | _      | В       | С      | _    | _ |

| 5'b0 1111   | MSSP1 (SCK/SCL)          | _    | В      | С    | _      | В       | С      | _    | _ |

| 5'b0 1110   | CMP2                     | Α    | _      | С    | Α      | _       | _      | _    | Е |

| 5'b0 1101   | CMP1                     | Α    | _      | С    | Α      | _       | _      | D    | _ |

| 5'b0 1100   | EUSART2 (RX)             | _    | В      | С    | _      | В       | _      | D    | _ |

| 5'b0 1011   | EUSART2 (TX)             | _    | В      | С    | _      | В       | _      | D    | _ |

| 5'b0 1010   | EUSART1 (RX)             | _    | В      | С    | _      | В       | С      | _    | _ |

| 5'b0 1001   | EUSART1 (TX)             | _    | В      | С    | _      | В       | С      | _    | _ |

| 5'b0 1000   | PWM4                     | Α    | _      | С    | Α      | _       | С      | _    | _ |

| 5'b0 0111   | PWM3                     | Α    | _      | С    | Α      | _       | _      | D    | _ |

| 5'b0 0110   | CCP2                     | _    | В      | С    | _      | В       | С      | _    | _ |

| 5'b0 0101   | CCP1                     | _    | В      | С    | _      | В       | С      | _    | _ |

| 5'b0 0100   | CWG1D                    | _    | В      | С    | _      | В       | _      | D    | _ |

| 5'b0 0011   | CWG1C                    | _    | В      | С    | _      | В       | _      | D    | _ |

| 5'b0 0010   | CWG1B                    | _    | В      | С    | _      | В       | _      | D    | _ |

| 5'b0 0001   | CWG1A                    | _    | В      | С    | _      | В       | С      | _    | _ |

| 5'b0 0000   | LATxy                    | Α    | В      | С    | Α      | В       | С      | D    | Е |

Note 1: PORTD is present only on the PIC18(L)F45/46K40 devices.

Data Bus Read Write SSPxBUF Rea **SSPxDATPPS** SDI **PPS** SSPSR Reg bit 0 Shift SDO **PPS RxyPPS** SS Control 2 (CKP, CKE) Enable **PPS** Clock Select Edge **SSPxSSPPS** Select SSPxCLKPPS(2) SSPM<3:0> T2\_match SCK **PPS** Prescaler Tosc Edge PPS 4, 16, 64 Select RxyPPS<sup>(1)</sup> **Baud Rate** TRIS bit Generator (SSPxADD) Note 1: Output selection for master mode 2: Input selection for slave mode

FIGURE 26-1: MSSP BLOCK DIAGRAM (SPI MODE)

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 26-2 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

PIC18(L)F27/47K40

#### **REGISTER 30-2: DAC1CON1: DAC DATA REGISTER**

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| _     | _   | _   |         |         | DAC1R<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 DAC1R<4:0>: Data Input Register for DAC bits

#### TABLE 30-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name     | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2     | Bit 1 | Bit 0  | Register on page |

|----------|-------|--------|-------|-------|-------------|-----------|-------|--------|------------------|

| DAC1CON0 | EN    | _      | OE1   | OE2   | PSS•        | <1:0>     | _     | NSS    | 428              |

| DAC1CON1 | _     | _      | _     |       |             | DAC1R<4:0 | >     |        | 429              |

| FVRCON   | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR<1:0> |           | ADFVF | R<1:0> | 423              |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

# 31.2.6 ADC CONVERSION PROCEDURE (BASIC MODE)

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRISx register)

- Configure pin as analog (Refer to the ANSELx register)

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- Select ADC input channel (precharge+acquisition)

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- Enable peripheral interrupt (PEIE bit)

- Enable global interrupt (GIE bit)<sup>(1)</sup>

- If ADACQ = 0, software must wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the ADGO bit.

- Wait for ADC conversion to complete by one of the following:

- · Polling the ADGO bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 31.3 "ADC Acquisition Requirements".

#### **EXAMPLE 31-1: ADC CONVERSION**

```

; This code block configures the ADC

; for polling, VDD and Vss references, FRC

; oscillator and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL ADCON1

B'11110000' ; Right justify,

MOVLW

;FRC oscillator

MOVWF

ADCON1

;Vdd and Vss Vref

BANKSEL TRISA

BSF

TRISA,0

;Set RAO to input

BANKSEL

ANSEL

BSF

ANSEL, 0 ; Set RAO to analog

BANKSEL

ADCON0

B'00000001' ;Select channel AN0

MOVLW

MOVWF

ADCON0

;Turn ADC On

SampleTime ;Acquisiton delay

CALL

ADCON0, ADGO ; Start conversion

BSF

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

$-1

;No, test again

BANKSEL

ADRESH

ADRESH,W ;Read upper 2 bits

MOVF

MOVWF

RESULTHI

;store in GPR space

BANKSEL

ADRESL

MOVF

ADRESL,W

;Read lower 8 bits

MOVWE

RESULTIO

;Store in GPR space

```

# PIC18(L)F27/47K40

| BCF              | Bit Clear                                             | ·f     |            |          |

|------------------|-------------------------------------------------------|--------|------------|----------|

| Syntax:          | BCF f, b                                              | o {,a} |            |          |

| Operands:        | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$ | 5      |            |          |

| Operation:       | $0 \rightarrow f < b >$                               |        |            |          |

| Status Affected: | None                                                  |        |            |          |

| Encoding:        | 1001                                                  | bbba   | ffff       | ffff     |

| Description:     | Bit 'b' in re                                         | 0      | s cleared. | aalaatad |

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See **Sec**tion 35.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

C7h

Example: BCF FLAG\_REG, 7, 0

Before Instruction FLAG\_REG =

After Instruction

FLAG\_REG = 47h

BN **Branch if Negative**

Syntax: BN n

Operands:  $-128 \le n \le 127$

Operation: if NEGATIVE bit is '1'  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0110 nnnn nnnn

Description: If the NEGATIVE bit is '1', then the program will branch.

> The 2's complement number '2n' is added to the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

2-cycle instruction.

Words: 1 Cycles: 1(2)

Q Cycle Activity: If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | 'n'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | 'n'          | Data    | operation |

Example: HERE BN Jump

Before Instruction

PC address (HERE)

After Instruction

If NEGATIVE

address (Jump)

address (HERE + 2)

#### 36.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 36.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 36.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 36.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

## 36.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# 37.4 AC Characteristics

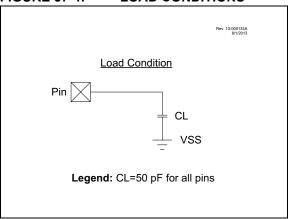

# FIGURE 37-4: LOAD CONDITIONS

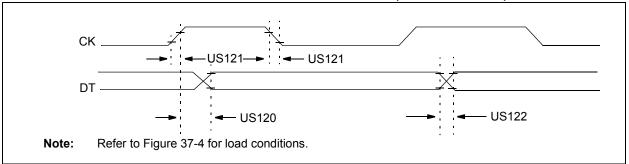

# FIGURE 37-14: EUSART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

# TABLE 37-21: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |          |                                                             |      |      |       |                                                  |

|---------------------------------------------------------|----------|-------------------------------------------------------------|------|------|-------|--------------------------------------------------|

| Param.<br>No.                                           | Symbol   | Characteristic                                              | Min. | Max. | Units | Conditions                                       |

| US120 TCKH2                                             | TCKH2DTV | V SYNC XMIT (Master and Slave) Clock high to data-out valid | _    | 80   | ns    | $3.0 \text{V} \leq \text{VDD} \leq 5.5 \text{V}$ |

|                                                         |          |                                                             | _    | 100  | ns    | $1.8V \leq V_{DD} \leq 5.5V$                     |

| US121 T                                                 | TCKRF    | Clock out rise time and fall time (Master mode)             | _    | 45   | ns    | $3.0 \text{V} \leq \text{VDD} \leq 5.5 \text{V}$ |

|                                                         |          |                                                             | _    | 50   | ns    | $1.8V \leq V_{DD} \leq 5.5V$                     |

| JS122                                                   | TDTRF    | Data-out rise time and fall time                            | _    | 45   | ns    | $3.0 \text{V} \leq \text{VDD} \leq 5.5 \text{V}$ |

|                                                         |          |                                                             | _    | 50   | ns    | $1.8V \leq V_{DD} \leq 5.5V$                     |

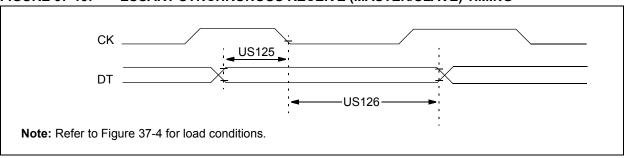

# FIGURE 37-15: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 37-22: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |          |                                                                   |      |      |       |            |

|---------------------------------------------------------|----------|-------------------------------------------------------------------|------|------|-------|------------|

| Param.<br>No.                                           | Symbol   | Characteristic                                                    | Min. | Max. | Units | Conditions |

| US125                                                   | TDTV2CKL | SYNC RCV (Master and Slave) Data-setup before CK ↓ (DT hold time) | 10   | 1    | ns    |            |

| US126                                                   | TCKL2DTL | Data-hold after CK ↓ (DT hold time)                               | 15   | _    | ns    |            |