Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K × 8                                                                    |

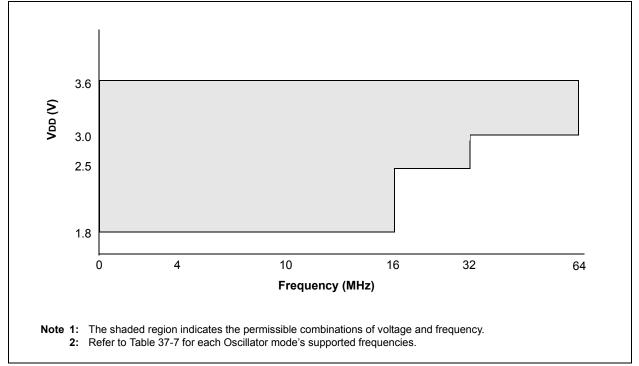

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27k40-e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

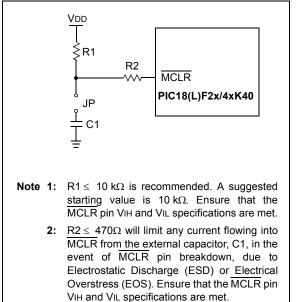

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

## FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

# 2.4 ICSP<sup>™</sup> Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 36.0 "Development Support"**.

# 6.0 POWER-SAVING OPERATION MODES

The purpose of the Power-Down modes is to reduce power consumption. There are three Power-Down modes:

- Doze mode

- Sleep mode

- Idle mode

# 6.1 Doze Mode

Doze mode allows for power saving by reducing CPU operation and program memory (PFM) access, without affecting peripheral operation. Doze mode differs from Sleep mode because the bandgap and system oscillators continue to operate, while only the CPU and PFM are affected. The reduced execution saves power by eliminating unnecessary operations within the CPU and memory.

When the Doze Enable (DOZEN) bit is set (DOZEN = 1), the CPU executes only one instruction cycle out of every N cycles as defined by the DOZE<2:0> bits of the CPUDOZE register. For example, if DOZE<2:0> = 001, the instruction cycle ratio is 1:4. The CPU and memory execute for one instruction cycle and then lay idle for three instruction cycles. During the unused cycles, the peripherals continue to operate at the system clock speed.

# 6.1.1 DOZE OPERATION

The Doze operation is illustrated in Figure 6-1. For this example:

- Doze enable (DOZEN) bit set (DOZEN = 1)

- DOZE<2:0> = 001 (1:4) ratio

- Recover-on-Interrupt (ROI) bit set (ROI = 1)

As with normal operation, the PFM fetches for the next instruction cycle. The Q-clocks to the peripherals continue throughout.

# 8.2 Register Definitions: Power Control

|                  | R/W/HS-0/q                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W/HC-1/q                                                                                                                                                                                         | R/W/HC-1/q                                                                                                                                           | R/W/HC-1/q                                                                                                                       | R/W/HC-1/q                                                               | R/W/HC-0/u                                          | R/W/HC-q/u         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|--------------------|

| STKOVF           | STKUNF                                                                                                                                                                                                                                                                                                                                                                                                                                  | WDTWV                                                                                                                                                                                              | RWDT                                                                                                                                                 | RMCLR                                                                                                                            | RI                                                                       | POR                                                 | BOR                |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                    |                                                                                                                                                      |                                                                                                                                  |                                                                          |                                                     | bit 0              |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                    |                                                                                                                                                      |                                                                                                                                  |                                                                          |                                                     |                    |

| •                | ared by hardwa                                                                                                                                                                                                                                                                                                                                                                                                                          | ire                                                                                                                                                                                                |                                                                                                                                                      | HS = Bit is se                                                                                                                   | et by hardware                                                           |                                                     |                    |

| R = Readable     | -                                                                                                                                                                                                                                                                                                                                                                                                                                       | W = Writable                                                                                                                                                                                       | bit                                                                                                                                                  |                                                                                                                                  | nented bit, read                                                         | <b>as</b> '0'                                       |                    |

| u = Bit is unch  | anged                                                                                                                                                                                                                                                                                                                                                                                                                                   | x = Bit is unkn                                                                                                                                                                                    | nown                                                                                                                                                 | -m/n = Value                                                                                                                     | at POR and BO                                                            | R/Value at all o                                    | other Resets       |

| ʻı' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                                                         | '0' = Bit is clea                                                                                                                                                                                  | ared                                                                                                                                                 | q = Value dep                                                                                                                    | pends on condit                                                          | ion                                                 |                    |

| bit 7            | STKOVE: Sta                                                                                                                                                                                                                                                                                                                                                                                                                             | ck Overflow Fla                                                                                                                                                                                    | og hit                                                                                                                                               |                                                                                                                                  |                                                                          |                                                     |                    |

|                  | 1 = A Stack                                                                                                                                                                                                                                                                                                                                                                                                                             | Overflow occur<br>Overflow has r                                                                                                                                                                   | rred (more CA                                                                                                                                        |                                                                                                                                  |                                                                          |                                                     |                    |

| bit 6            |                                                                                                                                                                                                                                                                                                                                                                                                                                         | ck Underflow F                                                                                                                                                                                     |                                                                                                                                                      |                                                                                                                                  |                                                                          |                                                     |                    |

|                  | 1 = A Stack                                                                                                                                                                                                                                                                                                                                                                                                                             | Underflow occ<br>Underflow has                                                                                                                                                                     | curred (more R                                                                                                                                       |                                                                                                                                  | ,                                                                        |                                                     |                    |

| bit 5            | WDTWV: Wat                                                                                                                                                                                                                                                                                                                                                                                                                              | chdog Window                                                                                                                                                                                       | Violation bit                                                                                                                                        |                                                                                                                                  |                                                                          |                                                     |                    |

|                  | 0 = A CLRWE                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                    | as issued whe                                                                                                                                        | n the WDT Re                                                                                                                     | '1' by firmware<br>set window was                                        | closed (set to '                                    | 0' in hardward     |

|                  | which u                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                    |                                                                                                                                                      |                                                                                                                                  |                                                                          |                                                     |                    |

| bit 4            |                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reset Flag bit                                                                                                                                                                                     |                                                                                                                                                      | ,                                                                                                                                |                                                                          |                                                     |                    |

| bit 4            | <b>RWDT</b> : WDT                                                                                                                                                                                                                                                                                                                                                                                                                       | overflow/time-o                                                                                                                                                                                    |                                                                                                                                                      | not occurred o                                                                                                                   | r set to '1' by fir<br>ɔ '0' in hardware                                 |                                                     | Reset occurs       |

| bit 4<br>bit 3   | <b>RWDT</b> : WDT<br>1 = A WDT 0<br>0 = A WDT 0                                                                                                                                                                                                                                                                                                                                                                                         | overflow/time-o                                                                                                                                                                                    | out Reset has o                                                                                                                                      | not occurred o                                                                                                                   |                                                                          |                                                     | Reset occurs       |

|                  | RWDT:         WDT           1 =         A WDT           0 =         A WDT <b>RMCLR:</b> MCL           1 =         A MCLR                                                                                                                                                                                                                                                                                                                | overflow/time-o<br>overflow/time-o<br>R Reset Flag I<br>Reset has not                                                                                                                              | out Reset has o<br>bit<br>t occurred or s                                                                                                            | not occurred o<br>occurred (set to<br>et to '1' by firm                                                                          | o '0' in hardware                                                        | e when a WDT                                        | Reset occurs       |

|                  | RWDT: WDT           1 =         A WDT           0 =         A WDT           0 =         A WDT           RMCLR: MCL           1 =         A MCLR           0 =         A MCLR           0 =         A MCLR           RI: RESET INS                                                                                                                                                                                                       | overflow/time-o<br>overflow/time-o<br>R Reset Flag I<br>Reset has not<br>Reset has occ<br>truction Flag b                                                                                          | out Reset has o<br>bit<br>t occurred or s<br>curred (set to '<br>it                                                                                  | not occurred o<br>occurred (set to<br>et to '1' by firn<br>0' in hardware                                                        | o 'o' in hardware<br>hware<br>when a MCLR                                | e when a WDT<br>Reset occurs)                       | Reset occurs       |

| bit 3            | RWDT: WDT           1 =         A WDT           0 =         A WDT           0 =         A WDT           RMCLR: MCL           1 =         A MCLR           0 =         A MCLR           0 =         A MCLR           1 =         A MCLR           RI: RESET INS         1 =           1 =         A RESET                                                                                                                                | Deverflow/time-op-<br>poverflow/time-op-<br>R Reset Flag I<br>Reset has not<br>Reset has occ<br>struction Flag b<br>r instruction ha<br>r instruction ha                                           | but Reset has o<br>bit<br>t occurred or s<br>curred (set to '<br>it<br>s not been exe                                                                | not occurred o<br>occurred (set to<br>et to '1' by firm<br>0' in hardware<br>ecuted or set t                                     | o '0' in hardware                                                        | e when a WDT<br>Reset occurs)<br>e                  |                    |

| bit 3            | RWDT:         WDT           1 =         A WDT           0 =         A WDT           0 =         A WDT           RMCLR:         MCL           1 =         A MCLR           0 =         A RESET           1 =         A RESET           0 =         A RESET | Deverflow/time-op-<br>poverflow/time-op-<br>R Reset Flag I<br>Reset has not<br>Reset has occ<br>struction Flag b<br>r instruction ha<br>r instruction ha                                           | but Reset has o<br>bit<br>t occurred or s<br>curred (set to '<br>it<br>s not been exe<br>has been exe                                                | not occurred o<br>occurred (set to<br>et to '1' by firm<br>0' in hardware<br>ecuted or set t                                     | o '0' in hardware<br>hware<br>when a MCLR<br>o '1' by firmware           | e when a WDT<br>Reset occurs)<br>e                  |                    |

| bit 3<br>bit 2   | RWDT: WDT           1 =         A WDT           0 =         A WDT           0 =         A WDT           0 =         A WDT           RMCLR: MCL         MCLR           1 =         A MCLR           0 =         A MCLR           RI: RESET Ins         A RESET           1 =         A RESET           0 =         A RESET           1 =         No Power-4           1 =         No Power-4                                             | overflow/time-o<br>overflow/time-o<br>Reset Flag I<br>Reset has not<br>Reset has occ<br>truction Flag b<br>instruction ha<br>instruction ha<br>instruction h<br>on Reset Statu-<br>er-on Reset occ | but Reset has o<br>bit<br>t occurred or s<br>curred (set to '<br>it<br>s not been exe<br>has been exe<br>s bit<br>curred or set t                    | not occurred o<br>occurred (set to<br>et to '1' by firm<br>0' in hardware<br>ecuted or set t<br>cuted (set to<br>o '1' by firmwa | o '0' in hardware<br>when a MCLR<br>o '1' by firmware<br>'0' in hardware | e when a WDT<br>Reset occurs)<br>e<br>e upon execut | ting <b>a</b> RESE |

| bit 3<br>bit 2   | RWDT:         WDT           1 =         A WDT (0)           0 =         A WDT (0)           RMCLR:         MCLR           1 =         A MCLR           0 =         A MCLR           RI:         RESET Ins           1 =         A RESET           0 =         A RESET           0 =         A RESET           0 =         A RESET           0 =         A Power                                                                         | overflow/time-o<br>overflow/time-o<br>Reset Flag I<br>Reset has not<br>Reset has occ<br>truction Flag b<br>instruction ha<br>instruction ha<br>instruction h<br>on Reset Statu-<br>er-on Reset occ | but Reset has o<br>bit<br>t occurred or s<br>curred (set to '<br>it<br>s not been exe<br>as been exe<br>s bit<br>curred or set t<br>urred (set to 'o | not occurred o<br>occurred (set to<br>et to '1' by firm<br>0' in hardware<br>ecuted or set t<br>cuted (set to<br>o '1' by firmwa | o '0' in hardware<br>when a MCLR<br>o '1' by firmware<br>'0' in hardware | e when a WDT<br>Reset occurs)<br>e<br>e upon execut | ting <b>a</b> RESE |

## REGISTER 8-2: PCON0: POWER CONTROL REGISTER 0

| Address           | Name       | Bit 7  | Bit 6   | Bit 5 | Bit 4         | Bit 3          | Bit 2        | Bit 1  | Bit 0     | <u>Value on</u><br>POR, BOR |  |

|-------------------|------------|--------|---------|-------|---------------|----------------|--------------|--------|-----------|-----------------------------|--|

| EB1h              | CWGINPPS   | _      | —       | _     | CWGINPPS<4:0> |                |              |        |           |                             |  |

| EB0h              | CCP2PPS    | _      | —       | _     |               | CCP2PPS<4:0>   |              |        |           |                             |  |

| EAFh              | CCP1PPS    | _      | _       | _     |               | CCP1PPS<4:0>   |              |        |           |                             |  |

| EAEh              | ADACTPPS   | _      | —       | _     |               | /              | ADACTPPS<4:( | )>     |           | 01100                       |  |

| EADh              | T6INPPS    | _      | _       | _     |               |                | T6INPPS<4:0> | •      |           | 01111                       |  |

| EACh              | T4INPPS    | _      | —       | _     |               |                | T4INPPS<4:0> | •      |           | 10101                       |  |

| EABh              | T2INPPS    | _      | —       | _     |               |                | T2INPPS<4:0> | •      |           | 10011                       |  |

| EAAh              | T5GPPS     | _      | —       | _     |               |                | T5GPPS<4:0>  |        |           | 01100                       |  |

| EA9h              | T5CKIPPS   | _      | —       | _     |               |                | T5CKIPPS<4:0 | >      |           | 10010                       |  |

| EA8h              | T3GPPS     | _      | —       | _     |               |                | T3GPPS<4:0>  |        |           | 10000                       |  |

| EA7h              | T3CKIPPS   | _      | —       | _     |               |                | T3CKIPPS<4:0 | >      |           | 10000                       |  |

| EA6h              | T1GPPS     | _      | —       | _     |               |                | T1GPPS<4:0>  |        |           | 01101                       |  |

| EA5h              | T1CKIPPS   | _      | —       | _     |               |                | T1CKIPPS<4:0 | >      |           | 10000                       |  |

| EA4h              | TOCKIPPS   | _      | —       | _     |               |                | T0CKIPPS<4:0 | >      |           | 00100                       |  |

| EA3h              | INT2PPS    | _      | —       | _     | INT2PPS<4:0>  |                |              |        |           | 01010                       |  |

| EA2h              | INT1PPS    | _      | —       | _     | INT1PPS<4:0>  |                |              |        |           |                             |  |

| EA1h              | INTOPPS    | _      | —       | _     | INTOPPS<4:0>  |                |              |        |           |                             |  |

| EA0h              | PPSLOCK    | _      | —       | _     | —             | —              | —            | —      | PPSLOCKED | 0                           |  |

| E9Fh              | BAUD2CON   | ABDOVF | RCIDL   | _     | SCKP          | BRG16          | _            | WUE    | ABDEN     | 01-00-00                    |  |

| E9Eh              | TX2STA     | CSRC   | TX9     | TXEN  | SYNC          | SENDB          | BRGH         | TRMT   | TX9D      | 00000010                    |  |

| E9Dh              | RC2STA     | SPEN   | RX9     | SREN  | CREN          | ADDEN          | FERR         | OERR   | RX9D      | 00000000                    |  |

| E9Ch              | SP2BRGH    |        |         | EUSA  | RT2 Baud Rat  | e Generator, H | igh Byte     |        |           | 00000000                    |  |

| E9Bh              | SP2BRGL    |        |         | EUSA  | ART2 Baud Rat | e Generator, L | ow Byte      |        |           | 00000000                    |  |

| E9Ah              | TX2REG     |        |         |       | EUSART2 Tra   | ansmit Registe | r            |        |           | 00000000                    |  |

| E99h              | RC2REG     |        |         |       | EUSART2 Re    | eceive Registe | r            |        |           | 00000000                    |  |

| E98h              | SSP2CON3   | ACKTIM | PCIE    | SCIE  | BOEN          | SDAHT          | SBCDE        | AHEN   | DHEN      | 00000000                    |  |

| E97h              | SSP2CON2   | GCEN   | ACKSTAT | ACKDT | ACKEN         | RCEN           | PEN          | RSEN   | SEN       | 00000000                    |  |

| E96h              | SSP2CON1   | WCOL   | SSPOV   | SSPEN | CKP           |                | SSPN         | 1<3:0> |           | 00000000                    |  |

| E95h              | SSP2STAT   | SMP    | CKE     | D/A   | Р             | S              | R/W          | UA     | BF        | 00000000                    |  |

| E94h              | SSP2MSK    |        |         |       | MSP           | <7:0>          |              |        |           | 11111111                    |  |

| E93h              | SSP2ADD    |        |         |       | ADE           | )<7:0>         |              |        |           | 00000000                    |  |

| E92h              | SSP2BUF    |        |         |       | BUF           | <7:0>          |              |        |           | xxxxxxxx                    |  |

| E91h              | SSP2SSPPS  | _      | —       | —     |               | :              | SSPSSPPS<4:( | )>     |           | 00101                       |  |

| E90h              | SSP2DATPPS | —      | —       | —     |               | S              | SPDATPPS<4:  | 0>     |           | 10100                       |  |

| E8Fh              | SSP2CLKPPS | —      | —       | —     |               | S              | SPCLKPPS<4:  | 0>     |           | 10011                       |  |

| E8Eh              | TX2PPS     | —      | —       | —     |               |                | TXPPS<4:0>   |        |           | 10110                       |  |

| E8Dh              | RX2PPS     | _      | _       | —     |               |                | RXPPS<4:0>   |        |           | 10111                       |  |

| E8Ch<br>-<br>E7Eh | _          |        |         |       | Unimpl        | emented        |              |        |           | _                           |  |

## TABLE 10-5: REGISTER FILE SUMMARY FOR PIC18(L)F27/47K40 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not available on LF devices.

2: Not available on PIC18(L)F27K40 (28-pin variants).

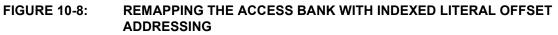

# 10.7.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the first 96 locations of Access RAM (00h to 5Fh) are mapped. Rather than containing just the contents of the bottom section of Bank 0, this mode maps the contents from a user defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 10.4.2 "Access Bank"**). An example of Access Bank remapping in this addressing mode is shown in Figure 10-8.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use direct addressing as before.

# 10.8 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 35.2 "Extended Instruction Set**".

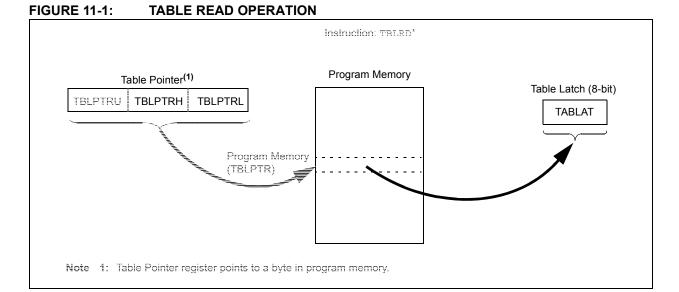

## 11.1.1 TABLE READS AND TABLE WRITES

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is eight bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register. Figure 11-1 shows the operation of a table read.

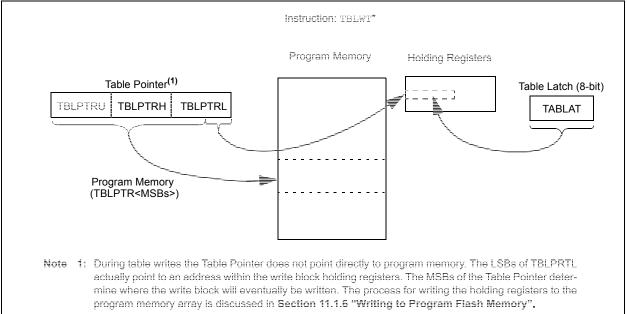

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in **Section 11.1.6 "Writing to Program Flash Memory"**. Figure 11-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. Tables containing data, rather than program instructions, are not required to be word aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

# FIGURE 11-2: TABLE WRITE OPERATION

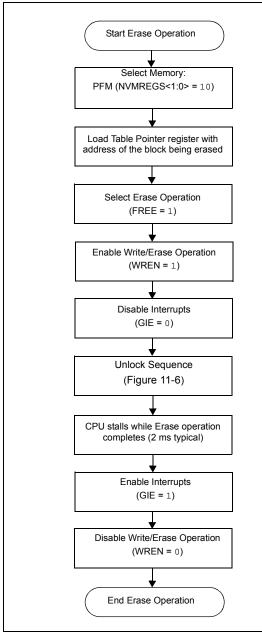

#### FIGURE 11-7: PFM ROW ERASE FLOWCHART

## 11.1.6 WRITING TO PROGRAM FLASH MEMORY

The programming write block size is described in Table 11-3. Word or byte programming is not supported. Table writes are used internally to load the holding registers needed to program the Flash memory. There are only as many holding registers as there are bytes in a write block. Refer to Table 11-3 for write latch size.

Since the table latch (TABLAT) is only a single byte, the TBLWT instruction needs to be executed multiple times for each programming operation. The write protection state is ignored for this operation. All of the table write operations will essentially be short writes because only the holding registers are written. NVMIF is not affected while writing to the holding registers.

After all the holding registers have been written, the programming operation of that block of memory is started by configuring the NVMCON1 register for a program memory write and performing the long write sequence.

If the PFM address in the TBLPTR is write-protected or if TBLPTR points to an invalid location, the WR bit is cleared without any effect and the WREER is signaled.

The long write is necessary for programming the internal Flash. CPU operation is suspended during a long write cycle and resumes when the operation is complete. The long write operation completes in one instruction cycle. When complete, WR is cleared in hardware and NVMIF is set and an interrupt will occur if NVMIE is also set. The latched data is reset to all '1s'. WREN is not changed.

The internal programming timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

| Name      | Bit 7      | Bit 6     | Bit 5  | Bit 4   | Bit 3  | Bit 2    | Bit 1   | Bit 0   | Register<br>on Page |

|-----------|------------|-----------|--------|---------|--------|----------|---------|---------|---------------------|

| CRCACCH   | ACC<15:8>  |           |        |         |        |          |         | 152     |                     |

| CRCACCL   | ACC<7:0>   |           |        |         |        |          |         | 153     |                     |

| CRCCON0   | EN         | GO        | BUSY   | ACCM    | —      | _        | SHIFTM  | FULL    | 151                 |

| CRCCON1   |            | DLEN<     | 3:0>   |         |        | PLE      | N<3:0>  |         | 151                 |

| CRCDATH   |            |           |        | DATA    | <15:8> |          |         |         | 152                 |

| CRCDATL   |            |           |        | DATA    | <7:0>  |          |         |         | 152                 |

| CRCSHIFTH |            |           |        | SHIFT   | <15:8> |          |         |         | 153                 |

| CRCSHIFTL |            |           |        | SHIF    | T<7:0> |          |         |         | 153                 |

| CRCXORH   | X<15:8>    |           |        |         |        |          | 154     |         |                     |

| CRCXORL   | X<7:1> —   |           |        |         |        | 154      |         |         |                     |

| PMD0      | SYSCMD     | FVRMD     | HLVDMD | CRCMD   | SCANMD | NVMMD    | CLKRMD  | IOCMD   | 68                  |

| SCANCON0  | SCANEN     | SCANGO    | BUSY   | INVALID | INTM   | —        | MODE    | =<1:0>  | 155                 |

| SCANHADRU | —          | —         |        |         | HADF   | R<21:16> |         |         | 157                 |

| SCANHADRH |            |           |        | HADR    | <15:8> |          |         |         | 158                 |

| SCANHADRL |            |           |        | HADF    | R<7:0> |          |         |         | 158                 |

| SCANLADRU | —          | —         |        |         | LADF   | R<21:16> |         |         | 156                 |

| SCANLADRH | LADR<15:8> |           |        |         |        |          | 156     |         |                     |

| SCANLADRL |            |           |        | LADF    | R<7:0> |          |         |         | 157                 |

| SCANTRIG  | —          | —         | _      | _       |        | TSEL     | _<3:0>  |         | 159                 |

| INTCON    | GIE/GIEH   | PEIE/GIEL | IPEN   | _       | —      | INT2EDG  | INT1EDG | INT0EDG | 170                 |

| PIR7      | SCANIF     | CRCIF     | NVMIF  |         |        |          |         | CWG1IF  | 178                 |

| PIE7      | SCANIE     | CRCIE     | NVMIE  | _       | _      | _        | _       | CWG1IE  | 186                 |

| IPR7      | SCANIP     | CRCIP     | NVMIP  | _       | _      | _        | _       | CWG1IP  | 194                 |

| TABLE 13-5: | SUMMARY OF REGISTERS ASSOCIATED WITH CRC |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the CRC module.

| U-0             | U-0                                                  | U-0              | U-0              | U-0              | R/W-1/1          | R/W-1/1         | R/W-1/1 |

|-----------------|------------------------------------------------------|------------------|------------------|------------------|------------------|-----------------|---------|

|                 | —                                                    |                  |                  | _                | TMR5GIP          | TMR3GIP         | TMR1GIP |

| bit 7           |                                                      |                  |                  |                  |                  | •               | bit 0   |

|                 |                                                      |                  |                  |                  |                  |                 |         |

| Legend:         |                                                      |                  |                  |                  |                  |                 |         |

| R = Readable    | bit                                                  | W = Writable     | bit              | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at P | OR                                                   | '1' = Bit is set |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 7-3         | Unimplomon                                           | ted: Read as '   | ۰ <b>،</b>       |                  |                  |                 |         |

|                 | Unimplemen                                           | ted: Read as '   | J                |                  |                  |                 |         |

| bit 2           | <b>TMR5GIP:</b> TM<br>1 = High prio<br>0 = Low prior | •                | rupt Priority bi | t                |                  |                 |         |

| bit 1           | <b>TMR3GIP:</b> TM<br>1 = High prio<br>0 = Low prior | •                | rupt Priority bi | t                |                  |                 |         |

| bit 0           | <b>TMR1GIP:</b> TM<br>1 = High prio<br>0 = Low prior | 2                | rupt Priority bi | t                |                  |                 |         |

# REGISTER 14-23: IPR5: PERIPHERAL INTERRUPT PRIORITY REGISTER 5

## 15.2.5 SLEW RATE CONTROL

The SLRCONx register (Register 15-7) controls the slew rate option for each port pin. Slew rate for each port pin can be controlled independently. When an SLRCONx bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONx bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

## 15.2.6 INPUT THRESHOLD CONTROL

The INLVLx register (Register 15-8) controls the input voltage threshold for each of the available PORTx input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTx register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-8 for more information on threshold levels.

| Note: | Changing the input threshold selection      |

|-------|---------------------------------------------|

|       | should be performed while all peripheral    |

|       | modules are disabled. Changing the          |

|       | threshold level during the time a module is |

|       | active may inadvertently generate a         |

|       | transition associated with an input pin,    |

|       | regardless of the actual voltage level on   |

|       | that pin.                                   |

## 15.2.7 WEAK PULL-UP CONTROL

The WPUx register (Register 15-5) controls the individual weak pull-ups for each port pin.

## 15.2.8 EDGE SELECTABLE INTERRUPT-ON-CHANGE

An interrupt can be generated by detecting a signal at the port pin that has either a rising edge or a falling edge. Any individual pin can be configured to generate an interrupt. The interrupt-on-change module is present on all the pins that are common between 28-pin and 40/44-pin devices. For further details about the IOC module refer to **Section 16.0 "Interrupt-on-Change**".

# 15.3 PORTE Registers

Depending on the device selected, PORTE is implemented in two different ways.

## 15.3.1 PORTE ON 40/44-PIN DEVICES

For PIC18(L)F4xK40 devices, PORTE is a 4-bit wide port. Three pins (RE0, RE1 and RE2) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's.

The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

TRISE controls the direction of the REx pins, even when they are being used as analog pins. The user must make sure to keep the pins configured as inputs when using them as analog inputs. RE<2:0> bits have other registers associated with them (i.e., ANSELE, WPUE, INLVLE, SLRCONE and ODCONE). The functionality is similar to the other ports.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

| Note: | On a Power-on Reset, RE<2:0> a | are |

|-------|--------------------------------|-----|

|       | configured as analog inputs.   |     |

The fourth pin of PORTE (MCLR/VPP/RE3) is an inputonly pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input-only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming.

RE3 in PORTE register is a read-only bit and will read '1' when MCLRE = 1 (i.e., Master Clear enabled).

| Note: | On a Power-on Reset, RE3 is enabled as |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|

|       | a digital input only if Master Clear   |  |  |  |  |  |  |

|       | functionality is disabled.             |  |  |  |  |  |  |

#### EXAMPLE 15-2: INITIALIZING PORTE

| CLRF  | PORTE  | ; Initialize PORTE by   |

|-------|--------|-------------------------|

|       |        | ; clearing output       |

|       |        | ; data latches          |

| CLRF  | LATE   | ; Alternate method      |

|       |        | ; to clear output       |

|       |        | ; data latches          |

| CLRF  | ANSELE | ; Configure analog pins |

|       |        | ; for digital only      |

| MOVLW | 05h    | ; Value used to         |

|       |        | ; initialize data       |

|       |        | ; direction             |

| MOVWF | TRISE  | ; Set RE<0> as input    |

|       |        | ; RE<1> as output       |

|       |        | ; RE<2> as input        |

|       |        |                         |

# 15.3.2 PORTE ON 28-PIN DEVICES

For PIC18(L)F2xK40 devices, PORTE is only available when Master Clear functionality is disabled (MCLRE = 0). In this case, PORTE is a single bit, inputonly port comprised of RE3 only. The pin operates as previously described. RE3 in PORTE register is a readonly bit and will read '1' when MCLRE = 1 (i.e., Master Clear enabled).

## 17.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- CCP module

- Note: The I<sup>2</sup>C default input pins are I<sup>2</sup>C and SMBus compatible. RB1 and RB2 are additional pins. RC4 and RC3 are default MMP1 pins and are SMBus compatible. Clock and data signals can be routed to any pin, however pins without I<sup>2</sup>C compatibility will operate at standard TTL/ST logic levels as selected by the INVLV register.

## 17.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 17-1.

## EXAMPLE 17-1: PPS LOCK SEQUENCE

| ; Disable interrupts:<br>BCF INTCON,GIE                                                      |

|----------------------------------------------------------------------------------------------|

| ; Bank to PPSLOCK register<br>BANKSEL PPSLOCK<br>MOVLB PPSLOCK<br>MOVLW 55h                  |

| ; Required sequence, next 4 instructions<br>MOVWF PPSLOCK<br>MOVLW AAh<br>MOVWF PPSLOCK      |

| ; Set PPSLOCKED bit to disable writes<br>; Only a BSF instruction will work<br>BSF PPSLOCK,0 |

| ; Enable Interrupts<br>BSF INTCON,GIE                                                        |

#### EXAMPLE 17-2: PPS UNLOCK SEQUENCE

```

; Disable interrupts:

BCF

INTCON, GIE

; Bank to PPSLOCK register

BANKSEL PPSLOCK

MOVLB

PPSLOCK

MOVIW

55h

; Required sequence, next 4 instructions

MOVWF

PPSLOCK

MOVLW

AAh

MOVWF

PPSLOCK

; Clear PPSLOCKED bit to enable writes

; Only a BCF instruction will work

BCF

PPSLOCK,0

; Enable Interrupts

BSF

INTCON.GIE

```

## 17.5 PPS One-Way Lock

Using the PPS1WAY Configuration bit, the PPS settings can be locked in. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

# 17.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

## 17.7 Effects of a Reset

A device Power-on-Reset (POR) clears all PPS input and output selections to their default values. All other Resets leave the selections unchanged. Default input selections are shown in the **Section "Pin Allocation Tables"**. The PPS one-way is also removed.

## 18.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the T016BIT bit of the T0CON register.

#### 18.1.1 16-BIT MODE

The register pair TMR0H:TMR0L, increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

# 18.1.1.1 Timer0 Reads and Writes in 16-Bit Mode

In 16-bit mode, to avoid rollover between reading high and low registers, the TMR0H register is a buffered copy of the actual high byte of Timer0, which is neither directly readable nor writable (see Figure 18-1). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte was valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

## 18.1.2 8-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

In 8-bit mode, the value of TMR0L is compared to that of the Period buffer, a copy of TMR0H, on each clock cycle. When the two values match, the following events happen:

- TMR0\_out goes high for one prescaled clock period

- TMR0L is reset

- The contents of TMR0H are copied to the period buffer

In 8-bit mode, the TMR0L and TMR0H registers are both directly readable and writable. The TMR0L register is cleared on any device Reset, while the TMR0H register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- Any device Reset Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or

- Brown-out Reset (BOR)

## 18.1.3 COUNTER MODE

In Counter mode, the prescaler is normally disabled by setting the T0CKPS bits of the T0CON1 register to '0000'. Each rising edge of the clock input (or the output of the prescaler if the prescaler is used) increments the counter by '1'.

## 18.1.4 TIMER MODE

In Timer mode, the Timer0 module will increment every instruction cycle as long as there is a valid clock signal and the T0CKPS bits of the T0CON1 register (Register 18-2) are set to '0000'. When a prescaler is added, the timer will increment at the rate based on the prescaler value.

## 18.1.5 ASYNCHRONOUS MODE

When the TOASYNC bit of the TOCON1 register is set (TOASYNC = '1'), the counter increments with each rising edge of the input source (or output of the prescaler, if used). Asynchronous mode allows the counter to continue operation during Sleep mode provided that the clock also continues to operate during Sleep.

#### 18.1.6 SYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is clear (T0ASYNC = 0), the counter clock is synchronized to the system clock (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

## 18.2 Clock Source Selection

The T0CS<2:0> bits of the T0CON1 register are used to select the clock source for Timer0. Register 18-2 displays the clock source selections.

## 18.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, Timer0 operates as a timer and will increment on multiples of the clock source, as determined by the Timer0 prescaler.

#### 18.2.2 EXTERNAL CLOCK SOURCE

When an external clock source is selected, Timer0 can operate as either a timer or a counter. Timer0 will increment on multiples of the rising edge of the external clock source, as determined by the Timer0 prescaler.

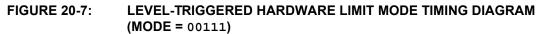

# 20.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

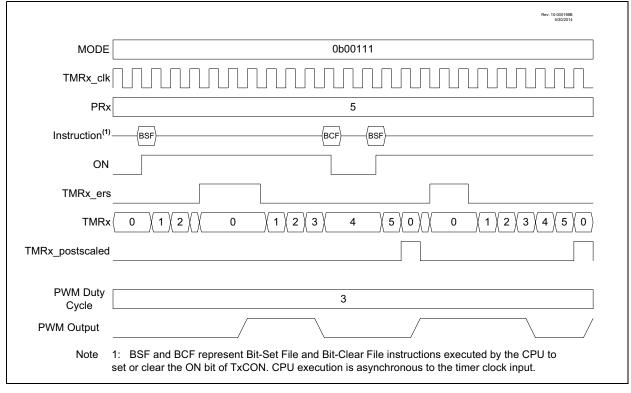

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 20-7. Selecting MODE<4:0> = 0.0110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 0.0111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

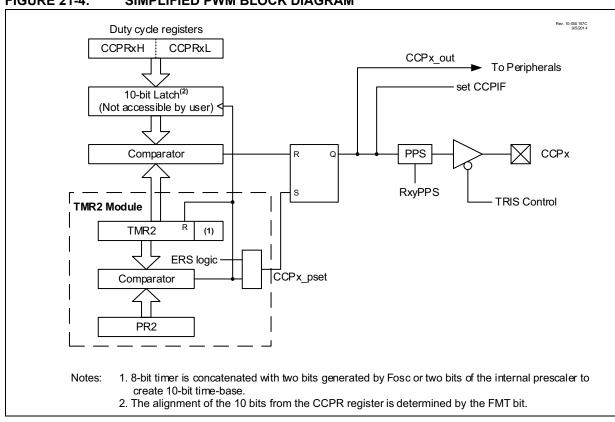

## FIGURE 21-4: SIMPLIFIED PWM BLOCK DIAGRAM

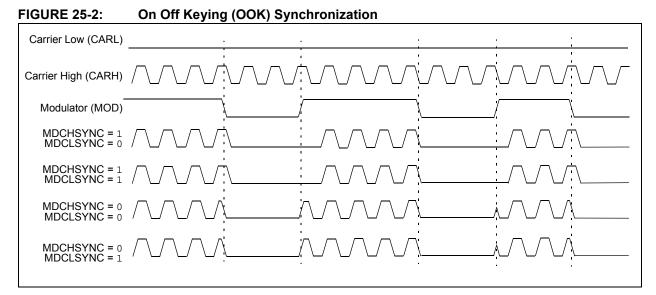

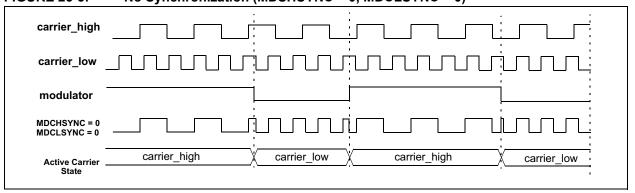

# FIGURE 25-3: No Synchronization (MDSHSYNC = 0, MDCLSYNC = 0)

FIGURE 25-4: Carrier High Synchronization (MDSHSYNC = 1, MDCLSYNC = 0)

| carrier_high                 |                                                                       |

|------------------------------|-----------------------------------------------------------------------|

| carrier_low                  |                                                                       |

| modulator                    |                                                                       |

| MDCHSYNC = 1<br>MDCLSYNC = 0 |                                                                       |

| Active Carrier<br>State      | carrier_high /_both\carrier_low \ / carrier_high / both \ carrier_low |

#### 26.9.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 26-19 displays a standard waveform of a 7-bit address slave transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCL line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- Slave software reads the <u>ACKTIM</u> bit of SSPxCON3 register, and R/W and D/A of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: <u>SSPx</u>BUF cannot be loaded until after the ACK.

- 13. Slave sets the CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the ninth SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

Note: Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

## 33.2 HLVD Setup

To set up the HLVD module:

- Select the desired HLVD trip point by writing the value to the HLVDSEL<3:0> bits of the HLVDCON1 register.

- Depending on the application to detect high-voltage peaks or low-voltage drops or both, set the HLVDINTH or HLVDINTL bit appropriately.

- 3. Enable the HLVD module by setting the HLVDEN bit.

- Clear the HLVD interrupt flag (PIR2 register), which may have been set from a previous interrupt.

- 5. If interrupts are desired, enable the HLVD interrupt by setting the HLVDIE in the PIE2 register and GIE bits.

An interrupt will not be generated until the HLVDRDY bit is set.

Note: Before changing any module settings (HLVDINTH, HLVDINTL, HLVDSEL<3:0>), first disable the module (HLVDEN = 0), make the changes and re-enable the module. This prevents the generation of false HLVD events.

# 33.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and consume static current. The total current consumption, when enabled, is specified in electrical specification Parameter **D206** (Table 37-3).

Depending on the application, the HLVD module does not need to operate constantly. To reduce current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After such a check, the module could be disabled.

# 33.4 HLVD Start-up Time

The internal reference voltage of the HLVD module, specified in electrical specification (Table 37-17), may be used by other internal circuitry, such as the programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TFVRST, is an interval that is independent of device clock speed. It is specified in electrical specification (Table 37-17).

The HLVD interrupt flag is not enabled until TFVRST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval (see Figure 33-2 or Figure 33-3).

## 35.1.1 STANDARD INSTRUCTION SET

| ADD     | LW                              | ADD litera              | al to W                                                                                   |  |            |  |  |  |

|---------|---------------------------------|-------------------------|-------------------------------------------------------------------------------------------|--|------------|--|--|--|

| Syntax: |                                 | ADDLW                   | ADDLW k                                                                                   |  |            |  |  |  |

| Opera   | ands:                           | $0 \le k \le 255$       | $0 \leq k \leq 255$                                                                       |  |            |  |  |  |

| Opera   | ation:                          | $(W) + k \rightarrow V$ | $(W) + k \to W$                                                                           |  |            |  |  |  |

| Status  | s Affected:                     | N, OV, C, D             | N, OV, C, DC, Z                                                                           |  |            |  |  |  |

| Enco    | ding:                           | 0000                    | 1111 kkkk                                                                                 |  | k kkkk     |  |  |  |

| Descr   | ription:                        |                         | The contents of W are added to the<br>8-bit literal 'k' and the result is placed in<br>W. |  |            |  |  |  |

| Word    | s:                              | 1                       | 1                                                                                         |  |            |  |  |  |

| Cycle   | s:                              | 1                       |                                                                                           |  |            |  |  |  |

| Q Cy    | cle Activity:                   |                         |                                                                                           |  |            |  |  |  |

| _       | Q1                              | Q2                      | Q3                                                                                        |  | Q4         |  |  |  |

|         | Decode                          | Read<br>literal 'k'     | Process<br>Data                                                                           |  | Write to W |  |  |  |

| Exam    | nle <sup>.</sup>                | ADDLW 1                 | .5h                                                                                       |  |            |  |  |  |

|         | <u>ipie</u> .<br>Before Instruc |                         | . 511                                                                                     |  |            |  |  |  |

| W = 10h |                                 |                         |                                                                                           |  |            |  |  |  |

|         |                                 |                         |                                                                                           |  |            |  |  |  |

|         |                                 |                         |                                                                                           |  |            |  |  |  |

| /       | After Instructio                |                         |                                                                                           |  |            |  |  |  |

| 1       | After Instructio<br>W =         | 25h                     |                                                                                           |  |            |  |  |  |

| ADDWF             | ADD W to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:           | ADDWF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Operation:        | $(W) + (f) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Status Affected:  | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Encoding:         | 0010 01da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Description:      | Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 35.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |  |  |  |  |  |  |