Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.6K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27k40t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

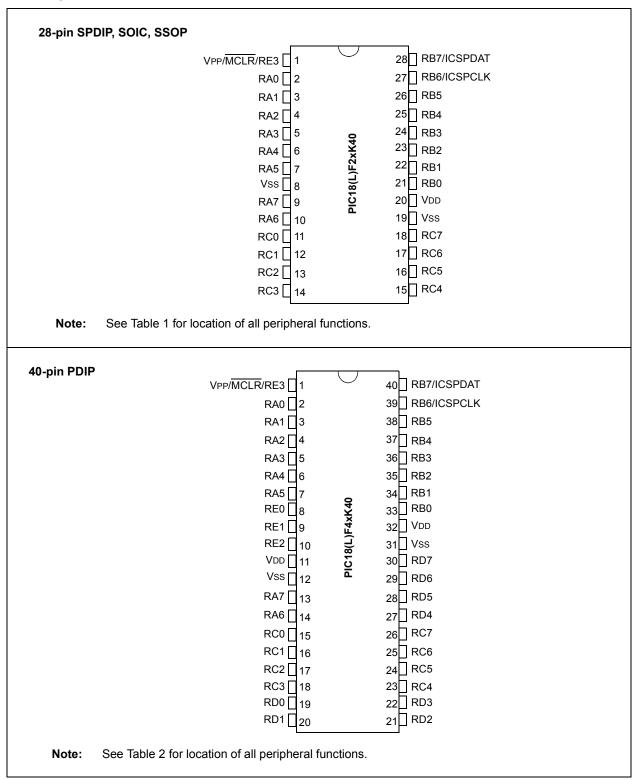

#### **Pin Diagrams**

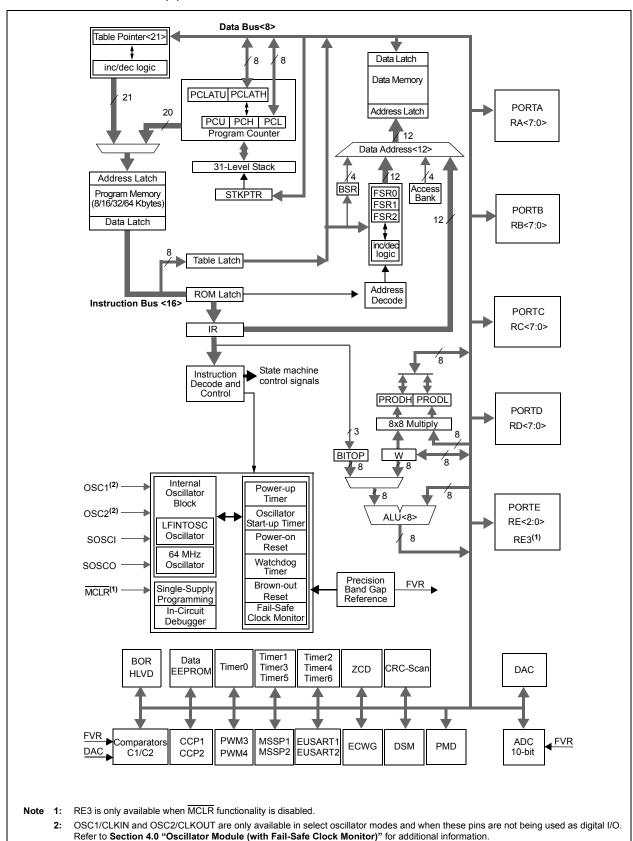

FIGURE 1-1: PIC18(L)F2X/4XK40 FAMILY BLOCK DIAGRAM

#### 4.4.2 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the clock switch interrupt flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

FIGURE 4-6: CLOCK SWITCH (CSWHOLD = 0)

Note 1: CSWIF is asserted coincident with NOSCR; interrupt is serviced at OSC#2 speed.

2: The assertion of NOSCR is hidden from the user because it appears only for the duration of the switch.

#### FIGURE 4-7: CLOCK SWITCH (CSWHOLD = 1)

Note 1: CSWIF is asserted coincident with NOSCR, and may be cleared before or after clearing CSWHOLD = 0.

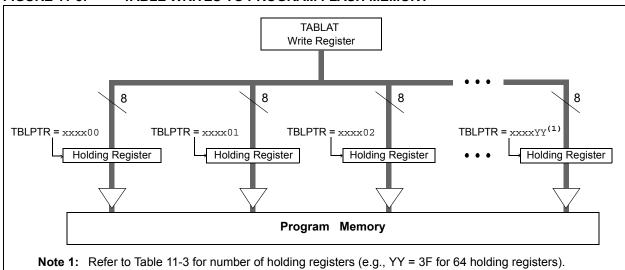

FIGURE 11-8: TABLE WRITES TO PROGRAM FLASH MEMORY

### 11.1.6.1 Program Flash Memory Write Sequence

The sequence of events for programming an internal program memory location should be:

- Read appropriate number of bytes into RAM. Refer to Table 11-2 for Write latch size.

- 2. Update data values in RAM as necessary.

- Load Table Pointer register with address being erased.

- 4. Execute the block erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- Write the n-byte block into the holding registers with auto-increment. Refer to Table 11-2 for Write latch size.

- 7. Set NVMREG<1:0> bits to point to program memory.

- Clear FREE bit and set WREN bit in NVMCON1 register.

- Disable interrupts.

- 10. Execute the unlock sequence (see Section 11.1.4 "NVM Unlock Sequence").

- 11. WR bit is set in NVMCON1 register.

- 12. The CPU will stall for the duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

This procedure will require about 6 ms to update each write block of memory. An example of the required code is given in Example 11-4.

**Note:** Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the bytes in the holding registers.

#### REGISTER 14-12: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0/0     | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |  |  |

|-------------|---------|-----|-----|-----|-----|---------|---------|--|--|

| HLVDIE      | ZCDIE   | _   | _   | _   | _   | C2IE    | C1IE    |  |  |

| bit 7 bit 0 |         |     |     |     |     |         |         |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 HLVDIE: HLVD Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 6 ZCDIE: Zero-Cross Detect Interrupt Enable bit

1 = Enabled0 = Disabled

bit 5-2 **Unimplemented:** Read as '0'

bit 1 C2IE: Comparator 2 Interrupt Enable bit

1 = Enabled0 = Disabled

bit 0 C1IE: Comparator 1 Interrupt Enable bit

1 = Enabled0 = Disabled

#### REGISTER 14-16: PIE6: PERIPHERAL INTERRUPT ENABLE REGISTER 6

|   | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---|-------|-----|-----|-----|-----|-----|---------|---------|

|   | _     | _   | _   | _   | _   |     | CCP2IE  | CCP1IE  |

| k | oit 7 |     |     |     |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-2 **Unimplemented:** Read as '0'

bit 1 CCP2IE: ECCP2 Interrupt Enable bit

1 = Enabled 0 = Disabled

bit 0 CCP1IE: ECCP1 Interrupt Enable bit

1 = Enabled

0 = Disabled

TABLE 20-1: TIMER2 OPERATING MODES

| Mode            | MODE  | <4:0>                    | Output                   | Onevetion                                                 |                              | Timer Control |                            |

|-----------------|-------|--------------------------|--------------------------|-----------------------------------------------------------|------------------------------|---------------|----------------------------|

| wode            | <4:3> | <2:0>                    | Operation                | Operation                                                 | Start                        | Reset         | Stop                       |

|                 |       | 000                      |                          | Software gate (Figure 20-4) ON = 1                        |                              | _             | ON = 0                     |

|                 |       | 001                      | Period<br>Pulse          | Hardware gate, active-high<br>(Figure 20-5)               | ON = 1 and —<br>TMRx_ers = 1 |               | ON = 0 or<br>TMRx_ers = 0  |

|                 |       | 010                      | 1 0100                   | Hardware gate, active-low                                 | ON = 1 and<br>TMRx_ers = 0   | _             | ON = 0 or<br>TMRx_ers = 1  |

| Free<br>Running | 00    | 011                      |                          | Rising or falling edge Reset                              |                              | TMRx_ers      |                            |

| Period          | 00    | 100                      | Period                   | Rising edge Reset (Figure 20-6)                           |                              | TMRx_ers ↑    | ON = 0                     |

|                 |       | 101                      | Pulse                    | Falling edge Reset                                        |                              | TMRx_ers ↓    |                            |

|                 |       | 110                      | with<br>Hardware         | Low level Reset                                           | ON = 1                       | TMRx_ers = 0  | ON = 0 or<br>TMRx_ers = 0  |

|                 |       | 111                      | Reset                    | High level Reset (Figure 20-7)                            |                              | TMRx_ers = 1  | ON = 0 or<br>TMRx_ers = 1  |

|                 |       | 000                      | One-shot                 | Software start (Figure 20-8)                              | ON = 1                       |               |                            |

|                 |       | 001                      | Edge                     | Rising edge start (Figure 20-9)                           | ON = 1 and<br>TMRx_ers ↑     | _             |                            |

|                 |       | 010                      | triggered<br>start       | Falling edge start                                        | ON = 1 and<br>TMRx_ers↓      |               |                            |

|                 |       | 011                      | (Note 1)                 | Any edge start                                            | ON = 1 and<br>TMRx_ers ↓     | _             | ON = 0<br>or<br>Next clock |

| One-shot        | 01    | 100                      | Edge                     | Rising edge start and<br>Rising edge Reset (Figure 20-10) | ON = 1 and<br>TMRx_ers ↑     | TMRx_ers ↑    | after TMRx = PRx           |

|                 |       | 101                      | triggered<br>start       | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers↓      | TMRx_ers ↓    | (Note 2)                   |

|                 |       | 110                      | and<br>hardware<br>Reset | Rising edge start and<br>Low level Reset (Figure 20-11)   | ON = 1 and<br>TMRx_ers ↑     | TMRx_ers = 0  |                            |

|                 |       | 111                      | (Note 1)                 | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers↓      | TMRx_ers = 1  |                            |

|                 |       | 000                      |                          | Rese                                                      | rved                         |               |                            |

|                 |       | 001                      | Edge                     | Rising edge start<br>(Figure 20-12)                       | ON = 1 and<br>TMRx_ers ↑     |               | ON = 0<br>or               |

| Mono-stable     |       | 010                      | triggered<br>start       | Falling edge start                                        | ON = 1 and<br>TMRx_ers↓      | _             | Next clock<br>after        |

|                 |       | 011                      | (Note 1)                 | Any edge start                                            | ON = 1 and<br>TMRx_ers ↓     | _             | TMRx = PRx<br>(Note 3)     |

| Reserved        | 10    | 100                      |                          | Rese                                                      | rved                         |               |                            |

| Reserved        |       | 101                      |                          | Rese                                                      | rved                         |               |                            |

|                 |       | 110                      | Level<br>triggered       | High level start and<br>Low level Reset (Figure 20-13)    | ON = 1 and<br>TMRx_ers = 1   | TMRx_ers = 0  | ON = 0 or                  |

| One-shot        |       | start and hardward Reset |                          | Low level start & ON = High level Reset TMRx_6            |                              | TMRx_ers = 1  | Held in Reset<br>(Note 2)  |

| Reserved        | 11    | xxx                      |                          | Rese                                                      | rved                         |               |                            |

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

<sup>2:</sup> When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

<sup>3:</sup> When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

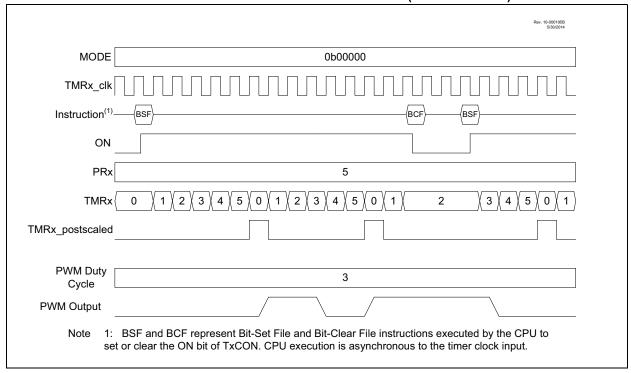

#### 20.5 Operation Examples

Unless otherwise specified, the following notes apply to the following timing diagrams:

- Both the prescaler and postscaler are set to 1:1 (both the CKPS and OUTPS bits in the TxCON register are cleared).

- The diagrams illustrate any clock except Fosc/4 and show clock-sync delays of at least two full cycles for both ON and Timer2\_ers. When using Fosc/4, the clock-sync delay is at least one instruction period for Timer2\_ers; ON applies in the next instruction period.

- The PWM Duty Cycle and PWM output are illustrated assuming that the timer is used for the PWM function of the CCP module as described in **Section**

**21.0** "Capture/Compare/PWM Module". The signals are not a part of the Timer2 module.

#### 20.5.1 SOFTWARE GATE MODE

This mode corresponds to legacy Timer2 operation. The timer increments with each clock input when ON=1 and does not increment when ON=0. When the TMRx count equals the PRx period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 20-4. With PRx = 5, the counter advances until TMRx = 5, and goes to zero with the next clock.

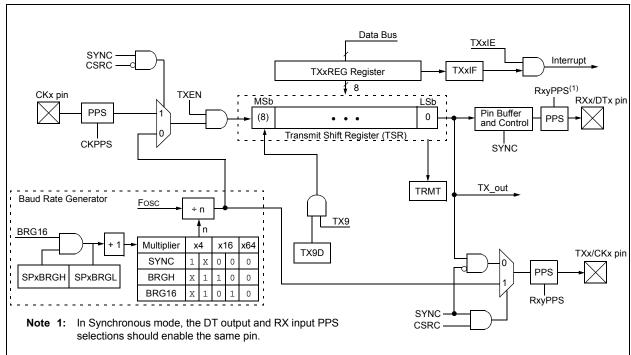

# 27.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

Note: The PIC18(L)F27/47K40 devices have two EUSARTs. Therefore, all information in this section refers to both EUSART 1 and EUSART 2.

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode useful communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers.

These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- · Two-character input buffer

- · One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- · Received character framing error detection

- · Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- · 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 27-1 and Figure 27-2.

#### FIGURE 27-1: EUSART TRANSMIT BLOCK DIAGRAM

# 27.3 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 4.3.2.3 "Internal Oscillator Frequency Adjustment"** for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see Section 27.4.1 "Auto-Baud Detect"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

#### 27.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 27.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPFN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXxSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

#### 27.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TXx/CKx pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 27.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDxCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 27.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RXx/DTx pin. The RXx/DTx and TXx/CKx pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXxREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXxREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXxREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

**Note:** The TSR register is not mapped in data memory, so it is not available to the user.

### 27.5.1.4 Synchronous Master Transmission Setup:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 27.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- If interrupts are desired, set the TXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXxREG register.

#### 31.2 ADC Operation

#### 31.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. A conversion may be started by any of the following:

- Software setting the ADGO bit of ADCON0 to '1'

- An external trigger (selected by Register 31-3)

- A continuous-mode retrigger (see section Section 31.5.8 "Continuous Sampling mode")

Note: The ADGO bit should not be set in the same instruction that turns on the ADC. Refer to Section 31.2.6 "ADC Conversion Procedure (Basic Mode)".

#### 31.2.2 COMPLETION OF A CONVERSION

When any individual conversion is complete, the value already in ADRES is written into ADPREV (if ADPSIS = 1) and the new conversion results appear in ADRES. When the conversion completes, the ADC module will:

- Clear the ADGO bit (unless the ADCONT bit of ADCON0 is set)

- · Set the ADIF Interrupt Flag bit

- · Set the ADMATH bit

- Update ADACC

When ADDSEN = 0 then after every conversion, or when ADDSEN = 1 then after every other conversion, the following events occur:

- · ADERR is calculated

- ADTIF is set if ADERR calculation meets threshold comparison

Importantly, filter and threshold computations occur after the conversion itself is complete. As such, interrupt handlers responding to ADIF should check ADTIF before reading filter and threshold results.

#### 31.2.3 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

### 31.2.4 EXTERNAL TRIGGER DURING SLEEP

If the external trigger is received during sleep while ADC clock source is set to the FRC, ADC module will perform the conversion and set the ADIF bit upon completion.

If an external trigger is received when the ADC clock source is something other than FRC, the trigger will be recorded, but the conversion will not begin until the device exits Sleep.

#### 31.2.5 AUTO-CONVERSION TRIGGER

The Auto-conversion Trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the ADGO bit is set by hardware.

The Auto-conversion Trigger source is selected with the ADACT<4:0> bits of the ADACT register.

Using the Auto-conversion Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met. See Table 31-2 for auto-conversion sources.

TABLE 31-2: ADC AUTO-CONVERSION TABLE

| Source<br>Peripheral | Description                                           |  |  |  |  |

|----------------------|-------------------------------------------------------|--|--|--|--|

| ADCACTPPS            | Pin selected by ADCACTPPS                             |  |  |  |  |

| TMR0                 | Timer0 overflow condition                             |  |  |  |  |

| TMR1/3/5             | Timer1/3/5 overflow condition                         |  |  |  |  |

| TMR2/4/6             | Match between Timer2/4/6 postscaled value and PR2/4/6 |  |  |  |  |

| CCP1/2               | CCP1/2 output                                         |  |  |  |  |

| PWM3/4               | PWM3/4 output                                         |  |  |  |  |

| C1/2                 | Comparator C1/2 output                                |  |  |  |  |

| IOC                  | Interrupt-on-change interrupt trigger                 |  |  |  |  |

| ADERR                | Read of ADERRH register                               |  |  |  |  |

| ADRESH               | Read of ADRESH register                               |  |  |  |  |

| ADPCH                | Write of ADPCH register                               |  |  |  |  |

#### 31.4.1 CVD OPERATION

A CVD operation begins with the ADC's internal and hold capacitor sample  $(C_{HOID})$ disconnected from the path which connects it to the external capacitive sensor node. While disconnected, C<sub>HOLD</sub> is precharged to V<sub>DD</sub> or V<sub>SS</sub>, while the path to the sensor node is also discharged to VDD or Vss. Typically, this node is discharged to the level opposite that of CHOLD. When the precharge phase is complete, the VDD/VSS bias paths for the two nodes are shut off and CHOLD and the path to the external sensor node are re-connected, at which time the acquisition phase of the CVD operation begins. During acquisition, a capacitive voltage divider is formed between the precharged CHOLD and sensor nodes, which results in a final voltage level setting on CHOLD which is determined by the capacitances and precharge levels of the two nodes. After acquisition, the ADC converts the voltage level on CHOLD. This process is then repeated with the selected precharge levels for both the CHOLD and the inverted sensor nodes. Figure 31-7 shows the waveform for two inverted CVD measurements, which is known as differential CVD measurement.

Precharge Acquisition Conversion Precharge Acquisition Conversion

Voo

Voo

Vss

First Sample

Second Sample

#### REGISTER 33-2: HLVDCON0: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER 0

| R/W-0/0     | U-0 | R-x | R-x | U-0 | U-0 | R/W-0/0 | R/W-0/0 |  |  |

|-------------|-----|-----|-----|-----|-----|---------|---------|--|--|

| EN          | _   | OUT | RDY | _   | _   | INTH    | INTL    |  |  |

| bit 7 bit 0 |     |     |     |     |     |         |         |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 EN: High/Low-voltage Detect Power Enable bit

1 = Enables HLVD, powers up HLVD circuit and supporting reference circuitry

0 = Disables HLVD, powers down HLVD and supporting circuitry

bit 6 Unimplemented: Read as '0'

bit 5 **OUT:** HLVD Comparator Output bit

1 = Voltage  $\leq$  selected detection limit (HLVDL $\leq$ 3:0>)

0 = Voltage ≥ selected detection limit (HLVDL<3:0>)

bit 4 RDY: Band Gap Reference Voltages Stable Status Flag bit

1 = Indicates HLVD Module is ready and output is stable

0 = Indicates HLVD Module is not ready

bit 3-2 **Unimplemented:** Read as '0'

bit 1 INTH: HLVD Positive going (High Voltage) Interrupt Enable

1 = HLVDIF will be set when voltage ≥ selected detection limit (HLVDSEL<3:0>)

0 = HLVDIF will not be set

bit 0 INTL: HLVD Negative going (Low Voltage) Interrupt Enable

1 = HLVDIF will be set when voltage ≤ selected detection limit (HLVDSEL<3:0>)

0 = HLVDIF will not be set

#### TABLE 33-2: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

| Name     | Bit 7    | Bit 6     | Bit 5  | Bit 4 | Bit 3  | Bit 2    | Bit 1   | Bit 0   | Register<br>on Page |  |

|----------|----------|-----------|--------|-------|--------|----------|---------|---------|---------------------|--|

| HLVDCON0 | EN       | _         | OUT    | RDY   | _      | -        | INTH    | INTL    | 482                 |  |

| HLVDCON1 | _        | _         | _      | _     |        | SEL<3:0> |         |         |                     |  |

| INTCON   | GIE/GIEH | PEIE/GIEL | IPEN   | -     | _      | INT2EDG  | INT1EDG | INT0EDG | 170                 |  |

| PIR2     | HLVDIF   | ZCDIF     | -      | _     | _      | _        | C2IF    | C1IF    | 173                 |  |

| PIE2     | HLVDIE   | ZCDIE     | -      | _     | _      | _        | C2IE    | C1IE    | 181                 |  |

| IPR2     | HLVDIP   | ZCDIP     | _      | -     | _      | _        | C2IP    | C1IP    | 189                 |  |

| PMD0     | SYSCMD   | FVRMD     | HLVDMD | CRCMD | SCANMD | NVMMD    | CLKRMD  | IOCMD   | 68                  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

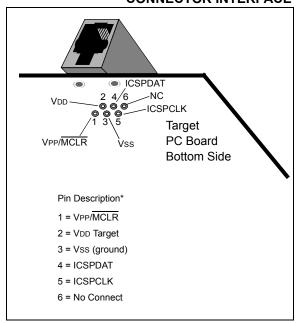

# 34.0 IN-CIRCUIT SERIAL PROGRAMMING™ (ICSP™)

ICSP<sup>TM</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>TM</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP $^{TM}$  refer to the "PIC18(L)F2X/4XK40 Memory Programming Specification" (DS40001772).

## 34.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

### 34.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC® Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at V<sub>IL</sub> for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 8.6** "MCLR" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

#### 34.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP™ header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 34-1.

FIGURE 34-1: ICD RJ-11 STYLE CONNECTOR INTERFACE

Another connector often found in use with the PICkit™ programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 34-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 34-3 for more information.

# PIC18(L)F27/47K40

POP Pop Top of Return Stack

Syntax: POP

Operands: None

Operation:  $(TOS) \rightarrow bit bucket$

Status Affected: None

Encoding: 0000 0000 0000 0110

Description:

The TOS value is pulled off the return stack and is discarded. The TOS value then becomes the previous value that was pushed onto the return stack.

This instruction is provided to enable

the user to properly manage the return stack to incorporate a software stack.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2        | Q3      | Q4        |

|--------|-----------|---------|-----------|

| Decode | No        | POP TOS | No        |

|        | operation | value   | operation |

Example: POP

GOTO NEW

Before Instruction

TOS = 0031A2h Stack (1 level down) = 014332h

After Instruction

TOS = 014332h PC = NEW PUSH Push Top of Return Stack

Syntax: PUSH Operands: None

Operation:  $(PC + 2) \rightarrow TOS$

Status Affected: None

Encoding: 0000 0000 0000 0101

Description: The PC + 2 is pushed onto the top of

the return stack. The previous TOS value is pushed down on the stack. This instruction allows implementing a software stack by modifying TOS and then pushing it onto the return stack.

then pushing it onto the return stack.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3        | Q4        |

|--------|--------------|-----------|-----------|

| Decode | PUSH         | No        | No        |

|        | PC + 2 onto  | operation | operation |

|        | return stack |           | -         |

Example: PUSH

Before Instruction

TOS = 345Ah PC = 0124h

After Instruction

PC = 0126h TOS = 0126h Stack (1 level down) = 345Ah

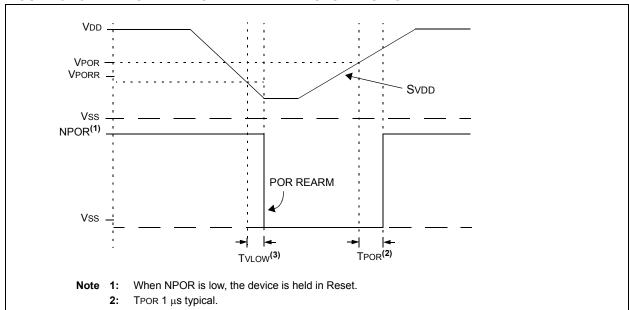

3: TvLow 2.7 μs typical.

FIGURE 37-12: T0CKI T1CKI TMR0 or TMR1

**TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS**

#### TABLE 37-19: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

|              | Standard Operating Conditions (unless otherwise stated) Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                           |                                                          |              |                                           |      |        |       |                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------|--------------|-------------------------------------------|------|--------|-------|---------------------|

| Param<br>No. | Sym.                                                                                                                  |                           | Characteristi                                            | c            | Min.                                      | Тур† | Max.   | Units | Conditions          |

| 40*          | Тт0Н                                                                                                                  | T0CKI High I              | Pulse Width                                              | No Prescaler | 0.5 Tcy + 20                              | -    |        | ns    |                     |

|              |                                                                                                                       | With Prescaler            |                                                          | 10           | _                                         | _    | ns     |       |                     |

| 41*          | T⊤0L                                                                                                                  | T0CKI Low F               | Pulse Width                                              | No Prescaler | 0.5 Tcy + 20                              | _    | _      | ns    |                     |

|              |                                                                                                                       |                           | With Prescaler                                           |              | 10                                        | _    | _      | ns    |                     |

| 42*          | Тт0Р                                                                                                                  | T0CKI Period              | d                                                        |              | Greater of:<br>20 or <u>Tcy + 40</u><br>N |      | _      | ns    | N = prescale value  |

| 45*          | Тт1Н                                                                                                                  | T1CKI High<br>Time        | Synchronous, No Prescaler<br>Synchronous, with Prescaler |              | 0.5 Tcy + 20                              | _    | _      | ns    |                     |

|              |                                                                                                                       |                           |                                                          |              | 15                                        | _    | _      | ns    |                     |

|              |                                                                                                                       |                           | Asynchronous                                             |              | 30                                        | _    | _      | ns    |                     |

| 46*          | T⊤1L                                                                                                                  | T1CKI Low                 | Synchronous, N                                           | No Prescaler | 0.5 Tcy + 20                              | _    | _      | ns    |                     |

|              |                                                                                                                       | Time                      | Synchronous, with Prescaler                              |              | 15                                        | _    | _      | ns    |                     |

|              |                                                                                                                       |                           | Asynchronous                                             |              | 30                                        | _    | _      | ns    |                     |

| 47*          | Тт1Р                                                                                                                  | T1CKI Input<br>Period     | Synchronous                                              | Synchronous  |                                           | _    | _      | ns    | N = prescale value  |

|              |                                                                                                                       |                           | Asynchronous                                             | _            | 60                                        | _    | _      | ns    |                     |

| 49*          | TCKEZTMR1                                                                                                             | Delay from E<br>Increment | xternal Clock Ed                                         | ge to Timer  | 2 Tosc                                    | _    | 7 Tosc | _     | Timers in Sync mode |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

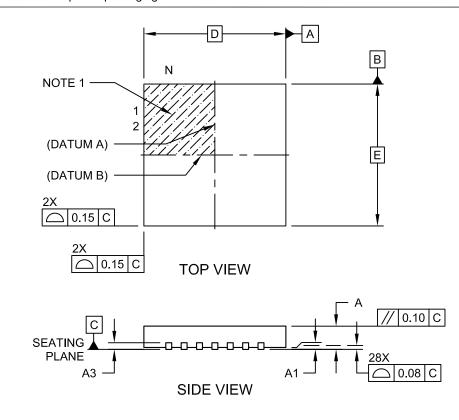

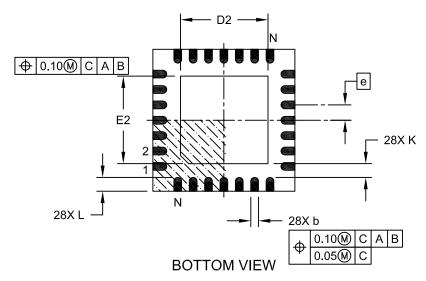

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-105C Sheet 1 of 2

#### Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277

Technical Support:

http://www.microchip.com/support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX

Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

**Los Angeles** Mission Viejo, CA

Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY

Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 **China - Qingdao** Tel: 86-532-8502-7355

Fax: 86-532-8502-7205 China - Shanghai

Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040

Fax: 86-756-3210049 India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

Germany - Garching Tel: 49-8931-9700 Germany - Haan

Tel: 49-2129-3766400 Germany - Heilbronn

Tel: 49-7131-67-3636 **Germany - Karlsruhe** Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Rosenheim** Tel: 49-8031-354-560

Israel - Ra'anana

Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw

Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820