Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.6K × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27k40t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 8.13 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON0 registers are updated to indicate the cause of the Reset. Table 8-3 shows the Reset conditions of these registers.

| Condition                          | Program<br>Counter    | STATUS<br>Register <sup>(2,3)</sup> | PCON0<br>Register |

|------------------------------------|-----------------------|-------------------------------------|-------------------|

| Power-on Reset                     | 0                     | -110 0000                           | 0011 110x         |

| Brown-out Reset                    | 0                     | -110 0000                           | 0011 11u0         |

| MCLR Reset during normal operation | 0                     | -uuu uuuu                           | uuuu Ouuu         |

| MCLR Reset during Sleep            | 0                     | -10u uuuu                           | uuuu Ouuu         |

| WDT Time-out Reset                 | 0                     | -0uu uuuu                           | սսս0 սսսս         |

| WDT Wake-up from Sleep             | PC + 2                | -00u uuuu                           | uuuu uuuu         |

| WWDT Window Violation Reset        | 0                     | -uuu uuuu                           | uu0u uuuu         |

| Interrupt Wake-up from Sleep       | PC + 2 <sup>(1)</sup> | -10u 0uuu                           | uuuu uuuu         |

| RESET Instruction Executed         | 0                     | -uuu uuuu                           | uuuu u0uu         |

| Stack Overflow Reset (STVREN = 1)  | 0                     | -uuu uuuu                           | luuu uuuu         |

| Stack Underflow Reset (STVREN = 1) | 0                     | -uuu uuuu                           | uluu uuuu         |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit (GIE) is set the return address is pushed on the stack and PC is loaded with the corresponding interrupt vector (depending on source, high or low priority) after execution of PC + 2.

2: If a Status bit is not implemented, that bit will be read as '0'.

3: Status bits Z, C, DC are reset by POR/BOR (Register 10-2).

#### 9.2 Independent Clock Source

The WWDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of WDTE<1:0> Configuration bits.

If WDTE = 2'blx, then the clock source will be enabled depending on the WDTCCS<2:0> Configuration bits.

If WDTE = 2'b01, the SEN bit should be set by software to enable WWDT, and the clock source is enabled by the WDTCS bits in the WDTCON1 register.

Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See **Section 37.0 "Electrical Specifications"** for LFINTOSC and MFINTOSC tolerances.

#### 9.3 WWDT Operating Modes

The Windowed Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.3.1 WWDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WWDT is always on.

WWDT protection is active during Sleep.

#### 9.3.2 WWDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WWDT is on, except in Sleep.

WWDT protection is not active during Sleep.

#### 9.3.3 WWDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WWDT is controlled by the SEN bit of the WDTCON0 register.

WWDT protection is unchanged by Sleep. See Table 9-1 for more details.

| TABLE 9-1: | WWDT OPERATING MODES |

|------------|----------------------|

|------------|----------------------|

| WDTE<1:0> | SEN | Device<br>Mode | WWDT<br>Mode |

|-----------|-----|----------------|--------------|

| 11        | Х   | Х              | Active       |

| 1.0       | 37  | Awake          | Active       |

| 10        | Х   | Sleep          | Disabled     |

| 01        | 1   | Х              | Active       |

| 01        | 0   | Х              | Disabled     |

| 00        | Х   | Х              | Disabled     |

#### 9.4 Time-out Period

If the WDTCPS<4:0> Configuration bits default to 5 'b11111, then the WDTPS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). If any value other than the default value is assigned to WDTCPS<4:0> Configuration bits, then the timer period will be based on the WDTCPS<4:0> bits in the CONFIG3L register. After a Reset, the default time-out period is 2s.

#### 9.5 Watchdog Window

The Windowed Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WWDT Reset, similar to a WWDT time out. See Figure 9-2 for an example.

The window size is controlled by the WINDOW<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

The five Most Significant bits of the WDTTMR register are used to determine whether the window is open, as defined by the WINDOW<2:0> bits of the WDTCON1 register.

In the event of a window violation, a Reset will be generated and the WDTWV bit of the PCON0 register will be cleared. This bit is set by a POR or can be set in firmware.

#### 9.6 Clearing the WWDT

The WWDT is cleared when any of the following conditions occur:

- Any Reset

- Valid CLRWDT instruction is executed

- Device enters Sleep

- Exit Sleep by Interrupt

- WWDT is disabled

- Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1

registers

#### 9.6.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WWDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation regardless of whether the window is open or not.

See Table 9-2 for more information.

| R/W-0/0                 | R/W/HC-0/0                                      | R-0                        | R-1                         | R/W-0/0           | U-0                                | R/W-0/0          | R/W-0/0                     |

|-------------------------|-------------------------------------------------|----------------------------|-----------------------------|-------------------|------------------------------------|------------------|-----------------------------|

| SCANEN                  | SCANGO BUSY INVALID                             |                            | INTM                        | —                 | MODE                               | <1:0>            |                             |

| bit 7                   |                                                 |                            |                             |                   |                                    |                  | bit                         |

|                         |                                                 |                            |                             |                   |                                    |                  |                             |

| Legend:<br>R = Readable | hit                                             | W = Writable               | hit                         | II – I Inimpler   | nented bit, read                   | as 'O'           |                             |

| u = Bit is unch         |                                                 | x = Bit is unkr            |                             |                   | at POR and BO                      |                  | ther Resets                 |

| (1) = Bit is unend      | ungeu                                           | 0' = Bit is clear          |                             |                   | eared by hardwa                    |                  |                             |

| 1 Bit io oot            |                                                 | o Ditio die                |                             | THO BILLIOU       |                                    |                  |                             |

| bit 7                   | SCANEN: Sca                                     | anner Enable k             | oit <sup>(1)</sup>          |                   |                                    |                  |                             |

|                         | 1 = Scanner is                                  |                            |                             |                   |                                    |                  |                             |

|                         |                                                 |                            | rnal states are             | reset             |                                    |                  |                             |

| bit 6                   |                                                 | anner GO bit <sup>(2</sup> |                             | N/M will be acc   | essed accordin                     | a to MDv and (   | tata passad t               |

|                         |                                                 | peripheral.                | reauy signal, r             |                   |                                    | g to MDX and t   | iala passeu l               |

|                         |                                                 | perations will i           | not occur                   |                   |                                    |                  |                             |

| bit 5                   |                                                 | er Busy Indica             |                             |                   |                                    |                  |                             |

|                         |                                                 | ycle is in proce           | ess<br>te (or never sta     | arted)            |                                    |                  |                             |

| bit 4                   |                                                 | Inner Abort Sig            |                             | arteu)            |                                    |                  |                             |

|                         |                                                 |                            |                             | n invalid addre   | ss <sup>(6)</sup> or the scan      | ner was not se   | tup correctly <sup>(7</sup> |

|                         |                                                 |                            | to a valid add              |                   |                                    |                  | , ,                         |

| bit 3                   |                                                 |                            | pt Managemen                | t Mode Select     | bit                                |                  |                             |

|                         | $\frac{\text{If MODE} = 10}{This hit is ison$   |                            |                             |                   |                                    |                  |                             |

|                         | This bit is igno                                |                            | until all data is           | transferred):     |                                    |                  |                             |

|                         |                                                 |                            |                             |                   | ration; scanner                    | resumes after    | returning fror              |

|                         | interrupt                                       |                            |                             |                   |                                    |                  | 0                           |

|                         |                                                 |                            | by interrupts,              | the interrupt rea | sponse will be a                   | ffected          |                             |

|                         | $\frac{\text{If MODE} = 00}{1 = \text{SCANGO}}$ |                            | (to zero) durinc            | interrupt opera   | ation; scan oper                   | ations resume    | after returnin              |

|                         | from inter                                      | rupt                       | . , -                       | ,                 | a, coa op c.                       |                  |                             |

|                         |                                                 | do not prevent             |                             |                   |                                    |                  |                             |

| bit 2                   | •                                               | ted: Read as '             |                             |                   |                                    |                  |                             |

| bit 1-0                 |                                                 | -                          | ss Mode bits <sup>(5)</sup> |                   |                                    |                  |                             |

|                         | 11 = Triggere<br>10 = Peek mo                   |                            |                             |                   |                                    |                  |                             |

|                         | 01 = Burst mo                                   | de                         |                             |                   |                                    |                  |                             |

|                         | 00 = Concurre                                   | ent mode                   |                             |                   |                                    |                  |                             |

|                         | •                                               | •                          | • •                         |                   | y other register                   | content.         |                             |

|                         | s bit is cleared v                              |                            | -                           | -                 |                                    |                  |                             |

|                         |                                                 |                            |                             |                   | ng an interrupt r<br>sends a ready |                  |                             |

|                         | e Table 13-2 for                                |                            | -                           |                   | Serius a ready                     | Signai.          |                             |

| 6: An                   | invalid address                                 | can occur whe              | en the entire rar           |                   | canned and the                     |                  |                             |

|                         |                                                 |                            |                             | Scan Low add      | lress registers p                  | oints to a locat | ion that is not             |

|                         | pped in the mer                                 |                            |                             | ting SCANGO       | bit. Refer to <b>Sec</b>           | tion 13 9 "Prov  | aram Memora                 |

|                         | an Configuratio                                 |                            |                             |                   |                                    |                  | 9. ann mennor j             |

#### REGISTER 13-11: SCANCONO: SCANNER ACCESS CONTROL REGISTER 0

| U-0                       | U-0                                                  | U-0                                                           | U-0  | R/W-0/0                            | R/W-0/0      | R/W-0/0 | R/W-0/0 |  |

|---------------------------|------------------------------------------------------|---------------------------------------------------------------|------|------------------------------------|--------------|---------|---------|--|

| _                         | —                                                    | —                                                             | _    |                                    | TSEL         | <3:0>   |         |  |

| bit 7                     |                                                      |                                                               |      |                                    |              |         | bit C   |  |

|                           |                                                      |                                                               |      |                                    |              |         |         |  |

| Legend:                   |                                                      |                                                               |      |                                    |              |         |         |  |

| R = Readable bit W = Writ |                                                      |                                                               | bit  | U = Unimplemented bit, read as '0' |              |         |         |  |

| u = Bit is und            | changed                                              | x = Bit is unknown -n/n = Value at POR and BOR/Value at all o |      |                                    | other Resets |         |         |  |

| '1' = Bit is se           | t                                                    | '0' = Bit is clea                                             | ared |                                    |              |         |         |  |

|                           |                                                      |                                                               |      |                                    |              |         |         |  |

| bit 7-4                   | Unimplemen                                           | ted: Read as '                                                | 0'   |                                    |              |         |         |  |

| bit 3-0                   | TSEL<3:0>: Scanner Data Trigger Input Selection bits |                                                               |      |                                    |              |         |         |  |

|                           |                                                      |                                                               |      |                                    |              |         |         |  |

|                           | 1111-1001 = Reserved                                 |                                                               |      |                                    |              |         |         |  |

|                           | 1000 = TMR6_postscaled                               |                                                               |      |                                    |              |         |         |  |

|                           |                                                      |                                                               |      |                                    |              |         |         |  |

#### **REGISTER 13-18: SCANTRIG: SCAN TRIGGER SELECTION REGISTER**

1000 = TMR6\_postscaled 1010 = TMR5\_output 1010 = TMR4\_postscaled 1010 = TMR3\_output 1000 = TMR2\_postscaled 1011 = TMR1\_output 1010 = TMR0\_output 1000 = CLKREF\_output

0000 = LFINTOSC

| R/W-0/0                                               | R/W-0/0 | R/W-0/0         | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0 |  |

|-------------------------------------------------------|---------|-----------------|---------|--------------|------------------|----------|---------|--|

| WPUx7                                                 | WPUx6   | WPUx5           | WPUx4   | WPUx3        | WPUx2            | WPUx1    | WPUx0   |  |

| bit 7                                                 |         |                 |         | -            |                  |          | bit 0   |  |

|                                                       |         |                 |         |              |                  |          |         |  |

| Legend:                                               |         |                 |         |              |                  |          |         |  |

| R = Readable bit W = Writable bit                     |         |                 |         | U = Unimpler | nented bit, read | d as '0' |         |  |

| '1' = Bit is set '0' = Bit is cleared                 |         | x = Bit is unkr | nown    |              |                  |          |         |  |

| -n/n = Value at POR and BOR/Value at all other Resets |         |                 |         |              |                  |          |         |  |

| -n/n = Value at POR and BOR/Value at all other Resets |         |                 |         |              |                  |          |         |  |

#### REGISTER 15-5: WPUx: WEAK PULL-UP REGISTER

bit 7-0

WPUx<7:0>: Weak Pull-up PORTx Control bits

1 = Weak Pull-up enabled

0 = Weak Pull-up disabled

|      | Dev        | /ice          |       |       |       |       |                      |       |       |       |

|------|------------|---------------|-------|-------|-------|-------|----------------------|-------|-------|-------|

| Name | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

| WPUA | Х          | Х             | WPUA7 | WPUA6 | WPUA5 | WPUA4 | WPUA3                | WPUA2 | WPUA1 | WPUA0 |

| WPUB | Х          | Х             | WPUB7 | WPUB6 | WPUB5 | WPUB4 | WPUB3                | WPUB2 | WPUB1 | WPUB0 |

| WPUC | Х          | Х             | WPUC7 | WPUC6 | WPUC5 | WPUC4 | WPUC3                | WPUC2 | WPUC1 | WPUC0 |

| WPUD | Х          |               | _     | _     | _     | _     | —                    | _     | _     | _     |

|      |            | Х             | WPUD7 | WPUD6 | WPUD5 | WPUD4 | WPUD3                | WPUD2 | WPUD1 | WPUD0 |

| WPUE | Х          |               | —     | _     | —     | _     | WPUE3 <sup>(1)</sup> | _     | _     | _     |

|      |            | Х             | _     | _     | _     | _     | WPUE3 <sup>(1)</sup> | WPUE2 | WPUE1 | WPUE0 |

#### TABLE 15-6: WEAK PULL-UP PORT REGISTERS

Note 1: If MCLRE = 1, the weak pull-up in RE3 is always enabled; bit WPUE3 is not affected.

#### REGISTER 19-5: TMRxL: TIMERx LOW BYTE REGISTER

| R/W-x/x          | R/W-x/x                   | R/W-x/x           | R/W-x/x | R/W-x/x         | R/W-x/x          | R/W-x/x          | R/W-x/x     |

|------------------|---------------------------|-------------------|---------|-----------------|------------------|------------------|-------------|

|                  |                           |                   | TMR     | <l<7:0></l<7:0> |                  |                  |             |

| bit 7            |                           |                   |         |                 |                  |                  | bit 0       |

|                  |                           |                   |         |                 |                  |                  |             |

| Legend:          |                           |                   |         |                 |                  |                  |             |

| R = Readable     | able bit W = Writable bit |                   |         | U = Unimpler    | mented bit, read | l as '0'         |             |

| u = Bit is unch  | anged                     | x = Bit is unkn   | own     | -n/n = Value a  | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |                           | '0' = Bit is clea | ired    |                 |                  |                  |             |

bit 7-0 **TMRxL<7:0>:**Timerx Low Byte bits

#### **REGISTER 19-6:** TMRxH: TIMERx HIGH BYTE REGISTER

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| TMRxH<7:0>  |         |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TMRxH<7:0>:Timerx High Byte bits

### 19.2 Timer1/3/5 Operation

The Timer1/3/5 module is a 16-bit incrementing counter which is accessed through the TMRxH:TMRxL register pair. Writes to TMRxH or TMRxL directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1/3/5 is enabled by configuring the ON and GE bits in the TxCON and TxGCON registers, respectively. Table 19-2 displays the Timer1/3/5 enable selections.

# TABLE 19-2:TIMER1/3/5 ENABLESELECTIONS

| ON | GE | Timer1/3/5<br>Operation |  |

|----|----|-------------------------|--|

| 1  | 1  | Count Enabled           |  |

| 1  | 0  | Always On               |  |

| 0  | 1  | Off                     |  |

| 0  | 0  | Off                     |  |

# 19.3 Clock Source Selection

The CS<3:0> bits of the TMRxCLK register (Register 19-3) are used to select the clock source for Timer1/3/5. The four TMRxCLK bits allow the selection of several possible synchronous and asynchronous clock sources. Register 19-3 displays the clock source selections.

#### 19.3.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMRxH:TMRxL register pair will increment on multiples of Fosc as determined by the Timer1/3/5 prescaler.

When the Fosc internal clock source is selected, the Timer1/3/5 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1/3/5 value. To utilize the full resolution of Timer1/3/5, an asynchronous input signal must be used to gate the Timer1/3/5 clock input.

The following asynchronous sources may be used at the Timer1/3/5 gate:

- · Asynchronous event on the TxGPPS pin

- TMR0OUT

- TMR1/3/5OUT (excluding the TMR for which it is being used)

- TMR 2/4/6OUT (post-scaled)

- CCP1/2OUT

- PWM3/4OUT

- CMP1/2OUT

- ZCDOUT

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge after any one or    |

|       | more of the following conditions:            |

- Timer1/3/5 enabled after POR

- Write to TMRxH or TMRxL

- Timer1/3/5 is disabled

- Timer1/3/5 is disabled (TMRxON = 0) when TxCKI is high then Timer1/3/5 is enabled (TMRxON = 1) when TxCKI is low.

### 19.3.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1/3/5 module may work as a timer or a counter.

When enabled to count, Timer1/3/5 is incremented on the rising edge of the external clock input of the TxCKIPPS pin. This external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated secondary internal oscillator circuit.

# 20.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- 8-bit period register

- Selectable external hardware timer Resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- Selectable synchronous/asynchronous operation

- · Alternate clock sources

- · Interrupt-on-period

- Three modes of operation:

- Free Running Period

- One-shot

- Monostable

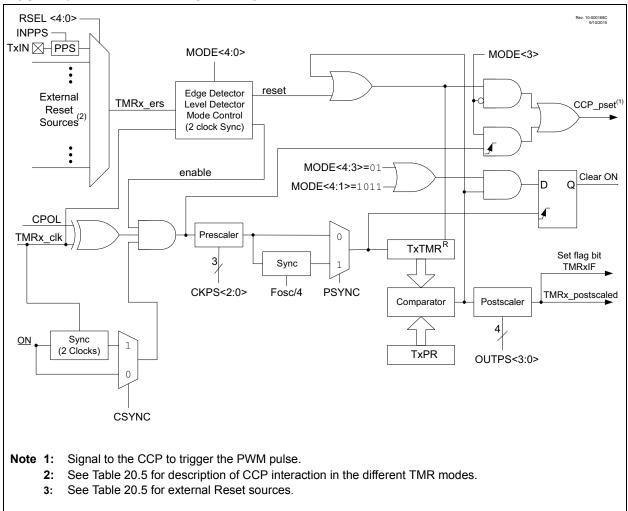

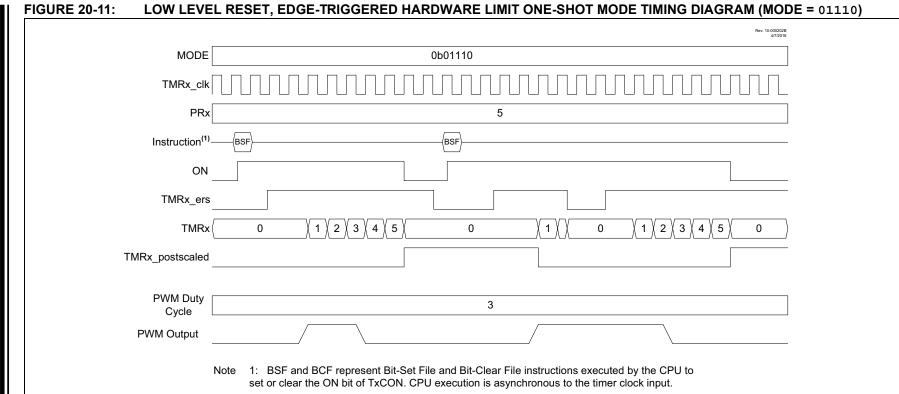

See Figure 20-1 for a block diagram of Timer2. See Figure 20-2 for the clock source block diagram.

Note: Three identical Timer2 modules are implemented on this device. The timers are named Timer2, Timer4 and Timer6. All references to Timer2 apply as well to Timer4 and Timer6. All references to PR2 apply equally to other timers as well.

#### FIGURE 20-1: TIMER2 BLOCK DIAGRAM

#### 26.6.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

# 26.7 Register Definitions: I<sup>2</sup>C Mode

The MSSPx module has seven registers for I<sup>2</sup>C operation.

#### These are:

- MSSP Status Register (SSPxSTAT)

- MSSP Control Register 1 (SSPxCON1)

- MSSP Control Register 2 (SSPxCON2)

- MSSP Control Register 3 (SSPxCON3)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSP Address Register (SSPxADD)

- I<sup>2</sup>C Slave Address Mask Register (SSPxMSK)

- MSSP Shift Register (SSPSR) not directly accessible

SSPxCON1, SSPxCON2, SSPxCON3 and SSPxSTAT

are the Control and Status registers in I<sup>2</sup>C mode operation. The SSPxCON1, SSPxCON2, and SSPxCON3 registers are readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write. SSPSR is the Shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from. SSPxADD contains the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPxADD act as the Baud Rate Generator reload value.

SSPxMSK holds the slave address mask value when the module is configured for 7-Bit Address Masking mode. While it is a separate register, it shares the same SFR address as SSPxADD; it is only accessible when the SSPM<3:0> bits are specifically set to permit access. In receive operations, SSPSR and SSPxBUF together, create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set. During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPSR.

### 26.8.9 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPxCON3 register are clear.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

# 26.9 I<sup>2</sup>C Slave Mode Operation

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of the SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 26.9.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 26-5) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register affects the address matching process. See **Section 26.9.9** "**SSP Mask Register**" for more information.

### 26.9.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

### 26.9.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPxIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 26.9.2 SLAVE RECEPTION

When the R/W bit of a matching received address byte is clear, the R/W bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPxSTAT register is set, or bit SSPOV of the SSPxCON1 register is set. The BOEN bit of the SSPxCON3 register modifies this operation. For more information see Register 26-3.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPxIF, must be cleared by software.

When the SEN bit of the SSPxCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPxCON1 register, except sometimes in 10-bit mode. See **Section 26.9.6.2 "10-bit Addressing Mode"** for more detail.

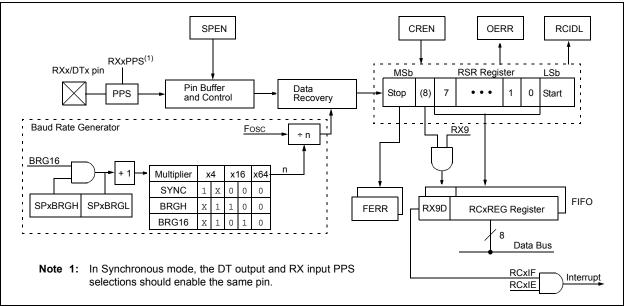

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXxSTA)

- Receive Status and Control (RCxSTA)

- Baud Rate Control (BAUDxCON)

These registers are detailed in Register 27-1, Register 27-2 and Register 27-3, respectively.

The RXx/DTx and TXx/CKx input pins are selected with the RXxPPS and TXxPPS registers, respectively. TXx, CKx, and DTx output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

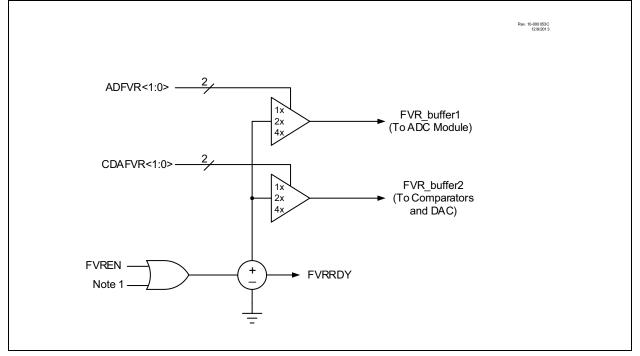

# 28.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- · ADC positive reference

- Comparator input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

#### 28.1 Independent Gain Amplifiers

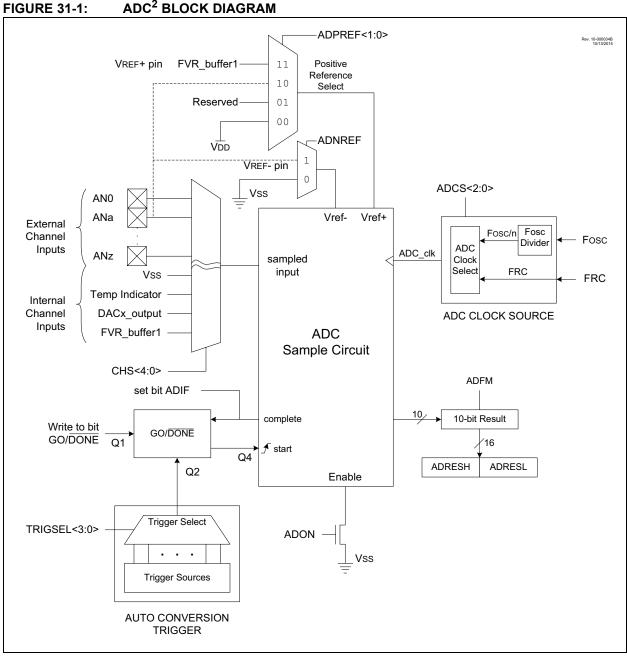

The output of the FVR, which is connected to the ADC, Comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels. The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 31.0 "Analog-to-Digital Converter with Computation (ADC2) Module"** for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference **Section 30.0 "5-Bit Digital-to-Analog Converter (DAC) Module**" and **Section 32.0 "Comparator Module**" for additional information.

# 28.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set.

# FIGURE 28-1: VOLTAGE REFERENCE BLOCK DIAGRAM

ADC<sup>2</sup> BLOCK DIAGRAM

### 31.4.2 PRECHARGE CONTROL

The Precharge stage is an optional period of time that brings the external channel and internal sample and hold capacitor to known voltage levels. Precharge is enabled by writing a non-zero value to the ADPRE register. This stage is initiated when an ADC conversion begins, either from setting the ADGO bit, a special event trigger, or a conversion restart from the computation functionality. If the ADPRE register is cleared when an ADC conversion begins, this stage is skipped.

During the precharge time, CHOLD is disconnected from the outer portion of the sample path that leads to the external capacitive sensor and is connected to either VDD or VSS, depending on the value of the ADPPOL bit of ADCON1. At the same time, the port pin logic of the selected analog channel is overridden to drive a digital high or low out, in order to precharge the outer portion of the ADC's sample path, which includes the external sensor. The output polarity of this override is also determined by the ADPPOL bit of ADCON1. The amount of time that this charging needs is controlled by the ADPRE register.

| Note: | The external charging overrides the TRIS       |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|

|       | setting of the respective I/O pin. If there is |  |  |  |  |

|       | a device attached to this pin, Precharge       |  |  |  |  |

|       | should not be used.                            |  |  |  |  |

# 31.4.3 ACQUISITION CONTROL

The Acquisition stage is an optional time for the voltage on the internal sample and hold capacitor to charge or discharge from the selected analog channel. This acquisition time is controlled by the ADACQ register. If ADPRE = 0, acquisition starts at the beginning of conversion. When ADPRE = 1, the acquisition stage begins when precharge ends.

At the start of the acquisition stage, the port pin logic of the selected analog channel is overridden to turn off the digital high/low output drivers so they do not affect the final result of the charge averaging. Also, the selected ADC channel is connected to CHOLD. This allows charge averaging to proceed between the precharged channel and the CHOLD capacitor.

Note: When ADPRE! = 0, acquisition time cannot be '0'. In this case, setting ADACQ to '0' will set a maximum acquisition time (256 ADC clock cycles). When precharge is disabled, setting ADACQ to '0' will disable hardware acquisition time control.

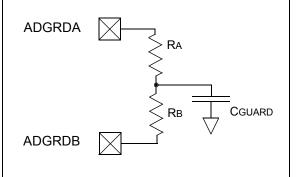

### 31.4.4 GUARD RING OUTPUTS

Figure 31-8 shows a typical guard ring circuit. CGUARD represents the capacitance of the guard ring trace placed on the PCB board. The user selects values for RA and RB that will create a voltage profile on CGUARD, which will match the selected acquisition channel.

The purpose of the guard ring is to generate a signal in phase with the CVD sensing signal to minimize the effects of the parasitic capacitance on sensing electrodes. It also can be used as a mutual drive for mutual capacitive sensing. For more information about active guard and mutual drive, see Application Note AN1478, "*mTouch<sup>TM</sup> Sensing Solution Acquisition Methods Capacitive Voltage Divider*" (DS01478).

The ADC has two guard ring drive outputs, ADGRDA and ADGRDB. These outputs can be routed through PPS controls to I/O pins (see Section **17.0 "Peripheral Pin Select (PPS) Module"** for details) and the polarity of these outputs are controlled by the ADGPOL and ADIPEN bits of ADCON1.

At the start of the first precharge stage, both outputs are set to match the ADGPOL bit of ADCON1. Once the acquisition stage begins, ADGRDA changes polarity, while ADGRDB remains unchanged. When performing a double sample conversion, setting the ADIPEN bit of ADCON1 causes both guard ring outputs to transition to the opposite polarity of ADGPOL at the start of the second precharge stage, and ADGRDA toggles again for the second acquisition. For more information on the timing of the guard ring output, refer to Figure 31-8 and Figure 31-9.

|                                                                                                                                                                                                                                                              | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| if ZERO bit                                                                                                                                                                                                                                                  | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                              | if ZERO bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| None                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 1110                                                                                                                                                                                                                                                         | 0000 nnr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nn nnnn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| If the ZERO bit is '1', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 1                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 1(2)                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Cycles: 1(2)<br>Q Cycle Activity:<br>If Jump:                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Q2                                                                                                                                                                                                                                                           | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Read literal<br>'n'                                                                                                                                                                                                                                          | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Write to PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| No<br>operation                                                                                                                                                                                                                                              | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Q2                                                                                                                                                                                                                                                           | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |