#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.6К х 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27k40t-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18(L)F27/47K40

#### PIC18(L)F2x/4xK40 Family Types

| Device         | Data Sheet Index | Program Memory Flash<br>(bytes) | Data SRAM<br>(bytes) | Data EEPROM<br>(bytes) | I/O Pins | 16-bit Timers | Comparators | 10-bit ADC <sup>2</sup> with<br>Computation (ch) | 5-bit DAC | Zero-Cross Detect | CCP/10-bit PWM | CWG | 8-bit TMR with HLT | Windowed Watchdog<br>Timer | <b>CRC</b> with Memory Scan | EUSART | I <sup>2</sup> C/SPI | Sdd | Peripheral Module Disable | Temperature Indicator | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------------|----------------------|------------------------|----------|---------------|-------------|--------------------------------------------------|-----------|-------------------|----------------|-----|--------------------|----------------------------|-----------------------------|--------|----------------------|-----|---------------------------|-----------------------|----------------------|

| PIC18(L)F24K40 | (1)              | 16k                             | 1024                 | 256                    | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 1      | 1                    | Y   | Y                         | Υ                     | Ι                    |

| PIC18(L)F25K40 | (1)              | 32k                             | 2048                 | 256                    | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 1      | 1                    | Υ   | Υ                         | Y                     | Ι                    |

| PIC18(L)F26K40 | (2)              | 64k                             | 3728                 | 1024                   | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Y   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F27K40 | (3)              | 128k                            | 3728                 | 1024                   | 25       | 4             | 2           | 24                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F45K40 | (2)              | 32k                             | 2048                 | 256                    | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F46K40 | (2)              | 64k                             | 3728                 | 1024                   | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Y                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

| PIC18(L)F47K40 | (3)              | 128k                            | 3728                 | 1024                   | 36       | 4             | 2           | 35                                               | 1         | 1                 | 2/2            | 1   | 3                  | Y                          | Υ                           | 2      | 2                    | Υ   | Υ                         | Υ                     | Ι                    |

**Note 1:** Debugging Methods: (I) – Integrated on Chip.

Data Sheet Index: (Unshaded devices are described in this document.)

1. DS40001843 PIC18(L)F24/25K40 Data Sheet, 28-Pin, 8-bit Flash Microcontrollers

2. DS40001816 PIC18(L)F26/45/46K40 Data Sheet, 28/40/44-Pin, 8-bit Flash Microcontrollers

3. DS40001844 PIC18(L)F27/47K40 Data Sheet, 28/40/44-Pin, 8-bit Flash Microcontrollers

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

# 1.2 Other Special Features

- **Memory Endurance:** The Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles up to 10K for program memory and 100K for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-programmability: These devices can write to their own program memory spaces under internal software control. By using a boot loader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18(L)F2x/ 4xK40 family introduces an optional extension to the PIC18 instruction set, which adds eight new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced Peripheral Pin Select: The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins.

- Enhanced Addressable EUSART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-bit A/D Converter with Computation:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead. It has a new module called ADC<sup>2</sup> with computation features, which provides a digital filter and threshold interrupt functions.

- Windowed Watchdog Timer (WWDT):

- Timer monitoring of overflow and underflow events

- Variable prescaler selection

- Variable window size selection

- All sources configurable in hardware or software

# 1.3 Details on Individual Family Members

Devices in the PIC18(L)F2x/4xK40 family are available in 28-pin and 40/44-pin packages. The block diagram for this device is shown in Figure 1-1.

The devices have the following differences:

- 1. Program Flash Memory

- 2. Data Memory SRAM

- 3. Data Memory EEPROM

- 4. A/D channels

- 5. I/O ports

- 6. Enhanced USART

- 7. Input Voltage Range/Power Consumption

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in the pin summary tables (Table 1 and Table 2).

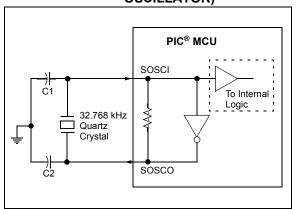

## 4.3.1.5 Secondary Oscillator

The secondary oscillator is a separate oscillator block that can be used as an alternate system clock source. The secondary oscillator is optimized for 32.768 kHz, and can be used with an external crystal oscillator connected to the SOSCI and SOSCO device pins, or an external clock source connected to the SOSCIN pin. The secondary oscillator can be selected during run-time using clock switching. Refer to **Section 4.4 "Clock Switching"** for more information.

#### FIGURE 4-5: QUARTZ CRYSTAL OPERATION (SECONDARY OSCILLATOR)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for PIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

# 4.3.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See Section 4.4 "Clock Switching" for more information.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory-calibrated and operates from 1 to 64 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

# 4.3.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 64 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (Fosc = 1 MHz) or '000' (Fosc = 64 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 4.4 "Clock Switching" for more information.

The HFINTOSC frequency can be selected by setting the HFFRQ<3:0> bits of the OSCFRQ register.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

#### 4.3.2.2 MFINTOSC

The module provides two (500 kHz and 31.25 kHz) constant clock outputs. These clocks are digital divisors of the HFINTOSC clock. Dynamic divider logic is used to provide constant MFINTOSC clock rates for all settings of HFINTOSC.

The MFINTOSC cannot be used to drive the system but it is used to clock certain modules such as the Timers and WWDT.

#### 4.3.2.3 Internal Oscillator Frequency Adjustment

The internal oscillator is factory-calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 4-3).

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE **does not affect** the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), WWDT, Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

# 4.3.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory-calibrated 31 kHz internal clock source.

The LFINTOSC is the frequency for the Power-up Timer (PWRT), Windowed Watchdog Timer (WWDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 4.4, Clock Switching for more information.

## 4.3.2.5 ADCRC

The ADCRC is an oscillator dedicated to the  $ADC^2$  module. The ADCRC oscillator can be manually enabled using the ADOEN bit of the OSCEN register. The ADCRC runs at a fixed frequency of 600 kHz. ADCRC is automatically enabled if it is selected as the clock source for the  $ADC^2$  module.

| R/W-x/u          | R/W-x/u                                                              | R/W-x/u           | R/W-x/u | R/W-x/u         | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|------------------|----------------------------------------------------------------------|-------------------|---------|-----------------|---------|---------|---------|--|--|

| LATx7            | LATx6                                                                | LATx5             | LATx4   | LATx3           | LATx2   | LATx1   | LATx0   |  |  |

| bit 7            |                                                                      |                   |         |                 |         |         | bit 0   |  |  |

|                  |                                                                      |                   |         |                 |         |         |         |  |  |

| Legend:          |                                                                      |                   |         |                 |         |         |         |  |  |

| R = Readable     | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                   |         |                 |         |         |         |  |  |

| '1' = Bit is set |                                                                      | '0' = Bit is clea | ared    | x = Bit is unki | nown    |         |         |  |  |

| -n/n = Value at  | -n/n = Value at POR and BOR/Value at all other Resets                |                   |         |                 |         |         |         |  |  |

# REGISTER 15-3: LATx: LATx REGISTER<sup>(1)</sup>

bit 7-0 LATx<7:0>: Rx7:Rx0 Output Latch Value bits

**Note 1:** Writes to LATx are equivalent with writes to the corresponding PORTx register. Reads from LATx register return register values, not I/O pin values.

|      | Dev        | vice          |       |       |       |       |       |       |       |       |

|------|------------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| LATA | Х          | Х             | LATA7 | LATA6 | LATA5 | LATA4 | LATA3 | LATA2 | LATA1 | LATA0 |

| LATB | Х          | Х             | LATB7 | LATB6 | LATB5 | LATB4 | LATB3 | LATB2 | LATB1 | LATB0 |

| LATC | Х          | Х             | LATC7 | LATC6 | LATC5 | LATC4 | LATC3 | LATC2 | LATC1 | LATC0 |

| LATD | Х          |               | _     | _     | _     | _     | —     | _     | —     | _     |

|      |            | Х             | LATD7 | LATD6 | LATD5 | LATD4 | LATD3 | LATD2 | LATD1 | LATD0 |

| LATE | Х          |               | _     | —     | —     | —     | —     | _     | _     | _     |

|      |            | Х             | _     | —     | —     | _     | —     | LATE2 | LATE1 | LATE0 |

#### TABLE 15-4: LAT REGISTERS

| R/W-0/0          | R/W-0/0                                                              | R/W-0/0           | R/W-0/0 | R/W-0/0         | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|------------------|----------------------------------------------------------------------|-------------------|---------|-----------------|---------|---------|---------|--|--|

| ODCx7            | ODCx6                                                                | ODCx5             | ODCx4   | ODCx3           | ODCx2   | ODCx1   | ODCx0   |  |  |

| bit 7            |                                                                      |                   |         | •               |         |         | bit 0   |  |  |

|                  |                                                                      |                   |         |                 |         |         |         |  |  |

| Legend:          |                                                                      |                   |         |                 |         |         |         |  |  |

| R = Readable     | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                   |         |                 |         |         |         |  |  |

| '1' = Bit is set |                                                                      | '0' = Bit is clea | ared    | x = Bit is unkr | nown    |         |         |  |  |

| -n/n = Value at  | -n/n = Value at POR and BOR/Value at all other Resets                |                   |         |                 |         |         |         |  |  |

#### REGISTER 15-6: ODCONx: OPEN-DRAIN CONTROL REGISTER

bit 7-0

ODCx<7:0>: Open-Drain Configuration on Pins Rx<7:0>

1 = Output drives only low-going signals (sink current only)

0 = Output drives both high-going and low-going signals (source and sink current)

|        | Dev        | /ice          |       |       |       |       |       |       |       |       |

|--------|------------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name   | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| ODCONA | Х          | Х             | ODCA7 | ODCA6 | ODCA5 | ODCA4 | ODCA3 | ODCA2 | ODCA1 | ODCA0 |

| ODCONB | Х          | Х             | ODCB7 | ODCB6 | ODCB5 | ODCB4 | ODCB3 | ODCB2 | ODCB1 | ODCB0 |

| ODCONC | Х          | Х             | ODCC7 | ODCC6 | ODCC5 | ODCC4 | ODCC3 | ODCC2 | ODCC1 | ODCC0 |

| ODCOND | Х          |               | _     | _     | —     | —     | _     | _     | _     | —     |

|        |            | Х             | ODCD7 | ODCD6 | ODCD5 | ODCD4 | ODCD3 | ODCD2 | ODCD1 | ODCD0 |

| ODCONE | Х          |               | _     | _     | _     | _     | _     | _     |       | _     |

|        |            | Х             | _     | _     | _     | _     | _     | ODCE2 | ODCE1 | ODCE0 |

#### TABLE 15-7:OPEN-DRAIN CONTROL REGISTERS

|                | CCPR    | x<15:8>                              |                |                 |       |

|----------------|---------|--------------------------------------|----------------|-----------------|-------|

|                |         |                                      |                |                 | bit 0 |

|                |         |                                      |                |                 |       |

|                |         |                                      |                |                 |       |

| W = Writab     | ole bit | U = Unimpleme                        | nted bit, read | as '0'          |       |

| '1' = Bit is s | set     | '0' = Bit is cleare                  | ed             | x = Bit is unkr | nown  |

|                |         | W = Writable bit<br>'1' = Bit is set | •              | •               |       |

# REGISTER 21-5: CCPRxH: CCPx REGISTER HIGH BYTE

| bit 7-0 | MODE = Capture Mode:                           |

|---------|------------------------------------------------|

|         | CCPRxH<7:0>: MSB of captured TMR1 value        |

|         | MODE = Compare Mode:                           |

|         | CCPRxH<7:0>: MSB compared to TMR1 value        |

|         | MODE = PWM Mode && FMT = 0:                    |

|         | CCPRxH<7:2>: Not used                          |

|         | CCPRxH<1:0>: CCPW<9:8> - Pulse-Width MS 2 bits |

|         | MODE = PWM Mode && FMT = 1:                    |

|         | CCPRxH<7:0>: CCPW<9:2> - Pulse-Width MS 8 bits |

# PIC18(L)F27/47K40

| SHUTDOWN<br>bit 7<br>Legend:<br>R = Readable bit                                                                                                           | REN                                                             | LSBD                                                                  | )<1:0>                                                    | LSAC                                                                                                             |                                                                    |              |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------|-------------|

| Legend:                                                                                                                                                    |                                                                 |                                                                       |                                                           | 20/10                                                                                                            | <1:0>                                                              | —            | —           |

|                                                                                                                                                            |                                                                 |                                                                       |                                                           |                                                                                                                  |                                                                    |              | bit C       |

|                                                                                                                                                            |                                                                 |                                                                       |                                                           |                                                                                                                  |                                                                    |              |             |

|                                                                                                                                                            |                                                                 | W = Writable                                                          | bit                                                       | II = Unimplem                                                                                                    | ented hit read                                                     | as '0'       |             |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Res |                                                                 |                                                                       |                                                           |                                                                                                                  |                                                                    |              | thar Resets |

| '1' = Bit is set     '0' = Bit is cleared     HS/HC = Bit is set/cleared by hardware                                                                       |                                                                 |                                                                       |                                                           |                                                                                                                  |                                                                    |              |             |

| q = Value depend                                                                                                                                           | ls on condition                                                 |                                                                       | areu                                                      |                                                                                                                  | sercleared by                                                      | naruware     |             |

|                                                                                                                                                            |                                                                 |                                                                       |                                                           |                                                                                                                  |                                                                    |              |             |

| bit 7<br>bit 6                                                                                                                                             | 1 = An auto<br>0 = No auto                                      | : Auto-Shutdo<br>-shutdown sta<br>-shutdown eve<br>estart Enable      | te is in effect<br>ent has occur                          |                                                                                                                  |                                                                    |              |             |

| טונס                                                                                                                                                       | 1 = Auto-res                                                    | estart is enable<br>start is disable                                  | d                                                         |                                                                                                                  |                                                                    |              |             |

| bit 5-4                                                                                                                                                    | 11 = A logic<br>10 = A logic<br>01 = Pin is tri<br>00 = The ina | 1' is placed or<br>0' is placed or<br>-stated on CW<br>ctive state of | CWG1B/D v<br>n CWG1B/D v<br>/G1B/D when<br>the pin, inclu | -Shutdown State<br>when an auto-sh<br>when an auto-sh<br>an auto-shutdo<br>uding polarity, is<br>hutdown event c | utdown event o<br>utdown event o<br>wn event occur<br>placed on CW | ccurs.<br>s. | he required |

| bit 3-2                                                                                                                                                    | 11 = A logic<br>10 = A logic<br>01 = Pin is tri<br>00 = The ina | 1' is placed or<br>0' is placed or<br>-stated on CW<br>ctive state of | CWG1A/C v<br>CWG1A/C v<br>/G1A/C when<br>the pin, inclu   | -Shutdown State<br>vhen an auto-sh<br>vhen an auto-sh<br>an auto-shutdo<br>iding polarity, is<br>hutdown event c | utdown event o<br>utdown event o<br>wn event occur<br>placed on CW | ccurs.<br>s. | he required |

| bit 1-0                                                                                                                                                    | Unimplemen                                                      | ted: Read as                                                          | <b>'</b> 0'                                               |                                                                                                                  |                                                                    |              |             |

2: The outputs will remain in auto-shutdown state until the next rising edge of the CWG data input after this bit is cleared.

| U-0             | U-0       | R/W-x/u                                                  | R/W-x/u        | R/W-x/u         | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|-----------------|-----------|----------------------------------------------------------|----------------|-----------------|------------------|------------------|--------------|

| _               | —         |                                                          |                | DBR             | <5:0>            |                  |              |

| bit 7           | ·         |                                                          |                |                 |                  |                  | bit 0        |

|                 |           |                                                          |                |                 |                  |                  |              |

| Legend:         |           |                                                          |                |                 |                  |                  |              |

| R = Readab      | ole bit   | W = Writable                                             | bit            | U = Unimplen    | nented bit, reac | l as '0'         |              |

| u = Bit is un   | changed   | x = Bit is unkr                                          | nown           | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is se | et        | '0' = Bit is cle                                         | ared           | q = Value dep   | ends on condit   | ion              |              |

|                 |           |                                                          |                |                 |                  |                  |              |

| bit 7-6         | Unimplem  | ented: Read as '                                         | 0'             |                 |                  |                  |              |

| bit 5-0         | DBR<5:0>: | CWG Rising Ed                                            | ge Triggered I | Dead-Band Cou   | int bits         |                  |              |

|                 | 11 1111 = | = 63-64 CWG cld                                          | ock periods    |                 |                  |                  |              |

|                 | 11 1110 = | = 62-63 CWG clo                                          | ock periods    |                 |                  |                  |              |

|                 |           |                                                          |                |                 |                  |                  |              |

|                 | •         |                                                          |                |                 |                  |                  |              |

|                 | •         |                                                          |                |                 |                  |                  |              |

|                 |           | = 2-3 CWG clock                                          | •              |                 |                  |                  |              |

|                 |           | <ul> <li>1-2 CWG clock</li> <li>0 CWG clock p</li> </ul> |                | hand concration | n is hypassod    |                  |              |

|                 | 00 0000 = |                                                          | enous. Deau-   | band generation | in is bypassed   |                  |              |

#### REGISTER 24-8: CWG1DBR: CWG RISING DEAD-BAND COUNT REGISTER

## REGISTER 24-9: CWG1DBF: CWG FALLING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | DBF∙    | <5:0>   |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-6 | Unimplemented: Read as '0'                                       |  |  |  |  |  |

|---------|------------------------------------------------------------------|--|--|--|--|--|

| bit 5-0 | DBF<5:0>: CWG Falling Edge Triggered Dead-Band Count bits        |  |  |  |  |  |

|         | 11 1111 = 63-64 CWG clock periods                                |  |  |  |  |  |

|         | 11 1110 = 62-63 CWG clock periods                                |  |  |  |  |  |

|         |                                                                  |  |  |  |  |  |

|         |                                                                  |  |  |  |  |  |

|         |                                                                  |  |  |  |  |  |

|         | 00 0010 = 2-3 CWG clock periods                                  |  |  |  |  |  |

|         | 00 0001 = 1-2 CWG clock periods                                  |  |  |  |  |  |

|         | 00 0000 = 0 CWG clock periods. Dead-band generation is bypassed. |  |  |  |  |  |

| REGISTE    |                                |                                      |                         | •                | C MASTER N           | •                |          |

|------------|--------------------------------|--------------------------------------|-------------------------|------------------|----------------------|------------------|----------|

| R/W-0      | -                              | R-0                                  | R-0                     | R-0              | R-0                  | R-0              | R-0      |

| SMP        | CKE                            | D/A                                  | P <sup>(1)</sup>        | S <sup>(1)</sup> | R/W <sup>(2,3)</sup> | UA               | BF       |

| bit 7      |                                |                                      |                         |                  |                      |                  | bit 0    |

| Legend:    |                                |                                      |                         |                  |                      |                  |          |

| R = Read   | able bit                       | W = Writable                         | > bit                   | U = Unimpler     | mented bit, read     | as '0'           |          |

| -n = Value |                                | '1' = Bit is se                      |                         | '0' = Bit is cle |                      | x = Bit is unkr  | nown     |

|            |                                | . 2.1.0 00                           | -                       | 0 2.1.0 0.0      |                      |                  |          |

| bit 7      | SMP: Slew                      | Rate Control bi                      | t                       |                  |                      |                  |          |

|            |                                | <u>Slave mode:</u>                   |                         |                  |                      |                  |          |

|            |                                |                                      |                         |                  | de (100 kHz and      | 1 MHz)           |          |

| bit 6      | CKE: SMBL                      | ite control is en                    |                         | Speed mode (4    |                      |                  |          |

| bit 0      |                                | <u>Slave mode:</u>                   |                         |                  |                      |                  |          |

|            |                                | SMBus-specifi                        | c inputs                |                  |                      |                  |          |

|            | 0 = Disables                   | s SMBus-specif                       | ic inputs               |                  |                      |                  |          |

| bit 5      | D/A: Data/A                    |                                      |                         |                  |                      |                  |          |

|            | In Master m<br>Reserved.       | <u>ode:</u>                          |                         |                  |                      |                  |          |

|            | In Slave mo                    | de:                                  |                         |                  |                      |                  |          |

|            | 1 = Indicate                   | s that the last b                    |                         |                  |                      |                  |          |

|            |                                | s that the last b                    | yte received or         | transmitted wa   | s address            |                  |          |

| bit 4      | P: Stop bit <sup>(1</sup>      |                                      | has been date           | ated last        |                      |                  |          |

|            |                                | s that a Stop bi<br>was not detected |                         | ected last       |                      |                  |          |

| bit 3      | S: Start bit <sup>(1</sup>     |                                      |                         |                  |                      |                  |          |

|            |                                | s that a Start bi                    |                         | ected last       |                      |                  |          |

|            |                                | was not detect                       |                         |                  |                      |                  |          |

| bit 2      |                                | Write Informatio                     | on bit <sup>(2,3)</sup> |                  |                      |                  |          |

|            | <u>In Slave mo</u><br>1 = Read | <u>de:</u>                           |                         |                  |                      |                  |          |

|            | 0 = Write                      |                                      |                         |                  |                      |                  |          |

|            | In Master m                    |                                      |                         |                  |                      |                  |          |

|            |                                | t is in progress                     |                         |                  |                      |                  |          |

| bit 1      |                                | t is not in progr<br>Address bit (10 |                         |                  |                      |                  |          |

| DIL        | -                              |                                      |                         | • •              | n the SSPxADD        | register         |          |

|            |                                | does not need                        |                         |                  |                      | . eg.ete.        |          |

| bit 0      | BF: Buffer F                   | Full Status bit                      |                         |                  |                      |                  |          |

|            | In Transmit                    |                                      |                         |                  |                      |                  |          |

|            | 1 = SSPxBL<br>0 = SSPxBL       |                                      |                         |                  |                      |                  |          |

|            | In Receive r                   |                                      |                         |                  |                      |                  |          |

|            | 1 = SSPxBl                     | JF is full (does                     |                         |                  |                      |                  |          |

|            | 0 = SSPxBl                     | JF is empty (do                      | es not include t        | he ACK and St    | op bits)             |                  |          |

| Note 1:    | This bit is cleare             | ed on Reset and                      | when SSPEN              | is cleared.      |                      |                  |          |

| 2:         | This bit holds th              |                                      |                         |                  | ss match. This b     | it is only valid | from the |

|            | address match f                | to the next Star                     | bit, Stop bit or        | not ACK bit.     |                      |                  |          |

# **REGISTER 26-6:** SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C MASTER MODE)

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.

| R/HS/HC-0       | R/W-0                                                                                                                                                                | R/W-0                        | R/W-0                       | R/W-0              | R/W-0             | R/W-0          | R/W-0         |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------|--------------------|-------------------|----------------|---------------|

| ACKTIM          | PCIE                                                                                                                                                                 | SCIE                         | BOEN                        | SDAHT              | SBCDE             | AHEN           | DHEN          |

| bit 7           |                                                                                                                                                                      |                              |                             |                    |                   |                | bit 0         |

|                 |                                                                                                                                                                      |                              |                             |                    |                   |                |               |

| Legend:         |                                                                                                                                                                      |                              |                             |                    |                   |                |               |

| R = Readable    |                                                                                                                                                                      | W = Writable                 | bit                         | •                  | nented bit, read  |                |               |

| -n = Value at I | -                                                                                                                                                                    | '1' = Bit is set             |                             | HS/HC = Bit i      | s set/cleared by  | / hardware     |               |

| x = Bit is unkn | own                                                                                                                                                                  | '0' = Bit is clea            | ared                        |                    |                   |                |               |

| bit 7           | ACKTIM: Ack                                                                                                                                                          | knowledge Time               | Status bit                  |                    |                   |                |               |

|                 | Unused in Ma                                                                                                                                                         | •                            |                             |                    |                   |                |               |

| bit 6           | PCIE: Stop C                                                                                                                                                         | ondition Interru             | pt Enable bit <sup>(1</sup> | )                  |                   |                |               |

|                 |                                                                                                                                                                      | nterrupt on dete             |                             |                    |                   |                |               |

|                 |                                                                                                                                                                      | ection interrupts            |                             |                    |                   |                |               |

| bit 5           | SCIE: Start C                                                                                                                                                        | ondition Interru             | pt Enable bit <sup>(1</sup> | 1)                 |                   |                |               |

|                 |                                                                                                                                                                      |                              |                             | r Restart condit   | tions             |                |               |

|                 |                                                                                                                                                                      | ction interrupts             |                             |                    |                   |                |               |

| bit 4           |                                                                                                                                                                      | r Overwrite Ena              |                             |                    |                   |                |               |

|                 |                                                                                                                                                                      | •                            | every time a r              | new data byte      | is available, igr | noring the SSI | POV effect on |

|                 |                                                                                                                                                                      | the buffer<br>is only update | d when SSPC                 | )V is clear        |                   |                |               |

| bit 3           |                                                                                                                                                                      | Hold Time Sel                |                             |                    |                   |                |               |

| bit o           |                                                                                                                                                                      |                              |                             | fter the falling e | edge of SCI       |                |               |

|                 | <ol> <li>1 = Minimum of 300ns hold time on SDA after the falling edge of SCL</li> <li>0 = Minimum of 100ns hold time on SDA after the falling edge of SCL</li> </ol> |                              |                             |                    |                   |                |               |

| bit 2           | <b>SBCDE:</b> Slave Mode Bus Collision Detect Enable bit                                                                                                             |                              |                             |                    |                   |                |               |

|                 | Unused in Master mode.                                                                                                                                               |                              |                             |                    |                   |                |               |

| bit 1           | AHEN: Address Hold Enable bit                                                                                                                                        |                              |                             |                    |                   |                |               |

|                 | Unused in Master mode.                                                                                                                                               |                              |                             |                    |                   |                |               |

| bit 0           | DHEN: Data Hold Enable bit                                                                                                                                           |                              |                             |                    |                   |                |               |

|                 | Unused in Master mode.                                                                                                                                               |                              |                             |                    |                   |                |               |

# **REGISTER 26-9:** SSPxCON3: MSSPx CONTROL REGISTER 3 (I<sup>2</sup>C MASTER MODE)

**Note 1:** This bit has no effect when SSPM<3:0> = 1111 or 1110.In these Slave modes the START and STOP condition interrupts are always enabled.

# **REGISTER 26-10:** SSPxBUF: MSSP DATA BUFFER REGISTER (I<sup>2</sup>C MASTER MODE)

|                  |       |                  |       |              | •                | ,      |       |

|------------------|-------|------------------|-------|--------------|------------------|--------|-------|

| R/W-x            | R/W-x | R/W-x            | R/W-x | R/W-x        | R/W-x            | R/W-x  | R/W-x |

|                  |       |                  | BUF   | <7:0>        |                  |        |       |

| bit 7            |       |                  |       |              |                  |        | bit 0 |

|                  |       |                  |       |              |                  |        |       |

| Legend:          |       |                  |       |              |                  |        |       |

| R = Readable bit |       | W = Writable bit |       | U = Unimpler | mented bit, read | as '0' |       |

| R = Readable bit     | vv = vvritable bit   | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 BUF<7:0>: MSSP Buffer bits

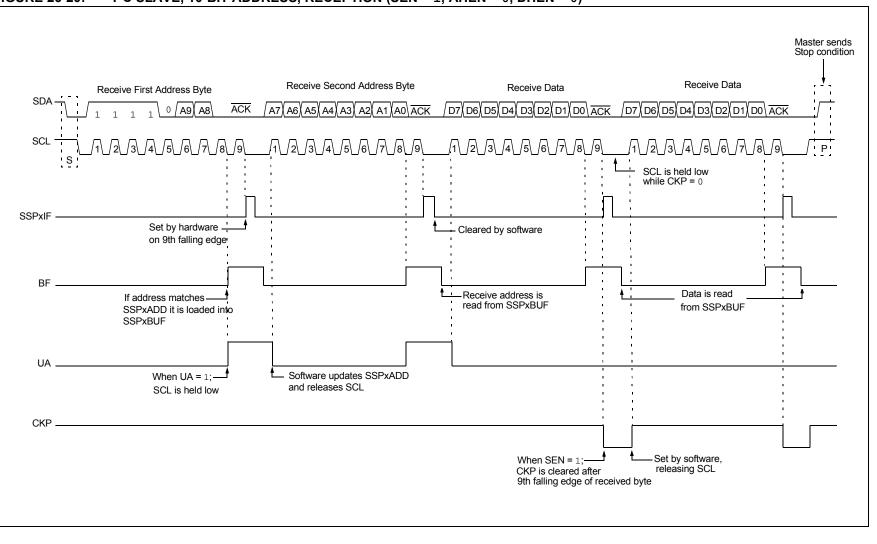

# FIGURE 26-20: I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 0, DHEN = 0)

PIC18(L)F27/47K40

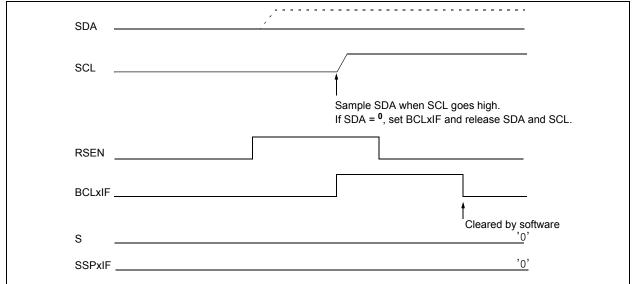

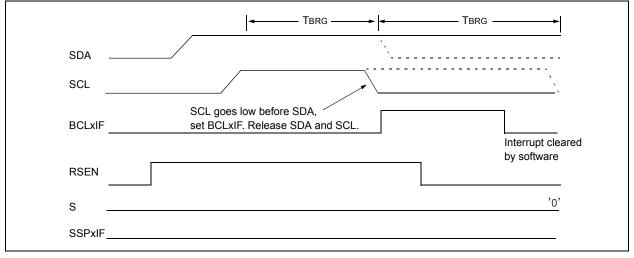

# 26.10.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPxADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 26-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 26-37.

If, at the end of the BRG time out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 26-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

# 30.6 Register Definitions: DAC Control

Long bit name prefixes for the DAC peripheral is shown in Table 30-1. Refer to **Section 1.4.2.2 "Long Bit Names"** for more information.

### TABLE 30-1:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| DAC        | DAC             |

# REGISTER 30-1: DAC1CON0: DAC CONTROL REGISTER

| R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 |

|---------|-----|---------|---------|---------|---------|-----|---------|

| EN      | —   | OE1     | OE2     | PSS     | i<1:0>  | —   | NSS     |

| bit 7   |     |         |         |         |         |     | bit 0   |

|         |     |         |         |         |         |     |         |

I

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: DAC Enable bit<br>1 = DAC is enabled<br>0 = DAC is disabled                                                                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 5   | <ul> <li>OE1: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is output on the DAC1OUT1 pin</li> <li>0 = DAC voltage level is disconnected from the DAC1OUT1 pin</li> </ul> |

| bit 4   | <ul> <li>OE2: DAC Voltage Output Enable bit</li> <li>1 = DAC voltage level is output on the DAC1OUT2 pin</li> <li>0 = DAC voltage level is disconnected from the DAC1OUT2 pin</li> </ul> |

| bit 3-2 | PSS<1:0>: DAC Positive Source Select bit<br>11 = Reserved<br>10 = FVR buffer<br>01 = VREF+<br>00 = AVDD                                                                                  |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 0   | NSS: DAC Negative Source Select bit<br>1 = VREF-<br>0 = AVSS                                                                                                                             |

# 31.4 Capacitive Voltage Divider (CVD) Features

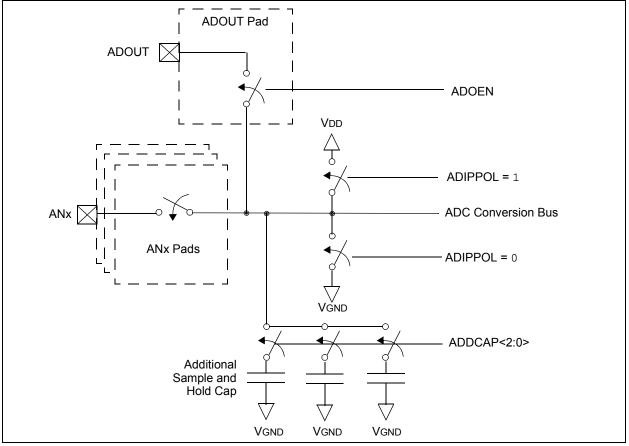

The ADC module contains several features that allow the user to perform a relative capacitance measurement on any ADC channel using the internal ADC sample and hold capacitance as a reference. This relative capacitance measurement can be used to implement capacitive touch or proximity sensing applications. Figure 31-6 shows the basic block diagram of the CVD portion of the ADC module.

| R/W-0/0              | R/W-0/0    | R/W-0/0                                                                          | R/W-0/0        | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|----------------------|------------|----------------------------------------------------------------------------------|----------------|-------------------------------------------------------|---------|---------|---------|--|

|                      |            |                                                                                  | ADPF           | RE<7:0>                                               |         |         |         |  |

| bit 7                |            |                                                                                  |                |                                                       |         |         | bit C   |  |

|                      |            |                                                                                  |                |                                                       |         |         |         |  |

| Legend:              |            |                                                                                  |                |                                                       |         |         |         |  |

| R = Readable bit     |            | W = Writable bit                                                                 |                | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged |            | x = Bit is unknown                                                               |                | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is se      | t          | '0' = Bit is clea                                                                | ared           |                                                       |         |         |         |  |

| bit 7-0              | 11111111 = | <ul> <li>Precharge Ti</li> <li>Precharge time</li> <li>Precharge time</li> </ul> | e is 255 clock | s of the selected                                     |         |         |         |  |

|                      | •          |                                                                                  |                |                                                       |         |         |         |  |

# REGISTER 31-9: ADPRE: ADC PRECHARGE TIME CONTROL REGISTER

00000001 = Precharge time is 1 clock of the selected ADC clock 00000000 = Precharge time is not included in the data conversion cycle

#### REGISTER 31-10: ADACQ: ADC ACQUISITION TIME CONTROL REGISTER

| R/W-0/0    | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|------------|-------------|---------|---------|---------|---------|---------|---------|

| ADACQ<7:0> |             |         |         |         |         |         |         |

| bit 7      | bit 7 bit 0 |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-0 | <b>ADACQ&lt;7:0&gt;</b> : Acquisition (charge share time) Select bits<br>11111111 = Acquisition time is 255 clocks of the selected ADC clock<br>11111110 = Acquisition time is 254 clocks of the selected ADC clock |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                                                   |

|         | •<br>00000001 = Acquisition time is 1 clock of the selected ADC clock<br>00000000 = Acquisition time is not included in the data conversion cycle                                                                   |

| Notor   | If ADRRE is not equal to $(a)$ then ADACO = b'00000000 means Acquisition time is 256 alor                                                                                                                           |

**Note:** If ADPRE is not equal to '0', then ADACQ = b'00000000 means Acquisition time is 256 clocks of the selected ADC clock.

# 32.11 CWG1 Auto-Shutdown Source

The output of the comparator module can be used as an auto-shutdown source for the CWG1 module. When the output of the comparator is active and the corresponding WGASxE is enabled, the CWG operation will be suspended immediately (see Section 24.10.1.2 "External Input Source").

# 32.12 ADC Auto-Trigger Source

The output of the comparator module can be used to trigger an ADC conversion. When the ADACT register is set to trigger on a comparator output, an ADC conversion will trigger when the Comparator output goes high.

# 32.13 TMR2/4/6 Reset

The output of the comparator module can be used to reset Timer2. When the TxERS register is appropriately set, the timer will reset when the Comparator output goes high.

# 32.14 Operation in Sleep Mode

The comparator module can operate during Sleep. The comparator clock source is based on the Timer1 clock source. If the Timer1 clock source is either the system clock (FOSC) or the instruction clock (FOSC/4), Timer1 will not operate during Sleep, and synchronized comparator outputs will not operate.

A comparator interrupt will wake the device from Sleep. The CxIE bits of the PIE2 register must be set to enable comparator interrupts.

# PIC18(L)F27/47K40

| SUBLW                                                              | Subtract                     | Subtract W from literal   |        |           |  |  |

|--------------------------------------------------------------------|------------------------------|---------------------------|--------|-----------|--|--|

| Syntax:                                                            | SUBLW I                      | K                         |        |           |  |  |

| Operands:                                                          | $0 \le k \le 25$             | 5                         |        |           |  |  |

| Operation:                                                         | $k-(W) \rightarrow$          | W                         |        |           |  |  |

| Status Affected:                                                   | N, OV, C,                    | DC, Z                     |        |           |  |  |

| Encoding:                                                          | 0000                         | 1000                      | kkkk   | kkkk      |  |  |

| Description                                                        | W is subtr<br>literal 'k'. 1 |                           |        |           |  |  |

| Words:                                                             | 1                            |                           |        |           |  |  |

| Cycles:                                                            | 1                            |                           |        |           |  |  |

| Q Cycle Activity:                                                  |                              |                           |        |           |  |  |

| Q1                                                                 | Q2                           | Q3                        |        | Q4        |  |  |

| Decode                                                             | Read<br>literal 'k'          | Proces<br>Data            |        | rite to W |  |  |

| Example 1:                                                         | SUBLW (                      | )2h                       |        |           |  |  |

| Before Instruct<br>W<br>C<br>After Instruction<br>W<br>C<br>Z<br>N | = 01h<br>= ?<br>n<br>= 01h   | esult is po               | sitive |           |  |  |

| Example 2:                                                         | SUBLW (                      | )2h                       |        |           |  |  |

| Before Instruct<br>W<br>C<br>After Instruction<br>W<br>C<br>Z<br>N | = 02h<br>= ?<br>n<br>= 00h   | esult is zei              | ro     |           |  |  |

| Example 3:                                                         | SUBLW (                      | )2h                       |        |           |  |  |

| Before Instruct<br>W<br>C<br>After Instruction<br>W<br>C<br>Z<br>N | = 03h<br>= ?<br>n<br>= FFh;( | 2's comple<br>esult is ne |        |           |  |  |

| SUBWF                                                                      | Subtract                                                                                                                                                                                                      | Subtract W from f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Syntax:                                                                    | SUBWF                                                                                                                                                                                                         | f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |  |  |

| Operands:                                                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |  |  |

| Operation:                                                                 | (f) – (W) –                                                                                                                                                                                                   | → dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |  |  |

| Status Affected:                                                           | N, OV, C,                                                                                                                                                                                                     | DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |  |  |

| Encoding:                                                                  | 0101                                                                                                                                                                                                          | 11da ffi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ff ffff              |  |  |