Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf47k40-e-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.2 Other Special Features

- **Memory Endurance:** The Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles up to 10K for program memory and 100K for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-programmability: These devices can write to their own program memory spaces under internal software control. By using a boot loader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18(L)F2x/ 4xK40 family introduces an optional extension to the PIC18 instruction set, which adds eight new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

- Enhanced Peripheral Pin Select: The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins.

- Enhanced Addressable EUSART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-bit A/D Converter with Computation:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead. It has a new module called ADC<sup>2</sup> with computation features, which provides a digital filter and threshold interrupt functions.

- Windowed Watchdog Timer (WWDT):

- Timer monitoring of overflow and underflow events

- Variable prescaler selection

- Variable window size selection

- All sources configurable in hardware or software

## 1.3 Details on Individual Family Members

Devices in the PIC18(L)F2x/4xK40 family are available in 28-pin and 40/44-pin packages. The block diagram for this device is shown in Figure 1-1.

The devices have the following differences:

- 1. Program Flash Memory

- 2. Data Memory SRAM

- 3. Data Memory EEPROM

- 4. A/D channels

- 5. I/O ports

- 6. Enhanced USART

- 7. Input Voltage Range/Power Consumption

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in the pin summary tables (Table 1 and Table 2).

| REGISTE   | к э-4. Coning             | juration word                       | 1211 (30 000  | siij. Supervi    | 1501            |                 |               |

|-----------|---------------------------|-------------------------------------|---------------|------------------|-----------------|-----------------|---------------|

| R/W-1     | U-1                       | R/W-1                               | R/W-1         | R/W-1            | R/W-1           | R/W-1           | R/W-1         |

| XINST     |                           | DEBUG                               | STVREN        | PPS1WAY          | ZCD             | BOR             | /<1:0>        |

| bit 7     |                           |                                     |               |                  |                 |                 | bit (         |

| Legend:   |                           |                                     |               |                  |                 |                 |               |

| R = Reada | able bit                  | W = Writable                        | bit           | U = Unimplei     | mented bit, rea | d as '1'        |               |

|           | for blank device          | '1' = Bit is set                    |               | '0' = Bit is cle |                 | x = Bit is unki | nown          |

|           |                           |                                     |               |                  |                 |                 |               |

| bit 7     |                           | ded Instruction                     |               |                  |                 |                 |               |

|           |                           | ed Instruction Seed Instruction See |               |                  |                 | (Legacy mode)   |               |

| bit 6     |                           | ited: Read as '1                    |               | u Audressing i   |                 |                 |               |

| bit 5     |                           | bugger Enable b                     |               |                  |                 |                 |               |

| bito      |                           | ound debugger                       |               |                  |                 |                 |               |

|           | 0 = Backgro               | ound debugger                       | enabled       |                  |                 |                 |               |

| bit 4     |                           | ack Overflow/Ur                     |               |                  |                 |                 |               |

|           |                           | verflow or Unde                     |               |                  | ł               |                 |               |

| bit 3     |                           | PSLOCKED bit                        |               |                  |                 |                 |               |

|           |                           | SLOCKED bit                         |               |                  | an unlocking s  | sequence is ex  | ecuted; once  |

|           |                           | CK is set, all ful                  |               |                  |                 |                 |               |

|           | execute                   | SLOCKED bit o<br>d)                 | an de set and | a cleared as n   |                 | a an uniockinę  | g sequence is |

| bit 2     | ZCD: ZCD Di               | ,                                   |               |                  |                 |                 |               |

|           |                           | sabled. ZCD car                     |               |                  | ZCDSEN bit of   | ZCDCON          |               |

|           |                           | vays enabled, Z                     |               |                  |                 |                 |               |

| bit 1-0   | BORV<1:0>:<br>PIC18F2x/4x | Brown-out Res                       | et Voltage Se | lection bit("    |                 |                 |               |

|           |                           | own-out Reset \                     | /oltage (VBOR | ) set to 2.45V   |                 |                 |               |

|           |                           | own-out Reset \                     |               |                  |                 |                 |               |

|           |                           | own-out Reset \<br>own-out Reset \  |               |                  |                 |                 |               |

|           |                           |                                     | onage (veor   | 000002.000       |                 |                 |               |

|           | PIC18LF2x/4               | xK40 device:<br>own-out Reset \     |               | ) set to $1.00V$ |                 |                 |               |

|           |                           | own-out Reset \                     | • •           |                  |                 |                 |               |

|           | 01 = Bro                  | own-out Reset \                     | oltage (VBOR  | ) set to 2.7V    |                 |                 |               |

|           | 00 = Bro                  | own-out Reset \                     | oltage (VBOR  | ) set to 2.85V   |                 |                 |               |

| Note 1 ·  | he higher voltage s       | ettina is recom                     | mended for on | eration at or a  | hove 16 MHz     |                 |               |

#### REGISTER 3-4: Configuration Word 2H (30 0003h): Supervisor

**Note 1:** The higher voltage setting is recommended for operation at or above 16 MHz.

| Name      | Bit 7    | Bit 6               | Bit 5  | Bit 4   | Bit 3  | Bit 2    | Bit 1   | Bit 0   | Register<br>on Page |  |  |

|-----------|----------|---------------------|--------|---------|--------|----------|---------|---------|---------------------|--|--|

| CRCACCH   |          |                     |        | ACC     | <15:8> |          |         |         | 152                 |  |  |

| CRCACCL   |          |                     |        | ACC     | <7:0>  |          |         |         | 153                 |  |  |

| CRCCON0   | EN       | GO                  | BUSY   | ACCM    | —      | _        | SHIFTM  | FULL    | 151                 |  |  |

| CRCCON1   |          | DLEN<3:0> PLEN<3:0> |        |         |        |          |         |         |                     |  |  |

| CRCDATH   |          |                     |        | DATA    | <15:8> |          |         |         | 152                 |  |  |

| CRCDATL   |          | DATA<7:0>           |        |         |        |          |         |         |                     |  |  |

| CRCSHIFTH |          |                     |        | SHIFT   | <15:8> |          |         |         | 153                 |  |  |

| CRCSHIFTL |          |                     |        | SHIF    | T<7:0> |          |         |         | 153                 |  |  |

| CRCXORH   |          |                     |        | X<1     | 5:8>   |          |         |         | 154                 |  |  |

| CRCXORL   | X<7:1> — |                     |        |         |        |          | 154     |         |                     |  |  |

| PMD0      | SYSCMD   | FVRMD               | HLVDMD | CRCMD   | SCANMD | NVMMD    | CLKRMD  | IOCMD   | 68                  |  |  |

| SCANCON0  | SCANEN   | SCANGO              | BUSY   | INVALID | INTM   | —        | MODE    | =<1:0>  | 155                 |  |  |

| SCANHADRU | —        | —                   |        |         | HADF   | R<21:16> |         |         | 157                 |  |  |

| SCANHADRH |          |                     |        | HADR    | <15:8> |          |         |         | 158                 |  |  |

| SCANHADRL |          |                     |        | HADF    | R<7:0> |          |         |         | 158                 |  |  |

| SCANLADRU | —        | —                   |        |         | LADF   | R<21:16> |         |         | 156                 |  |  |

| SCANLADRH |          |                     |        | LADR    | <15:8> |          |         |         | 156                 |  |  |

| SCANLADRL |          |                     |        | LADF    | R<7:0> |          |         |         | 157                 |  |  |

| SCANTRIG  | —        | —                   | _      | _       |        | TSEL     | _<3:0>  |         | 159                 |  |  |

| INTCON    | GIE/GIEH | PEIE/GIEL           | IPEN   | _       | —      | INT2EDG  | INT1EDG | INT0EDG | 170                 |  |  |

| PIR7      | SCANIF   | CRCIF               | NVMIF  |         |        |          |         | CWG1IF  | 178                 |  |  |

| PIE7      | SCANIE   | CRCIE               | NVMIE  | _       | _      | _        | _       | CWG1IE  | 186                 |  |  |

| IPR7      | SCANIP   | CRCIP               | NVMIP  | _       | _      | _        | _       | CWG1IP  | 194                 |  |  |

| TABLE 13-5: | SUMMARY OF REGISTERS ASSOCIATED WITH CRC |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the CRC module.

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISx7  | TRISx6  | TRISx5  | TRISx4  | TRISx3  | TRISx2  | TRISx1  | TRISx0  |

| bit 7   |         |         | •       |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

#### REGISTER 15-2: TRISx: TRI-STATE CONTROL REGISTER

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0

- TRISx<7:0>: TRISx Port I/O Tri-state Control bits

- 1 = Port output driver is disabled

- 0 = Port output driver is enabled

|       | Dev        | /ice          |                       |                       |        |        |        |        |        |        |

|-------|------------|---------------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|

| Name  | 28<br>Pins | 40/44<br>Pins | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| TRISA | Х          | Х             | TRISA7                | TRISA6                | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| TRISB | Х          | Х             | TRISB7 <sup>(1)</sup> | TRISB6 <sup>(1)</sup> | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| TRISC | Х          | Х             | TRISC7                | TRISC6                | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| TRISD | Х          |               | _                     |                       | _      | _      | —      | _      | _      | _      |

|       |            | Х             | TRISD7                | TRISD6                | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

| TRISE | Х          |               | _                     |                       |        | _      | —      | _      | _      | _      |

|       |            | Х             | —                     | —                     | _      | _      | (2)    | TRISE2 | TRISE1 | TRISE0 |

Note 1: Bits RB6 and RB7 read '1' while in Debug mode.

2: TRISE3 bit is read-only, and will read '1'

| R/W-0/0          | R/W-0/0                                               | R/W-0/0           | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|------------------|-------------------------------------------------------|-------------------|---------|------------------------------------|---------|---------|---------|--|--|

| ODCx7            | ODCx6                                                 | ODCx5             | ODCx4   | ODCx3                              | ODCx2   | ODCx1   | ODCx0   |  |  |

| bit 7            |                                                       |                   |         |                                    |         |         | bit 0   |  |  |

|                  |                                                       |                   |         |                                    |         |         |         |  |  |

| Legend:          |                                                       |                   |         |                                    |         |         |         |  |  |

| R = Readable     | bit                                                   | W = Writable      | bit     | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| '1' = Bit is set |                                                       | '0' = Bit is clea | ared    | x = Bit is unknown                 |         |         |         |  |  |

| -n/n = Value at  | -n/n = Value at POR and BOR/Value at all other Resets |                   |         |                                    |         |         |         |  |  |

#### REGISTER 15-6: ODCONx: OPEN-DRAIN CONTROL REGISTER

bit 7-0

ODCx<7:0>: Open-Drain Configuration on Pins Rx<7:0>

1 = Output drives only low-going signals (sink current only)

0 = Output drives both high-going and low-going signals (source and sink current)

|        | Device     |               |       |       |       |       |       |       |       |       |

|--------|------------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name   | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| ODCONA | Х          | Х             | ODCA7 | ODCA6 | ODCA5 | ODCA4 | ODCA3 | ODCA2 | ODCA1 | ODCA0 |

| ODCONB | Х          | Х             | ODCB7 | ODCB6 | ODCB5 | ODCB4 | ODCB3 | ODCB2 | ODCB1 | ODCB0 |

| ODCONC | Х          | Х             | ODCC7 | ODCC6 | ODCC5 | ODCC4 | ODCC3 | ODCC2 | ODCC1 | ODCC0 |

| ODCOND | Х          |               | _     | _     | —     | —     | _     | _     | _     | —     |

|        |            | Х             | ODCD7 | ODCD6 | ODCD5 | ODCD4 | ODCD3 | ODCD2 | ODCD1 | ODCD0 |

| ODCONE | Х          |               | _     | _     | _     | _     | _     | _     |       | _     |

|        |            | Х             | _     | _     | _     | _     | _     | ODCE2 | ODCE1 | ODCE0 |

#### TABLE 15-7:OPEN-DRAIN CONTROL REGISTERS

# PIC18(L)F27/47K40

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                        | R/W-0/0                               | R/W-0/0        | R/W-0/0        | R/W-0/0                  | R/W-0/0          | R/W-0/0      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|----------------|--------------------------|------------------|--------------|

|                  | T0CS<2:0>                                                                                                                                                                                                                      |                                       | TOASYNC        |                | TOCKP                    | °S<3:0>          |              |

| bit 7            |                                                                                                                                                                                                                                |                                       |                | •              |                          |                  | bit          |

|                  |                                                                                                                                                                                                                                |                                       |                |                |                          |                  |              |

| Legend:          |                                                                                                                                                                                                                                |                                       |                |                |                          |                  |              |

| R = Readable     | bit                                                                                                                                                                                                                            | W = Writable                          | bit            | U = Unimpler   | mented bit, read         | l as '0'         |              |

| u = Bit is unch  | anged                                                                                                                                                                                                                          | x = Bit is unki                       | nown           | -n/n = Value a | at POR and BO            | R/Value at all c | other Resets |

| '1' = Bit is set |                                                                                                                                                                                                                                | '0' = Bit is cle                      | ared           |                |                          |                  |              |

| bit 7-5<br>bit 4 | 111 = Resen<br>110 = Resen<br>101 = SOSC<br>100 = LFINT<br>011 = HFINT<br>010 = Fosc/4<br>001 = Pin se<br>000 = Pin se                                                                                                         | ved<br>OSC<br>TOSC                    | (IPPS (Inverte | d)<br>/erted)  |                          |                  |              |

|                  | 1 = The inpu                                                                                                                                                                                                                   |                                       | counter is not | synchronized f | to system clock<br>osc/4 | S                |              |

| bit 3-0          | <b>TOCKPS&lt;3:0</b><br>1111 = 1:327<br>1110 = 1:163<br>1101 = 1:819<br>1001 = 1:409<br>1011 = 1:204<br>1010 = 1:102<br>1001 = 1:512<br>1000 = 1:512<br>1000 = 1:256<br>0111 = 1:128<br>0100 = 1:4<br>0011 = 1:2<br>0000 = 1:1 | 384<br>92<br>96<br>48<br>24<br>2<br>5 | ate Select bit |                |                          |                  |              |

#### 20.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal can also gate the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 20-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

| Rev. 10.000 1988<br>5/30/2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE 0b00001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| TMRx_ers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| PRx 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| $TMRx \left( \begin{array}{c} 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2 \\ 1 \\ 2 \\ 2$ |  |

| TMRx_postscaled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PWM Duty   3     Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Name   | Bit 7  | Bit 6 | Bit 5         | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0   | Register<br>on page |

|--------|--------|-------|---------------|--------|-------|--------|---------|---------|---------------------|

| PIE2   | HLVDIE | ZCDIE | _             | _      | _     | —      | C2IE    | C1IE    | 181                 |

| PIR2   | HLVDIF | ZCDIF | _             | _      | _     | —      | C2IF    | C1IF    | 173                 |

| IPR2   | HLVDIP | ZCDIP |               |        |       | —      | C2IP    | C1IP    | 189                 |

| ZCDCON | ZCDSEN | _     | ZCDOUT        | ZCDPOL | _     | _      | ZCDINTP | ZCDINTN | 294                 |

| PMD2   | _      | DACMD | <b>ADC</b> MD | _      | _     | CMP2MD | CMP1MD  | ZCDMD   | 70                  |

#### TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### TABLE 23-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit 15/7 | Bit 14/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|----------|----------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 15:8 | XINST    | _        | DEBUG    | STVREN   | PPS1WAY  | ZCD      | BORV1   | BORV0   | 24                  |

|         | 7:0  | BOREN1   | BOREN0   | LPBOREN  | _        | _        | _        | PWRTE   | MCLRE   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

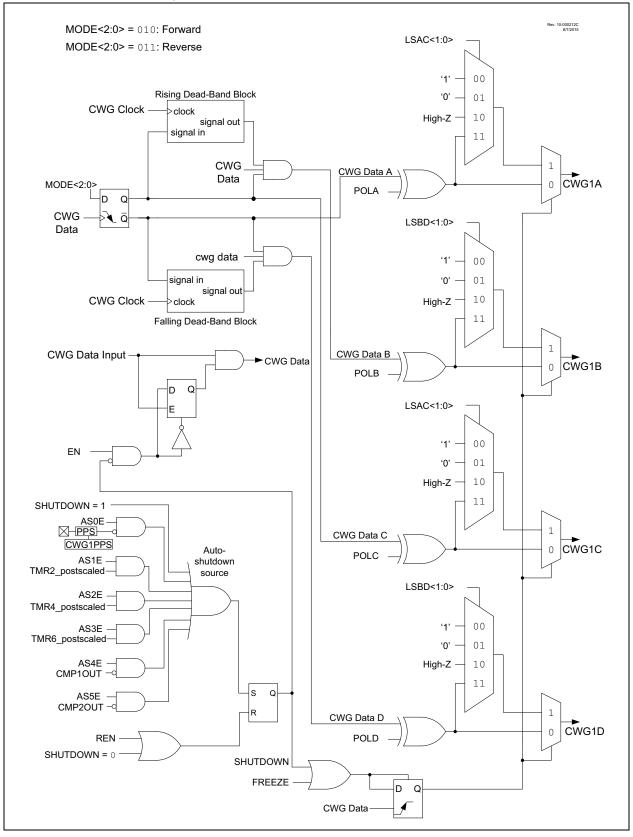

## FIGURE 24-6: SIMPLIFIED CWG BLOCK DIAGRAM (FORWARD AND REVERSE FULL-BRIDGE MODES)

### 24.7 Rising Edge and Reverse Dead Band

In Half-Bridge mode, the rising edge dead band delays the turn-on of the CWG1A output after the rising edge of the CWG data input. In Full-Bridge mode, the reverse dead-band delay is only inserted when changing directions from Forward mode to Reverse mode, and only the modulated output CWG1B is affected.

The CWG1DBR register determines the duration of the dead-band interval on the rising edge of the input source signal. This duration is from 0 to 64 periods of the CWG clock.

Dead band is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBR register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBR is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input, after the LD bit (Register 24-1) is set. Refer to Figure 24-12 for an example.

## 24.8 Falling Edge and Forward Dead Band

In Half-Bridge mode, the falling edge dead band delays the turn-on of the CWG1B output at the falling edge of the CWG data input. In Full-Bridge mode, the forward dead-band delay is only inserted when changing directions from Reverse mode to Forward mode, and only the modulated output CWG1D is affected.

The CWG1DBF register determines the duration of the dead-band interval on the falling edge of the input source signal. This duration is from zero to 64 periods of CWG clock.

Dead-band delay is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWG1DBF register value is double-buffered. When EN = 0 (Register 24-1), the buffer is loaded when CWG1DBF is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input after the LD (Register 24-1) is set. Refer to Figure 24-13 for an example.

# PIC18(L)F27/47K40

| REGISTER 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -6: CWG1A                                                                                                                                             | S0: CWG Al                                                                | JTO-SHUTD                                                   | OWN CONTR                                                                                                        | OL REGISTE                                                         | R 0           |             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------|-------------|--|--|--|

| R/W/HS/HC-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 R/W-0/0                                                                                                                                             | R/W-0/0                                                                   | R/W-1/1                                                     | R/W-0/0                                                                                                          | R/W-1/1                                                            | U-0           | U-0         |  |  |  |

| SHUTDOWN REN                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                       | N LSBD<1:0>                                                               |                                                             | LSAC                                                                                                             | C<1:0>                                                             |               | _           |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |                                                                           |                                                             |                                                                                                                  |                                                                    |               | bit C       |  |  |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                       |                                                                           |                                                             |                                                                                                                  |                                                                    |               |             |  |  |  |

| R = Readable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                | it                                                                                                                                                    | W = Writable                                                              | hit                                                         | =   Inimplem                                                                                                     | nented hit read                                                    | as 'O'        |             |  |  |  |

| u = Bit is uncha                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                       | x = Bit is unk                                                            |                                                             | U = Unimplemented bit, read as '0'<br>-n/n = Value at POR and BOR/Value at all other Resets                      |                                                                    |               |             |  |  |  |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ngeu                                                                                                                                                  | '0' = Bit is cle                                                          |                                                             |                                                                                                                  | s set/cleared by                                                   |               |             |  |  |  |

| q = Value deper                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nde on condition                                                                                                                                      |                                                                           | aleu                                                        |                                                                                                                  | s sel/cleared by                                                   | Taluwale      |             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                       | 1                                                                         |                                                             |                                                                                                                  |                                                                    |               |             |  |  |  |

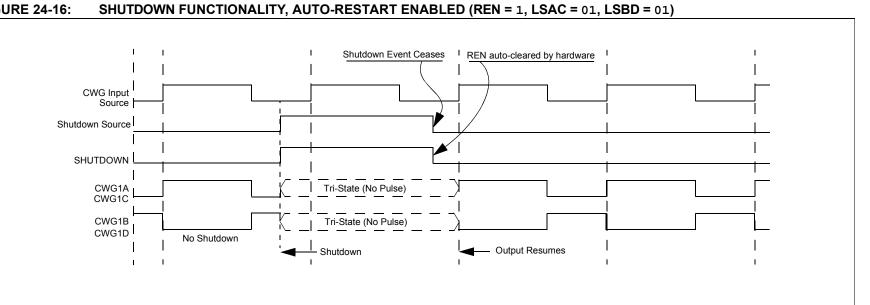

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7 SHUTDOWN: Auto-Shutdown Event Status bit <sup>(1,2)</sup><br>1 = An auto-shutdown state is in effect<br>0 = No auto-shutdown event has occurred |                                                                           |                                                             |                                                                                                                  |                                                                    |               |             |  |  |  |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>REN:</b> Auto-Restart Enable bit<br>1 = Auto-restart is enabled<br>0 = Auto-restart is disabled                                                    |                                                                           |                                                             |                                                                                                                  |                                                                    |               |             |  |  |  |

| bit 5-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11 = A logic<br>10 = A logic<br>01 = Pin is tr<br>00 = The ina                                                                                        | '1' is placed on<br>'0' is placed on<br>i-stated on CV<br>active state of | n CWG1B/D v<br>n CWG1B/D v<br>VG1B/D when<br>the pin, inclu | -Shutdown State<br>when an auto-sh<br>when an auto-sh<br>an auto-shutdo<br>uding polarity, is<br>hutdown event o | utdown event o<br>utdown event o<br>wn event occur<br>placed on CV | occurs.<br>s. | he requirec |  |  |  |

| bit 3-2 <b>LSAC&lt;1:0&gt;:</b> CWG1A and CWG1C Auto-Shutdown State Control bits<br>11 = A logic '1' is placed on CWG1A/C when an auto-shutdown event occurs.<br>10 = A logic '0' is placed on CWG1A/C when an auto-shutdown event occurs.<br>01 = Pin is tri-stated on CWG1A/C when an auto-shutdown event occurs.<br>00 = The inactive state of the pin, including polarity, is placed on CWG1A/C after the required dead-band interval when an auto-shutdown event occurs. |                                                                                                                                                       |                                                                           |                                                             |                                                                                                                  |                                                                    |               |             |  |  |  |

| bit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Unimplemer                                                                                                                                            | nted: Read as                                                             | '0'                                                         |                                                                                                                  |                                                                    |               |             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                     |                                                                           |                                                             | 4-1), to place the                                                                                               | -                                                                  |               | •           |  |  |  |

## 2: The outputs will remain in auto-shutdown state until the next rising edge of the CWG data input after this bit is cleared.

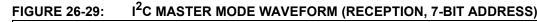

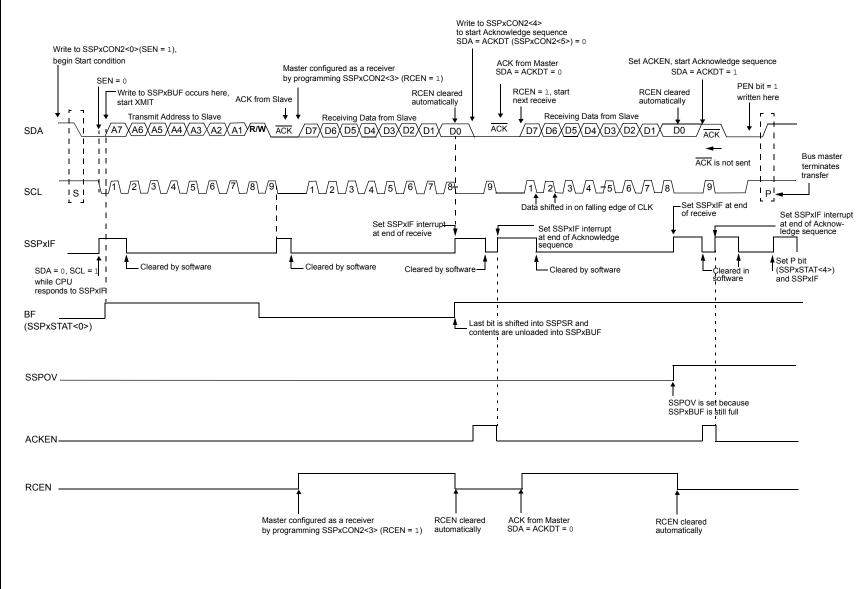

#### 26.6.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

## 26.7 Register Definitions: I<sup>2</sup>C Mode

The MSSPx module has seven registers for  $I^2C$  operation.

#### These are:

- MSSP Status Register (SSPxSTAT)

- MSSP Control Register 1 (SSPxCON1)

- MSSP Control Register 2 (SSPxCON2)

- MSSP Control Register 3 (SSPxCON3)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSP Address Register (SSPxADD)

- I<sup>2</sup>C Slave Address Mask Register (SSPxMSK)

- MSSP Shift Register (SSPSR) not directly accessible

SSPxCON1, SSPxCON2, SSPxCON3 and SSPxSTAT

are the Control and Status registers in I<sup>2</sup>C mode operation. The SSPxCON1, SSPxCON2, and SSPxCON3 registers are readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write. SSPSR is the Shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from. SSPxADD contains the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPxADD act as the Baud Rate Generator reload value.

SSPxMSK holds the slave address mask value when the module is configured for 7-Bit Address Masking mode. While it is a separate register, it shares the same SFR address as SSPxADD; it is only accessible when the SSPM<3:0> bits are specifically set to permit access. In receive operations, SSPSR and SSPxBUF together, create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set. During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPSR.

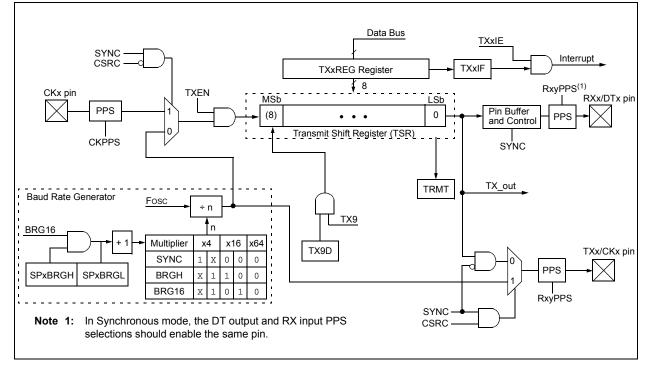

## 27.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

Note: The PIC18(L)F27/47K40 devices have two EUSARTs. Therefore, all information in this section refers to both EUSART 1 and EUSART 2.

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous svstem. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits. serial EEPROMs or other microcontrollers.

These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- · Two-character input buffer

- · One-character output buffer

- · Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- · Input buffer overrun error detection

- · Received character framing error detection

- · Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 27-1 and Figure 27-2.

#### FIGURE 27-1: EUSART TRANSMIT BLOCK DIAGRAM

© 2016-2017 Microchip Technology Inc.

#### 27.2.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 27-2. The data is received on the RXx/DTx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCxREG register.

#### 27.2.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCxSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RXx/DTx I/O pin as an input.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

## 27.2.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 27.2.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCxIF interrupt flag bit of the PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCxREG register.

#### 27.2.2.3 Receive Interrupts

The RCxIF interrupt flag bit of the PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCxIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCxIF interrupts are enabled by setting all of the following bits:

- RCxIE, Interrupt Enable bit of the PIE3 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCxIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

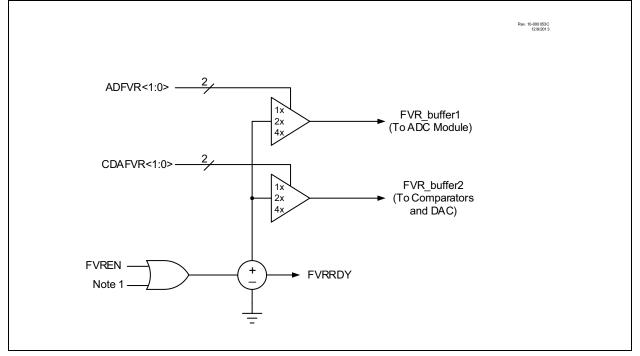

## 28.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- · ADC positive reference

- Comparator input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

#### 28.1 Independent Gain Amplifiers

The output of the FVR, which is connected to the ADC, Comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels. The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 31.0 "Analog-to-Digital Converter with Computation (ADC2) Module"** for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference **Section 30.0 "5-Bit Digital-to-Analog Converter (DAC) Module**" and **Section 32.0 "Comparator Module**" for additional information.

## 28.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set.

## FIGURE 28-1: VOLTAGE REFERENCE BLOCK DIAGRAM

| R-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R-0/0                                                                                                     | R-0/0                                                                                                   | R/HS/HC-0/0     | U-0                                                   | R-0/0            | R-0/0       | R-0/0 |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------|------------------|-------------|-------|--|--|

| ADAOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ADAOV ADUTHR                                                                                              |                                                                                                         | ADMATH          | —                                                     |                  | ADSTAT<2:0> |       |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                           |                                                                                                         |                 |                                                       |                  |             | bit 0 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                           |                                                                                                         |                 |                                                       |                  |             |       |  |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                           |                                                                                                         |                 |                                                       |                  |             |       |  |  |

| R = Readable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           | W = Writable bit                                                                                        |                 | U = Unimplemented bit, read as '0'                    |                  |             |       |  |  |

| u = Bit is unchanged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                           | x = Bit is unknown                                                                                      |                 | -n/n = Value at POR and BOR/Value at all other Resets |                  |             |       |  |  |

| '1' = Bit is se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | et                                                                                                        | '0' = Bit is cleared                                                                                    |                 | HS/HC = Bit                                           | is set/cleared b | y hardware  |       |  |  |

| bit 7 <b>ADAOV</b> : ADC Accumulator Overflow bit<br>1 = ADC accumulator or ADERR calculation have overflowed<br>0 = ADC accumulator and ADERR calculation have not overflowed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                           |                                                                                                         |                 |                                                       |                  |             |       |  |  |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6 <b>ADUTHR</b> : ADC Module Greater-than Upper Threshold Flag bit<br>1 = ADERR >ADUTH<br>0 = ADERR≤ADUTH |                                                                                                         |                 |                                                       |                  |             |       |  |  |