Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.6K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf47k40t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **15.4 Register Definitions: Port Control**

| R/W-x/u      | R/W-x/u | R/W-x/u                           | R/W-x/u | R/W-x/u                         | R/W-x/u          | R/W-x/u  | R/W-x/u |

|--------------|---------|-----------------------------------|---------|---------------------------------|------------------|----------|---------|

| Rx7          | Rx6     | Rx5                               | Rx4     | Rx3                             | Rx2              | Rx1      | Rx0     |

| bit 7        |         |                                   |         |                                 |                  | •        | bit     |

|              |         |                                   |         |                                 |                  |          |         |

|              |         |                                   |         |                                 |                  |          |         |

| Legend:      |         |                                   |         |                                 |                  |          |         |

| R = Readable | bit     | W = Writable                      | bit     | U = Unimplen                    | nented bit, read | d as '0' |         |

| •            |         | W = Writable<br>'0' = Bit is clea |         | U = Unimplen<br>x = Bit is unkr | ,                | d as '0' |         |

REGISTER 15-1: PORTx: PORTx REGISTER<sup>(1)</sup>

bit 7-0 **Rx<7:0>:** Rx7:Rx0 Port I/O Value bits 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTx are actually written to the corresponding LATx register. Reads from PORTx register return actual I/O pin values.

|       | Dev        | /ice          | Bit 7              |                    |       |       |                    |       |       |       |  |

|-------|------------|---------------|--------------------|--------------------|-------|-------|--------------------|-------|-------|-------|--|

| Name  | 28<br>Pins | 40/44<br>Pins |                    | Bit 6              | Bit 5 | Bit 4 | Bit 3              | Bit 2 | Bit 1 | Bit 0 |  |

| PORTA | Х          | Х             | RA7                | RA6                | RA5   | RA4   | RA3                | RA2   | RA1   | RA0   |  |

| PORTB | Х          | Х             | RB7 <sup>(1)</sup> | RB6 <sup>(1)</sup> | RB5   | RB4   | RB3                | RB2   | RB1   | RB0   |  |

| PORTC | Х          | Х             | RC7                | RC6                | RC5   | RC4   | RC3                | RC2   | RC1   | RC0   |  |

| PORTD | Х          |               | _                  | _                  | _     | —     | —                  | _     | _     | _     |  |

|       |            | Х             | RD7                | RD6                | RD5   | RD4   | RD3                | RD2   | RD1   | RD0   |  |

| PORTE | Х          |               | _                  | _                  | _     | _     | RE3 <sup>(2)</sup> | _     | _     | _     |  |

|       |            | Х             | _                  | _                  | _     | —     | RE3 <sup>(2)</sup> | RE2   | RE1   | RE0   |  |

TABLE 15-2: PORT REGISTERS

Note 1: Bits RB6 and RB7 read '1' while in Debug mode.

2: Bit PORTE3 is read-only, and will read '1' when MCLRE = 1 (Master Clear enabled).

| R/W-x/u                                               | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------------------------------------------------------|---------|--------------------|---------|------------------------------------|---------|---------|---------|--|

| LATx7                                                 | LATx6   | LATx5              | LATx4   | LATx3                              | LATx2   | LATx1   | LATx0   |  |

| bit 7                                                 |         |                    |         |                                    |         |         | bit 0   |  |

|                                                       |         |                    |         |                                    |         |         |         |  |

| Legend:                                               |         |                    |         |                                    |         |         |         |  |

| R = Readable bit W = Writable bit                     |         |                    | bit     | U = Unimplemented bit, read as '0' |         |         |         |  |

| '1' = Bit is set '0' = Bit is cleared                 |         | x = Bit is unknown |         |                                    |         |         |         |  |

| -n/n = Value at POR and BOR/Value at all other Resets |         |                    |         |                                    |         |         |         |  |

#### REGISTER 15-3: LATx: LATx REGISTER<sup>(1)</sup>

bit 7-0 LATx<7:0>: Rx7:Rx0 Output Latch Value bits

**Note 1:** Writes to LATx are equivalent with writes to the corresponding PORTx register. Reads from LATx register return register values, not I/O pin values.

|      | Dev        | vice          |       |       |       |       |       |       |       |       |

|------|------------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Name | 28<br>Pins | 40/44<br>Pins | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| LATA | Х          | Х             | LATA7 | LATA6 | LATA5 | LATA4 | LATA3 | LATA2 | LATA1 | LATA0 |

| LATB | Х          | Х             | LATB7 | LATB6 | LATB5 | LATB4 | LATB3 | LATB2 | LATB1 | LATB0 |

| LATC | Х          | Х             | LATC7 | LATC6 | LATC5 | LATC4 | LATC3 | LATC2 | LATC1 | LATC0 |

| LATD | Х          |               | _     | _     | _     | _     | —     | _     | —     | _     |

|      |            | Х             | LATD7 | LATD6 | LATD5 | LATD4 | LATD3 | LATD2 | LATD1 | LATD0 |

| LATE | Х          |               | _     | —     | —     | —     | —     | _     | _     | _     |

|      |            | Х             | _     | —     | —     | _     | —     | LATE2 | LATE1 | LATE0 |

#### TABLE 15-4: LAT REGISTERS

### 19.2 Timer1/3/5 Operation

The Timer1/3/5 module is a 16-bit incrementing counter which is accessed through the TMRxH:TMRxL register pair. Writes to TMRxH or TMRxL directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1/3/5 is enabled by configuring the ON and GE bits in the TxCON and TxGCON registers, respectively. Table 19-2 displays the Timer1/3/5 enable selections.

## TABLE 19-2:TIMER1/3/5 ENABLESELECTIONS

| ON | GE | Timer1/3/5<br>Operation |

|----|----|-------------------------|

| 1  | 1  | Count Enabled           |

| 1  | 0  | Always On               |

| 0  | 1  | Off                     |

| 0  | 0  | Off                     |

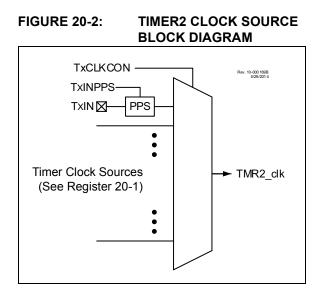

## 19.3 Clock Source Selection

The CS<3:0> bits of the TMRxCLK register (Register 19-3) are used to select the clock source for Timer1/3/5. The four TMRxCLK bits allow the selection of several possible synchronous and asynchronous clock sources. Register 19-3 displays the clock source selections.

#### 19.3.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMRxH:TMRxL register pair will increment on multiples of Fosc as determined by the Timer1/3/5 prescaler.

When the Fosc internal clock source is selected, the Timer1/3/5 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1/3/5 value. To utilize the full resolution of Timer1/3/5, an asynchronous input signal must be used to gate the Timer1/3/5 clock input.

The following asynchronous sources may be used at the Timer1/3/5 gate:

- · Asynchronous event on the TxGPPS pin

- TMR0OUT

- TMR1/3/5OUT (excluding the TMR for which it is being used)

- TMR 2/4/6OUT (post-scaled)

- CCP1/2OUT

- PWM3/4OUT

- CMP1/2OUT

- ZCDOUT

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge after any one or    |

|       | more of the following conditions:            |

- Timer1/3/5 enabled after POR

- Write to TMRxH or TMRxL

- Timer1/3/5 is disabled

- Timer1/3/5 is disabled (TMRxON = 0) when TxCKI is high then Timer1/3/5 is enabled (TMRxON = 1) when TxCKI is low.

### 19.3.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1/3/5 module may work as a timer or a counter.

When enabled to count, Timer1/3/5 is incremented on the rising edge of the external clock input of the TxCKIPPS pin. This external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated secondary internal oscillator circuit.

## 20.1 Timer2 Operation

Timer2 operates in three major modes:

- · Free Running Period

- One-shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 20-1 lists the options.

In all modes, the TMR2 count register is incremented on the rising edge of the clock signal from the programmable prescaler. When TMR2 equals T2PR, a high level is output to the postscaler counter. TMR2 is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a TMR2 count Reset. In Gate modes the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the TMR2 count is reset on either the level or edge from the external source.

The TMR2 and T2PR registers are both directly readable and writable. The TMR2 register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- · a write to the TMR2 register

- a write to the T2CON register

- any device Reset

- External Reset Source event that resets the timer.

| Note: | TMR2     | is | not | cleared | when | T2CON | is |

|-------|----------|----|-----|---------|------|-------|----|

|       | written. |    |     |         |      |       |    |

#### 20.1.1 FREE RUNNING PERIOD MODE

The value of TMR2 is compared to that of the Period register, T2PR, on each clock cycle. When the two values match, the comparator resets the value of TMR2 to 00h on the next cycle and increments the output

postscaler counter. When the postscaler count equals the value in the OUTPS<4:0> bits of the TMRxCON1 register then a one clock period wide pulse occurs on the TMR2\_postscaled output, and the postscaler count is cleared.

#### 20.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when TMR2 matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS<4:0> values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

#### 20.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

## 20.2 Timer2 Output

The Timer2 module's primary output is TMR2\_postscaled, which pulses for a single TMR2\_clk period when the postscaler counter matches the value in the OUTPS bits of the TMR2CON register. The T2PR postscaler is incremented each time the TMR2 value matches the T2PR value. This signal can be selected as an input to several other input modules:

- The ADC module, as an Auto-conversion Trigger

- · COG, as an auto-shutdown source

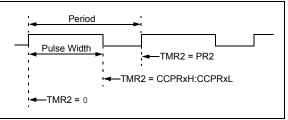

In addition, the Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual TMR2 value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See **Section 21.0 "Capture/Compare/PWM Module"** for more details on setting up Timer2 for use with the CCP, as well as the timing diagrams in **Section 20.5 "Operation Examples"** for examples of how the varying Timer2 modes affect CCP PWM output.

## 20.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2, Timer4 and Timer6 with the T2RST, T4RST and T6RST registers, respectively. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE<4:0> bits of the TMRxHLT register. Edge-Triggered modes require six Timer clock periods between external triggers. Level-Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

### 20.4 Timer2 Interrupt

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE4 register. Interrupt timing is illustrated in Figure 20-3.

#### FIGURE 20-3: TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM

|                 | Rev. 10.00005A<br>47/2016                                |

|-----------------|----------------------------------------------------------|

| CKPS            | 06010                                                    |

| PRx             | 1                                                        |

| OUTPS           | 0b0001                                                   |

| TMRx_clk        |                                                          |

| TMRx            |                                                          |

| TMRx_postscaled |                                                          |

| TMRxIF          | (1) (2)                                                  |

| Note 1:<br>2:   | Synchronization may take as many as 2 instruction cycles |

## 20.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

#### 21.4.1 CCPx PIN CONFIGURATION

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See **Section 17.0 "Peripheral Pin Select (PPS) Module"** for more details.

The CCP output can also be used as an input for other peripherals.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

#### 21.4.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 19.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 21.4.3 AUTO-CONVERSION TRIGGER

All CCPx modes set the CCP interrupt flag (CCPxIF). When this flag is set and a match occurs, an auto-conversion trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to **Section 31.2.5 "Auto-Conversion Trigger"** for more information.

Note: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Auto-conversion Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring

#### 21.4.4 COMPARE DURING SLEEP

Since FOSC is shut down during Sleep mode, the Compare mode will not function properly during Sleep, unless the timer is running. The device will wake on interrupt (if enabled).

#### 21.5 **PWM Overview**

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the ON state and the low portion of the signal is considered the OFF state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse-width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 21-3 shows a typical waveform of the PWM signal.

#### 21.5.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- T2CON registers

- · CCPRxL and CCPRxH registers

- CCPxCON registers

It is required to have Fosc/4 as the clock input to TMR2/4/6 for correct PWM operation. Figure 21-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

#### FIGURE 21-3: CCP PWM OUTPUT SIGNAL

| R/W-0/0          | R/W-0/0                                                                                                                                            | R/W-0/0                                                                                                                                     | R/W-0/0               | R/W-0/0       | R-0/0           | R/HC-0/0          | R/HC-0/0    |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|-----------------|-------------------|-------------|--|--|--|--|

| SPEN             | RX9                                                                                                                                                | SREN                                                                                                                                        | CREN                  | ADDEN         | FERR            | OERR              | RX9D        |  |  |  |  |

| bit 7            | ·                                                                                                                                                  |                                                                                                                                             | ·                     |               | ·               | ·                 | bit (       |  |  |  |  |

| Legend:          |                                                                                                                                                    |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

| R = Readable     | e bit                                                                                                                                              | W = Writable                                                                                                                                | bit                   | HC = Bit is o | cleared by hard | ware              |             |  |  |  |  |

| u = Bit is uncl  |                                                                                                                                                    | x = Bit is unk                                                                                                                              |                       |               | -               | OR/Value at all c | ther Resets |  |  |  |  |

| '1' = Bit is set | •                                                                                                                                                  | '0' = Bit is cle                                                                                                                            | ared                  |               |                 |                   |             |  |  |  |  |

| bit 7            | SPEN: Seria                                                                                                                                        | l Port Enable b                                                                                                                             | it                    |               |                 |                   |             |  |  |  |  |

|                  | 1 = Serial po                                                                                                                                      |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

|                  |                                                                                                                                                    | ort disabled (he                                                                                                                            | ld in Reset)          |               |                 |                   |             |  |  |  |  |

| bit 6            | <b>RX9:</b> 9-Bit R                                                                                                                                | eceive Enable                                                                                                                               | bit                   |               |                 |                   |             |  |  |  |  |

|                  |                                                                                                                                                    | 9-bit reception<br>8-bit reception                                                                                                          |                       |               |                 |                   |             |  |  |  |  |

| bit 5            | SREN: Singl                                                                                                                                        | e Receive Ena                                                                                                                               | ble bit               |               |                 |                   |             |  |  |  |  |

|                  | <u>Asynchronou</u>                                                                                                                                 | <u>us mode</u> :                                                                                                                            |                       |               |                 |                   |             |  |  |  |  |

|                  | Don't care                                                                                                                                         | •                                                                                                                                           |                       |               |                 |                   |             |  |  |  |  |

|                  | Synchronous mode – Master:                                                                                                                         |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

|                  | 1 = Enables single receive                                                                                                                         |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

|                  |                                                                                                                                                    | <ul> <li>Disables single receive</li> <li>This bit is cleared after reception is complete.</li> </ul>                                       |                       |               |                 |                   |             |  |  |  |  |

|                  |                                                                                                                                                    | Synchronous mode – Slave                                                                                                                    |                       |               |                 |                   |             |  |  |  |  |

|                  | Don't care                                                                                                                                         |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

| bit 4            | CREN: Cont                                                                                                                                         | inuous Receive                                                                                                                              | e Enable bit          |               |                 |                   |             |  |  |  |  |

|                  | <u>Asynchronou</u>                                                                                                                                 | <u>us mode</u> :                                                                                                                            |                       |               |                 |                   |             |  |  |  |  |

|                  | 1 = Enables                                                                                                                                        |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

|                  |                                                                                                                                                    | 0 = Disables receiver                                                                                                                       |                       |               |                 |                   |             |  |  |  |  |

|                  | -                                                                                                                                                  | Synchronous mode:                                                                                                                           |                       |               |                 |                   |             |  |  |  |  |

|                  | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

| bit 3            | ADDEN: Address Detect Enable bit                                                                                                                   |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

|                  |                                                                                                                                                    | Asynchronous mode 9-bit (RX9 = 1):                                                                                                          |                       |               |                 |                   |             |  |  |  |  |

|                  | -                                                                                                                                                  | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set                                              |                       |               |                 |                   |             |  |  |  |  |

|                  |                                                                                                                                                    | 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit                                              |                       |               |                 |                   |             |  |  |  |  |

|                  |                                                                                                                                                    | <u>us mode 8-bit (l</u>                                                                                                                     | <del>RX9 = 0)</del> : |               |                 |                   |             |  |  |  |  |

|                  | Don't care                                                                                                                                         |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

| bit 2            | FERR: Fram                                                                                                                                         | -                                                                                                                                           |                       |               | ~ · · ·         |                   |             |  |  |  |  |

|                  | •                                                                                                                                                  | <ul> <li>1 = Framing error (can be updated by reading RCxREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul> |                       |               |                 |                   |             |  |  |  |  |

| bit 1            | OERR: Over                                                                                                                                         | run Error bit                                                                                                                               |                       |               |                 |                   |             |  |  |  |  |

|                  | 1 = Overrun<br>0 = No over                                                                                                                         | error (can be o<br>run error                                                                                                                | cleared by clea       | ring bit CREN | 1)              |                   |             |  |  |  |  |

|                  |                                                                                                                                                    |                                                                                                                                             |                       |               |                 |                   |             |  |  |  |  |

| bit 0            | RX9D: Ninth                                                                                                                                        | bit of Received                                                                                                                             | d Data                |               |                 |                   |             |  |  |  |  |

## REGISTER 27-2: RCxSTA: RECEIVE STATUS AND CONTROL REGISTER

#### 31.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| The ADIF bit is set at the completion of |

|------------------------------------------|

| every conversion, regardless of whether  |

| or not the ADC interrupt is enabled.     |

|                                          |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

#### 31.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bits of the ADCON0 register controls the output format.

Figure 31-3 shows the two output formats.

#### FIGURE 31-3: 10-BIT ADC CONVERSION RESULT FORMAT

## 31.3 ADC Acquisition Requirements

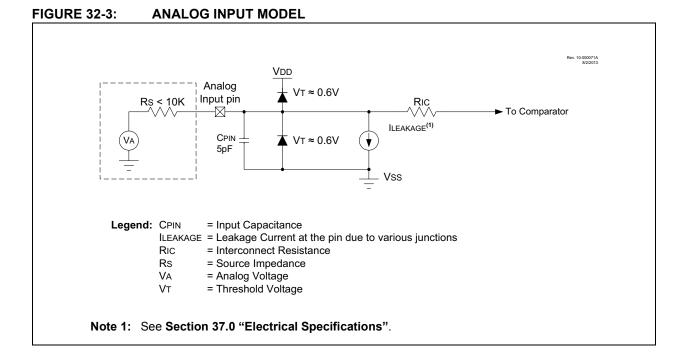

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 31-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 31-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be completed before the conversion can be started. To calculate the minimum acquisition time, Equation 31-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 31-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

*The value for TC can be approximated with the following equations:*

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad ;combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

ł

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)

= 1.37\mus

Therefore:

$$TACQ = 2\mu s + 892ns + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

| U-0                                                                          | U-0                                                        | U-0             | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|------------------------------------|---------|---------|---------|---------|--|

| _                                                                            | _                                                          | —               | ADCAP<4:0>                         |         |         |         |         |  |

| bit 7                                                                        |                                                            |                 | ·                                  |         |         |         | bit 0   |  |

|                                                                              |                                                            |                 |                                    |         |         |         |         |  |

| Legend:                                                                      |                                                            |                 |                                    |         |         |         |         |  |

| R = Readable bit W = Writable bit                                            |                                                            | bit             | U = Unimplemented bit, read as '0' |         |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at |                                                            | R/Value at all  | other Resets                       |         |         |         |         |  |

| '1' = Bit is set '0' = Bit is cleared                                        |                                                            | ared            |                                    |         |         |         |         |  |

|                                                                              |                                                            |                 |                                    |         |         |         |         |  |

| bit 7-5                                                                      | Unimpleme                                                  | nted: Read as ' | ʻ0'                                |         |         |         |         |  |

| bit 4-0                                                                      | ADCAP<4:0>: ADC Additional Sample Capacitor Selection bits |                 |                                    |         |         |         |         |  |

| bit 4-0 | ADCAP<4:0>: ADC Additional Sample Capacitor Selection bits |  |  |  |  |

|---------|------------------------------------------------------------|--|--|--|--|

|         | 11111 <b>= 31 pF</b>                                       |  |  |  |  |

|         | 11110 = <b>30</b> pF                                       |  |  |  |  |

|         | 11101 <b>= 29 pF</b>                                       |  |  |  |  |

|         | •                                                          |  |  |  |  |

|         | •                                                          |  |  |  |  |

|         | •                                                          |  |  |  |  |

|         | 00011 <b>= 3 pF</b>                                        |  |  |  |  |

|         | $00010 = 2 \mathrm{pF}$                                    |  |  |  |  |

|         | 00001 = 1 pF                                               |  |  |  |  |

|         | 00000 = No additional capacitance                          |  |  |  |  |

#### REGISTER 31-12: ADRPT: ADC REPEAT SETTING REGISTER

| R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADRPT<7:0> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         |         | bit 0   |

|            |         |         |         |         |         |         |         |

| Legend:    |         |         |         |         |         |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 Unimplemented: Read as '0'

bit 7-0 **ADRPT<7:0>**: ADC Repeat Threshold bits Counts the number of times that the ADC has been triggered and is used along with ADCNT to determine when the error threshold is checked when the computation is Low-pass Filter, Burst Average, or Average modes. See Table 31-3 for more details.

### 32.9 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 37-15 and Table 37-17 for more details.

### 32.10 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 32-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

| Mnemonic,<br>Operands   |         | Description                    | Qualas     | 16-Bit Instruction Word |      |      |      | Status    | Natas |

|-------------------------|---------|--------------------------------|------------|-------------------------|------|------|------|-----------|-------|

|                         |         | Description                    | Cycles     | MSb                     |      |      | LSb  | Affected  | Notes |

| BIT-ORIENTED OPERATIONS |         |                                |            |                         |      |      |      |           |       |

| BCF                     | f, b, a | Bit Clear f                    | 1          | 1001                    | bbba | ffff | ffff | None      | 1, 2  |

| BSF                     | f, b, a | Bit Set f                      | 1          | 1000                    | bbba | ffff | ffff | None      | 1, 2  |

| BTFSC                   | f, b, a | Bit Test f, Skip if Clear      | 1 (2 or 3) | 1011                    | bbba | ffff | ffff | None      | 3, 4  |

| BTFSS                   | f, b, a | Bit Test f, Skip if Set        | 1 (2 or 3) | 1010                    | bbba | ffff | ffff | None      | 3, 4  |

| BTG                     | f, b, a | Bit Toggle f                   | 1          | 0111                    | bbba | ffff | ffff | None      | 1, 2  |

| CONTROL                 | OPERA   | TIONS                          |            |                         |      |      |      |           | •     |

| BC                      | n       | Branch if Carry                | 1 (2)      | 1110                    | 0010 | nnnn | nnnn | None      |       |

| BN                      | n       | Branch if Negative             | 1 (2)      | 1110                    | 0110 | nnnn | nnnn | None      |       |

| BNC                     | n       | Branch if Not Carry            | 1 (2)      | 1110                    | 0011 | nnnn | nnnn | None      |       |

| BNN                     | n       | Branch if Not Negative         | 1 (2)      | 1110                    | 0111 | nnnn | nnnn | None      |       |

| BNOV                    | n       | Branch if Not Overflow         | 1 (2)      | 1110                    | 0101 | nnnn | nnnn | None      |       |

| BNZ                     | n       | Branch if Not Zero             | 1 (2)      | 1110                    | 0001 | nnnn | nnnn | None      |       |

| BOV                     | n       | Branch if Overflow             | 1 (2)      | 1110                    | 0100 | nnnn | nnnn | None      |       |

| BRA                     | n       | Branch Unconditionally         | 2          | 1101                    | 0nnn | nnnn | nnnn | None      |       |

| ΒZ                      | n       | Branch if Zero                 | 1 (2)      | 1110                    | 0000 | nnnn | nnnn | None      |       |

| CALL                    | k, s    | Call subroutine 1st word       | 2          | 1110                    | 110s | kkkk | kkkk | None      |       |

|                         |         | 2nd word                       |            | 1111                    | kkkk | kkkk | kkkk |           |       |

| CLRWDT                  | _       | Clear Watchdog Timer           | 1          | 0000                    | 0000 | 0000 | 0100 | TO, PD    |       |

| DAW                     | —       | Decimal Adjust WREG            | 1          | 0000                    | 0000 | 0000 | 0111 | С         |       |

| GOTO                    | k       | Go to address 1st word         | 2          | 1110                    | 1111 | kkkk | kkkk | None      |       |

|                         |         | 2nd word                       |            | 1111                    | kkkk | kkkk | kkkk |           |       |

| NOP                     | _       | No Operation                   | 1          | 0000                    | 0000 | 0000 | 0000 | None      |       |

| NOP                     | _       | No Operation                   | 1          | 1111                    | xxxx | xxxx | xxxx | None      | 4     |

| POP                     | _       | Pop top of return stack (TOS)  | 1          | 0000                    | 0000 | 0000 | 0110 | None      |       |

| PUSH                    | _       | Push top of return stack (TOS) | 1          | 0000                    | 0000 | 0000 | 0101 | None      |       |

| RCALL                   | n       | Relative Call                  | 2          | 1101                    | 1nnn | nnnn | nnnn | None      |       |

| RESET                   |         | Software device Reset          | 1          | 0000                    | 0000 | 1111 | 1111 | All       |       |

| RETFIE                  | S       | Return from interrupt enable   | 2          | 0000                    | 0000 | 0001 | 000s | GIE/GIEH, |       |

|                         |         |                                |            |                         |      |      |      | PEIE/GIEL |       |

| RETLW                   | k       | Return with literal in WREG    | 2          | 0000                    | 1100 | kkkk | kkkk | None      |       |

| RETURN                  | S       | Return from Subroutine         | 2          | 0000                    | 0000 | 0001 | 001s | None      |       |

| SLEEP                   |         | Go into Standby mode           | 1          | 0000                    | 0000 | 0000 | 0011 | TO, PD    |       |

#### TABLE 35-2: INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| CPF      | SGT              | Compare                                                                                                                                                                                                                                                                     | Compare f with W, skip if f > W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |  |  |  |  |

|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

| Synta    | ax:              | CPFSGT                                                                                                                                                                                                                                                                      | f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |  |  |  |  |

| ,        | ands:            | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |  |  |  |  |

| Oper     | ation:           |                                                                                                                                                                                                                                                                             | (f) - (W),<br>skip if $(f) > (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |  |  |  |  |

| Statu    | s Affected:      | None                                                                                                                                                                                                                                                                        | comparison)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |  |  |  |  |

| Enco     | ding:            | 0110                                                                                                                                                                                                                                                                        | 010a fff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | f ffff    |  |  |  |  |

|          | ription:         | location 'f to<br>performing<br>If the conten-<br>contents of<br>instruction i<br>executed in<br>2-cycle instruction i<br>f 'a' is '0', th<br>If 'a' is '0', th<br>GPR bank.<br>If 'a' is '0' an<br>set is enabl<br>in Indexed I<br>mode when<br>tion 35.2.3<br>Oriented In | Compares the contents of data memory<br>ocation 'f' to the contents of the W by<br>performing an unsigned subtraction.<br>f the contents of 'f' are greater than the<br>contents of WREG, then the fetched<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction.<br>f 'a' is '0', the Access Bank is selected.<br>f 'a' is '1', the BSR is used to select the<br>GPR bank.<br>f 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq$ 95 (5Fh). See Sec-<br>ion 35.2.3 "Byte-Oriented and Bit-<br>Driented Instructions in Indexed Lite- |           |  |  |  |  |

| Word     | ls.              | eral Offset                                                                                                                                                                                                                                                                 | Mode" for det                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ails.     |  |  |  |  |

| Cycle    | es:              | •                                                                                                                                                                                                                                                                           | cles if skip and<br>2-word instruc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |  |  |  |  |

| QC       | ycle Activity:   |                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |  |  |  |  |

|          | Q1               | Q2                                                                                                                                                                                                                                                                          | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q4        |  |  |  |  |

|          | Decode           | Read                                                                                                                                                                                                                                                                        | Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | No        |  |  |  |  |

|          |                  | register 'f'                                                                                                                                                                                                                                                                | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | operation |  |  |  |  |

| lf sk    | ip:              |                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |  |  |  |  |

|          | Q1               | Q2                                                                                                                                                                                                                                                                          | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q4        |  |  |  |  |

|          | No               | No                                                                                                                                                                                                                                                                          | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No        |  |  |  |  |

| 16       | operation        | operation                                                                                                                                                                                                                                                                   | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | operation |  |  |  |  |

| IT SK    |                  | d by 2-word in:                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01        |  |  |  |  |

| l        | Q1<br>No         | Q2<br>No                                                                                                                                                                                                                                                                    | Q3<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q4<br>No  |  |  |  |  |

|          | operation        | operation                                                                                                                                                                                                                                                                   | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | operation |  |  |  |  |

|          | No               | No                                                                                                                                                                                                                                                                          | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No        |  |  |  |  |