Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 80MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, WDT                                                            |

| Number of I/O              | -                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 32K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 16x12b                                                               |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TJ)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-TQFP Exposed Pad                                                      |

| Supplier Device Package    | 64-eTQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc570s40e1cefay |

# List of tables

| Table 1.  | SPC570Sx device feature summary (Family Superset Configuration)           | . 6 |

|-----------|---------------------------------------------------------------------------|-----|

| Table 2.  | SPC570S40Ex, SPC570S50Ex device configuration differences                 |     |

| Table 3.  | SPC570Sx series block summary                                             | 11  |

| Table 4.  | eTQFP64 and eTQFP100 pinout                                               | 16  |

| Table 5.  | Parameter classifications                                                 | 22  |

| Table 6.  | Absolute maximum ratings                                                  |     |

| Table 7.  | Radiated emissions testing specification,                                 | 24  |

| Table 8.  | ESD ratings,                                                              | 24  |

| Table 9.  | Device operating conditions                                               | 25  |

| Table 10. | Thermal characteristics for eTQFP64                                       | 26  |

| Table 11. | Current consumption                                                       | 29  |

| Table 12. | I/O pad specification descriptions                                        | 29  |

| Table 13. | I/O input DC electrical characteristics                                   | 30  |

| Table 14. | I/O pull-up/pull-down DC electrical characteristics                       | 32  |

| Table 15. | Weak configuration I/O output characteristics,                            | 33  |

| Table 16. | Medium configuration I/O output characteristics,                          | 33  |

| Table 17. | Strong configuration I/O output characteristics                           | 34  |

| Table 18. | Very Strong configuration I/O output characteristics                      | 35  |

| Table 19. | I/O output characteristics for pads 4, 9, 11, 55, 56                      | 36  |

| Table 20. | Reset electrical characteristics                                          |     |

| Table 21. | Voltage regulator electrical characteristics                              |     |

| Table 22. | Trimmed (PVT) values                                                      |     |

| Table 23. | RWSC settings                                                             | 42  |

| Table 24. | Flash memory program and erase specifications                             |     |

| Table 25. | Flash memory Life Specification                                           |     |

| Table 26. | PLL1 electrical characteristics                                           |     |

| Table 27. | PLL0 electrical characteristics                                           |     |

| Table 28. | External Oscillator electrical specifications                             |     |

| Table 29. | Selectable load capacitance                                               |     |

| Table 30. | Internal RC oscillator electrical specifications                          |     |

| Table 31. | ADC input leakage current                                                 |     |

| Table 32. | ADC conversion characteristics                                            |     |

| Table 33. | Temperature sensor electrical characteristics                             |     |

| Table 34. | JTAG pin AC electrical characteristics                                    |     |

| Table 35. | DSPI CMOS master classic timing (full duplex and output only) – MTFE = 0  |     |

| Table 36. | DSPI CMOS master modified timing (full duplex and output only) – MTFE = 1 |     |

| Table 37. | eTQFP64 package mechanical data                                           |     |

| Table 38. | eTQFP100 mechanical data                                                  |     |

| Table 39. | Document revision history                                                 | 66  |

#### 1 Introduction

#### 1.1 Document overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device. To ensure a complete understanding of the device functionality, refer also to the device reference manual and errata sheet.

### 1.2 Description

The SPC570Sx is a family of next generation microcontrollers built on the Power Architecture embedded category.

The SPC570Sx family of 32-bit microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding family of automotive-focused products designed to address the next wave of Chassis and Safety electronics applications within the vehicle. The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category and only implements the VLE (variable-length encoding) APU, providing improved code density. It operates at speeds of up to 80 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

Table 1. SPC570Sx device feature summary (Family Superset Configuration)

| F                                | eature                        | Description                     |  |  |

|----------------------------------|-------------------------------|---------------------------------|--|--|

| Process                          |                               | 55 nm                           |  |  |

|                                  | Core                          | e200z0h                         |  |  |

|                                  | Number of main cores          | 1                               |  |  |

| Main processor                   | Number of checker cores       | 1                               |  |  |

|                                  | VLE                           | Yes                             |  |  |

|                                  | Main processor frequency      | 80 MHz <sup>(1)</sup>           |  |  |

| Interrupt controllers (including | interrupt controller checker) | 1                               |  |  |

| Software watchdog timer          |                               | 1                               |  |  |

| System timers                    |                               | 1 AUTOSAR <sup>®</sup> STM      |  |  |

| Cystem uniors                    |                               | 1 PIT with four 32-bit channels |  |  |

| DMA (including DMA checker)      |                               | 1                               |  |  |

| DMA channels                     |                               | 16                              |  |  |

| SMPU                             |                               | Yes (8 regions) <sup>(2)</sup>  |  |  |

| System SRAM                      | System SRAM                   |                                 |  |  |

| Code flash memory                | 512 KB                        |                                 |  |  |

| Data flash memory (suitable fo   | or EEPROM emulation)          | 32 KB                           |  |  |

# 2 Block diagram

Figure 1 shows the top-level block diagram.

Figure 1. Block diagram Nexus3 JTAGM JTAGC DCI SPU RCCU Nexus 2+ Nexus 2+ DMACHMUX DMACHMUX RCCU (lockstep) INTC Power PC Power PC RCCU INTC e200z0h e200z0h (lockstep) (lockstep) DMA DMA RCCU (lockstep) **RCCU** e2eEDC e2eEDC e2eEDC XBAR XBIC RAM Flash controller controller AIPS1 AIPS0 AIC1 AIC0 RAM Flash INTC\_0 XBIC PFLASHC DSPI\_2 CMU\_1 XBAR SMPU SRAM eTimer\_2 CMU\_2 STM SWT DMA\_0 eTimer\_0 eTimer\_1 CTU LINFlex\_1 FCCU FlexCAN\_1 lexCAN\_0 SARADC\_0 SARADC\_B STCU JTAGM PMCDIG ADCSAR\_ SEQ\_0 ADCSAR\_ SEQ\_B LINFlex 0 MEMU MC\_CGM CRC DMA CHMUX\_0 DSPI\_0 DSPI\_1 MC\_PCU SSCM PIT MC\_RGM MC\_ME SIUL CFLASH\_INF RCOSC\_DIG XOSC\_DIG PLL\_DIG\_0 CMU\_PLL JDC

*Table 3* summarizes the functions of all blocks present in the SPC570Sx series of microcontrollers. Please note that the presence and number of blocks vary by device and package.

Table 3. SPC570Sx series block summary

| Block                                            | Function                                                                                                           |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| e200z0 CPU                                       | Allows single clock instruction execution                                                                          |

| Analog-to-digital converter (ADC)                | Multi-channel, 12-bit analog-to-digital converter                                                                  |

| Cross triggering unit (CTU)                      | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                       |

| Deserial serial peripheral interface (DSPI)      | Provides a synchronous serial interface for communication with external devices                                    |

| Enhanced Direct Memory Access (eDMA)             | Performs complex data transfers with minimal intervention from a host processor via 16 programmable channels.      |

| DMACHMUX                                         | Allows to route a defined number of DMA peripheral sources to the DMA channels                                     |

| Flash memory                                     | Provides non-volatile storage for program code, constants and variables                                            |

| FlexCAN (controller area network)                | Supports the standard CAN communications protocol                                                                  |

| PLL0                                             | Output independent of core clock frequency                                                                         |

| Frequency-modulated phase-<br>locked loop (PLL1) | Generates high-speed system clocks and supports programmable frequency modulation                                  |

| Interrupt controller (INTC)                      | Provides priority-based preemptive scheduling of interrupt requests                                                |

| AIPS                                             | System bus to peripheral bus interface                                                                             |

| RAM controller                                   | Acts as an interface between the system bus and the integrated system RAM                                          |

| System RAM                                       | Supports read/write accesses mapped to the SRAM memory from any master                                             |

| Flash memory controller                          | Acts as an interface between the system bus and the Flash memory module                                            |

| Flash memory                                     | Up to 512 KB of programmable, non-volatile Flash memory for code and 32 KB for data                                |

| IRCOSC                                           | Controls the internal 16 MHz RC oscillator system                                                                  |

| XOSC                                             | Controls the on-chip oscillator (XOSC) and provides the register interface for the programmable features           |

| JTAG Master                                      | Provides software the option to write data for driving JTAG                                                        |

| JTAG Data Communication<br>Module                | Provides the capability to move register data between the IPS and JTAG domains                                     |

| PASS                                             | Programs a set of Flash memory access protections, based on user programmable passwords                            |

| Sequence Processing Unit                         | Provides an on-device trigger functions similar to those found on a logic analyzer                                 |

| LINFlex controller                               | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load |

Table 3. SPC570Sx series block summary (continued)

| Block                                     | Function                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock generation module (MC_CGM)          | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                   |

| Mode entry module (MC_ME)                 | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications |

| MC_PMC                                    | Contains registers that enable/disable the various voltage monitors                                                                                                                                                                                                                                      |

| Reset generation module (MC_RGM)          | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                            |

| Memory protection unit (MPU)              | Provides hardware access control for all memory references generated in a device                                                                                                                                                                                                                         |

| eTimer                                    | Has six 16-bit general purpose counter, where each counter can be used as input capture or output compare function                                                                                                                                                                                       |

| FCCU                                      | Collects fault event notification from the rest of the system and translates them into internal and/or external system reactions                                                                                                                                                                         |

| RCCU                                      | Compares input signals and issues an alarm in the case of a mismatch                                                                                                                                                                                                                                     |

| MEMU                                      | Collects and reports error events associated with ECC (Error Correction Code) logic used on SRAM, DMA RAM and Flash memory                                                                                                                                                                               |

| XBIC                                      | Verifies the integrity of the attribute information for crossbar transfers and signals the Fault Collection and Control Unit (FCCU) when an error is detected                                                                                                                                            |

| STCU2                                     | Handles the BIST procedure                                                                                                                                                                                                                                                                               |

| CRC                                       | Controls the computation of CRC, off-loading this work from the CPU                                                                                                                                                                                                                                      |

| RegProt                                   | Protects several registers against accidental writing, locking their value till the next reset phase                                                                                                                                                                                                     |

| Temperature sensor                        | Monitors the device temperature                                                                                                                                                                                                                                                                          |

| Debug Control Interface                   | Provides debug features for the MCU                                                                                                                                                                                                                                                                      |

| Nexus Port Controller                     | Monitor a variety of signals including addresses, data, control signals, status signals, etc.                                                                                                                                                                                                            |

| Nexus Multimaster Trace Client            | Monitors the system bus and provides real-time trace information to debug or development tools                                                                                                                                                                                                           |

| Periodic interrupt timer (PIT)            | Produces periodic interrupts and triggers                                                                                                                                                                                                                                                                |

| System integration unit (SIUL)            | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration                                                                                 |

| System status configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable                                                                         |

| System timer module (STM)                 | Provides a set of output compare events to support AUTOSAR and operating system tasks                                                                                                                                                                                                                    |

| System watchdog timer (SWT)               | Provides protection from runaway code                                                                                                                                                                                                                                                                    |

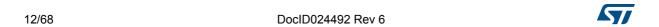

Figure 3. eTQFP 100-pin configuration

Table 4. eTQFP64 and eTQFP100 pinout (continued)

|             |           | Pin     | No.      |       | Alternate functions                       |                         |                    |                         |  |  |

|-------------|-----------|---------|----------|-------|-------------------------------------------|-------------------------|--------------------|-------------------------|--|--|

| Port<br>pin | Pad       | eTQFP64 | eTQFP100 | Туре  | AF1                                       | AF2                     | AF3                | AF4                     |  |  |

| PD[9]       | PAD[57]   | 49      | 76       | Ю     | FlexCAN 0 -<br>RX                         | DSPI 2 -<br>CS 1        | FlexCAN 1 -<br>RX  | Timer 2 -<br>ch. 2      |  |  |

| PD[10]      | PAD[58]   | 50      | 77       | Ю     | FlexCAN 0 -<br>TX                         | _                       | FlexCAN 1 -<br>TX  | Timer 2 -<br>ch. 3      |  |  |

| PD[11]      | PAD[59]   | 51      | 78       | Ю     | Timer 3 -<br>ch. 2                        | DSPI 2 -<br>CLK         | DSPI 1 -<br>CS 7   | _                       |  |  |

| PD[12]      | PAD[60]   | _       | 79       | Ю     | DSPI 2 -<br>Serial Data                   | Timer 2 -<br>ch. 3      | DSPI 2 -<br>CS 2   | _                       |  |  |

| PD[13]      | PAD[61]   | _       | 80       | Ю     | DSPI 2 -<br>CLK                           | Timer 2 -<br>ch. 4      | DSPI 2 -<br>CS 3   | _                       |  |  |

| PD[14]      | PAD[62]   | 52      | 81       | Ю     | Timer 2 -<br>ch. 3                        | DSPI 2 -<br>Serial Data | Timer 3 -<br>ch. 3 | _                       |  |  |

| PD[15]      | PAD[63]   | 53      | 82       | Ю     | Timer 2 -<br>ch. 4                        | DSPI 2 -<br>Serial Data | Timer 3 -<br>ch. 4 | _                       |  |  |

| PE[0]       | PAD[64]   | _       | 83       | Ю     | Timer 3 -<br>ch. 3                        | Ext. INT 2              | _                  | Timer 2 -<br>ch. 4      |  |  |

| PE[1]       | PAD[65]   | _       | 84       | Ю     | Timer 3 -<br>ch. 4                        | _                       | _                  | Timer 2 -<br>ch. 5      |  |  |

| _           | VDD_HV_IO | 54      | 85       | PWB85 |                                           | _                       | _                  |                         |  |  |

| PE[2]       | PAD[66]   | 55      | 86       | Ю     | Timer 2 -<br>ch. 5                        | DSPI 2 -<br>CS 0        | DSPI 0 -<br>CS 3   | _                       |  |  |

| PE[3]       | PAD[67]   | 56      | 87       | Ю     | Nexus<br>MSEO <sup>(2)</sup>              | _                       | DSPI 0 -<br>CS 4   | DSPI 2 -<br>CLK         |  |  |

| PE[4]       | PAD[68]   | _       | 88       | Ю     | Timer 3 -<br>ch. 5                        | DSPI 2 -<br>CS 2        | Timer 2 -<br>ch. 4 | _                       |  |  |

| PE[5]       | PAD[69]   | 57      | 89       | Ю     | Nexus<br>MDO 3 <sup>(2)</sup>             | _                       | CLOCKOUT           | DSPI 2 -<br>Serial Data |  |  |

| PE[6]       | PAD[70]   | 58      | 90       | Ю     | Nexus<br>MDO 2 <sup>(2)</sup>             | _                       | DSPI 0 -<br>CS 6   | DSPI 2 -<br>Serial Data |  |  |

| PE[7]       | PAD[71]   | 59      | 91       | Ю     | Nexus<br>MDO 1 <sup>(2)</sup>             | _                       | DSPI 0 -<br>CS 7   | Timer 3 -<br>ch. 4      |  |  |

| PE[8]       | PAD[72]   | 60      | 92       | Ю     | Nexus DSPI 0<br>MDO 0 <sup>(2)</sup> CS 0 |                         | Ext. INT 3         | Timer 3 -<br>ch. 5      |  |  |

| PE[9]       | PAD[73]   | _       | 93       | Ю     | _                                         | Timer 3 -<br>ch. 2      | Ext. INT 4         | DSPI 2 -<br>CS 1        |  |  |

| PE[10]      | PAD[74]   | _       | 94       | Ю     | _                                         | Timer 3 -<br>ch. 3      | DSPI 0 -<br>CS 5   | DSPI 2 -<br>CS 2        |  |  |

| _           | VDD_HV_IO | 61      | 95       | PW    |                                           | _                       | _                  |                         |  |  |

# 4.6 Operating conditions

Table 9. Device operating conditions<sup>(1)</sup>

|                                                         |    |   |                                                             | operating condition                          |       |     | Value                        |      |

|---------------------------------------------------------|----|---|-------------------------------------------------------------|----------------------------------------------|-------|-----|------------------------------|------|

| Symbol                                                  |    | С | Parameter                                                   | Conditions                                   | Min   | Тур | Max                          | Unit |

|                                                         |    |   |                                                             | Frequency                                    | I     | ı   |                              |      |

| f <sub>SYS</sub>                                        | SR |   | Device operating frequency <sup>(2)</sup>                   | -40 °C < T <sub>J</sub> < 150 °C             | _     | _   | 80                           | MHz  |

|                                                         |    |   | 7                                                           | emperature                                   |       |     |                              |      |

| TJ                                                      | SR | Р | Operating<br>temperature<br>range - junction                | _                                            | -40.0 | _   | 150.0                        | °C   |

| T <sub>A</sub> (T <sub>L</sub> to T <sub>H</sub> )      | SR | Р | Ambient operating temperature range                         | _                                            | -40.0 | _   | 125.0                        | °C   |

|                                                         |    |   |                                                             | Voltage                                      |       |     |                              |      |

|                                                         |    | Р |                                                             | LVD290/HVD400<br>enabled                     | 2.97  |     | 3.63                         |      |

| $V_{DD\_HV\_IO}$                                        | SR | С | I/O supply voltage                                          | LVD290 enabled<br>HVD400 disabled<br>(3),(4) | 2.97  | _   | 5.5                          | V    |

| V                                                       |    |   | PMC and OSC                                                 | LVD290/HVD400<br>enabled                     | 2.97  | _   | 3.63                         | V    |

| V <sub>DD_HV_OSC_PMC</sub>                              | SR | С | supply voltage                                              | LVD290 enabled<br>HVD400 disabled            | 2.97  | _   | 5.5                          | V    |

|                                                         |    | D | CAD ADC supply                                              | LVD400 enabled                               | 4.5   | _   | 5.5                          |      |

| V <sub>DD_HV_ADC_TSENS</sub>                            | SR | С | SAR ADC supply voltage                                      | LVD400<br>disabled <sup>(3),(5)</sup>        | 3.0   | _   | 3.6                          | V    |

| V <sub>REFH_ADC</sub>                                   | SR | Р | SAR ADC reference voltage                                   | _                                            | 2.0   | _   | V <sub>DD_HV_ADC_TSENS</sub> | ٧    |

| V <sub>REFH_ADC</sub> -<br>V <sub>DD_HV_ADC_TSENS</sub> | SR | D | SAR ADC<br>reference<br>differential voltage                | _                                            | _     | _   | 25                           | mV   |

| $V_{RAMP}$                                              | SR | D | Slew rate on power supply pins                              | _                                            | _     | _   | 0.5                          | V/µs |

| V <sub>IN</sub>                                         | SR | С | I/O input voltage range                                     | _                                            | 0     | _   | 5.5                          | ٧    |

|                                                         |    | • | Inj                                                         | ection current                               |       |     |                              |      |

| I <sub>IC</sub>                                         | SR | Т | DC injection<br>current (per<br>pin) <sup>(6),(7),(8)</sup> | Digital pins and analog pins                 | -3    | _   | 3                            | mA   |

| I <sub>MAXSEG</sub>                                     | SR | D | Maximum current<br>per power<br>segment <sup>(9)</sup>      | _                                            | -80   | _   | 80                           | mA   |

where:

$T_A$  = ambient temperature for the package (°C)

$R_{\theta,JA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal resistance values used are based on the JEDEC JESD51 series of standards to provide consistent values for estimations and comparisons. The difference between the values determined for the single-layer (1s) board compared to a four-layer board that has two signal layers, a power and a ground plane (2s2p), demonstrate that the effective thermal resistance is not a constant. The thermal resistance depends on the:

- Construction of the application board (number of planes)

- Effective size of the board which cools the component

- Quality of the thermal and electrical connections to the planes

- Power dissipated by adjacent components

Connect all the ground and power balls to the respective planes with one via per ball. Using fewer vias to connect the package to the planes reduces the thermal performance. Thinner planes also reduce the thermal performance. When the clearance between the vias leave the planes virtually disconnected, the thermal performance is also greatly reduced.

As a general rule, the value obtained on a single-layer board is within the normal range for the tightly packed printed circuit board. The value obtained on a board with the internal planes is usually within the normal range if the application board has:

- One oz. (35 micron nominal thickness) internal planes

- Components are well separated

- Overall power dissipation on the board is less than 0.02 W/cm2

The thermal performance of any component depends on the power dissipation of the surrounding components. In addition, the ambient temperature varies widely within the application. For many natural convection and especially closed box applications, the board temperature at the perimeter (edge) of the package is approximately the same as the local air temperature near the device. Specifying the local ambient conditions explicitly as the board temperature provides a more precise description of the local ambient conditions that determine the temperature of the device.

At a known board temperature, the junction temperature is estimated using the following equation:

Equation 2:

$$T_J = T_B + (R_{\alpha JB} * P_D)$$

where:

T<sub>B</sub> = board temperature for the package perimeter (°C)

R<sub>o.IB</sub> = junction-to-board thermal resistance (°C/W) per JESD51-8

$P_D$  = power dissipation in the package (W)

When the heat loss from the package case to the air does not factor into the calculation, the junction temperature is predictable if the application board is similar to the thermal test condition, with the component soldered to a board with internal planes.

The thermal resistance is expressed as the sum of a junction-to-case thermal resistance plus a case-to-ambient thermal resistance:

Table 13. I/O input DC electrical characteristics (continued)

|                                    |    |   |                                                 |                                                                                                                                   | v                               | alue       |                                 |      |

|------------------------------------|----|---|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------|---------------------------------|------|

| Symbol                             |    | С | Parameter                                       | Conditions                                                                                                                        | Min                             | in Typ Max |                                 | Unit |

| V <sub>ILCMOS</sub> <sup>(2)</sup> | SR | Р | Input low level<br>CMOS<br>(without hysteresis) | $3.0 \text{ V} < \text{V}_{\text{DD\_HV\_IO}} < 3.6 \text{ V}$ and $4.5 \text{ V} < \text{V}_{\text{DD\_HV\_IO}} < 5.5 \text{ V}$ | -0.3                            | _          | 0.4 *<br>V <sub>DD_HV_IO</sub>  | V    |

| V <sub>HYSCMOS</sub>               | _  | С | Input hysteresis<br>CMOS                        | $3.0 \text{ V} < \text{V}_{\text{DD\_HV\_IO}} < 3.6 \text{ V}$ and $4.5 \text{ V} < \text{V}_{\text{DD\_HV\_IO}} < 5.5 \text{ V}$ | 0.1 *<br>V <sub>DD_HV_IO</sub>  | _          | _                               | V    |

|                                    |    |   |                                                 | Automotive                                                                                                                        |                                 |            |                                 |      |

| V <sub>IH</sub> (3)                | SR | D | Input high level                                | 4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V                                                                                             | 3.8                             | _          | V <sub>DD_HV_IO</sub> + 0.3     | V    |

| VIH.                               | SK | Г | Automotive                                      | 3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V                                                                                             | 0.75 *<br>V <sub>DD_HV_IO</sub> | _          | V <sub>DD_HV_IO</sub><br>+ 0.3  | V    |

|                                    |    |   | Input low lovel                                 | 4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V                                                                                             | -0.3                            | _          | 2.2                             |      |

| V <sub>IL</sub>                    | SR | Р | Input low level Automotive                      | 3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V                                                                                             | -0.3                            | _          | 0.35 *<br>V <sub>DD_HV_IO</sub> | V    |

|                                    |    |   | Input hystorogic                                | 4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V                                                                                             | 0.5                             | _          | _                               |      |

| V <sub>HYST</sub>                  | _  | С | Input hysteresis<br>Automotive                  | 3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V                                                                                             | 0.11 *<br>V <sub>DD_HV_IO</sub> | _          | _                               | V    |

|                                    |    |   |                                                 | Input Characteristics                                                                                                             |                                 |            |                                 |      |

| I <sub>LKG</sub>                   | СС | Р | Digital input leakage                           | _                                                                                                                                 | _                               | _          | 1                               | μA   |

| C <sub>IN</sub>                    | С  | D | Digital input capacitance                       | _                                                                                                                                 | _                               | _          | 10                              | pF   |

<sup>1.</sup> Minimum hysteresis at 4.0 V

Table 14 provides weak pull figures. Both pull-up and pull-down current specifications are provided.

<sup>2.</sup>  $VSIO[VSIO\_xx] = 0 \text{ in the range } 3.0 \text{ V} < V_{DD\_HV\_IO} < 4.0 \text{ V}, \\ VSIO[VSIO\_xx] = 1 \text{ in the range } 4.0 \text{ V} < V_{DD\_HV\_IO} < 5.9 \text{ V}.$

<sup>3.</sup>  $VSIO[VSIO_xx] = 0$  in the range 3.0  $V < V_{DD_HV_IO} < 4.0 V$ ,  $VSIO[VSIO_xx] = 1$  in the range 4.0  $V < V_{DD_HV_IO} < 5.9 V$ .

Value **Symbol** C **Parameter Conditions** Unit Min Тур Max  $\overline{V_{IN}}$  = 0.69 \*  $V_{DD\_HV\_IO}$ 23  $4.5 \text{ V} < \text{V}_{DD HV IO} < 5.5 \text{ V}$  $V_{IN} = 0.49 * V_{DD HV IO}$ CC Ρ 82  $4.5 \text{ V} < \text{V}_{DD HV IO} < 5.5 \text{ V}$  $V_{IN} > V_{IL} = 1.1 \text{ V (TTL)}$ 130 4.5 V < V<sub>DD\_HV\_IO</sub> < 5.5 V Weak pull-up/down  $|I_{WPU}|$ μΑ current absolute value<sup>(1)</sup> V<sub>IN</sub> = 0.75 \* V<sub>DD\_HV\_IO</sub> 10  $3.0 \text{ V} < \text{V}_{DD \text{ HV IO}} < 3.6 \text{ V}$  $V_{IN} = 0.35 * V_{DD HV IO}$ CC Т 70  $3.0 \text{ V} < \text{V}_{DD\_HV\_IO} < 3.6 \text{ V}$ V<sub>IN</sub> > V<sub>IL</sub> = 1.1 V (TTL) 75  $3.0 \text{ V} < \text{V}_{DD\_HV\_IO} < 3.6 \text{ V}$ V<sub>IN</sub> = 0.69 \* V<sub>DD HV IO</sub> 130  $4.5 \text{ V} < \text{V}_{DD HV IO} < 5.5 \text{ V}$ V<sub>IN</sub> = 0.49 \* V<sub>DD HV IO</sub> CC Ρ 40  $4.5 \text{ V} < \text{V}_{DD HV IO} < 5.5 \text{ V}$  $V_{IN} > V_{IL} = 1.1 \text{ V (TTL)}$ 16  $4.5 \text{ V} < \text{V}_{DD\_HV\_IO} < 5.5 \text{ V}$ Weak pull-down current  $|I_{WPD}|$ μΑ absolute value  $V_{IN} = 0.75 * V_{DD\_HV\_IO}$ 92  $3.0 \text{ V} < \text{V}_{DD \text{ HV IO}} < 3.6 \text{ V}$  $V_{IN} = 0.35 * V_{DD HV IO}$ CC Т 19  $3.0 \text{ V} < \text{V}_{DD HV IO} < 3.6 \text{ V}$  $V_{IN} > V_{IL} = 1.1 \text{ V (TTL)}$ 16  $3.0 \text{ V} < \text{V}_{\text{DD HV IO}} < 3.6 \text{ V}$

Table 14. I/O pull-up/pull-down DC electrical characteristics

#### 4.9.3 I/O output DC characteristics

*Table 15: Weak configuration I/O output characteristics*, provide DC characteristics for bidirectional pads in the following configurations:

- Weak

- Medium

- Strong

- Very Strong

Weak pull-up/down is enabled within t<sub>WK\_PU</sub> = 1 µs after internal/external reset has been asserted. Output voltage will depend on the amount of capacitance connected to the pin.

Table 17. Strong configuration I/O output characteristics (continued)

| Symbol              |   | С | Parameter                  | Conditions                                                      |     | Value |     | Unit |

|---------------------|---|---|----------------------------|-----------------------------------------------------------------|-----|-------|-----|------|

| Syllibol            |   | C | Farameter                  | Conditions                                                      | Min | Тур   | Max | Oill |

|                     |   |   |                            | 3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V<br>C <sub>L</sub> = 25 pF | _   | _     | 11  |      |

|                     | С | D | Transition time output pin | 3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V<br>C <sub>L</sub> = 50 pF | _   | _     | 22  | 20   |

| t <sub>TR_S</sub>   | С | ט | strong configuration       | 4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V<br>C <sub>L</sub> = 25 pF | _   | _     | 8   | ns   |

|                     |   |   |                            | 4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V<br>C <sub>L</sub> = 50 pF | _   | _     | 13  |      |

| +.                  | С | т | Difference between rise    | 3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V                           | _   | _     | 40  | %    |

| t <sub>SKEW_S</sub> | С | ' | time and fall time         | 4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V                           | _   | _     | 28  | 70   |

Table 18. Very Strong configuration I/O output characteristics

| Symbo              |        | С | Dovemeter                 | Canditions                                                                                                                                                 |     | Value |     | Unit    |

|--------------------|--------|---|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|---------|

| Symbo              | Зушьог |   | Parameter                 | Conditions                                                                                                                                                 | Min | Тур   | Max | Unit    |

| D.                 | С      | Р | PMOS output impedance     | $3.0 \text{ V} < \text{V}_{\text{DD\_HV\_IO}} < 3.6 \text{ V}$<br>Push pull, $\text{I}_{\text{OH}} < 7 \text{ mA}$                                         | _   | _     | 85  | Ω       |

| R <sub>OH_V</sub>  | С      | F | very strong configuration | $\begin{array}{l} \textrm{4.5 V} < \textrm{V}_{\textrm{DD\_HV\_IO}} < 5.5 \textrm{ V} \\ \textrm{Push pull, I}_{\textrm{OH}} < 8 \textrm{ mA} \end{array}$ |     | _     | 65  | 22      |

| В                  | С      | Р | NMOS output impedance     | $3.0 \text{ V} < \text{V}_{\text{DD\_HV\_IO}} < 3.6 \text{ V}$<br>Push pull, $\text{I}_{\text{OL}} < 7 \text{ mA}$                                         | _   | _     | 85  | Ω       |

| R <sub>OL_V</sub>  | С      | F | very strong configuration |                                                                                                                                                            |     | _     | 65  | 22      |

|                    |        |   |                           | 3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V<br>C <sub>L</sub> = 15 pF                                                                                            |     | _     | 50  |         |

|                    |        |   |                           | 3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V<br>C <sub>L</sub> = 25 pF                                                                                            |     | _     | 30  |         |

|                    | С      | Т | Output frequency very     | 3.0 V < V <sub>DD_HV_IO</sub> < 3.6 V<br>T <sub>d</sub> = 0.6 ns, load = 10 pF                                                                             |     | _     | 25  | MHz     |

| f <sub>max_V</sub> | С      | ' | strong configuration      | 4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V<br>C <sub>L</sub> = 25 pF                                                                                            |     | _     | 50  | IVII IZ |

|                    |        |   |                           | 4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V<br>C <sub>L</sub> = 50 pF                                                                                            | _   | _     | 25  |         |

|                    |        |   |                           | 4.5 V < V <sub>DD_HV_IO</sub> < 5.5 V<br>T <sub>d</sub> = 1 ns, load = 10 pF                                                                               | _   | _     | 25  |         |

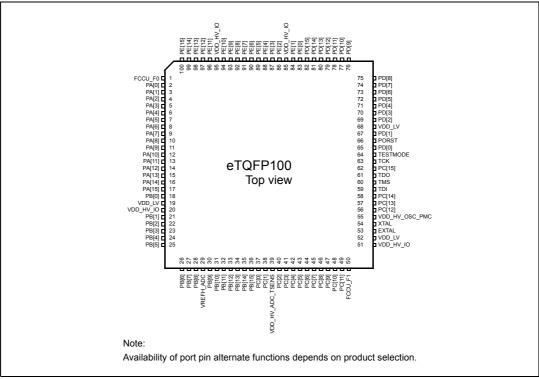

Figure 6 describes device behavior depending on supply signal on PORST:

- 1. PORST does not go low enough: it is filtered by input buffer hysteresis. The device remains in the current state.

- 2. PORST goes low enough, but not for long enough: it is filtered by a low pass filter. The device remains in the current state.

- 3. The PORST generates a reset:

- a) PORST low but initially filtered during at least W<sub>FRST</sub>. Device remains initially in current state.

- b) PORST potentially filtered until W<sub>NFRST</sub>. Device state is unknown. It may either be reset or remains in current state depending on extra conditions (PVT process, voltage, temperature).

- c) PORST asserted for longer than W<sub>NFRST</sub>. The device is under hardware reset.

Figure 6. Noise filtering on reset signal

4

|                      |                                                             | Value |       |              |                    |   |                               |                                |                  |   |      |

|----------------------|-------------------------------------------------------------|-------|-------|--------------|--------------------|---|-------------------------------|--------------------------------|------------------|---|------|

| Symbol               | Characteristics <sup>(1)</sup>                              | Tyn   | Typ C | Initial max  |                    |   | Typical                       | Lifetime<br>max <sup>(4)</sup> |                  |   | Unit |

|                      |                                                             | (2)   |       | 25 °C<br>(5) | All<br>temp<br>(6) | С | end of<br>life <sup>(3)</sup> | ≤1 K<br>cycles                 | ≤100 K<br>cycles | С |      |

| t <sub>AIC0P</sub>   | Array Integrity Check (0.5 MB, proprietary) <sup>(11)</sup> | 0.75  | Т     | _            | _                  | _ | _                             | _                              | _                | _ | s    |

| t <sub>MR0S</sub>    | Margin Read<br>(0.5 MB, sequential)                         | 25    | Т     | _            | _                  | _ | _                             | _                              | _                | _ | ms   |

| t <sub>MR128KS</sub> | Margin Read<br>(128 KB, sequential)                         | 6.26  | Т     | _            | _                  | _ | _                             | _                              | _                |   | ms   |

| t <sub>AABT</sub>    | Array Integrity Check Abort<br>Latency                      | _     |       | _            | _                  | _ | _                             |                                | 10               | _ | μs   |

| t <sub>MABT</sub>    | Margin Read Abort Latency                                   | _     | —     |              |                    |   | _                             |                                | 10               | — | μs   |

Table 24. Flash memory program and erase specifications (continued)

- 1. Actual hardware programming times; this does not include software overhead.

- Typical program and erase times assume nominal supply values and operation at 25 °C. All times are subject to change pending device characterization.

- Typical End of Life program and erase times represent the median performance and assume nominal supply values.

Typical End of Life program and erase values may be used for throughput calculations. These values are characteristic, but not tested.

- 4. Lifetime maximum program & erase times apply across the voltages and temperatures and occur after the specified number of program/erase cycles. These maximum values are characterized but not tested or guaranteed.

- Initial factory condition: < 100 program/erase cycles, 20 °C < T<sub>J</sub> < 30 °C junction temperature, and nominal (± 2%) supply voltages. These values are verified at production testing.

- Initial maximum "All temp" program and erase times provide guidance for time-out limits used in the factory and apply for less than or equal to 100 program or erase cycles, -40 °C < T<sub>J</sub> < 150 °C junction temperature, and nominal (± 2%) supply voltages. These values are verified at production testing.

- 7. Rate computed based on 128K sectors.

- 8. Only code sectors, not including EEPROM.

- Time between erase suspend resume and next erase suspend.

- 10. Timings guaranteed by design.

- 11. AIC is done using system clock, thus all timing is dependant on system frequency and number of wait states. Timing in the table is calculated at 80 MHz.

All the Flash operations require the presence of the system clock for internal synchronization. About 50 synchronization cycles are needed: this means that the timings of the previous table can be longer if a low frequency system clock is used.

Table 25. Flash memory Life Specification

| Symbol              | Characteristics <sup>(1)</sup> |     | Unit |     |   |         |

|---------------------|--------------------------------|-----|------|-----|---|---------|

|                     | ondiacteristics.               | Min | С    | Тур | C | Offic   |

| N <sub>CER16K</sub> | 16 KB CODE Flash endurance     | 10  | _    | 100 | _ | Kcycles |

| N <sub>CER32K</sub> | 32 KB CODE Flash endurance     | 10  | _    | 100 | _ | Kcycles |

| N <sub>CER64K</sub> | 64 KB CODE Flash endurance     | 10  | _    | 100 | _ | Kcycles |

**Value** Characteristics<sup>(1)</sup> **Symbol** Unit Min C Typ C 128 KB CODE Flash endurance 100 **Kcycles** N<sub>CER128K</sub> 1 16 KB EEPROM Flash endurance 100 **Kcycles** N<sub>DER16K</sub> Minimum data retention Blocks with 0 - 1,000 P/E 25 Years t<sub>DR1k</sub> Minimum data retention Blocks with 1,001 - 10,000 15 Years t<sub>DR10k</sub> P/E cycles Minimum data retention Blocks with 10,001 -15 Years t<sub>DR100k</sub> 100,000 P/E cycles

Table 25. Flash memory Life Specification (continued)

#### 4.15 PLL0/PLL1 electrical characteristics

The device provides a phase-locked loop (PLL0) as well as a frequency-modulated phase-locked loop (PLL1) module to generate a fast system clock from the main oscillator driver.

Value Conditions<sup>(1)</sup> **Symbol** С **Parameter** Unit Min Typ Max PLL1 reference clock<sup>(2)</sup> SR 37.5 78.125 MHz f<sub>PLLIN</sub> PLL1 reference clock duty SR 35 65 %  $\Delta_{\mathsf{PLLIN}}$ cycle(2) CC D PLL1 output clock frequency 4.762 625 MHz **f**PLLOUT  $f_{VCO}^{(3)}$ CC Ρ VCO frequency 600 1250 MHz CC Ρ PLL1 lock time Stable oscillator (f<sub>PLLIN</sub> = 16 MHz) 110 μs t<sub>LOCK</sub> f<sub>PLLIN</sub> = 16 MHz (resonator), CC Τ PLL1 short term jitter 1.8 ns  $\Delta t_{STJIT}$ f<sub>PLLCLK</sub> @ 64 MHz T<sub>A</sub> = 25 °C CC C PLL1 consumption 6 mA  $I_{PLL}$

Table 26. PLL1 electrical characteristics

<sup>1.</sup> Program and erase cycles supported across specified temperature specs.

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 to 125 °C, unless otherwise specified.

PLLIN clock retrieved directly from FXOSC clock. Input characteristics are granted when oscillator is used in functional

mode. When bypass mode is used, oscillator input clock should verify f<sub>PLLIN</sub> and Δ<sub>PLLIN</sub>.

<sup>3.</sup> Frequency modulation is considered ±2%.

| Symbol              |    | С | Parameter                                      | Conditions <sup>(1)</sup>                                                | Value |     |      | Unit  |

|---------------------|----|---|------------------------------------------------|--------------------------------------------------------------------------|-------|-----|------|-------|

|                     |    | C | Farameter                                      | Conditions                                                               | Min   | Тур | Max  | Uilli |

| f <sub>PLLIN</sub>  | SR | _ | PLL0 reference clock <sup>(2)</sup>            | _                                                                        | 8     |     | 56   | MHz   |

| $\Delta_{PLLIN}$    | SR | _ | PLL0 reference clock duty cycle <sup>(2)</sup> | _                                                                        | 30    | _   | 70   | %     |

| f <sub>PLLOUT</sub> | СС | D | PLL0 output clock frequency                    | _                                                                        | 4.762 | _   | 625  | MHz   |

| f <sub>VCO</sub>    | CC | Р | VCO frequency                                  | _                                                                        | 600   | _   | 1250 | MHz   |

| t <sub>LOCK</sub>   | СС | Ρ | PLL0 lock time                                 | Stable oscillator (f <sub>PLLIN</sub> = 16 MHz)                          |       | 1   | 110  | μs    |

| $\Delta t_{STJIT}$  | С  | Т | PLL0 short term jitter                         | f <sub>sys</sub> maximum                                                 |       | 1   | 300  | ps    |

| $\Delta t_{LTJIT}$  | СС | Т | PLL0 long term jitter                          | f <sub>PLLIN</sub> = 16 MHz (resonator),<br>f <sub>PLLCLK</sub> @ 64 MHz | -1    |     | 1    | ns    |

| I <sub>PLL</sub>    | СС | С | PLL0 consumption                               | T <sub>A</sub> = 25 °C                                                   |       | _   | 5.5  | mA    |

Table 27. PLL0 electrical characteristics

### 4.16 External oscillator (XOSC) electrical characteristics

Table 28. External Oscillator electrical specifications<sup>(1)</sup>

| Symbol               |    | С                                     | Davamatav                                                   | Conditions                                      |                            | Value                  |                        | Unit |

|----------------------|----|---------------------------------------|-------------------------------------------------------------|-------------------------------------------------|----------------------------|------------------------|------------------------|------|

|                      |    | C                                     | Parameter                                                   |                                                 |                            | Min                    | Max                    | Unit |

|                      |    | D                                     | Crystal Frequency Range <sup>(2)</sup>                      |                                                 | _                          | 4 8                    |                        |      |

| f <sub>XTAL</sub>    | СС |                                       |                                                             |                                                 | _                          | >8                     | 20                     | MHz  |

|                      |    |                                       |                                                             |                                                 | _                          | >20                    | 40                     |      |

| t <sub>cst</sub>     | СС | Т                                     | [Covers: ADD12.017]Crystal start-up time (3),(4)            | T <sub>J</sub> = 150 °C —                       |                            | 5                      | ms                     |      |

| trec                 | СС | _                                     | Crystal recovery time <sup>(5)</sup>                        | _                                               |                            | _                      | 0.5                    | ms   |

| V <sub>IHEXT</sub>   | СС | D                                     | EXTAL input high voltage (External Reference)               | V <sub>REF</sub> = 0.28 * V <sub>DD_HV_IO</sub> |                            | V <sub>REF</sub> + 0.6 | _                      | V    |

| V <sub>ILEXT</sub>   | СС | D                                     | EXTAL input low voltage <sup>(6),(7)</sup>                  | V <sub>REF</sub> = 0.28 * V <sub>DD_HV_IO</sub> |                            | _                      | V <sub>REF</sub> - 0.6 | V    |

| C <sub>S_EXTAL</sub> | СС | Т                                     | Total on-chip stray capacitance on EXTAL pin <sup>(8)</sup> | QFP                                             |                            | 6.0                    | 8.0                    | pF   |

| C <sub>S_XTAL</sub>  | СС | Т                                     | Total on-chip stray capacitance on XTAL pin <sup>8</sup>    | QFP                                             |                            | 6.0                    | 8.0                    | pF   |

|                      |    | C C Oscillator Transconductance (5 V) |                                                             |                                                 | f <sub>XTAL</sub> ≤ 8 MHz  | 2.6                    | 11.0                   |      |

| 9 <sub>m</sub>       | СС |                                       |                                                             | T <sub>J</sub> = -40 °C<br>to 150 °C            | f <sub>XTAL</sub> ≤ 20 MHz | 7.9                    | 26.0                   | mA/V |

| ļ                    |    |                                       |                                                             | f <sub>XTAL</sub> ≤ 40 MHz                      | 10.4                       | 34.0                   |                        |      |

<sup>1.</sup>  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%, TA = -40 to 125 °C, unless otherwise specified.

<sup>2.</sup> PLLIN clock retrieved directly from FXOSC clock. Input characteristics are granted when oscillator is used in functional mode. When bypass mode is used, oscillator input clock should verify  $f_{PLLIN}$  and  $\Delta_{PLLIN}$ .

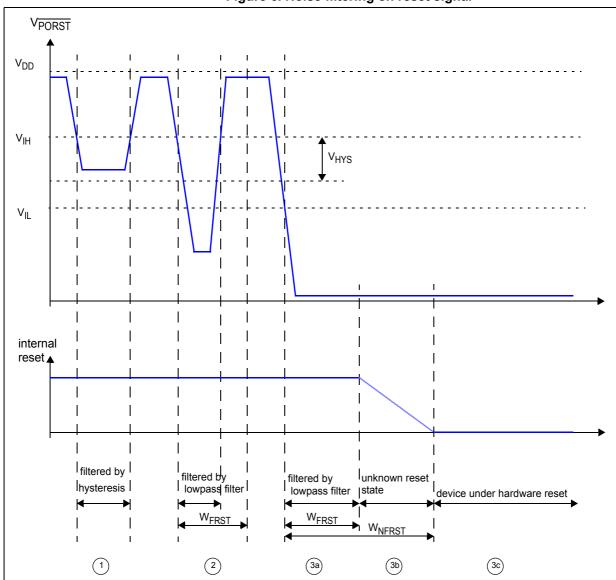

### 4.18 ADC electrical characteristics

#### 4.18.1 Introduction

The device provides a 12-bit Successive Approximation Register (SAR) analog-to-digital converter.

Figure 10. ADC characteristic and error definitions

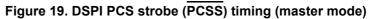

Table 35. DSPI CMOS master classic timing (full duplex and output only) – MTFE =  $0^{(1)}$

| #                                    | Cumi                                  | 0    |     | Characteristic                       | Condition                   |                           | Value <sup>(2)</sup>                             |                               | Unit        |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

|--------------------------------------|---------------------------------------|------|-----|--------------------------------------|-----------------------------|---------------------------|--------------------------------------------------|-------------------------------|-------------|-------|-------------|---------|----------|-------------|--|--------------------------|-------------|--------------------|--|--|--|--|--------------------|-------------|------|---|---|----|

| #                                    | Symbol                                |      | С   |                                      | Pad drive <sup>(3)</sup>    | Load (C <sub>L</sub> )    | Min                                              | Max                           | Jill        |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

|                                      |                                       |      | ; D | After SCK delay                      | SCK and PCS dr              | ive strength              |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 3                                    | 3 t <sub>ASC</sub>                    | СС   |     |                                      | Very strong                 | PCS = 0 pF<br>SCK = 50 pF | 53                                               | _                             | ns          |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 4                                    | 4 t <sub>SDC</sub>                    | СС   | D   | SCK duty cycle <sup>(4)</sup>        | SCK drive streng            | th                        |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| _                                    |                                       |      |     |                                      | Very strong                 | 0 pF                      | <sup>1</sup> / <sub>2</sub> t <sub>SCK</sub> - 2 | $^{1}/_{2}t_{SCK} + 2$        | ns          |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

|                                      |                                       |      |     |                                      |                             |                           |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 5                                    | t                                     | СС   | D   | PCSx to PCSS time <sup>(5)</sup>     | PCS and PCSS of             | drive strength            |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| J                                    | t <sub>PCSC</sub>                     | 0    |     |                                      | Very strong                 | 25 pF                     | 25                                               | _                             | ns          |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 6                                    | t                                     | СС   | D   | PCSS to PCSx time <sup>(5)</sup>     | PCS and PCSS drive strength |                           |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| Ü                                    | t <sub>PASC</sub>                     |      |     |                                      | Very strong                 | 25 pF                     | 25                                               | _                             | ns          |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| SIN setup time                       |                                       |      |     |                                      |                             |                           |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 7                                    | t                                     | СС   | D   | SIN setup time to SCK <sup>(6)</sup> | SCK drive strength          |                           |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| ,                                    | t <sub>sui</sub>                      | 0    |     |                                      | Very strong                 | 25 pF                     | 32                                               | _                             | ns          |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

|                                      | SIN hold time                         |      |     |                                      |                             |                           |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 8                                    | t                                     | СС   | D   | SIN hold time from                   | SCK drive strength          |                           |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

|                                      | чні                                   | 0    |     |                                      |                             |                           |                                                  |                               |             |       | 4H   CC   L | HI   CC | thi CC L | HI   CC   L |  | <sup>1</sup> HI   CC   L | HI   CC   D | t <sub>HI</sub> CC |  |  |  |  | SCK <sup>(6)</sup> | Very strong | 0 pF | 0 | _ | ns |

|                                      | SOUT data valid time (after SCK edge) |      |     |                                      |                             |                           |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 9                                    | t <sub>SUO</sub>                      | СС   |     | SOUT data valid                      | SOUT and SCK drive strength |                           |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 3                                    | เรียด                                 | 0    |     | time from SCK <sup>(7)</sup>         | Very strong                 | 25 pF                     | _                                                | 5                             | ns          |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| SOUT data hold time (after SCK edge) |                                       |      |     |                                      |                             |                           |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 10                                   | tuo                                   | CC D | ח   | SOUT data hold                       | SOUT and SCK                | drive strength            |                                                  |                               |             |       |             |         |          |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

| 10                                   | t <sub>HO</sub>                       |      |     |                                      |                             | , ט                       | ים                                               | time after SCK <sup>(7)</sup> | Very strong | 25 pF | 2           | _       | ns       |             |  |                          |             |                    |  |  |  |  |                    |             |      |   |   |    |

<sup>1.</sup> Protocol clock is 40 MHz and all pads are configured as very strong.

<sup>2.</sup> All timing values for output signals in this table are measured to 50% of the output voltage.

<sup>3.</sup> Timing is guaranteed to same drive capabilities for all signals, mixing of pad drives may reduce operating speeds and may cause incorrect operation.

t<sub>SDC</sub> is only valid for even divide ratios. For odd divide ratios the fundamental duty cycle is not 50:50. For these odd divide ratios cases, the absolute spec number is applied as jitter/uncertainty to the nominal high time and low time.

<sup>5.</sup> PCSx and PCSS using same pad configuration.

<sup>6.</sup> Input timing assumes an input slew rate of 1 ns (10% – 90%) and uses TTL / Automotive voltage thresholds.

SOUT Data Valid and Data hold are independent of load capacitance if SCK and SOUT load capacitances are the same value.

SCK Output (CPOL = 0)

SCK Output (CPOL = 1)

SIN

First Data

Data

Last Data

SOUT

First Data

Data

Last Data

Figure 18. DSPI CMOS master mode – modified timing, CPHA = 1

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved