Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 86                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 4K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

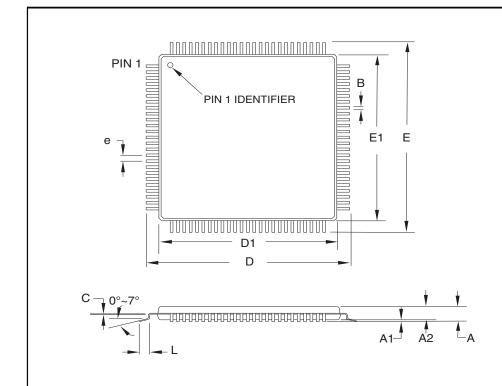

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-TFBGA                                                                 |

| Supplier Device Package    | 100-CBGA (9x9)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega1280-16cu |

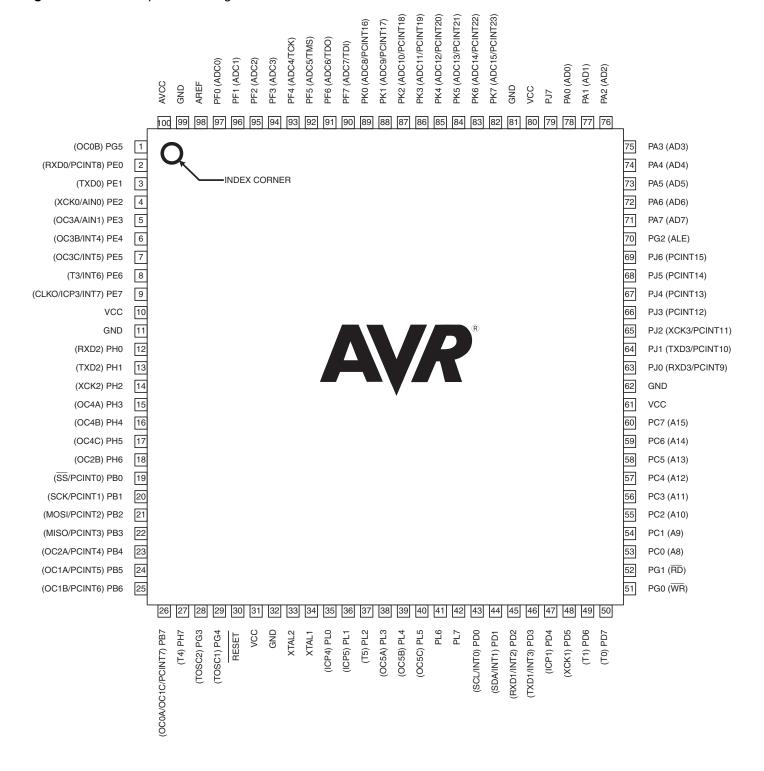

# 1. Pin Configurations

Figure 1-1. TQFP-pinout ATmega640/1280/2560

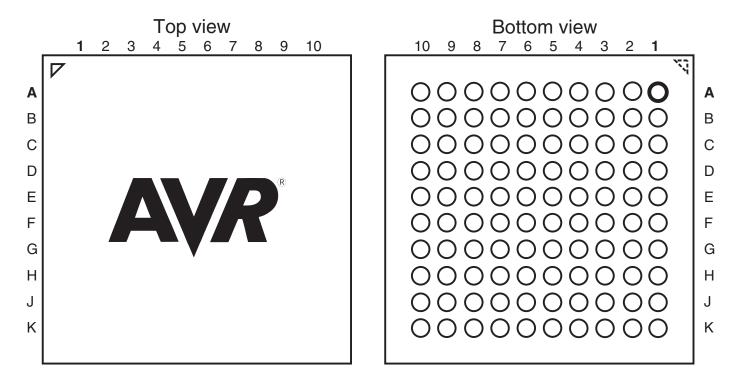

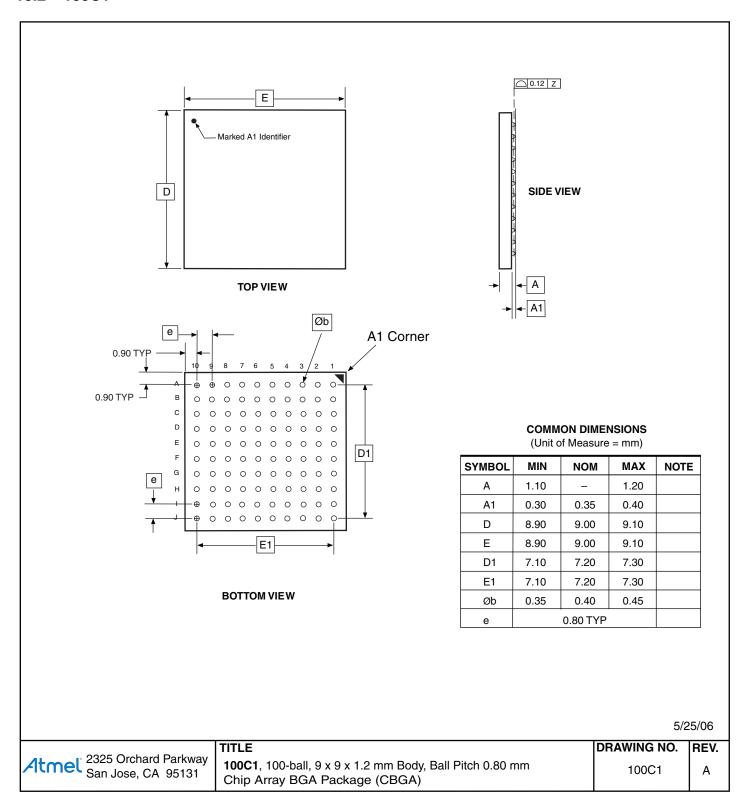

Figure 1-2. CBGA-pinout ATmega640/1280/2560

**Table 1-1.** CBGA-pinout ATmega640/1280/2560

|   | 1    | 2    | 3     | 4   | 5     | 6   | 7   | 8   | 9   | 10  |

|---|------|------|-------|-----|-------|-----|-----|-----|-----|-----|

|   | '    | 2    | 3     | 4   | 3     | 0   | 1   | 0   | 9   | 10  |

| Α | GND  | AREF | PF0   | PF2 | PF5   | PK0 | PK3 | PK6 | GND | VCC |

| В | AVCC | PG5  | PF1   | PF3 | PF6   | PK1 | PK4 | PK7 | PA0 | PA2 |

| С | PE2  | PE0  | PE1   | PF4 | PF7   | PK2 | PK5 | PJ7 | PA1 | PA3 |

| D | PE3  | PE4  | PE5   | PE6 | PH2   | PA4 | PA5 | PA6 | PA7 | PG2 |

| E | PE7  | PH0  | PH1   | PH3 | PH5   | PJ6 | PJ5 | PJ4 | PJ3 | PJ2 |

| F | VCC  | PH4  | PH6   | PB0 | PL4   | PD1 | PJ1 | PJ0 | PC7 | GND |

| G | GND  | PB1  | PB2   | PB5 | PL2   | PD0 | PD5 | PC5 | PC6 | VCC |

| Н | PB3  | PB4  | RESET | PL1 | PL3   | PL7 | PD4 | PC4 | PC3 | PC2 |

| J | PH7  | PG3  | PB6   | PL0 | XTAL2 | PL6 | PD3 | PC1 | PC0 | PG1 |

| K | PB7  | PG4  | VCC   | GND | XTAL1 | PL5 | PD2 | PD6 | PD7 | PG0 |

Note: The functions for each pin is the same as for the 100 pin packages shown in Figure 1-1 on page 2.

# 2. Overview

The ATmega640/1280/1281/2560/2561 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega640/1280/1281/2560/2561 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

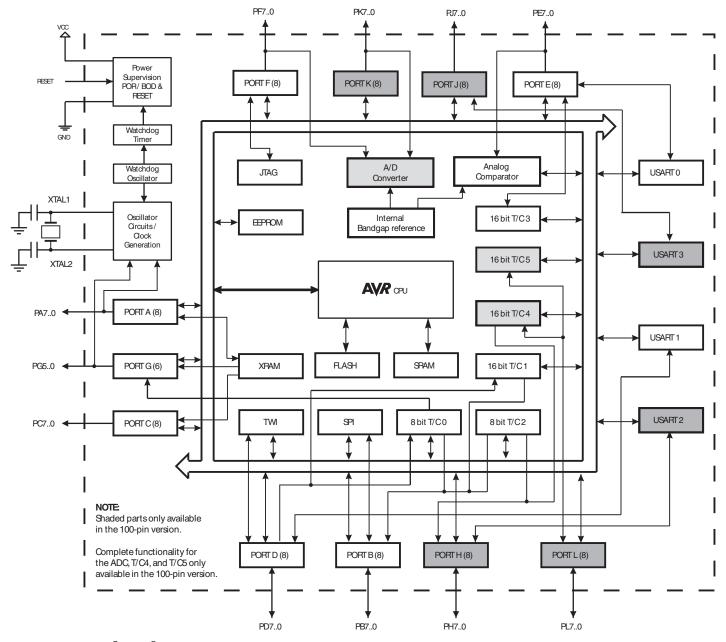

# 2.1 Block Diagram

Figure 2-1. Block Diagram

The Atmel® AVR® core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega640/1280/1281/2560/2561 provides the following features: 64K/128K/256K bytes of In-System Programmable Flash with Read-While-Write capabilities, 4Kbytes EEPROM, 8Kbytes SRAM, 54/86 general purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), six flexible Timer/Counters with compare modes and PWM, four USARTs, a byte oriented 2-wire Serial Interface, a 16-channel, 10-bit ADC with optional differential input stage with programmable gain, programmable Watchdog Timer with Internal Oscillator, an SPI serial port, IEEE® std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the Crystal/Resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run.

Atmel offers the QTouch<sup>®</sup> library for embedding capacitive touch buttons, sliders and wheels functionality into AVR microcontrollers. The patented charge-transfer signal acquisition offersrobust sensing and includes fully debounced reporting of touch keys and includes Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop and debug your own touch applications.

The device is manufactured using the Atmel high-density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega640/1280/1281/2560/2561 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega640/1280/1281/2560/2561 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

## 2.2 Comparison Between ATmega1281/2561 and ATmega640/1280/2560

Each device in the ATmega640/1280/1281/2560/2561 family differs only in memory size and number of pins. Table 2-1 summarizes the different configurations for the six devices.

**Table 2-1.** Configuration Summary

| Device     | Flash | EEPROM | RAM | General<br>Purpose I/O pins | 16 bits resolution PWM channels | Serial<br>USARTs | ADC<br>Channels |

|------------|-------|--------|-----|-----------------------------|---------------------------------|------------------|-----------------|

| ATmega640  | 64KB  | 4KB    | 8KB | 86                          | 12                              | 4                | 16              |

| ATmega1280 | 128KB | 4KB    | 8KB | 86                          | 12                              | 4                | 16              |

| ATmega1281 | 128KB | 4KB    | 8KB | 54                          | 6                               | 2                | 8               |

| ATmega2560 | 256KB | 4KB    | 8KB | 86                          | 12                              | 4                | 16              |

| ATmega2561 | 256KB | 4KB    | 8KB | 54                          | 6                               | 2                | 8               |

# 2.3 Pin Descriptions

#### 2.3.1 VCC

Digital supply voltage.

### 2.3.2 GND

Ground.

#### 2.3.3 Port A (PA7..PA0)

Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 75.

#### 2.3.4 Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B has better driving capabilities than the other ports.

Port B also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 76.

## 2.3.5 Port C (PC7..PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port C also serves the functions of special features of the ATmega640/1280/1281/2560/2561 as listed on page 79.

## 2.3.6 Port D (PD7..PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 80.

#### 2.3.7 Port E (PE7..PE0)

Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port E also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 82.

# 2.3.8 Port F (PF7..PF0)

Port F serves as analog inputs to the A/D Converter.

Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS), and PF4(TCK) will be activated even if a reset occurs.

Port F also serves the functions of the JTAG interface.

#### 2.3.9 Port G (PG5..PG0)

Port G is a 6-bit I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port G also serves the functions of various special features of the ATmega640/1280/1281/2560/2561 as listed on page 86.

#### 2.3.10 Port H (PH7..PH0)

Port H is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port H output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port H pins that are externally pulled low will source current if the pull-up resistors are activated. The Port H pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port H also serves the functions of various special features of the ATmega640/1280/2560 as listed on page 88.

# 2.3.11 Port J (PJ7..PJ0)

Port J is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port J output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port J pins that are externally pulled low will source current if the pull-up resistors are activated. The Port J pins are tri-stated when a reset condition becomes active, even if the clock is not running. Port J also serves the functions of various special features of the ATmega640/1280/2560 as listed on page 90.

# 7. Register Summary

| Address                       | Name                  | Bit 7           | Bit 6           | Bit 5           | Bit 4              | Bit 3              | Bit 2           | Bit 1              | Bit 0           | Page                                    |

|-------------------------------|-----------------------|-----------------|-----------------|-----------------|--------------------|--------------------|-----------------|--------------------|-----------------|-----------------------------------------|

| (0x1FF)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

|                               | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x13F)                       | Reserved              |                 |                 |                 |                    |                    |                 |                    |                 |                                         |

| (0x13E)                       | Reserved              |                 |                 |                 |                    |                    |                 |                    |                 |                                         |

| (0x13D)                       | Reserved              |                 |                 |                 |                    |                    |                 |                    |                 |                                         |

| (0x13C)                       | Reserved              |                 |                 |                 |                    |                    |                 |                    |                 |                                         |

| (0x13B)                       | Reserved              |                 |                 |                 |                    |                    |                 |                    |                 |                                         |

| (0x13A)                       | Reserved              |                 |                 |                 |                    |                    |                 |                    |                 |                                         |

| (0x139)                       | Reserved              |                 |                 |                 |                    |                    |                 |                    |                 |                                         |

| (0x138)                       | Reserved              |                 |                 |                 |                    |                    |                 |                    |                 |                                         |

| (0x137)                       | Reserved<br>UDR3      |                 |                 |                 | LICADTO I/O        | Data Danistan      |                 |                    |                 | nama 010                                |

| (0x136)<br>(0x135)            | UBRR3H                | -               | -               | -               | USANTS I/C         | Data Register      | ICADT2 Paud Pa  | te Register High E | Duto            | page 218                                |

| (0x135)<br>(0x134)            | UBRR3L                | -               | -               |                 |                    | ate Register Low I |                 | te Register High E | byte            | page 222<br>page 222                    |

| (0x134)                       | Reserved              | -               | -               | -               | - Land             |                    | -               | -                  | -               | page 222                                |

| (0x132)                       | UCSR3C                | UMSEL31         | UMSEL30         | UPM31           | UPM30              | USBS3              | UCSZ31          | UCSZ30             | UCPOL3          | page 235                                |

| (0x131)                       | UCSR3B                | RXCIE3          | TXCIE3          | UDRIE3          | RXEN3              | TXEN3              | UCSZ32          | RXB83              | TXB83           | page 234                                |

| (0x130)                       | UCSR3A                | RXC3            | TXC3            | UDRE3           | FE3                | DOR3               | UPE3            | U2X3               | MPCM3           | page 233                                |

| (0x12F)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               | P 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |

| (0x12E)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x12D)                       | OCR5CH                |                 |                 | Timer/Co        | unter5 - Output C  | ompare Register    | C High Byte     |                    |                 | page 160                                |

| (0x12C)                       | OCR5CL                |                 |                 |                 |                    | Compare Register   |                 |                    |                 | page 160                                |

| (0x12B)                       | OCR5BH                |                 |                 | Timer/Co        | unter5 - Output C  | ompare Register    | B High Byte     |                    |                 | page 160                                |

| (0x12A)                       | OCR5BL                |                 |                 |                 |                    | Compare Register   |                 |                    |                 | page 160                                |

| (0x129)                       | OCR5AH                |                 |                 | Timer/Co        | unter5 - Output C  | ompare Register    | A High Byte     |                    |                 | page 160                                |

| (0x128)                       | OCR5AL                |                 |                 | Timer/Co        | unter5 - Output C  | ompare Register    | A Low Byte      |                    |                 | page 160                                |

| (0x127)                       | ICR5H                 |                 |                 | Timer/0         | Counter5 - Input ( | Capture Register   | High Byte       |                    |                 | page 161                                |

| (0x126)                       | ICR5L                 |                 |                 | Timer/          | Counter5 - Input   | Capture Register   | Low Byte        |                    |                 | page 161                                |

| (0x125)                       | TCNT5H                |                 |                 | Time            | er/Counter5 - Co   | unter Register Hig | gh Byte         |                    |                 | page 158                                |

| (0x124)                       | TCNT5L                |                 |                 | Tim             | er/Counter5 - Co   | unter Register Lo  | w Byte          |                    |                 | page 158                                |

| (0x123)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x122)                       | TCCR5C                | FOC5A           | FOC5B           | FOC5C           | -                  | -                  | -               | -                  | -               | page 157                                |

| (0x121)                       | TCCR5B                | ICNC5           | ICES5           | -               | WGM53              | WGM52              | CS52            | CS51               | CS50            | page 156                                |

| (0x120)                       | TCCR5A                | COM5A1          | COM5A0          | COM5B1          | COM5B0             | COM5C1             | COM5C0          | WGM51              | WGM50           | page 154                                |

| (0x11F)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x11E)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x11D)                       | Reserved<br>Reserved  | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x11C)<br>(0x11B)            | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x11B)<br>(0x11A)            | Reserved              | -               | -               |                 | -                  | -                  | -               | _                  | -               |                                         |

| (0x11A)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x118)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x117)                       | Reserved              | _               | _               | -               | -                  | _                  | _               | -                  | -               |                                         |

| (0x116)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x115)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x114)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x113)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x112)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x111)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x110)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x10F)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x10E)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x10D)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | -               |                                         |

| (0x10C)                       | Reserved              | -               | -               | -               | -                  | -                  | -               | -                  | - DODTI O       |                                         |

| (0x10B)                       | PORTL                 | PORTL7          | PORTL6          | PORTL5          | PORTL4             | PORTL3             | PORTL2          | PORTL1             | PORTL0          | page 100                                |

| (0x10A)                       | DDRL<br>PINL          | DDL7<br>PINL7   | DDL6<br>PINL6   | DDL5            | DDL4               | DDL3               | DDL2            | DDL1               | DDL0            | page 100                                |

| (0x109)                       | PORTK                 | PINL7<br>PORTK7 | PORTK6          | PINL5<br>PORTK5 | PINL4<br>PORTK4    | PINL3<br>PORTK3    | PINL2<br>PORTK2 | PINL1<br>PORTK1    | PINL0<br>PORTK0 | page 100                                |

| (0x108)                       | DDRK                  | DDK7            | DDK6            | DDK5            | DDK4               | DDK3               | DDK2            | DDK1               | DDK0            | page 99<br>page 99                      |

| (0v107)                       |                       | אטט             |                 |                 | PINK4              | PINK3              | PINK2           | PINK1              | PINK0           | page 99                                 |

| (0x107)<br>(0x106)            |                       | PINK7           | PINKE           |                 |                    | I HALLO            | 1 1131134       | 1 113131           | I II VI VU      | page 00                                 |

| (0x106)                       | PINK                  | PINK7           | PINK6<br>PORTJ6 | PINK5<br>PORTJ5 |                    |                    | PURT 12         | PORT I1            | PORT.In         | page 90                                 |

| (0x106)<br>(0x105)            | PINK<br>PORTJ         | PORTJ7          | PORTJ6          | PORTJ5          | PORTJ4             | PORTJ3             | PORTJ2<br>DDJ2  | PORTJ1             | PORTJ0          | page 99                                 |

| (0x106)<br>(0x105)<br>(0x104) | PINK<br>PORTJ<br>DDRJ | PORTJ7<br>DDJ7  | PORTJ6<br>DDJ6  | PORTJ5<br>DDJ5  | PORTJ4<br>DDJ4     | PORTJ3<br>DDJ3     | DDJ2            | DDJ1               | DDJ0            | page 99                                 |

| (0x106)<br>(0x105)            | PINK<br>PORTJ         | PORTJ7          | PORTJ6          | PORTJ5          | PORTJ4             | PORTJ3             |                 |                    |                 |                                         |

| Address                    | Name             | Bit 7          | Bit 6          | Bit 5          | Bit 4              | Bit 3                                  | Bit 2            | Bit 1             | Bit 0          | Page                              |

|----------------------------|------------------|----------------|----------------|----------------|--------------------|----------------------------------------|------------------|-------------------|----------------|-----------------------------------|

| (0x78)                     | ADCL             |                |                |                | ADC Data Re        | egister Low byte                       |                  | •                 |                | page 286                          |

| (0x77)                     | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              |                                   |

| (0x76)                     | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              |                                   |

| (0x75)                     | XMCRB            | XMBK           | -              | -              | -                  | -                                      | XMM2             | XMM1              | XMM0           | page 38                           |

| (0x74)<br>(0x73)           | XMCRA<br>TIMSK5  | SRE<br>-       | SRL2           | SRL1<br>ICIE5  | SRL0               | SRW11<br>OCIE5C                        | SRW10<br>OCIE5B  | SRW01<br>OCIE5A   | SRW00<br>TOIE5 | page 36                           |

| (0x73)<br>(0x72)           | TIMSK4           | -              | -              | ICIE5          | -                  | OCIE4C                                 | OCIE3B<br>OCIE4B | OCIE4A            | TOIE3          | page 162<br>page 161              |

| (0x71)                     | TIMSK3           | -              | -              | ICIE3          | -                  | OCIE3C                                 | OCIE3B           | OCIE3A            | TOIE3          | page 161                          |

| (0x70)                     | TIMSK2           | -              | -              | -              | -                  | -                                      | OCIE2B           | OCIE2A            | TOIE2          | page 188                          |

| (0x6F)                     | TIMSK1           | -              | -              | ICIE1          | -                  | OCIE1C                                 | OCIE1B           | OCIE1A            | TOIE1          | page 161                          |

| (0x6E)                     | TIMSK0           | -              | -              | -              | -                  | -                                      | OCIE0B           | OCIE0A            | TOIE0          | page 131                          |

| (0x6D)                     | PCMSK2           | PCINT23        | PCINT22        | PCINT21        | PCINT20            | PCINT19                                | PCINT18          | PCINT17           | PCINT16        | page 113                          |

| (0x6C)                     | PCMSK1           | PCINT15        | PCINT14        | PCINT13        | PCINT12            | PCINT11                                | PCINT10          | PCINT9            | PCINT8         | page 113                          |

| (0x6B)                     | PCMSK0           | PCINT7         | PCINT6         | PCINT5         | PCINT4             | PCINT3                                 | PCINT2           | PCINT1            | PCINT0         | page 114                          |

| (0x6A)<br>(0x69)           | EICRB<br>EICRA   | ISC71<br>ISC31 | ISC70<br>ISC30 | ISC61<br>ISC21 | ISC60<br>ISC20     | ISC51<br>ISC11                         | ISC50<br>ISC10   | ISC41<br>ISC01    | ISC40<br>ISC00 | page 110                          |

| (0x69)                     | PCICR            | -              | -              | -              | 15020              | -                                      | PCIE2            | PCIE1             | PCIE0          | page 110<br>page 112              |

| (0x67)                     | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              | page 112                          |

| (0x66)                     | OSCCAL           |                |                |                | Oscillator Cal     | bration Register                       |                  |                   |                | page 48                           |

| (0x65)                     | PRR1             | -              | -              | PRTIM5         | PRTIM4             | PRTIM3                                 | PRUSART3         | PRUSART2          | PRUSART1       | page 56                           |

| (0x64)                     | PRR0             | PRTWI          | PRTIM2         | PRTIM0         | -                  | PRTIM1                                 | PRSPI            | PRUSART0          | PRADC          | page 55                           |

| (0x63)                     | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              |                                   |

| (0x62)                     | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              |                                   |

| (0x61)                     | CLKPR            | CLKPCE         | -              | -              | -                  | CLKPS3                                 | CLKPS2           | CLKPS1            | CLKPS0         | page 48                           |

| (0x60)                     | WDTCSR           | WDIF           | WDIE           | WDP3           | WDCE               | WDE<br>V                               | WDP2             | WDP1              | WDP0           | page 65                           |

| 0x3F (0x5F)<br>0x3E (0x5E) | SREG<br>SPH      | SP15           | T<br>SP14      | H<br>SP13      | S<br>SP12          | SP11                                   | N<br>SP10        | Z<br>SP9          | C<br>SP8       | page 13<br>page 15                |

| 0x3D (0x5D)                | SPL              | SP7            | SP6            | SP5            | SP4                | SP3                                    | SP2              | SP1               | SP0            | page 15                           |

| 0x3C (0x5C)                | EIND             | -              | -              | -              | -                  | -                                      | -                | -                 | EIND0          | page 16                           |

| 0x3B (0x5B)                | RAMPZ            | -              | -              | -              | -                  | -                                      | -                | RAMPZ1            | RAMPZ0         | page 16                           |

| 0x3A (0x5A)                | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              |                                   |

| 0x39 (0x59)                | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              |                                   |

| 0x38 (0x58)                | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              |                                   |

| 0x37 (0x57)                | SPMCSR           | SPMIE          | RWWSB          | SIGRD          | RWWSRE             | BLBSET                                 | PGWRT            | PGERS             | SPMEN          | page 323                          |

| 0x36 (0x56)                | Reserved         | - ITD          | -              | -              | - DUD              | -                                      | -                | - IVCEI           | -              | neme C4 100 00 001                |

| 0x35 (0x55)<br>0x34 (0x54) | MCUCR<br>MCUSR   | JTD<br>-       | -              | -              | PUD<br>JTRF        | WDRF                                   | BORF             | IVSEL<br>EXTRF    | IVCE<br>PORF   | page 64, 108, 96, 301<br>page 301 |

| 0x33 (0x53)                | SMCR             | -              | -              | -              | -                  | SM2                                    | SM1              | SM0               | SE             | page 50                           |

| 0x32 (0x52)                | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              | page                              |

| 0x31 (0x51)                | OCDR             | OCDR7          | OCDR6          | OCDR5          | OCDR4              | OCDR3                                  | OCDR2            | OCDR1             | OCDR0          | page 294                          |

| 0x30 (0x50)                | ACSR             | ACD            | ACBG           | ACO            | ACI                | ACIE                                   | ACIC             | ACIS1             | ACIS0          | page 266                          |

| 0x2F (0x4F)                | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              |                                   |

| 0x2E (0x4E)                | SPDR             |                |                |                | SPI Da             | ta Register                            | 1                | ı                 |                | page 199                          |

| 0x2D (0x4D)                | SPSR             | SPIF           | WCOL           | -              | -                  | -                                      | -                | -                 | SPI2X          | page 198                          |

| 0x2C (0x4C)                | SPCR             | SPIE           | SPE            | DORD           | MSTR Conoral Burns | CPOL                                   | CPHA             | SPR1              | SPR0           | page 197                          |

| 0x2B (0x4B)<br>0x2A (0x4A) | GPIOR2<br>GPIOR1 |                |                |                |                    | se I/O Register 2<br>se I/O Register 1 |                  |                   |                | page 36<br>page 36                |

| 0x29 (0x49)                | Reserved         | -              | -              | -              | -                  | -                                      | -                | -                 | -              | page oo                           |

| 0x28 (0x48)                | OCR0B            |                |                | Tin            | ner/Counter0 Out   | out Compare Reg                        | ister B          |                   |                | page 130                          |

| 0x27 (0x47)                | OCR0A            |                |                |                | ner/Counter0 Out   |                                        |                  |                   |                | page 130                          |

| 0x26 (0x46)                | TCNT0            |                |                |                | Timer/Co           | unter0 (8 Bit)                         |                  |                   |                | page 130                          |

| 0x25 (0x45)                | TCCR0B           | FOC0A          | FOC0B          | -              | -                  | WGM02                                  | CS02             | CS01              | CS00           | page 129                          |

| 0x24 (0x44)                | TCCR0A           | COM0A1         | COM0A0         | COM0B1         | COM0B0             | -                                      | -                | WGM01             | WGM00          | page 126                          |

| 0x23 (0x43)                | GTCCR            | TSM            | -              | -              | -                  | -                                      | -                | PSRASY            | PSRSYNC        | page 166, 189                     |

| 0x22 (0x42)<br>0x21 (0x41) | EEARH<br>EEARL   | -              | -              | -              | EEPROM Addres      |                                        | EEPROM Address   | s Hegister High B | уте            | page 34<br>page 34                |

| 0x21 (0x41)<br>0x20 (0x40) | EEDR             |                |                |                |                    | s недізіег Low в<br>Data Register      | yıe              |                   |                | page 34                           |

| 0x1F (0x3F)                | EECR             | -              | -              | EEPM1          | EEPM0              | EERIE                                  | EEMPE            | EEPE              | EERE           | page 34                           |

| 0x1E (0x3E)                | GPIOR0           |                |                |                |                    | se I/O Register 0                      |                  |                   |                | page 36                           |

| 0x1D (0x3D)                | EIMSK            | INT7           | INT6           | INT5           | INT4               | INT3                                   | INT2             | INT1              | INT0           | page 111                          |

| 0x1C (0x3C)                | EIFR             | INTF7          | INTF6          | INTF5          | INTF4              | INTF3                                  | INTF2            | INTF1             | INTF0          | page 112                          |

| 0x1B (0x3B)                | PCIFR            | -              | -              | -              | -                  |                                        | PCIF2            | PCIF1             | PCIF0          | page 113                          |

| 0x1A (0x3A)                | TIFR5            | -              | -              | ICF5           | -                  | OCF5C                                  | OCF5B            | OCF5A             | TOV5           | page 162                          |

| 0x19 (0x39)                | TIFR4            | -              | -              | ICF4           | -                  | OCF4C                                  | OCF4B            | OCF4A             | TOV4           | page 162                          |

| 0x18 (0x38)                | TIFR3            | -              | -              | ICF3           | -                  | OCF3C                                  | OCF3B            | OCF3A             | TOV3           | page 162                          |

| 0x17 (0x37)<br>0x16 (0x36) | TIFR2<br>TIFR1   | -              | -              | -<br>ICF1      | -                  | OCF1C                                  | OCF2B<br>OCF1B   | OCF2A<br>OCF1A    | TOV2<br>TOV1   | page 188                          |

| 0x16 (0x36)<br>0x15 (0x35) | TIFRI<br>TIFR0   | -              | -              | IUF I          | -                  | -                                      | OCF1B<br>OCF0B   | OCF1A<br>OCF0A    | TOV1           | page 162<br>page 131              |

| 0.10 (0.00)                | III NO           | _              | •              | -              | _                  | -                                      | 1 00100          | COLON             | 1000           | page 101                          |

# 8. Instruction Set Summary

| APPLIANT CAMP   Add two Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mnemonics        | Operands          | Description                              | Operation                                            | Flags         | #Clocks |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|------------------------------------------|------------------------------------------------------|---------------|---------|

| ACC   Ris Ris   Add two Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ARITHMETIC AND L | OGIC INSTRUCTIONS | •                                        |                                                      |               |         |

| ACOUNT   Ris   Ris   Act will corpy to Engates   Ris - Ris - Ris - Ris   C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                   |                                          | Rd ← Rd + Rr                                         | Z. C. N. V. H | 1       |

| ADM   ADM   ADM   Add Immediate to World   Ref. Fig Ref Fig Z. C., N. V., S   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | ,                 |                                          |                                                      |               |         |

| SUBBLE   PR   K   Subtent Consistence   Pac   Pac   Pac   Fac   K   Z   C, N, V, H   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                   |                                          |                                                      |               |         |

| Subsect Constant from Register   Rec. Fig. 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                   |                                          | Rd ← Rd - Rr                                         |               |         |

| SEC   Ris Rr   Subtent with Carry for Registers   Ris C   Ri  |                  | ,                 |                                          |                                                      |               | 1       |

| SEC   Risk   Subtest work Carry Corestant from Reg.   Risk - Risk - C   Z. C. N. V. N   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |                   |                                          |                                                      |               |         |

| SIMPLE   BALFAEL   Subtect Immediate from Worst   BARFAEL - BARFAEL   Z. C. N. V. S.   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |                   | -                                        |                                                      |               | 1       |

| AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SBIW             | Rdl,K             |                                          | Rdh:Rdl ← Rdh:Rdl - K                                |               | 2       |

| OR         Rd, K.         Logoal Of Registers         Re ← Box Pr         Z, N, V         1           EOR         Rd, K.         Exclusion OR Registers         Rd ← Rel Rel Pr         Z, N, V         1           EOR         Rd, R.         Exclusion OR Registers         Rd ← Rel Rel Pr         Z, N, V         1           NCO         Rd         More Complement         Rd ← Rel Rel Pr         Z, N, V         1           NEG         Rd         Town Complement         Rd ← Rel Rel Pr         Z, N, V         1           SBR         RdX         Collega Religion Register         Rd ← Rel « Rel Fe (Religion Register)         Rd ← Rel « Religion Register)         Rd ← Rel « Religion Register)         Rd ← Religion Register         Rd ← Religion Reli                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AND              | Rd, Rr            |                                          | Rd ← Rd • Rr                                         | Z, N, V       | 1       |

| OFI         R.K.         Logisted RR Register and Constant         Rat − Rat = Rr         2_R, V         1           EGR         R.M. R         Exclusive OR Register         Rat − Rat = Rr         2_C, N, V         1           COM         Rd         One Complement         Rat − Rat = Rr         2_C, N, V         1           SRR         RAK         Set Billio in Register         Rat − Rat × K         2_C, N, V         1           SRR         RAK         Set Billio in Register         Rat − Rat × K         2_C, N, V         1           DCC         Rd         Moderner         Rat − Rat × R         2_C, N, V         1           DCC         Rd         Docement         Rat − Rat × R         2_C, N, V         1           TST         Rd         Text Cars on Minus         Rat − Rat × R         2_C, N, V         1           TST         Rd         Text Cars on Minus         Rat − Rat × R         2_C, N, V         1           SER         Rd         Text Cars on Minus         Rat − Rat × R         2_C, N, V         1           SER         Rd         Text Cars on Minus         Rat − Rat × R         2_C, N, V         1           SER         Rd         Moderno Minus         Rat − Rat × R         2_C,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ANDI             | Rd, K             | Logical AND Register and Constant        | Rd ← Rd • K                                          | Z, N, V       | 1       |

| EOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OR               | Rd, Rr            | Logical OR Registers                     | Rd ← Rd v Rr                                         | Z, N, V       | 1       |

| EOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ORI              | Rd, K             | Logical OR Register and Constant         | Rd ← Rd v K                                          | Z, N, V       | 1       |